Результат интеллектуальной деятельности: Способ изготовления высокотемпературных КМОП КНИ интегральных схем

Вид РИД

Изобретение

ОБЛАСТЬ ТЕХНИКИ

Заявленное изобретение относится к области технологии изготовления полупроводниковых приборов и сверхбольших интегральных схем (СБИС) на основе кремниевой подложки с использованием скрытого диэлектрика (КНИ), предназначенных для использования в средах с максимальной температурой до 250°С.

УРОВЕНЬ ТЕХНИКИ

Из существующего технического уровня известны интегральные схемы, основным элементом которых являются МОП-транзисторы, выполненные на основе подложки из объемного кремния (патенты № RU 2197769, № RU 2024107, № RU 2053586, № RU 2245589, № US 6087235 А) или на основе кремниевой подложки с использованием скрытого диэлектрика (кремний на изоляторе, КНИ) (патенты № US 5893729, № US 20130187230 A1, № RU 2284611, № RU 2193255).

В первом случае МОП-транзисторы представляют собой структуры, изготовленные на основе кремниевой подложки путем осуществления определенной последовательности технологических операций, включающей жидкостное и плазмохимическое травление, химико-механическую полировку, окисление, ионную имплантацию кремния, отжиг структур после ионной имплантации, осаждение слоев поликристаллического кремния и металлов (Фиг. 1). При этом для обеспечения межприборной изоляции МОП-транзисторов используют области локального окисления кремния или, в случае субмикронных минимальных технологических норм, области мелкой щелевой изоляции (Shallow Trench Isolation, STI), получаемые путем последовательного осуществления травления канавок в кремнии, окисления их поверхности и заполнения диоксидом кремния. Максимальная рабочая температура интегральных схем на основе МОП-транзисторов, выполненных на подложках из объемного кремния, составляет 125°С [1].

В случае изготовления МОП-транзисторов на основе кремниевой подложки с использованием скрытого диэлектрика (КНИ), выполняются технологические операции, аналогичные операциям, осуществляемым при изготовлении МОП-транзисторов на основе подложки из объемного кремния, но для обеспечения межприборной изоляции МОП-транзисторов, помимо областей локального окисления кремния или мелкой щелевой изоляции, используют скрытый диэлектрик (Фиг. 2). Максимальная рабочая температура интегральных МОП-транзисторов и интегральных схем, выполненных на основе подложек КНИ, составляет 175°С [2].

К причинам, препятствующим повышению максимальной рабочей температуры интегральных схем на основе МОП-транзисторов, изготавливаемых способом № RU 2053586, относятся эффекты паразитных сопротивлений подложки и паразитных биполярных транзисторов (Фиг. 3), обусловленные проводимостью объемного кремния при высоких температурах, и, как следствие, дрейфом носителей из активных областей МОП-транзисторов в весь объем подложки.

К причинам, препятствующим повышению максимальной рабочей температуры интегральных схем на основе МОП-транзисторов, изготавливаемых способом № US 20130187230 А1, относятся большие значения токов утечки через р-n переходы, отсутствие изоляции смежных МОП-транзисторов, что приводит к дрейфу носителей в пределах приборного слоя кремния и появлению дополнительных искажающих потенциалов при температурах >175°С.

Способ изготовления интегральных схем на основе КНИ МОП-транзисторов № US 5893729 «Method of making SOI circuit for higher temperature and higher voltage applications» [3] характеризуется следующими отличительными признаками:

- формирование областей межприборной мелкой щелевой изоляции STI;

- формирование областей n- и p-карманов в приборном слое кремния посредством ионной имплантации;

- причем доза имплантируемой примеси в n-карман составляет 3,3×1012 см-2, а конечная концентрация примеси в р-кармане составляет от 0,35×1017 до 1,5×1017 см-3;

- для областей стоков и истоков конечная концентрация примеси составляет от 0,8×1020 до 2×1020 см-3.

Вследствие указанных существенных признаков и сходства решаемой проблемы температурной стойкости интегральных схем способ № US 5893729 «Method of making SOI circuit for higher temperature and higher voltage applications» [3] является наиболее близким по технической сущности предлагаемому изобретению и принимается в качестве прототипа предлагаемого изобретения.

К недостаткам данного способа изготовления высокотемпературных интегральных схем следует отнести то, что значения доз имплантируемых примесей, а также концентрации примесей в карманах МОП-транзисторов, изготавливаемых согласно способу [3], не обеспечивают стойкости получаемых интегральных схем к воздействию температур в диапазоне от 175 до 250°С. В случае использования высокотемпературных интегральных микросхем в непосредственной близости от источников тепла, выполненных в соответствии со способом № US 5893729 «Method of making SOI circuit for higher temperature and higher voltage applications» [3], имеют место повышение токов утечки и паразитные потенциалы, уменьшающие пороговые напряжения МОП-транзисторов, как показано в [4].

Вследствие указанного недостатка интегральные схемы и МОП-транзисторы, изготовленные в соответствии с последовательностью технологических операций способа № US 5893729 «Method of making SOI circuit for higher temperature and higher voltage applications» [3], не обладают достаточной стойкостью к воздействиям высоких температур в сравнении с интегральными схемами и МОП-транзисторами, изготавливаемыми предлагаемым способом.

РАСКРЫТИЕ ИЗОБРЕТЕНИЯ

Задачей, на решение которой направлен способ изготовления высокотемпературных КМОП КНИ интегральных схем, является достижение технического результата, заключающегося в повышении максимальной рабочей температуры полупроводниковых интегральных МОП-транзисторов до 375°С и, как следствие, повышении устойчивости интегральных микросхем к воздействию высоких температур (свыше 175°С).

Поставленная задача решается за счет того, что способ изготовления высокотемпературных КМОП КНИ интегральных схем, включающий операции формирования областей мелкой щелевой изоляции STI, ионной имплантации в области карманов n- и р-канальных МОП-транзисторов, формирования слоя подзатворного диэлектрика, осаждения слоя поликристаллического кремния и формирования затворов МОП-транзисторов, ионной имплантации в области стоков и истоков МОП-транзисторов, формирования контактных окон к активным областям, отличается тем, что при осуществлении операции ионной имплантации в области стоков и истоков МОП-транзисторов n-типа доза ионов мышьяка составляет от 2×1015 до 3×1015 см-2, энергия пучка - от 63 до 77 кэВ, а для областей стоков и истоков МОП-транзисторов р-типа доза ионов бора составляет от 2,8×1015 до 4,2×1015 см-2, энергия пучка - от 6 до 8 кэВ.

В предлагаемом способе изготовления высокотемпературных КМОП КНИ интегральных схем, в отличие от способа № US 5893729 «Method of making SOI circuit for higher temperature and higher voltage applications» [3], обеспечиваются оптимальные параметры дозы и энергии имплантируемых ионов при формировании карманов, стоков и истоков МОП-транзисторов, физическое сопряжение областей мелкой щелевой изоляции STI и скрытой изоляции BOX, а также физическое сопряжение областей кармана, стока и истока с верхней границей слоя BOX.

При этом токи утечки МОП-транзисторов, выполненных согласно предложенному способу, в несколько раз меньше в сравнении с МОП-транзисторами, известными из текущего уровня техники. Минимальные токи утечки предлагаемых к осуществлению интегральных МОП-транзисторов позволяют использовать их в составе интегральных схем, стойких к воздействию высоких температур.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Предложенный способ поясняется чертежами.

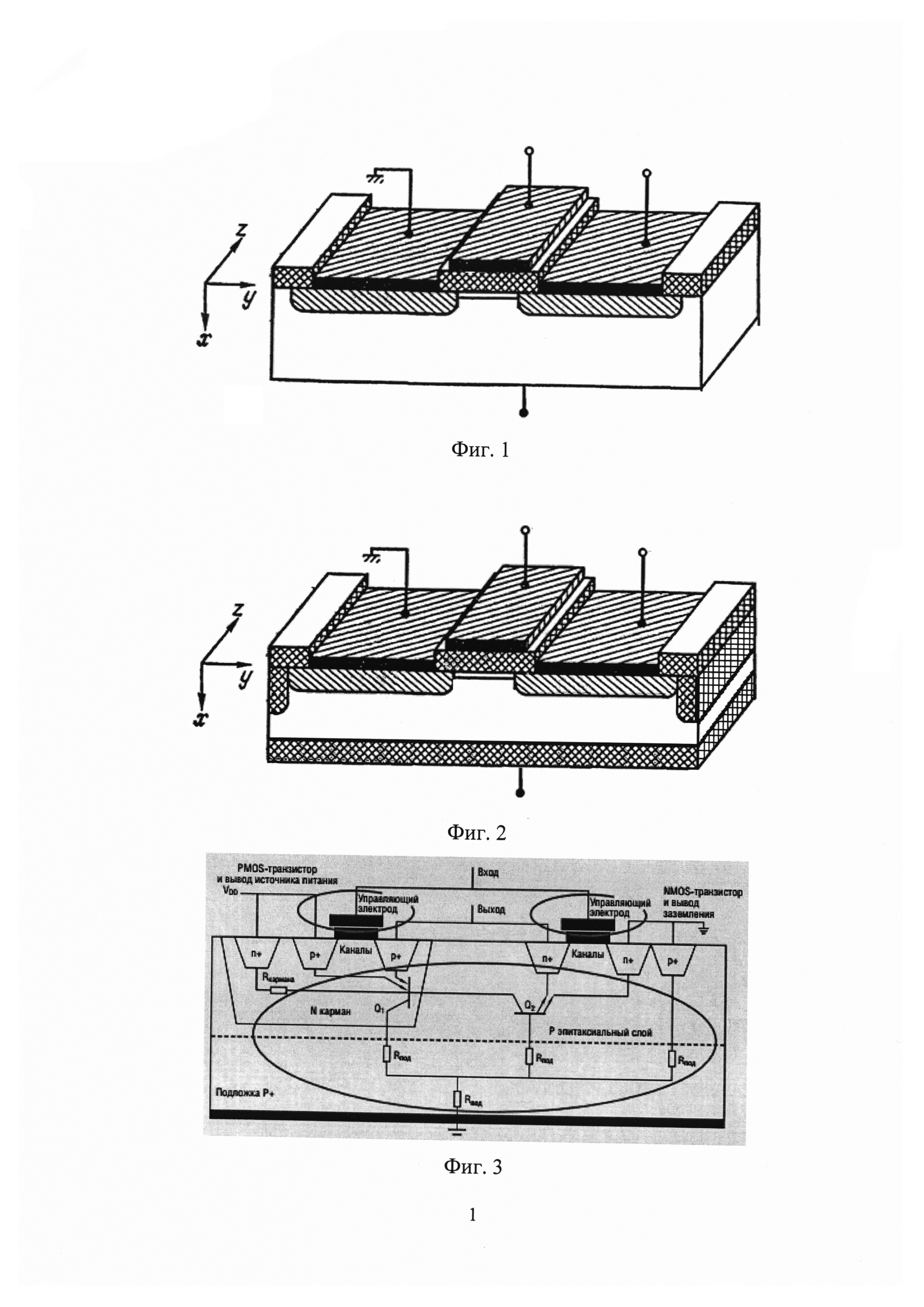

На Фиг. 1 изображена упрощенная структурная схема МОП-транзистора на основе подложки из объемного кремния.

На Фиг. 2 изображена упрощенная структурная схема МОП-транзистора на основе кремниевой подложки с использованием скрытого диэлектрика.

На Фиг. 3 показаны эффекты паразитных элементов, обусловленные исполнением интегральных МОП-транзисторов на общей полупроводниковой подложке.

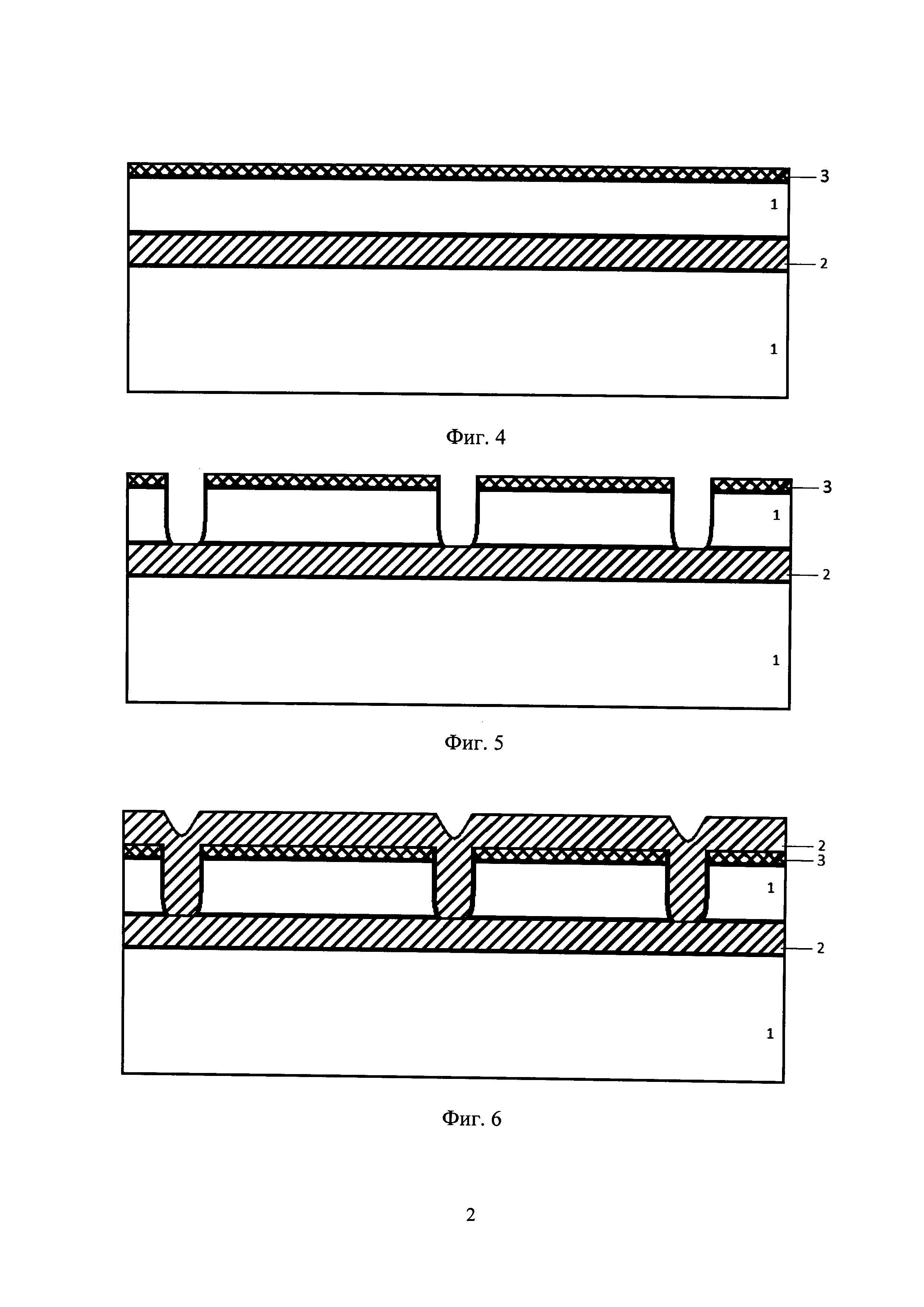

На Фиг. 4 приведено схематическое изображение поперечного сечения исходной структуры КНИ, включающей слои кремния (1), диоксида кремния (2) и жертвенного нитрида кремния (3).

На Фиг. 5 приведено схематическое изображение поперечного сечения формируемой структуры после операций плазмохимического травления слоев жертвенного нитрида кремния (3) и слоя приборного кремния (1) до поверхности скрытого диэлектрика (2) и удаления остатков фоторезиста.

На Фиг. 6 приведено схематическое изображение поперечного сечения формируемой структуры после операций термического окисления вытравленных канавок STI и их последующего заполнения нелегированным диоксидом кремния (2) путем осаждения в высокоплотной плазме.

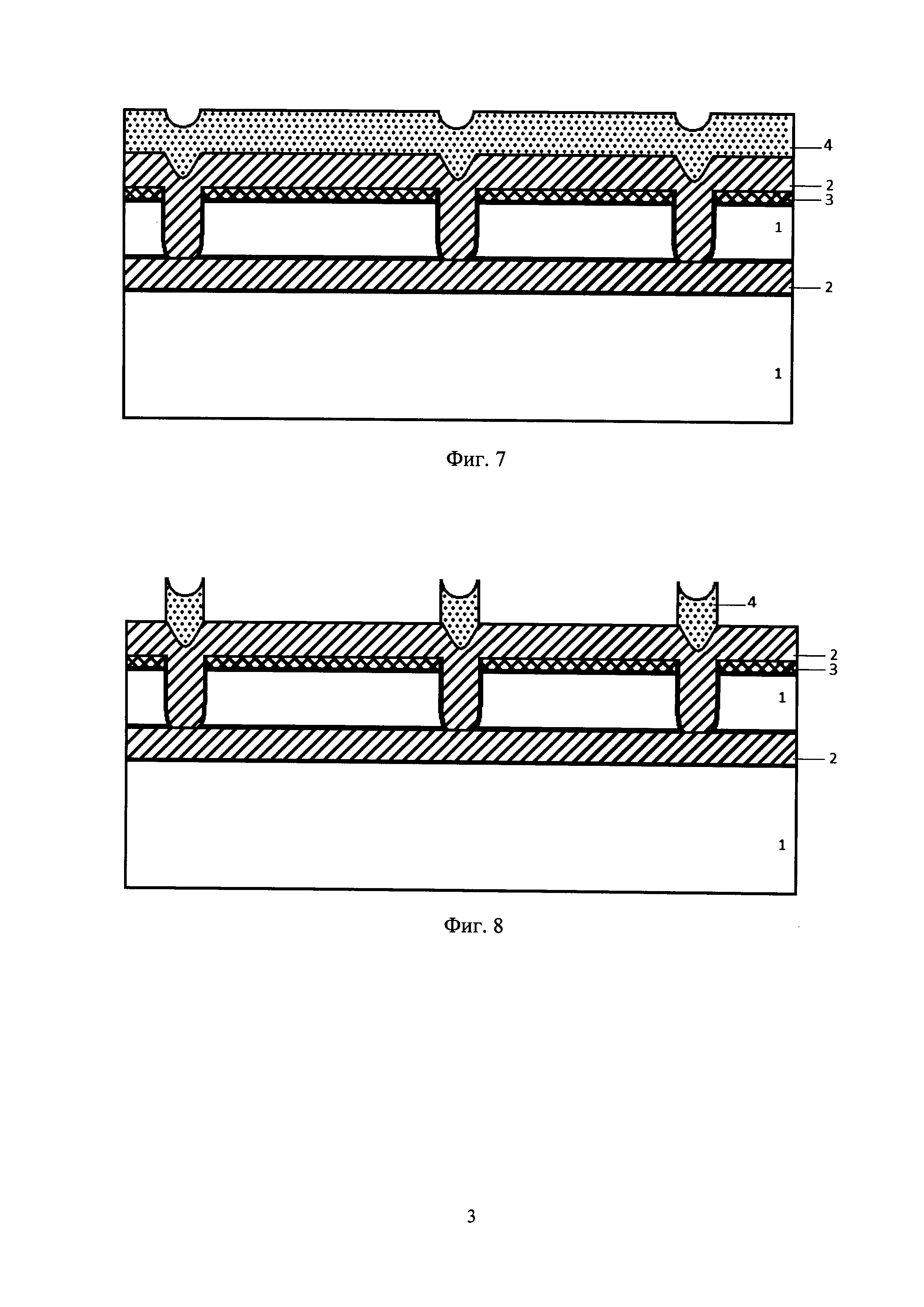

На Фиг. 7 приведено схематическое изображение поперечного сечения формируемой структуры после операции осаждения тетраэтилортосиликата (4) из газовой фазы (CVD).

На Фиг. 8 приведено схематическое изображение поперечного сечения формируемой структуры после операции плазмохимического травления сформированных диэлектрических слоев тетраэтилортосиликата (4) и диоксида кремния (2).

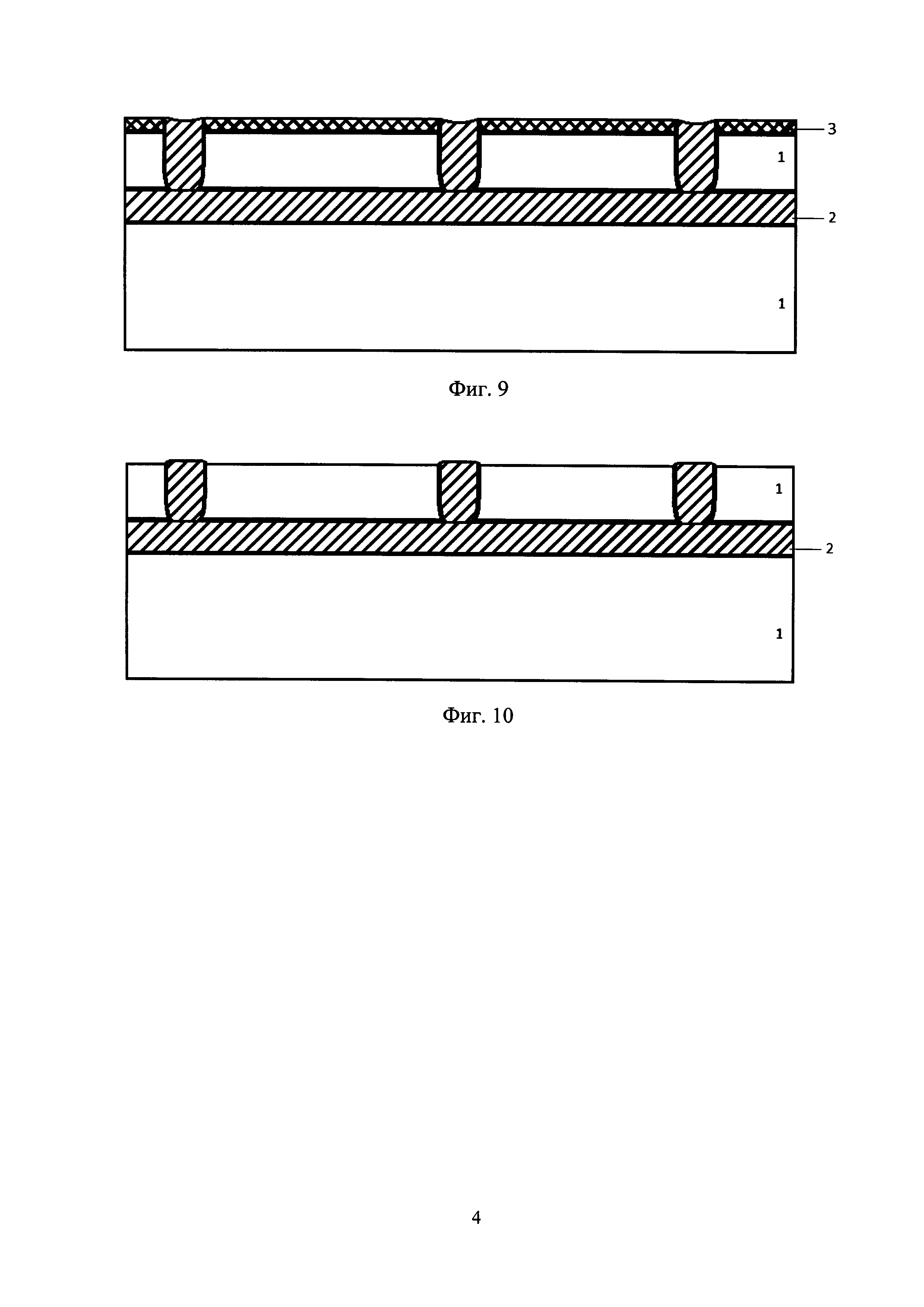

На Фиг. 9 приведено схематическое изображение поперечного сечения формируемой структуры после операции химико-механической полировки оставшегося после травления слоя диоксида кремния (2) до уровня жертвенного слоя нитрида кремния (3).

На Фиг. 10 приведено схематическое изображение поперечного сечения формируемой структуры после операции жидкостного травления жертвенного слоя нитрида кремния (3) с лицевой и задней сторон пластины.

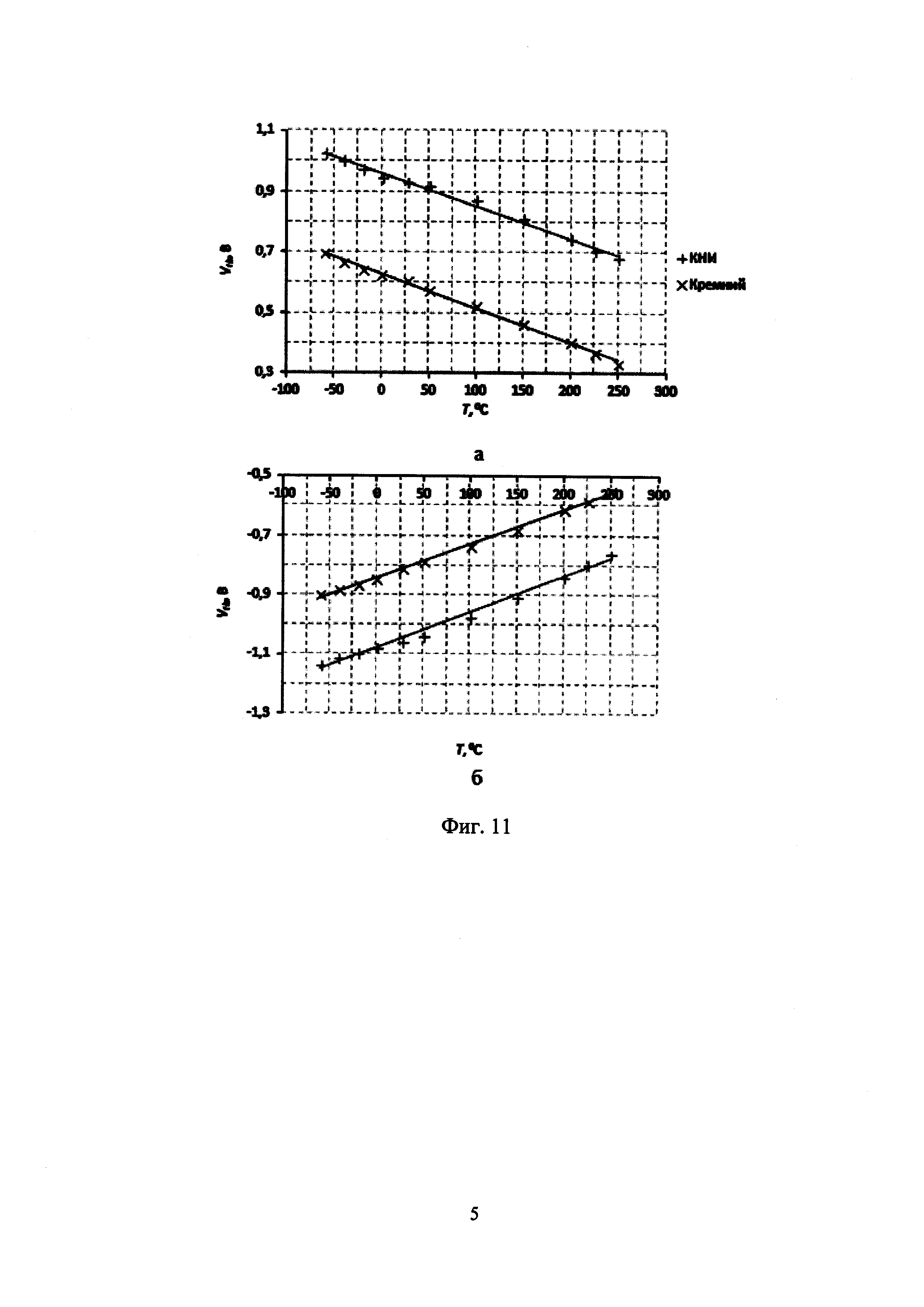

На Фиг. 11 приведены зависимости порогового напряжения Vth от температуры T для МОП-транзисторов с напряжением питания в 5 В. На Фиг. 11а - зависимости для n-канальных МОП-транзисторов; на Фиг. 11б - зависимости для р-канальных МОП-транзисторов.

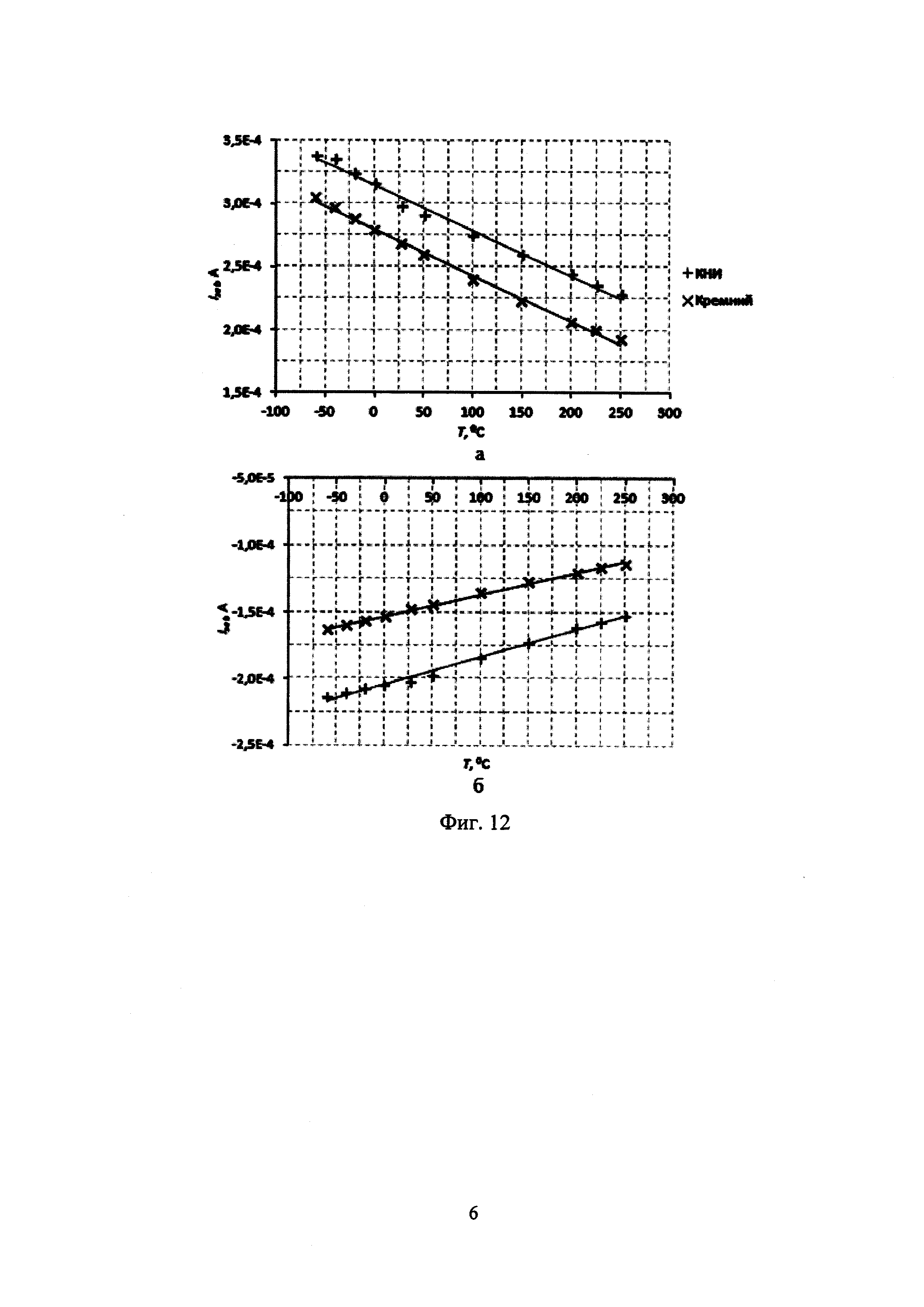

На Фиг. 12 приведены зависимости тока насыщения Isat от температуры Т для МОП-транзисторов с напряжением питания в 5 В. На Фиг. 12а - зависимости для n-канальных МОП-транзисторов; на Фиг. 12б - зависимости для р-канальных МОП-транзисторов.

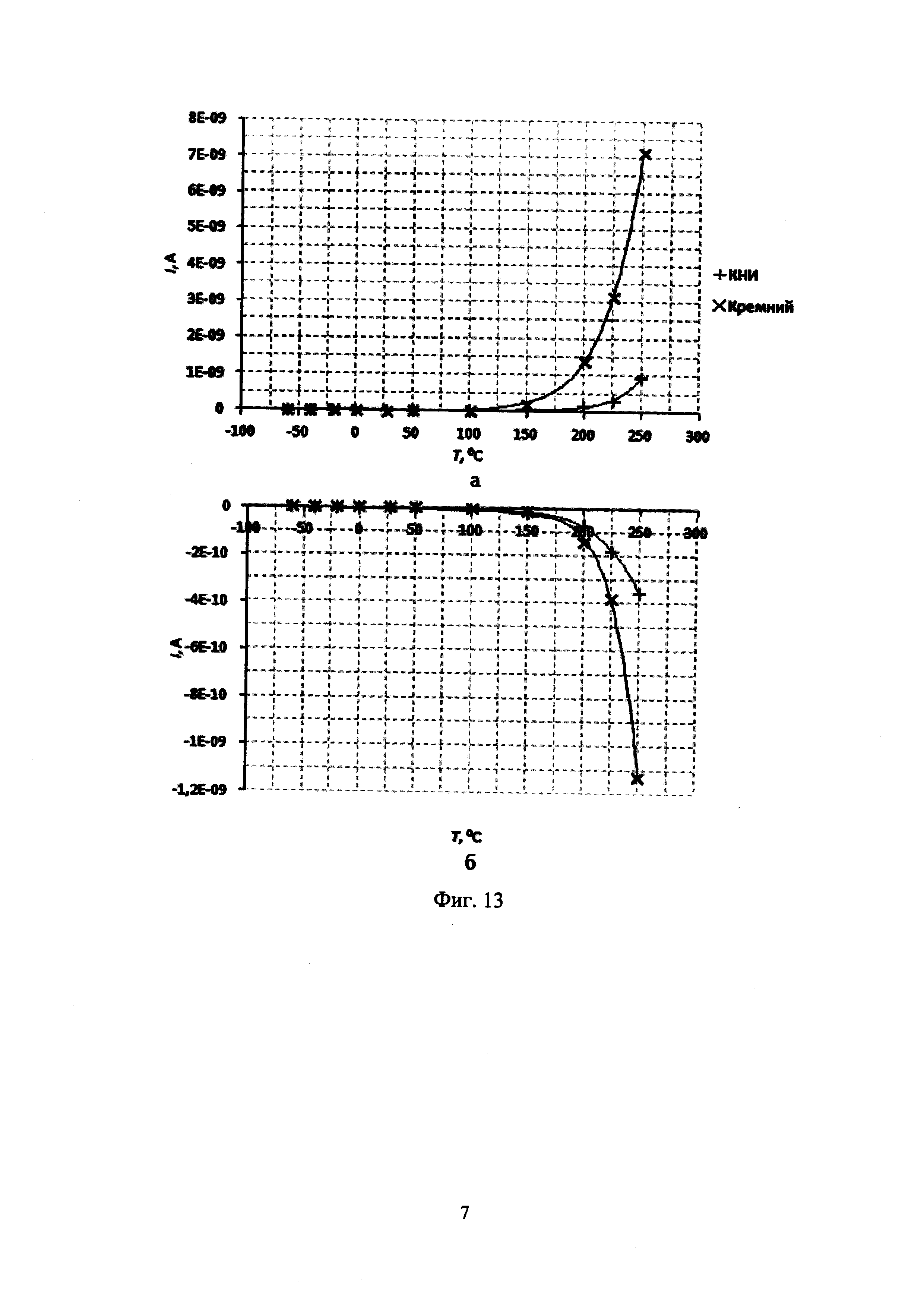

На Фиг. 13 приведены зависимости тока утечки I от температуры T для МОП-транзисторов с напряжением питания в 5 В. На Фиг 13а - зависимости для n-канальных МОП-транзисторов; на Фиг. 13б - зависимости для р-канальных МОП-транзисторов.

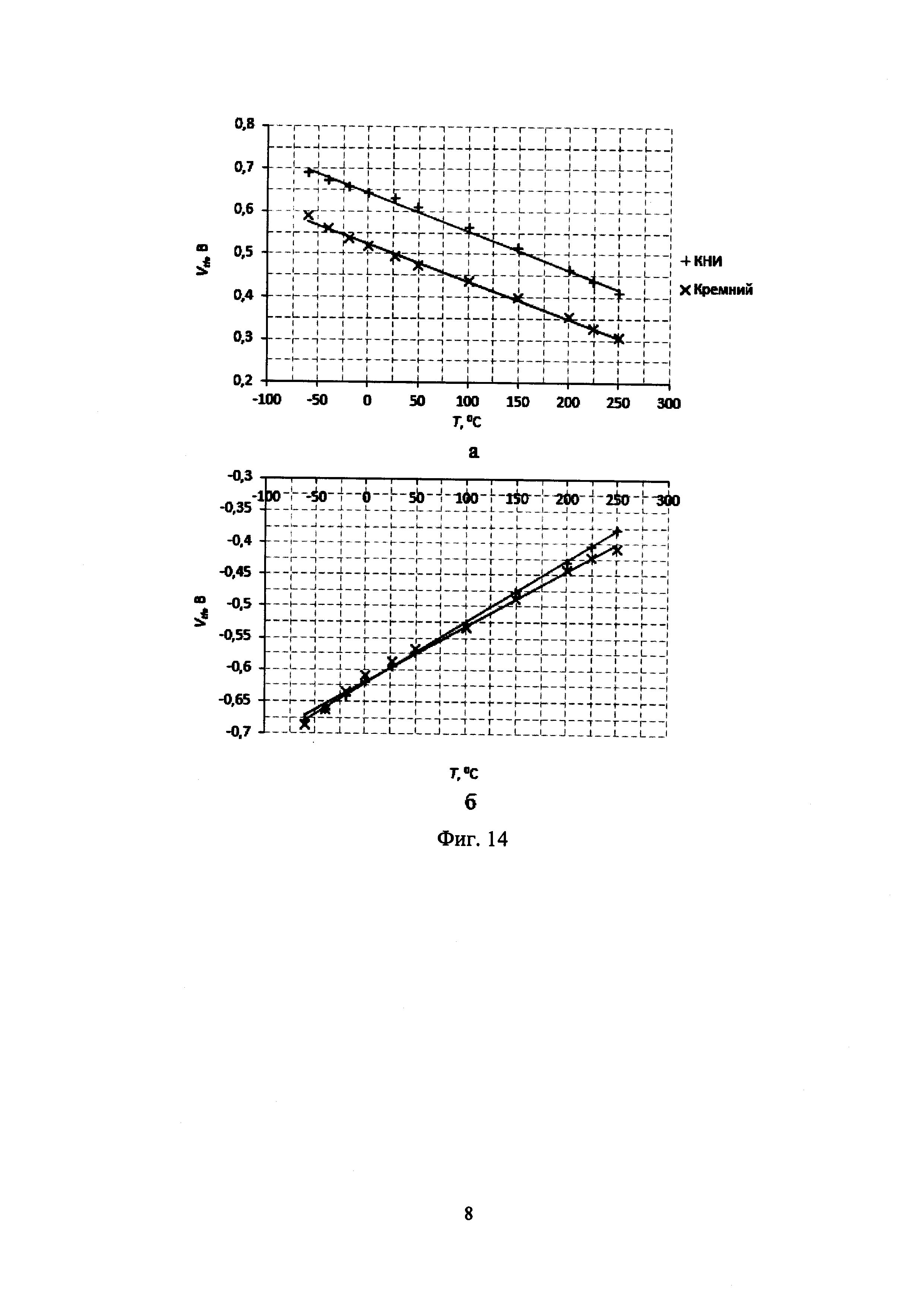

На Фиг. 14 приведены зависимости порогового напряжения Vth от температуры Т для МОП-транзисторов с напряжением питания в 1,8 В. На Фиг. 14а - зависимости для n-канальных МОП-транзисторов; на Фиг. 14б - зависимости для р-канальных МОП-транзисторов.

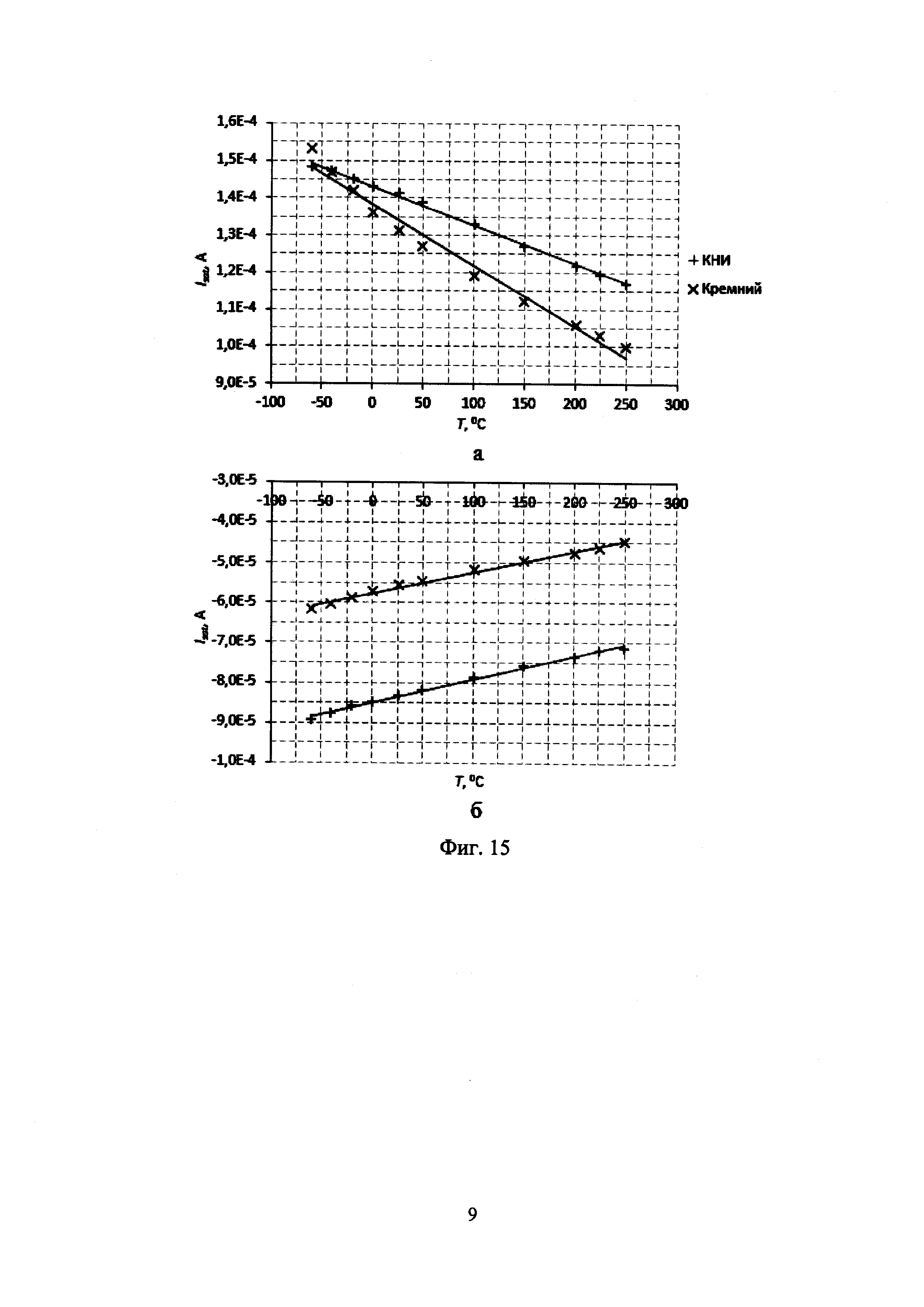

На Фиг. 15 приведены зависимости тока насыщения Isat от температуры Т для МОП-транзисторов с напряжением питания в 1,8 В. На Фиг. 15а - зависимости для n-канальных МОП-транзисторов; на Фиг. 15б - зависимости для р-канальных МОП-транзисторов.

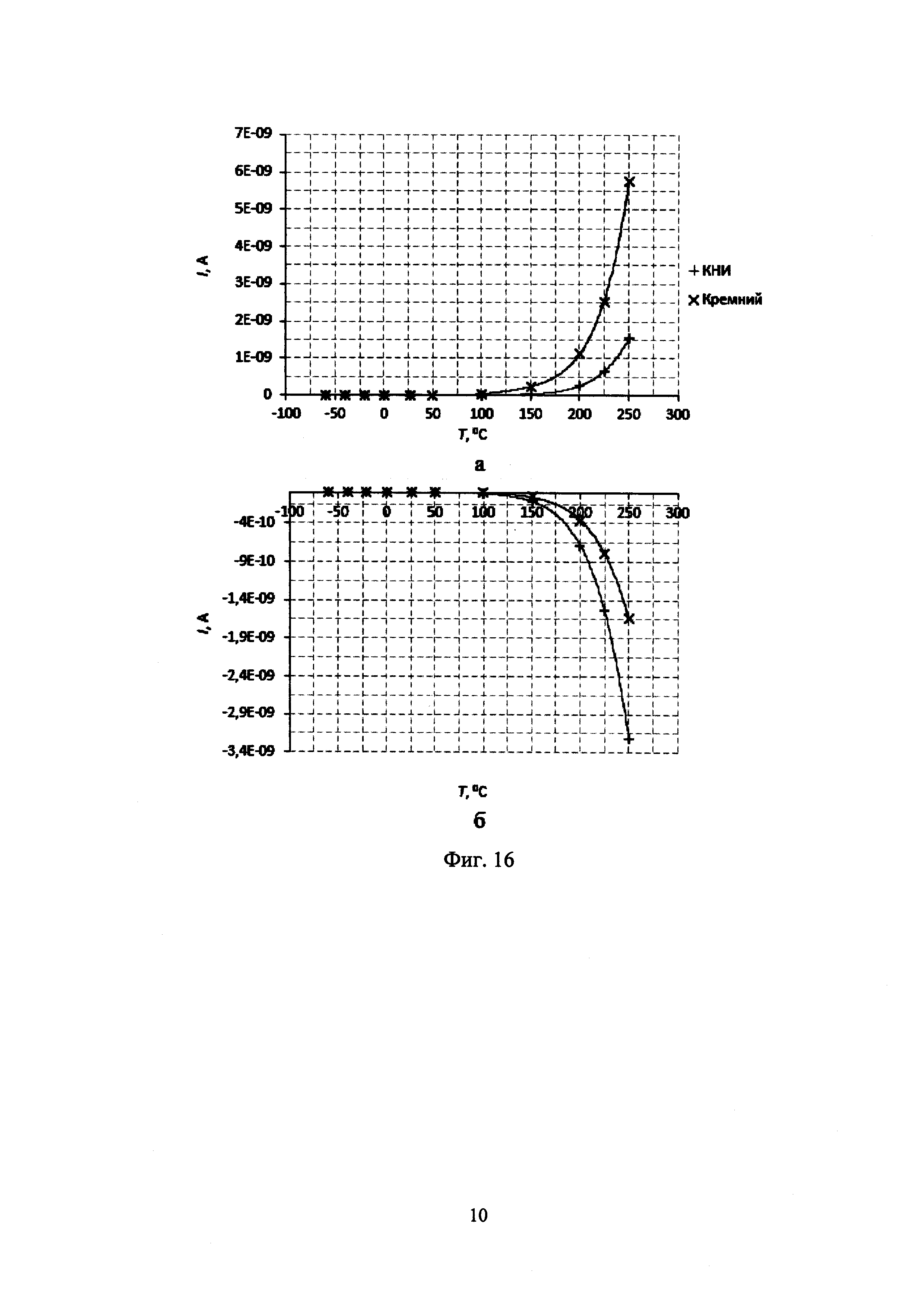

На Фиг. 16 приведены зависимости тока утечки I от температуры T для МОП-транзисторов с напряжением питания в 1,8 В. На Фиг 16а - зависимости для n-канальных МОП-транзисторов; на Фиг. 16б - зависимости для р-канальных МОП-транзисторов.

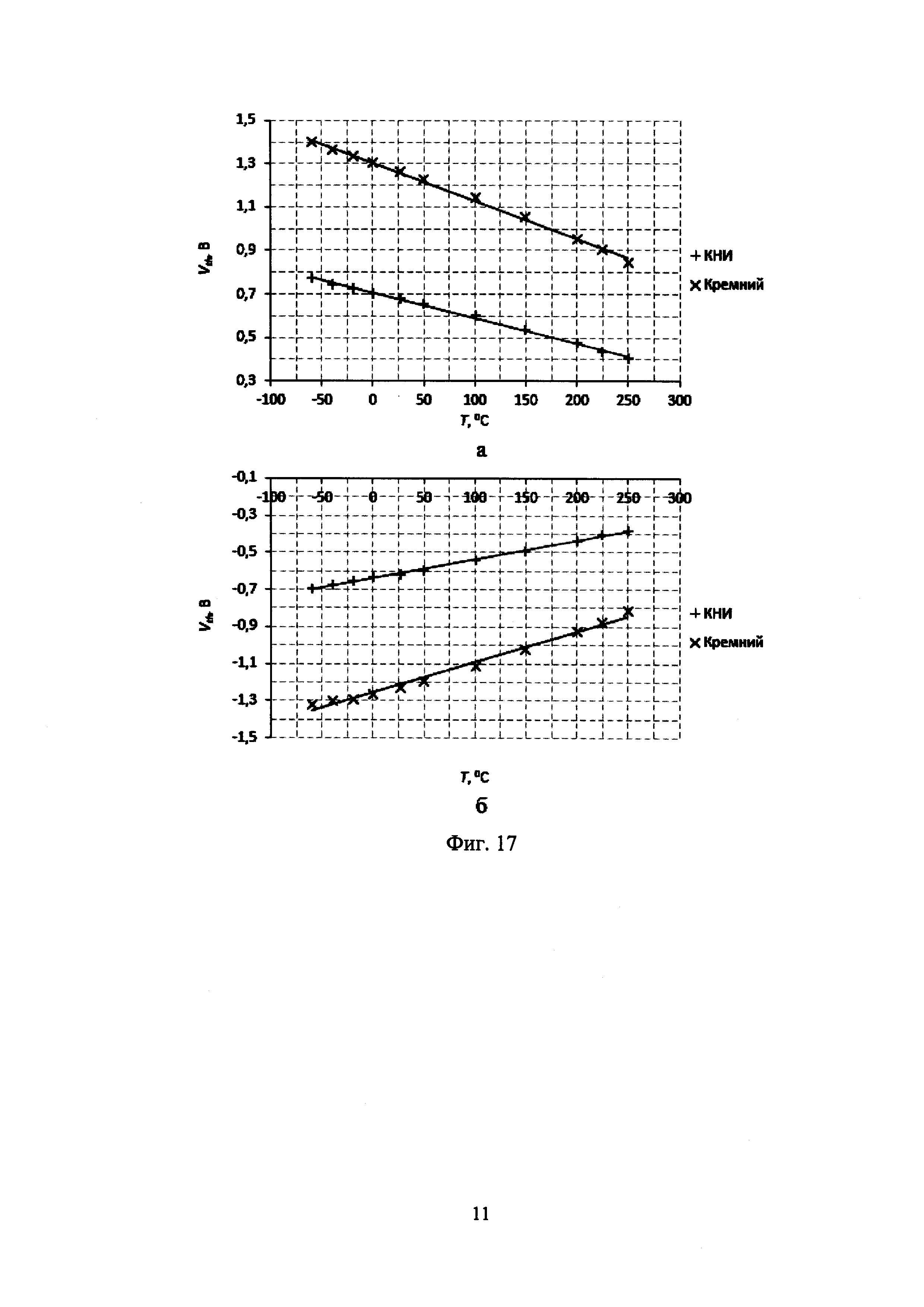

На Фиг. 17 приведены зависимости порогового напряжения Vth от температуры Т для МОП-транзисторов с напряжением питания в 3,3В. На Фиг. 17а - зависимости для n-канальных МОП-транзисторов; На Фиг. 17б - зависимости для р-канальных МОП-транзисторов.

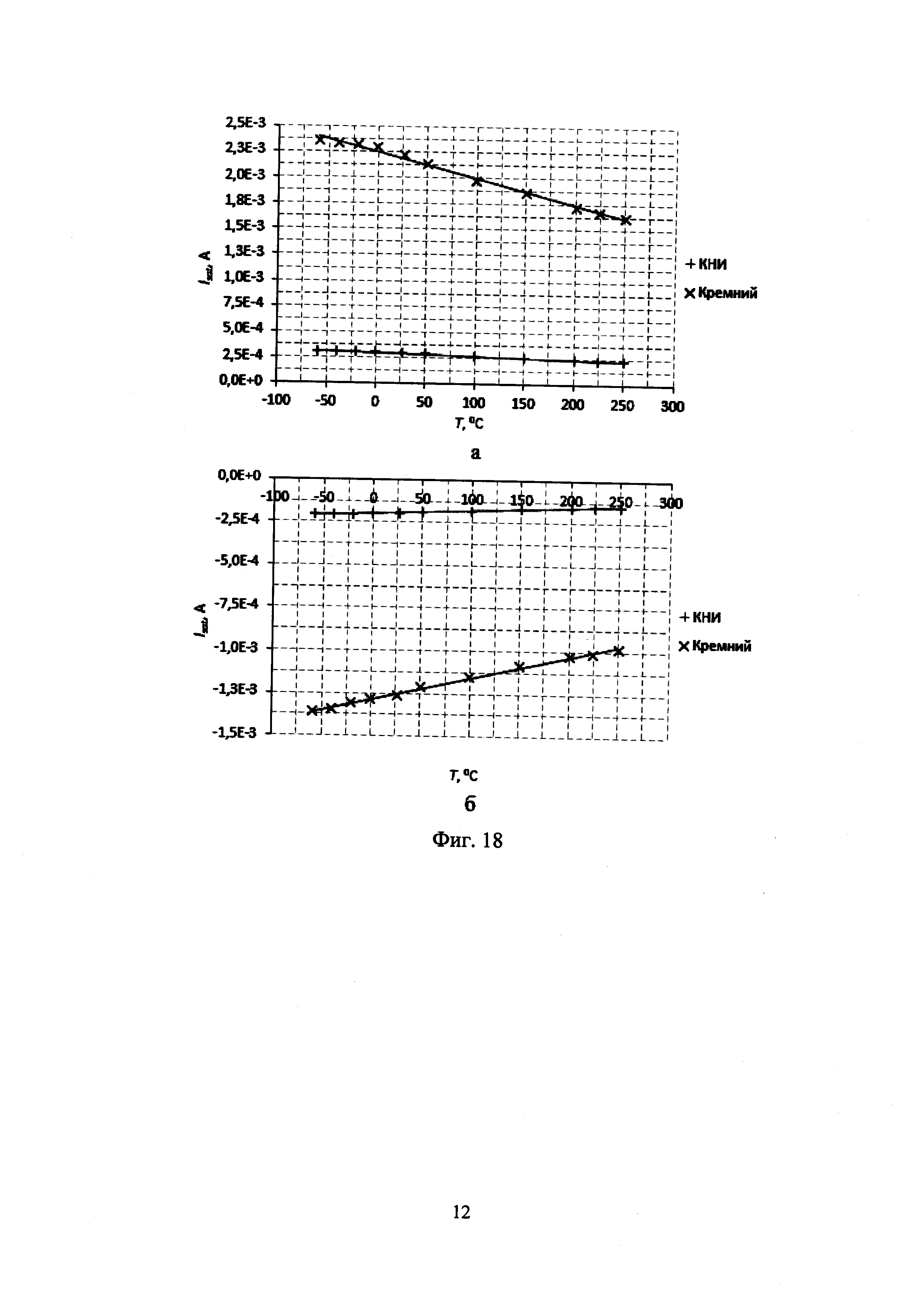

На Фиг. 18 приведены зависимости тока насыщения Isat от температуры Т для МОП-транзисторов с напряжением питания в 3,3 В. На Фиг. 18а - зависимости для n-канальных МОП-транзисторов; на Фиг. 18б - зависимости для р-канальных МОП-транзисторов.

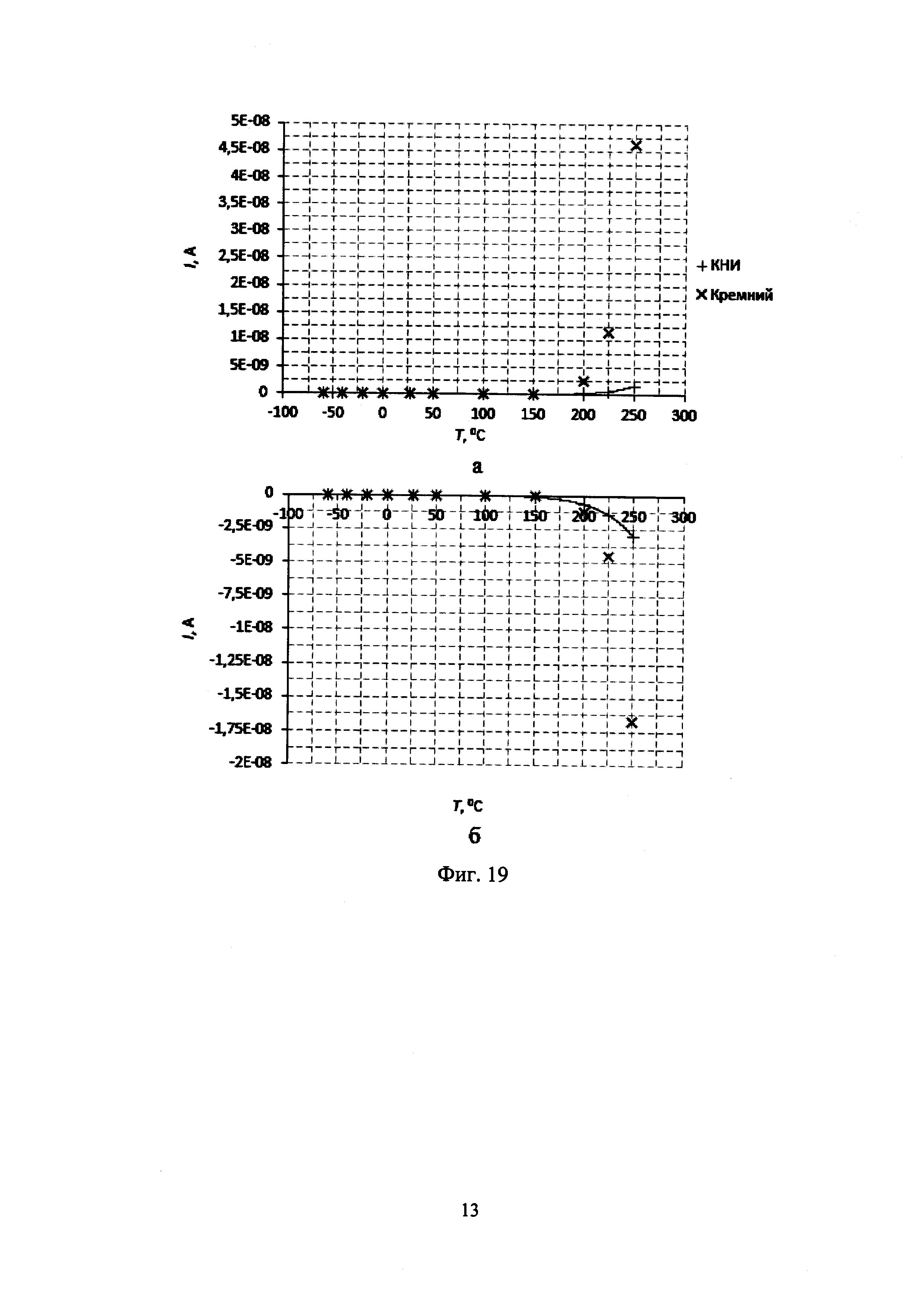

На Фиг. 19 приведены зависимости тока утечки I от температуры T для МОП-транзисторов с напряжением питания в 3,3 В. На Фиг 19а - зависимости для n-канальных МОП-транзисторов; на Фиг. 19б - зависимости для р-канальных МОП-транзисторов.

ОСУЩЕСТВЛЕНИЕ ИЗОБРЕТЕНИЯ

Способ изготовления высокотемпературных КМОП КНИ интегральных схем, в котором, в отличие от способов № US 6087235 А и № US 5893729 «Method of making SOI circuit for higher temperature and higher voltage applications» [3] обеспечивается:

- физическое сопряжение областей мелкой щелевой изоляции STI и скрытой изоляции BOX;

- физическое сопряжение областей кармана, областей стока и истока с верхней границей слоя BOX;

- причем, для областей карманов МОП-транзисторов дозы ионов подобраны таким образом, чтобы обеспечить физическое сопряжение областей карманов и BOX и уменьшить количество дефектов в конечной структуре транзитора;

- операция ионной имплантации в области стоков и истоков МОП-транзисторов n-типа осуществляется в следующем режиме: доза ионов мышьяка составляет от 2×1015 до 3×1015 см-2, энергия пучка - от 63 до 77 кэВ, а для областей стоков и истоков МОП-транзисторов р-типа доза ионов бора составляет от 2,8×1015 до 4,2×1015 см-2, энергия пучка - от 6 до 8 кэВ.

Предлагаемое изобретение реализуется следующим образом. За исходную структуру принимается пластина КНИ, выполненная методом Smart-Cut US 5374564 A «Process for the production of thin semiconductor material films» [5]. На поверхности пластины после термического окисления в атмосфере кислорода осажден из газовой фазы слой жертвенного нитрида кремния (Фиг. 4).

Далее на пластину наносится фоторезист и производится его экспонирование. Впоследствии методом анизотропного плазмохимического травления вытравливаются канавки STI в приборном слое кремния до поверхности скрытого диэлектрика. При проведении операции плазмохимического травления маски фоторезист частично стравливается; остатки фоторезиста удаляются жидкостным способом после плазмохимического травления (Фиг. 5). После удаления фоторезиста осуществляются термическое окисление вытравленных канавок STI и их последующее заполнение нелегированным диоксидом кремния путем осаждения в высокоплотной плазме (Фиг. 6). Затем поверх осажденного слоя нелегированного диоксида кремния осуществляется осаждение тетраэтилортосиликата из газовой фазы (CVD) (Фиг. 7). После осаждения тетраэтилортосиликата производят отжиг пластины для компенсации образовавшихся воздушных каверн в осажденных слоях. Далее методом анизотропного плазмохимического травления осуществляется травление сформированных оксидных пленок до уровня схематически показанного на Фиг. 8, а после удаления остатков фоторезиста жидкостным способом осуществляется химико-механическая полировка оставшегося после травления слоя диоксида кремния до уровня слоя жертвенного нитрида кремния (Фиг. 9). Впоследствии осуществляется жидкостное травление слоя жертвенного нитрида кремния с лицевой и обратной сторон пластины одновременно. После проведения стандартных операций по выращиванию на структуре, показанной на Фиг. 10, жертвенного окисла на пластину на пластину наносится фоторезист и производится его экспонирование согласно фотошаблонам для n-канальных МОП-транзисторов с длиной канала 0,5, 0,32 или 0,18 мкм. Далее последовательно проводят операции ионной имплантации фосфора, а затем мышьяка в области карманов изготавливаемых МОП-транзисторов. После осуществления имплантации фоторезист удаляют и производят нанесение свежего фоторезиста для экспонирования согласно фотошаблонам для р-канальных МОП-транзисторов с длиной канала 0,5, 0,32 или 0,18 мкм. Далее последовательно проводят операции ионной имплантации бора, а затем дифторида бора в области карманов изготавливаемых МОП-транзисторов. При этом, как для n-канальных так и для р-канальных МОП-транзисторов дозы ионов и энергии пучка выбирают такими, чтобы обеспечить проникновение примеси в весь объем кремния до верхней границы слоя BOX и сформировать карман МОП-транзистора во всем пространстве приборного слоя кремния, ограниченном областями диэлектрической изоляции BOX и STI. Впоследствии производится удаление фоторезиста и осуществляется термический отжиг пластины для активации примеси. Далее осуществляют стандартные операции по формированию поликремниевых затворов МОП-транзисторов и защитных слоев. После окончания формирования поликремниевых затворов МОП-транзисторов и сопутствующих операций на пластину наносится фоторезист и производится его экспонирование по фотошаблону для формирования областей стоков и истоков n-канальных МОП-транзисторов. Затем осуществляют дубление фоторезиста ультрафиолетовым излучением. После дубления производится ионная имплантация мышьяка в области стоков и истоков изготавливаемых МОП-транзиторов. Далее фоторезист удаляется и проводятся аналогичные операции экспонирования, дубления фоторезиста ультрафиолетом и ионной имплантации бора для формирования областей стока и истока р-канальных МОП-транзиторов. При этом, как для n-канальных так и для р-канальных МОП-транзисторов дозы ионов и энергии пучка выбирают такими, чтобы обеспечить физическое сопряжение областей стоков и истоков изготавливаемых МОП-транзиторов с верхней границей слоя BOX. После операций ионной имплантации в области стоков и истоков МОП-транзисторов осуществляют высокотемпературный отжиг пластины, в ходе которого активирутются имплантируемые примеси. Далее, пластина считается подготовленной для проведения последующих операций по формированию структур МОП-транзисторов, аналогичных операциям, применяемым в существующем уровне техники до получения структуры, схематически изображенной на Фиг. 2.

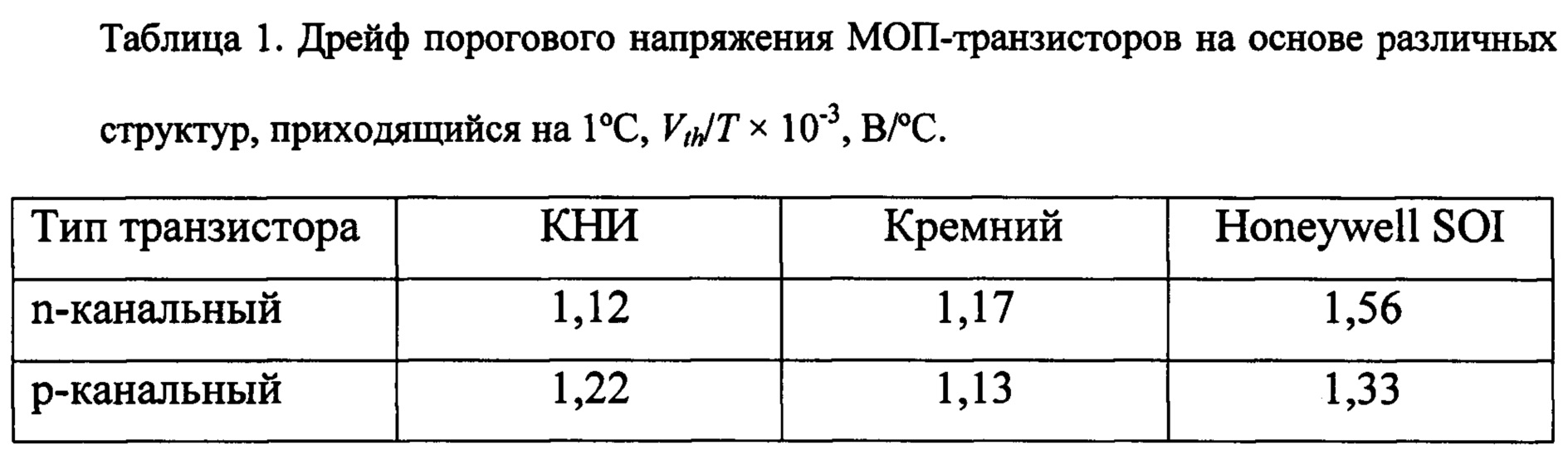

За счет указанных изменений в технологическом маршруте изготовления интегрального МОП-транзистора, выполненного на основе кремниевой подложки со скрытым диэлектриком (КНИ), предлагаемый способ является более предпочтительным при изготовлении интегральных схем, рассчитанных на максимальную рабочую температуру в 250°С, в сравнении со способом № US 6087235 А и № US 5893729 «Method of making SOI circuit for higher temperature and higher voltage applications» [3], изготовления МОП-транзисторов. Это подтверждается результатами сравнительных измерений транзисторных структур с одинаковыми геометрическими размерами и топологическим исполнением на основе объемного кремния и структур КНИ в диапазоне температур от минус 60 до 250°С. Так, на Фиг. 11 приведены зависимости порогового напряжения МОП-транзисторов от температуры. Согласно зависимостям для n-канальных транзисторов (Фиг. 11а) пороговое КНИ МОП-транзистора составляет примерно 1 В при температуре минус 60°С и 0,7 В при Т=250°С. Аналогичные значения для МОП-транзистора на объемном кремнии равны 0,7 и 0,3 В соответственно. На Фиг. 11б приведены значения пороговых напряжений при различных температурах для р-канальных МОП-транзисторов. Пороговое напряжение транзистора на основе КНИ при минимальной и максимальной температурах составляет минус 1,2 и минус 0,8 В соответственно. Аналогичные значения для транзистора на объемном кремнии составляют приблизительно минус 0,9 и минус 0,5 В. Учитывая линейный характер представленных зависимостей, приведем значения дрейфа порогового напряжения на 1°С для исследуемых МОП-транзисторов (табл. 1). Также в таблице 1 приведены аналогичные показатели для КНИ МОП-транзисторов, разработанных фирмой Honeywell в рамках проекта Energy Deep Trek [6]. Согласно таблице 1 дрейф порогового напряжения n-канального КНИ МОП-транзистора, чем у сопоставляемых транзисторов на объемном кремнии и транзистора Honeywell. Аналогичный показатель для р-канального КНИ МОП-транзистора меньше удельного порогового напряжения аналога Honeywell. Разница между показателями КНИ исследуемых МОП-транзисторов и транзисторов фирмы Honeywell объясняется обратной зависимостью дрейфа порогового напряжения от концентрации легирующей примеси в области сток-исток транзистора. Так как минимальная технологическая норма КНИ МОП-транзисторов фирмы Honeywell равна 0,8 мкм (против 0,5 - у исследуемых транзисторов), то удельная концентрация легирующей примеси меньше, чем у исследуемого транзистора, что определяет большие значения дрейфа порогового напряжения, приходящиеся на 1°С.

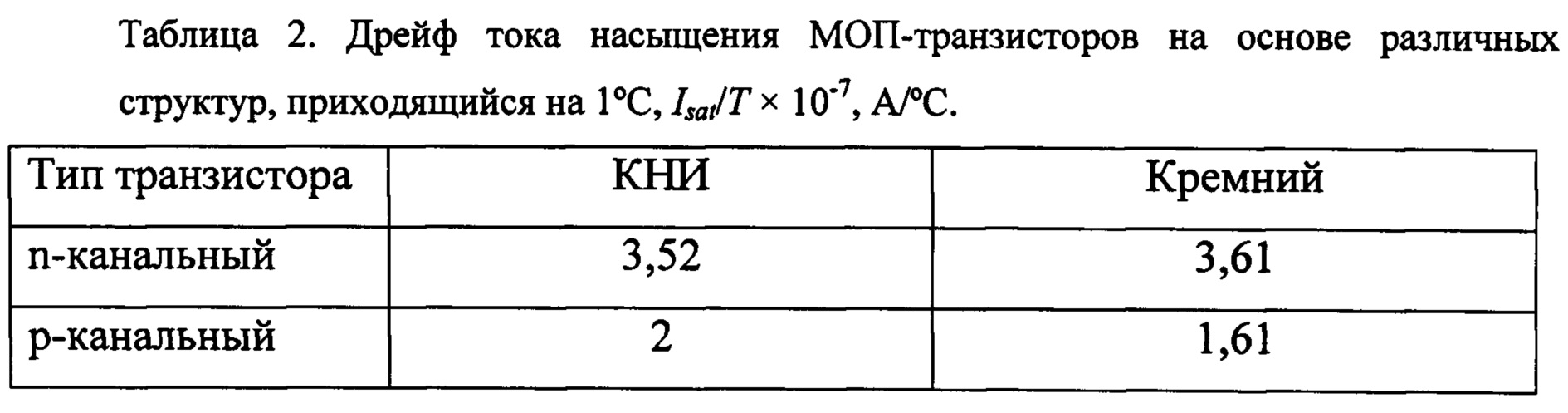

Зависимости токов насыщения МОП-транзисторов при различных температурах показаны на Фиг. 12а и 12б. Так как ток насыщения МОП-транзистора имеет линейную зависимость от температуры [1], то, как и в случае предыдущей зависимости, приведем значения дрейфа токов насыщения МОП-транзисторов на 1°С (табл. 2). Согласно сопоставлению, значения дрейфа тока насыщения для однотипных (по типу проводимости) МОП-транзисторов можно считать приблизительно одинаковыми.

Аналогичные результаты получены и для МОП-транзисторов аналогичных типов с рабочими напряжениями 1,8 (Фиг. 14-16) и 3,3 В (Фиг. 17-19).

При этом на всем диапазоне температур значения токов насыщения КНИ МОП-транзисторов отличаются от значений токов насыщения МОП-транзисторов на объемном кремнии примерно на 0,4..0,5×10-4 А. Зависимости токов утечки транзисторов от температуры приведены на Фиг. 13. Как в случае n-канальных (Фиг. 13а), так и в случае р-канальных (Фиг. 13б) МОП-транзисторов ток утечки достигает экстремальных значений при температуре 250°С. Для всех четырех исследуемых транзисторов характерно экспоненциальное изменение тока утечки с изменением температуры, причем при температурах >125°С отмечено более интенсивное изменение токов утечки у МОП-транзисторов на объемном кремнии. Так, при максимальной температуре токи утечки составляют 7,16×10-9 А и минус 1,13×10-9 А для n- и р-канального транзистора соответственно, что в 7 и 3 раза превышает аналогичные показатели КНИ МОП-транзисторов.

ИСТОЧНИКИ ИНФОРМАЦИИ

[1] Зи, С. Физика полупроводниковых приборов: В 2-х книгах. Кн. 2. / С. Зи; пер. с англ. - 2-е перераб. и доп. изд. - М.: Мир, 1984. - 456 с.

[2] 0,18 μm Process Family: ХТ018. 0.18 Micron HV SOI CMOS Technology//XT018 Data Sheet. - X-FAB Semiconductor Foundries AG, 2014. - 11 p.

[3] Roger L. Roisen METHOD OF MAKING SOI CIRCUIT FOR HIGHER TEMPERATURE AND HIGHER VOLTAGE APPLICATIONS/ Invention patent US 5893729. Application number: US 08/671,100. Date of publication: 13.04.1999. Classification: H01L 21/00.

[4] Shmidt, A. Analog Circuit Design in PD-SOI CMOS Technology for High Temperatures up to 400°C using Reverse Body Biasing (RBB) / A. Shmidt. - Duisburg: University of Duisburg-Essen, 2014. - 223 p.

[5] Bruel M. PROCESS FOR THE PRODUCTION OF THIN SEMICONDUCTOR MATERIAL FILMS/ Invention patent US 5374564 (A). Application number: US 19920945001 19920915. Date of publication: 20.12.1994. Classification: B28D 5/00, G01L 9/00, H01L 21/02, H01L 21/027, H01L 21/205, H01L 21/265, H01L 21/762, H01L 27/12, H01L 31/04, H01L 33/00, H01L 21/265.

[6] Ohme В., Johnson M., Hansen J. et al. Updated Results from Deep Trek High Temperature Electronics Development Programs. Plymouth: Honeywell International Inc., 2007. 8 p.