Результат интеллектуальной деятельности: СПОСОБ ФОРМИРОВАНИЯ СИСТЕМЫ МНОГОУРОВНЕВОЙ МЕТАЛЛИЗАЦИИ НА ОСНОВЕ ВОЛЬФРАМА ДЛЯ ВЫСОКОТЕМПЕРАТУРНЫХ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ

Вид РИД

Изобретение

ОБЛАСТЬ ТЕХНИКИ

Заявленное изобретение относится к технологии изготовления полупроводниковых приборов и сверхбольших интегральных схем (СБИС) в части формирования многоуровневых металлических соединений.

УРОВЕНЬ ТЕХНИКИ

Известны способы изготовления системы металлизации, называемые термином Damascene, в которых в качестве материала горизонтальных и вертикальных проводников используется медь (патенты № US 7038320 В1, US 5801094, US 7538025). Данный способ предполагает вытравливание канавок в диэлектрическом слое с последующим нанесением барьерной пленки и зародышевого слоя металла на поверхность пластины, на стенки и дно канавок и нанесение металла электрохимическим способом на всю пластину, включая и внутреннюю полость канавок до полного заполнения канавок. С поверхности пластины слой металла и барьерная пленка удаляются химико-механической полировкой (ХМП).

Одним из частных применений указанного способа является изготовление системы металлизации высокотемпературных интегральных микросхем. Металлизация с использованием меди в качестве материала горизонтальных и вертикальных проводников применяется в высокотемпературных интегральных микросхемах различных производителей, в частности Honeywell [1], IBM [2] и XFAB [3]. За счет использования способа Damascene и меди обеспечивается относительная температурная устойчивость интегральных схем, но ее повышение не представляется возможным.

К причинам, препятствующим повышению температурной устойчивости системы металлизации, изготавливаемой способом № US 7038320 В1, относится наличие дефектообразующих операций травления межуровневого диэлектрика. Кроме того, разность коэффициентов температурного расширения межуровневого диэлектрика и меди в системе металлизации, выполняемой способом Damascene, составляет 16,05×10-6 °C-1, при этом аналогичный показатель для межуровневого диэлектрика и вольфрама - 3,75×10-6 °C-1. Сравнительно высокая разность коэффициентов температурного расширения межуровневого диэлектрика и меди является одним из показателей образования расслоений между различными материалами при высоких температурах.

К причинам, препятствующим повышению температурной устойчивости системы металлизации, изготавливаемой способом US 5801094, относится то, что в результате электрохимического осаждения меди в получаемом проводнике образуются пустоты, что приводит к разрыву проводника при повышении температуры. Кроме того, в технологическом маршруте формирования системы металлизации присутствуют дефектообразующие операции травления межуровневого диэлектрика, что, в конечном итоге, приводит к снижению надежности системы металлической разводки.

К причинам, препятствующим повышению температурной устойчивости системы металлизации, изготавливаемой способом US 7538025, относится то, что для меди, предлагаемой в качестве материала горизонтальных и вертикальных проводников, при повышении температуры окружающей среды характерно развитие явления электромиграции. Кроме того, разность коэффициентов температурного расширения межуровневого диэлектрика и меди в системе металлизации, выполняемой способом Damascene, составляет 16,05×10-6 °С-1, при этом аналогичный показатель для межуровневого диэлектрика и вольфрама - 3,75×10-6 °C-1. Сравнительно высокая разность коэффициентов температурного расширения межуровневого диэлектрика и меди является одним из показателей образования расслоений между различными материалами при высоких температурах.

Способом Damascene, наиболее близким по технической сущности предлагаемому изобретению, является способ [4], включающий операции нанесения на кремниевую подложку диэлектрического и металлического слоев, ХМП меди, фотолитографии с последующим травлением канавок в диэлектрике под заполнение медью, нанесения барьерных и зародышевых слоев, электрохимического осаждения меди, термообработки и ХМП меди до поверхности диэлектрика. Способ [4] принимается в качестве прототипа предлагаемого изобретения.

Данный способ, как и другие подобные, может применяться при формировании систем металлизации высокотемпературных интегральных микросхем. При этом в случае системы металлизации для высокотемпературных интегральных микросхем, выполненной согласно способу [4], имеют место дефектообразующие операции травления межуровневого диэлектрика и расслоения в системе металлизации из-за высокой разницы коэффициента температурного расширения между межуровневым диэлектриком и медью. Вследствие этого, системы металлизации высокотемпературных интегральных микросхем, выполненные согласно способу [4], менее устойчивы к воздействию высоких температур в сравнении с системами металлизации, изготавливаемыми предлагаемым способом.

РАСКРЫТИЕ ИЗОБРЕТЕНИЯ

Задачей, на решение которой направлено данное изобретение, является достижение технического результата, заключающегося в повышении устойчивости интегральных микросхем к воздействию высоких температур (свыше 125°C).

Поставленная задача решается за счет того, что способ формирования системы многоуровневой металлизации для высокотемпературных интегральных микросхем, включающий операции нанесения диэлектрических и металлических слоев, фотолитографию и травление канавок в этих слоях, нанесение барьерного и зародышевого слоев, нанесение слоя металла и его ХМП, отличается тем, что процесс формирования одного уровня металлической разводки включает следующую последовательность основных операций: на пластину кремния со сформированным транзисторным циклом наносится слой вольфрама для формирования горизонтальных проводников, проводится его ХМП и сквозное травления областей под заполнение проводящим барьерным слоем нитрида титана и диэлектриком, ХМП диэлектрика, нанесение барьерного слоя нитрида титана и слоя вольфрама для формирования вертикальных проводников, ХМП слоя вольфрама, сквозное травление областей под заполнение диэлектрическим барьерным слоем нитрида кремния и диэлектриком, ХМП диэлектрика с последующим покрытием полученной структуры проводящим барьерным слоем нитрида титана.

В предлагаемом способе изготовления системы металлизации, в отличие от способа Damascene, исключены дефектообразующие операции травления межуровневого диэлектрика. Вместо указанных операций производится нанесение слоя вольфрама на всю поверхность пластины кремния с предварительно сформированным транзисторным циклом, и последующим сквозным травлением этого слоя, и нанесением межуровневого диэлектрика в вытравленные области.

При этом коэффициент температурного расширения вольфрама близок к аналогичному значению для материала межуровневых диэлектриков, что позволяет при высоких температурах избежать расслоений не только между различными уровнями металлизации, но и между металлами и диэлектриками.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Предложенный способ поясняется чертежами.

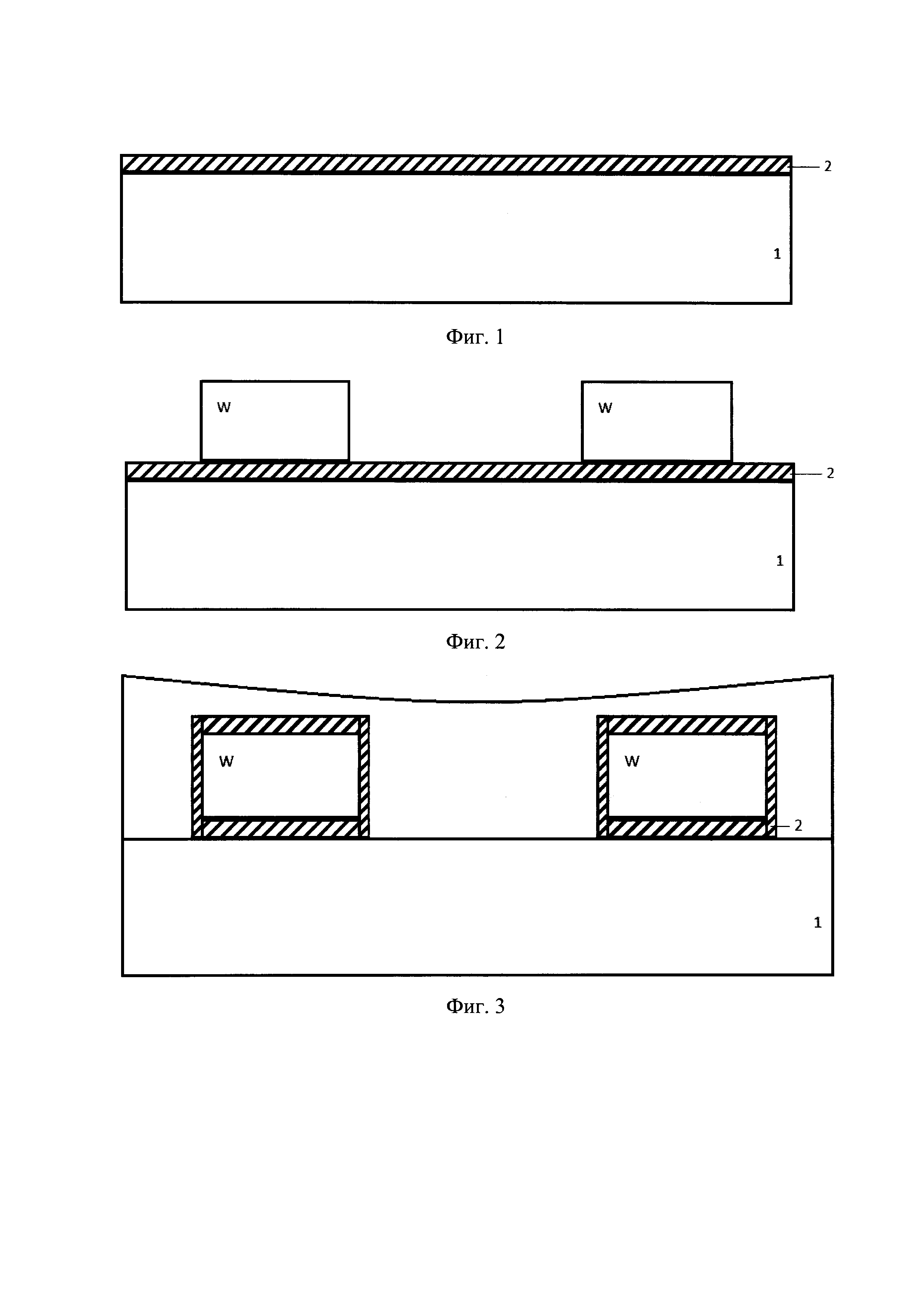

На Фиг. 1 изображена исходная структура подложки (1) с нанесенным проводящим барьерным слоем нитрида титана (2), подготовленная для формирования системы вольфрамовой металлизации.

На Фиг. 2 изображен результат проведения операций по формированию горизонтальных вольфрамовых проводников, включающих нанесение слоя вольфрама, его планаризацию и нанесение жесткой маской из нитрида титана (2). Через жесткую маску проведено сквозное травление слоя вольфрама и проводящего барьерного слоя нитрида титана.

На Фиг. 3 изображен вертикальный срез горизонтальных вольфрамовых проводников, покрытых проводящим барьерным слоем (2); поверх нанесен диэлектрик.

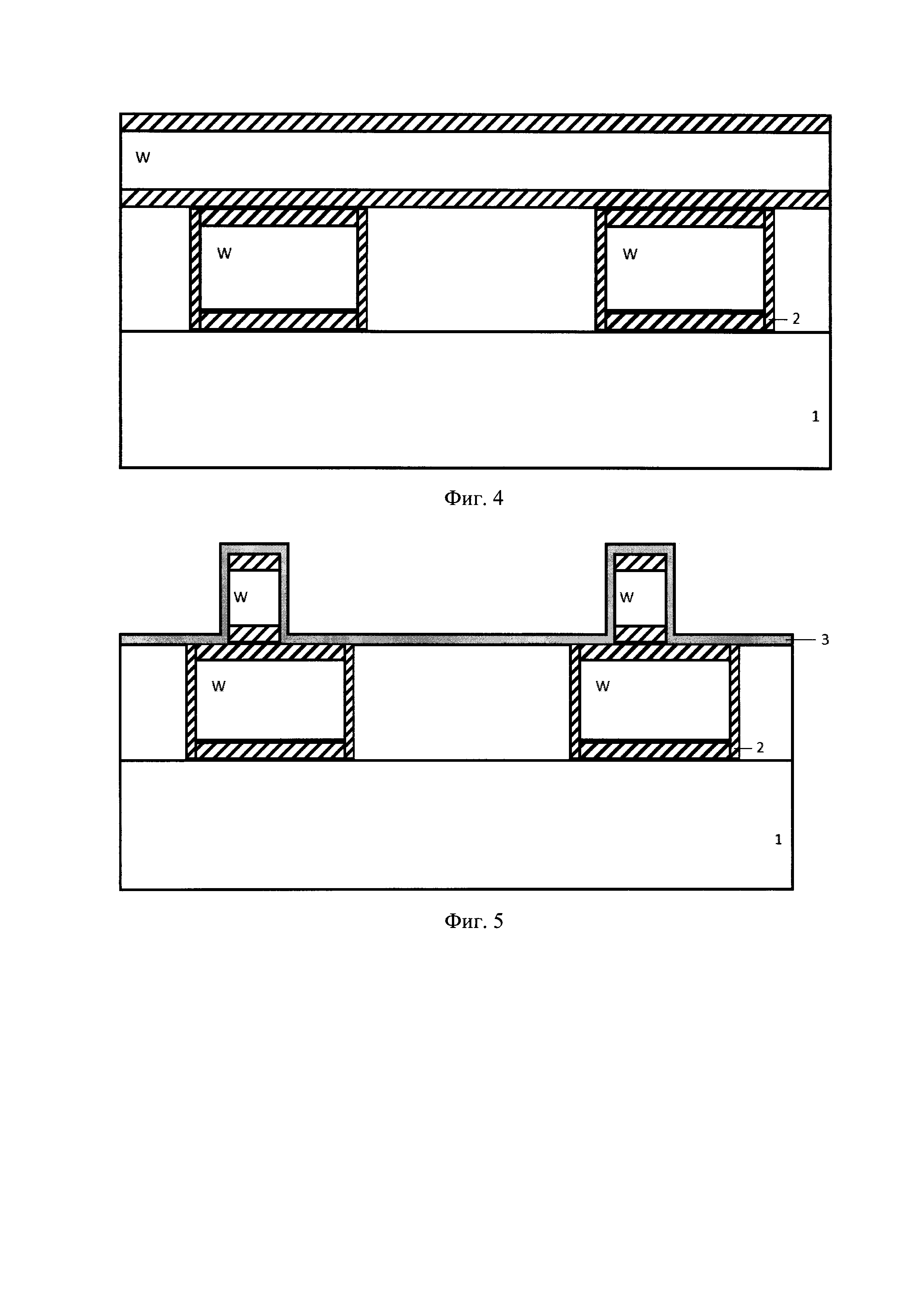

На Фиг. 4 поверх сформированного уровня горизонтальных вольфрамовых проводников нанесен слой вольфрама для последующего формирования вертикальных проводников, включающий помимо вольфрама проводящий барьерный слой нитрида титана (2) и жесткую маску (2).

На Фиг. 5 последовательно произведены травление вертикальных вольфрамовых проводников и нанесение диэлектрического барьерного слоя нитрида кремния (3).

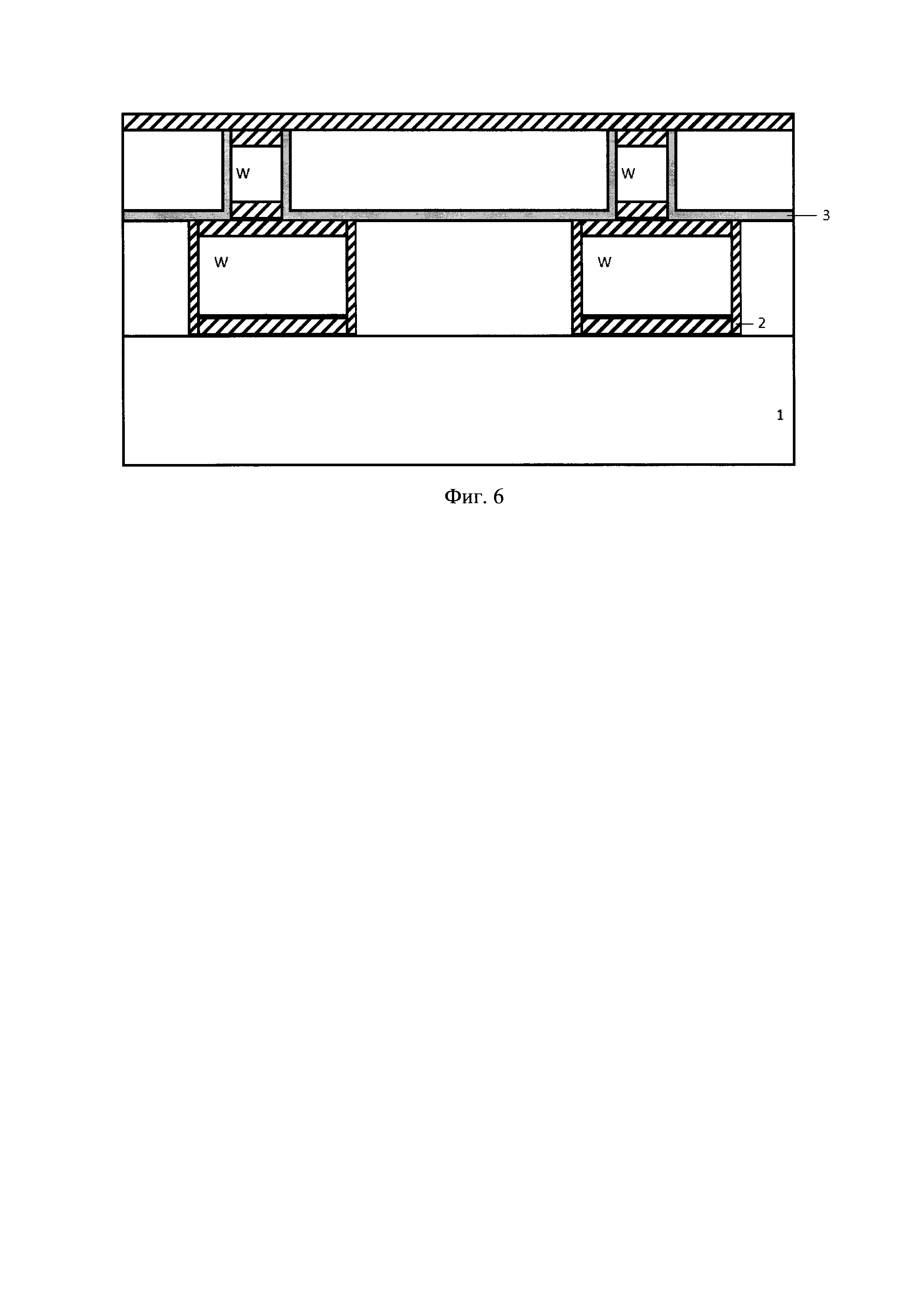

На Фиг. 6 последовательно произведены формирование диэлектрика, ХМП до уровня поверхности жесткой маски и нанесение проводящего барьерного слоя нитрида титана (2).

ОСУЩЕСТВЛЕНИЕ ИЗОБРЕТЕНИЯ

Способ формирования системы многоуровневой металлизации на основе вольфрама для высокотемпературных интегральных микросхем, в котором, в отличие от способа Damascene, исключены дефектообразующие операции травления межуровневого диэлектрика. Вместо указанных операций производится нанесение слоя вольфрама на всю поверхность пластины с последующим сквозным травлением этого слоя и нанесением межуровневого диэлектрика в вытравленные области. При этом коэффициент температурного расширения вольфрама близок к аналогичному значению для материала межуровневых диэлектриков, что позволяет при высоких температурах избежать расслоений не только между различными уровнями металлизации, но и между металлами и диэлектриками.

Предлагаемое изобретение реализуется следующим образом.

За исходную структуру принимается кремниевая пластина с частично сформированными структурами СБИС. Внешняя поверхность исходной структуры представляет собой слой межуровневого диэлектрика с протравленными переходными контактными окнами. На всю поверхность пластины нанесен проводящий барьерный слой нитрида титана, поверх которого проведено заполнение переходных контактных окон вольфрамом (Фиг. 1). Данная структура повторно покрыта проводящим барьерным слоем нитрида титана.

На внешнюю поверхность исходной структуры наносится слой вольфрама и проводится его ХМП. Поверх вольфрама наносится проводящая жесткая маска из нитрида титана. Далее на пластину наносится фоторезист и производится его экспонирование. Впоследствии методом плазмохимического травления проводится вскрытие жесткой маски до поверхности вольфрама. При проведении операции плазмохимического травления жесткой маски фоторезист частично стравливается; остатки фоторезиста удаляются жидкостным способом после плазмохимического травления. Затем через вскрытую жесткую маску вытравливается слой вольфрама до поверхности нижележащего проводящего барьерного слоя методом реактивного ионного травления (Фиг. 2). Затем путем плазмохимического травления с подачей обратного потенциала на подложку проводящий барьерный слой нитрида титана вытравливается до поверхности нижележащего диэлектрика. В процессе данной операции происходит распыление нитрида титана на боковые поверхности вольфрамовых горизонтальных проводников, что способствует предотвращению диффузии вольфрама при последующих технологических операциях. Далее на пластину со сформированными вольфрамовыми горизонтальными проводниками способом химического осаждения из газовой фазы (CVD) формируется диэлектрик (Фиг. 3) и проводится химико-механическая полировка пластины до поверхности жесткой маски. Далее на пластину наносится проводящий барьерный слой нитрида титана и наносится слой вольфрама, который планаризуется. Поверх вольфрама наносится проводящая жесткая маска из нитрида титана (Фиг. 4). Далее на пластину наносится фоторезист и проводится его экспонирование. Впоследствии методом плазмохимического травления проводится вскрытие жесткой маски до поверхности вольфрама. При проведении операции плазмохимического травления жесткой маски фоторезист частично стравливается; остатки фоторезиста удаляются жидкостным способом после плазмохимического травления. Затем через вскрытую жесткую маску вытравливается слой вольфрама до поверхности нижележащего проводящего барьерного слоя методом реактивного ионного травления. Далее на сформированные вольфрамовые вертикальные проводники методом CVD наносится диэлектрический барьерный слой нитрида кремния (Фиг. 5). После этого на пластину со сформированными вертикальными вольфрамовыми проводниками способом CVD наносится диэлектрик и проводится химико-механическая полировка пластины до поверхности вольфрама. Затем пластина покрывается проводящим барьерным слоем нитрида титана (Фиг. 6). Последующие слои системы металлизации на основе вольфрама в качестве материала горизонтальных и вертикальных межуровневых проводников получаются путем кратного повторения приведенной последовательности технологических операций.

За счет указанных изменений в технологическом маршруте формирования системы металлизации на основе вольфрама в качестве материала металлических шин и вертикальных контактных переходов предлагаемый способ является более предпочтительным в сравнении со способом Damascene изготовления системы медной металлизации.

ИСТОЧНИКИ ИНФОРМАЦИИ

1. Updated Results from Deep Trek High Temperature Electronics Development Programs / B. Ohme [et al.]. - Plymouth: Honeywell International Inc., 2007. - 8 p.

2. Foundry technologies 180-nm CMOS, RF CMOS and SiGe BiCMOS // Data Sheet. - IBM Microelectronics Division. - 4 p.

3. 0,18 μm Process Family: XT018. 0.18 Micron HV SOI CMOS Technology // XT018 Data Sheet. - X-FAB Semiconductor Foundries AG, 2014. - 11 p.

4. Патент № US 7038320 B1, «Single damascene integration scheme for preventing copper contamination of dielectric layer».

Способ формирования системы многоуровневой металлизации для высокотемпературных интегральных микросхем, включающий операции нанесения диэлектрических и металлических слоев, фотолитографию и травление канавок в этих слоях, нанесение барьерного и зародышевого слоев, нанесение слоя металла и его ХМП, отличающийся тем, что процесс формирования одного уровня металлической разводки включает следующую последовательность основных операций: на пластину кремния со сформированным транзисторным циклом наносится слой вольфрама для формирования горизонтальных проводников, проводится его ХМП и сквозное травления областей под заполнение проводящим барьерным слоем нитрида титана и диэлектриком, ХМП диэлектрика, нанесение барьерного слоя нитрида титана и слоя вольфрама для формирования вертикальных проводников, ХМП слоя вольфрама, сквозное травление областей под заполнение диэлектрическим барьерным слоем нитрида кремния и диэлектриком, ХМП диэлектрика с последующим покрытием полученной структуры проводящим барьерным слоем нитрида титана.