Результат интеллектуальной деятельности: Однотранзисторный логический вентиль И с архитектурой без перекрытия областей затвор-сток/исток

Вид РИД

Изобретение

Изобретение относится к области микро- и наноэлектронике, а именно к полупроводниковым прибором, в частности к конструкции логического вентиля, реализующего операцию конъюнкции, и может быть использовано при создании цифровых интегральных схем с элементами субмикронных и нанометровых размеров.

На современном этапе развития микроэлектроники решение проблемы дальнейшего масштабирования параметров элементов микросхем ищется с помощью альтернативных транзисторных структур, о чем свидетельствуют многочисленные доклады представителей крупнейших корпораций Intel, IBM, AMD, Hitachi на ведущих Международных конференциях по электронным приборам. Опираясь на последние достижения, формируется новый подход масштабирования - функционализация элементной базы [1].

Перспективным кандидатом для реализации логических операций логического вентиля на основе одной мультизатворной транзисторной структуры является известный однотранзисторный логический вентиль И на структуре «кремний на изоляторе» с архитектурой без перекрытия затвор-сток/исток с тонкой нелегированной рабочей областью транзистора, известная как «gate-underlap design». Данная архитектура является прототипом и включает вытянутые в продольном направлении вдоль рабочей области транзистора области стока и истока, один фронтальный подзатворный и один погруженный окислы, один фронтальный и один обратный затворы и характеризуется большим расстоянием между краем затвора и положением максимального уровня концентрации легирующей примеси в области стока/истока [2].

Недостатком известного логического вентиля И является низкая степень интеграции логических функций на кристалле и достаточно высокий уровень потребляемой мощности.

Техническая проблема, решаемая патентуемым изобретением, является увеличение плотности интеграции за счет объединения трех логических сигналов на одной транзисторной структуре, что позволяет снизить конструктивно топологическую сложность цифровых схем, и снижение уровня потребляемой мощности за счет применения германия в качестве основного материала транзистора, который обладает значительно большей подвижностью носителей заряда по сравнению с кремнием.

Указанная проблеме решается однотранзисторным логическим вентилем И с архитектурой без перекрытия областей затвор-сток/исток, включающим фронтальный и обратный затворы, вытянутые в продольном направлении вдоль рабочей области транзистора области стока и истока с контактами к указанным областям стока и истока, фронтальный подзатворный и погруженный окислы, и который выполнен на структуре «германий на изоляторе», фронтальный затвор выполнен в виде трех идентичных фронтальных затворов с тремя идентичными фронтальными подзатворными окислами, а обратный затвор - в виде трех идентичных обратных затворов.

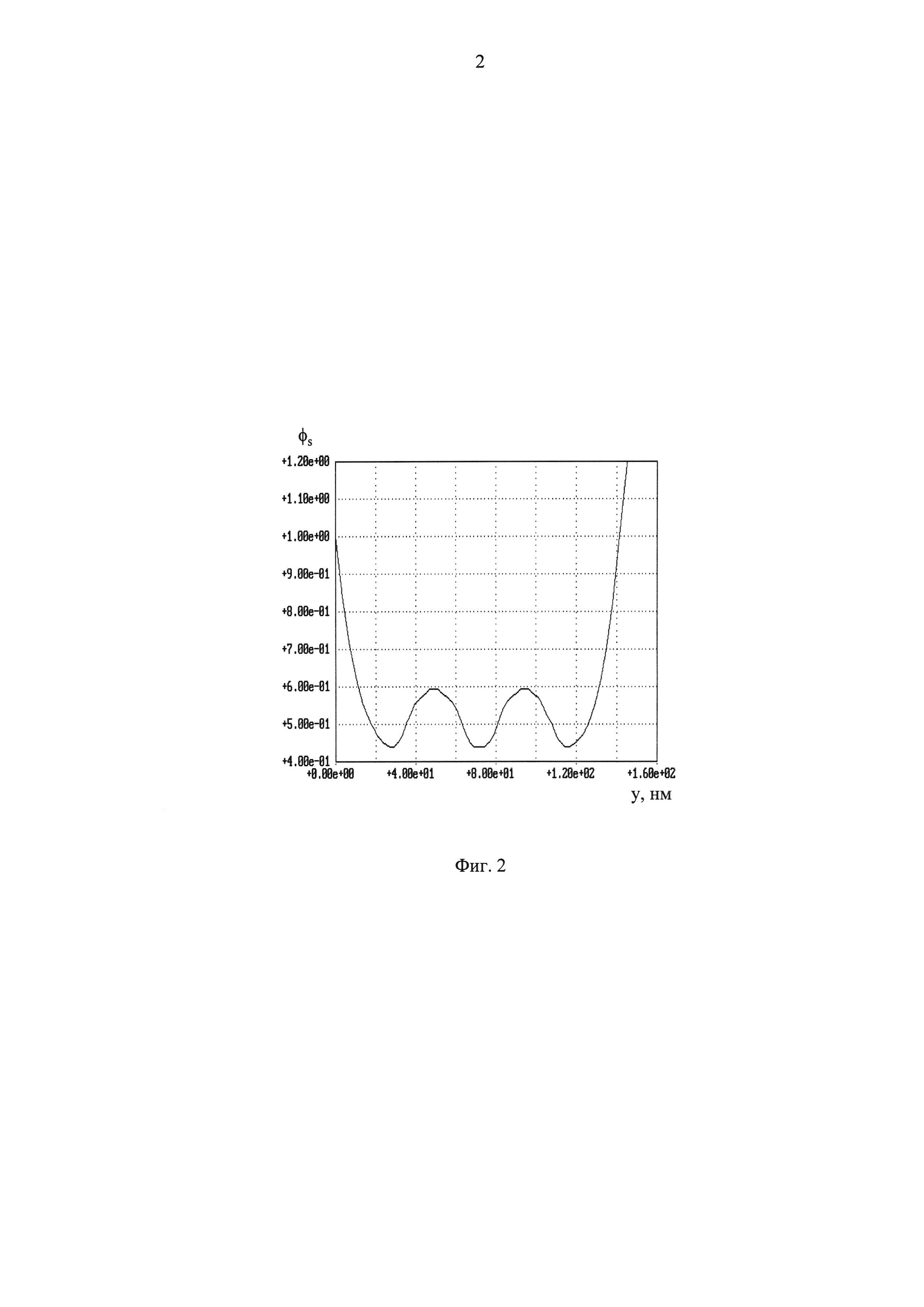

На фиг. 1 - патентуемый однотранзисторный логический вентиль И.

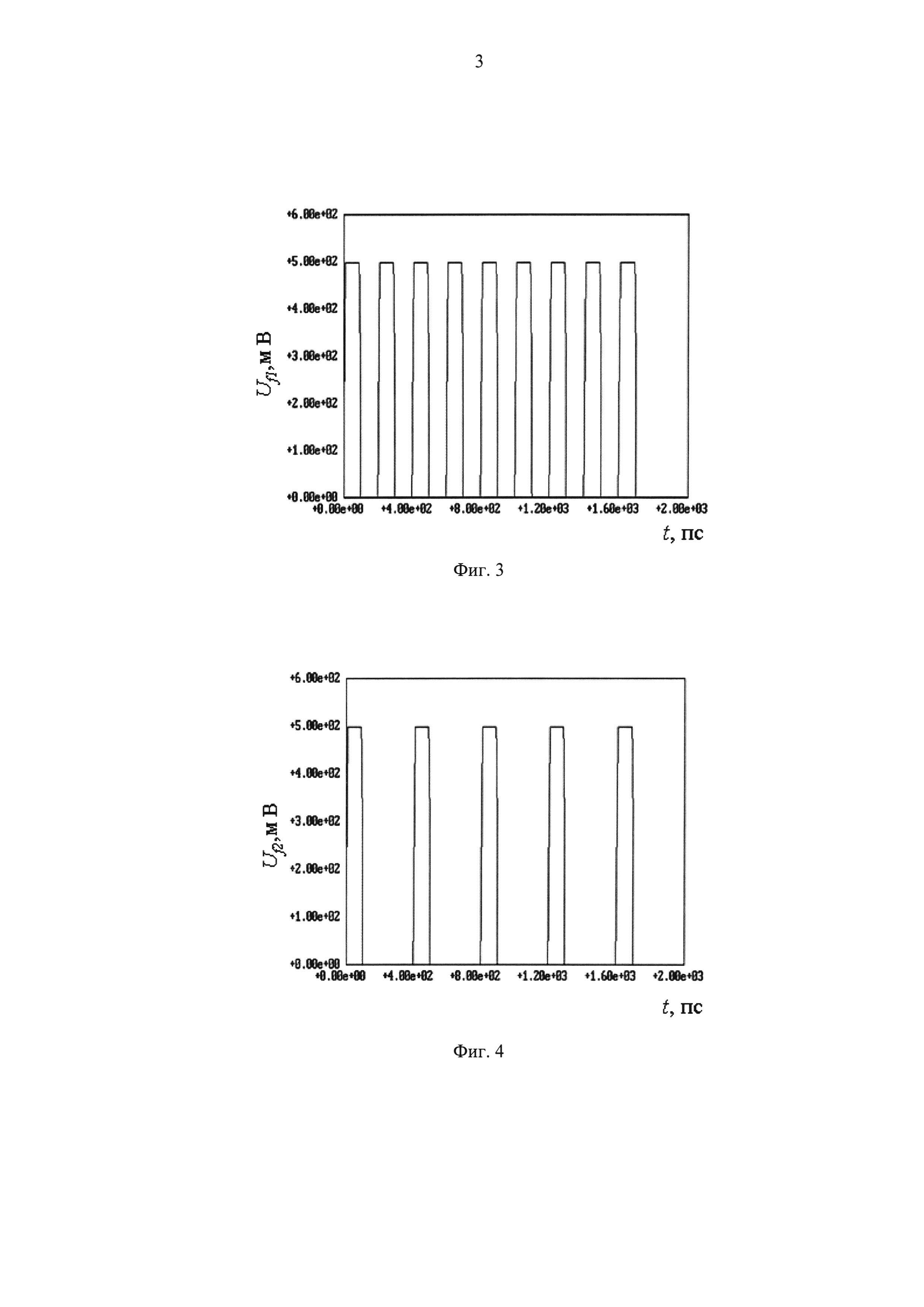

На фиг. 2 - нормированное распределение поверхностного потенциала вдоль транзисторной структуры с тремя независимыми затворами.

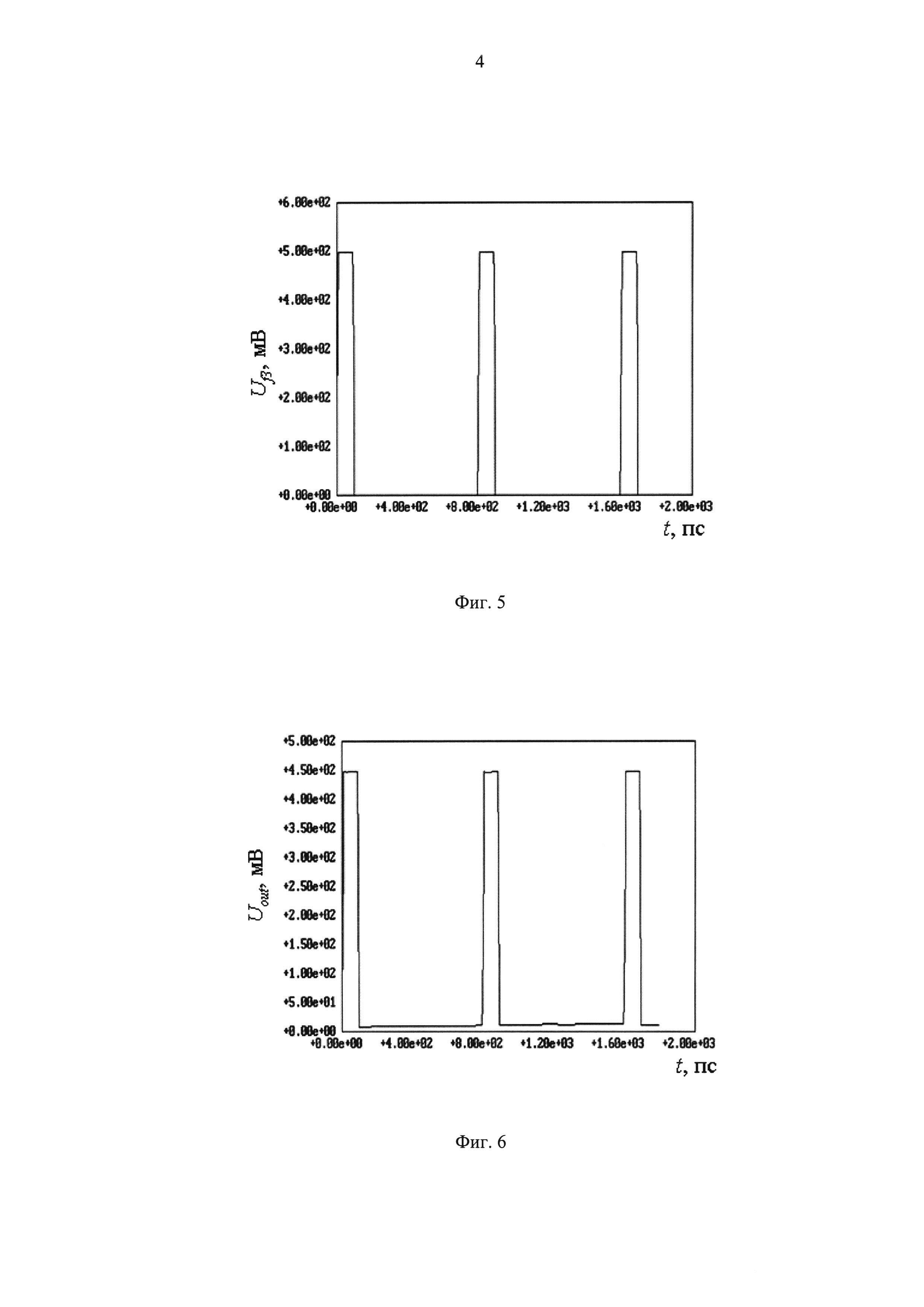

На фиг. 3 - временная диаграмма напряжения на первом фронтальном затворе вентиля.

На фиг. 4 - временная диаграмма напряжения на втором фронтальном затворе вентиля.

На фиг. 5 - временная диаграмма напряжения на третьем фронтальном затворе вентиля.

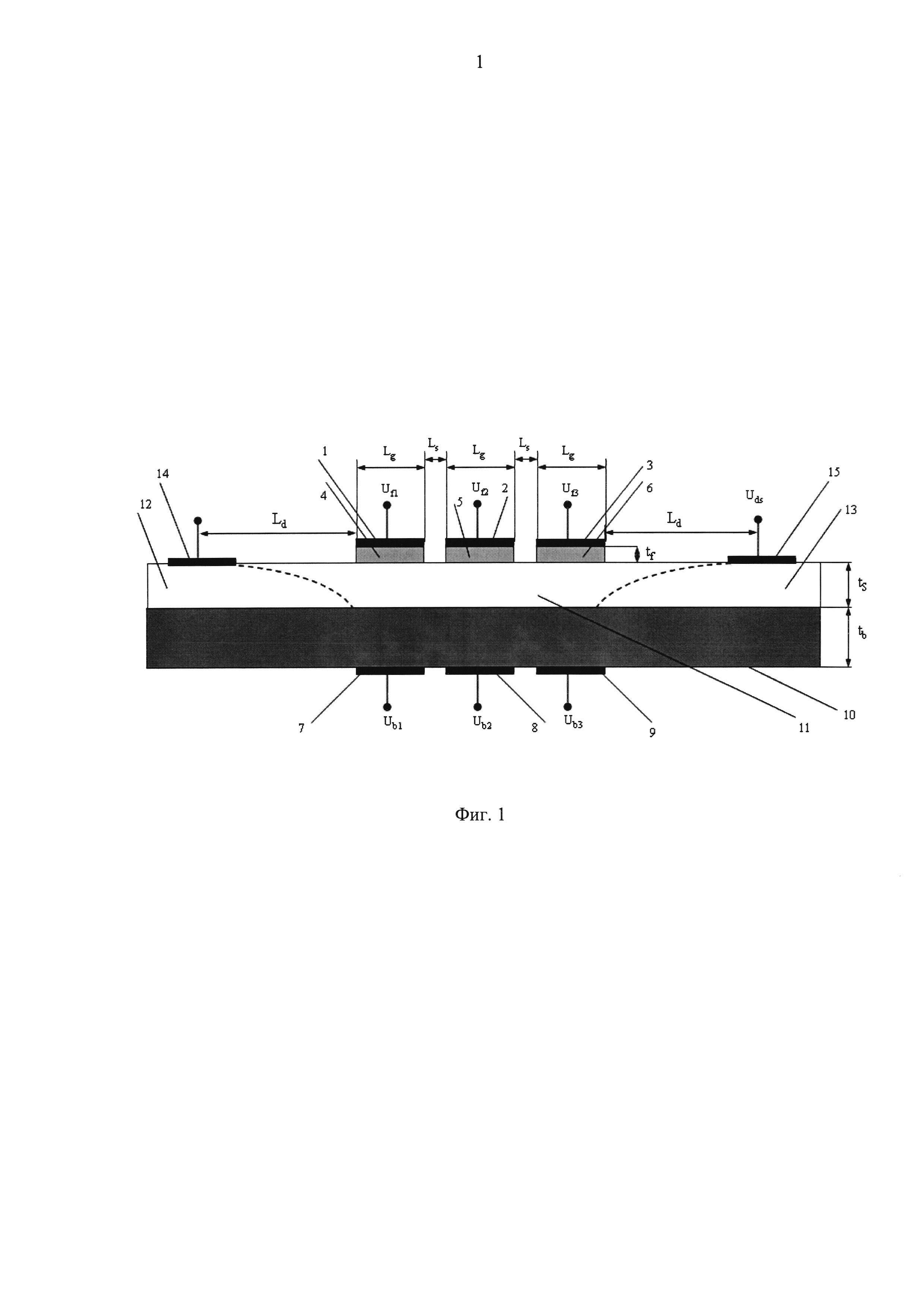

На фиг. 6 - временная диаграмма напряжения на выходе (область истока) вентиля, полученная при помощи математического ядра программы схемотехнического моделирования HSPICE.

Патентуемый однотранзисторный логический вентиль И включает три идентичных фронтальных затвора 1, 2 и 3, три идентичных фронтальных подзатворных окислов 4, 5 и 6, три идентичных обратных затвора 7, 8 и 9, погруженный окисел 10, вытянутые в продольном направлении вдоль рабочей области транзистора 11 область стока 12 и область истока 13, контакт 14 к области стока 12, контакт 15 к области истока 13.

Ток протекает через транзистор только в случае если напряжение, соответствующее уровню логической единицы, приложено ко всем трем фронтальным затворам одновременно. Поэтому напряжение питания Uds (напряжение между стоком и истоком) должно быть равно уровню логической единицы. При всех других комбинациях напряжений на фронтальных затворах ток через транзистор течь не будет и на его выходе будет уровень логического нуля. Таким образом, устройство функционирует как классический вентиль И.

Для моделирования характеристик рассматриваемого устройства была выбрана апробированная транзисторная структура, отвечающая требованиям современной технологии с пиковым уровнем легирования стока/истока 5×1020 см-3 [3]. На фиг. 2 для прототипа транзистора n-типа с длиной каждого затвора Lg1=Lg2=Lg3=25 нм, Ls=20 нм, Ld=45 нм, tS=10 нм, tf и tb 1.5 нм и 50 нм, соответственно, на основе аналитического решения уравнения Пуассона представлено численно рассчитанное распределение поверхностного потенциала для случая Uds=Uf1=Uf2=Uf3=0.1 В и Ub1=Ub2=Ub3=0 В.

При моделировании статических и динамических характеристик вентиля принималась модель подвижности, которая учитывает высокую степень полевой деградации [3], при этом низко полевая подвижность носителей равна 720 см2/(В*с) для n-типа транзистора [4].

На фиг. 3-6 представлена временная диаграмма напряжений на фронтальных затворах и выходе (область стока) вентиля, полученная при помощи математического ядра программы схемотехнического моделирования HSPICE. Длительность импульсов Uf1, Uf2, и Uf3, подающихся на соответствующий затвор (вход вентиля), одинакова. Частота их следования на каждом входе отличается ровно в два раза от предыдущего. Это влечет наложение импульсов из низкочастотной последовательности Uf3 на нечетные импульсы среднечастотной и высокочастотной последовательности Uf2 и Uf1, соответственно. Именно в данных случаях происходит срабатывание вентиля и на его выходе формируется сигнал логической единицы, что иллюстрируется фиг. 6. Во всех остальных случаях напряжение на выходе устройства соответствует уровню логического нуля.

В общем случае время срабатывания вентиля ограничено временным откликом транзисторной структуры, которое можно оптимизировать подбором топологических параметров: Lg - длина затвора, tS - толщина рабочей области,  - толщина окисла фронтального затвора, Ld - длина зазора, g - градиент легирования областей стока/истока.

- толщина окисла фронтального затвора, Ld - длина зазора, g - градиент легирования областей стока/истока.

На основе транзистора со структурой «германий на изоляторе» с тонкой нелегированной рабочей областью и без перекрытия областей затвора и стока/истока выполнен логический вентиль, реализующий операцию конъюнкции. Предложенный подход позволяет, во-первых, повысить степень интеграции логических функций на кристалле, во-вторых, оптимизировать топологические параметры и электрофизические характеристики логического вентиля, в частности уменьшения приложенного напряжения без потери быстродействия, в соответствии с технологическими требованиями, не прибегая к детальному 2D моделированию, и, в-третьих, открывает перспективу существенного уменьшения многих негативных характеристик современных микросхем. Результаты численного моделирования характеристик вентиля показывают, что проекты устройств, выполненных в рамках рассматриваемого подхода масштабирования на основе современных технологий, применимы для реализации эксафлопных вычислений с низким уровнем потребляемой мощности.

Список источников информации

1. International technology roadmap for semiconductor 2014 edition. - [Электронный ресурс] - Режим доступа: http://public.itrs.net.

2. Kranti A., Hao Y., Armstrong G. A. Performance projections and design optimization of planar double gate SOI MOSFETs for logic technology applications // Semiconductor Science and Technology. - 2008, v. 23, №4, P. 217-224.

3. Масальский H.B. Характеристики двух затворных КНИ КМОП нанотранзисторов для перспективных технологий с низким уровнем потребляемой мощности // Микроэлектроника. - 2012, т. 41, №6, с. 436-444.

4. З.С.Физика полупроводниковых приборов. М.: Мир. 1984.

Однотранзисторный логический вентиль И с архитектурой без перекрытия областей затвор-сток/исток, включающий фронтальный и обратный затворы, вытянутые в продольном направлении вдоль рабочей области транзистора, области стока и истока с контактами к указанным областям стока и истока, фронтальный подзатворный и погруженный окислы, отличающийся тем, что он выполнен на структуре «германий на изоляторе», фронтальный затвор выполнен в виде трех идентичных фронтальных затворов с тремя идентичными фронтальными подзатворными окислами, а обратный затвор - в виде трех идентичных обратных затворов.