Результат интеллектуальной деятельности: СПОСОБ ПРЕДЗАРЯДА ЛИНИИ СОВПАДЕНИЯ РЕГИСТРА АССОЦИАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА (АЗУ) И МОДУЛЬ ПРЕДЗАРЯДА

Вид РИД

Изобретение

Изобретение относится к области вычислительной цифровой техники, а именно к вычислительным системам на основе микропроцессоров с ассоциативным запоминающим устройством (АЗУ).

Известен способ предзаряда к потенциалу питания линии совпадения регистра АЗУ, включающий разбиение линии совпадения на иерархические уровни и предзаряд только тех линий совпадений нижнего уровня, в которых произошел разряд их до потенциала земли во время сравнения данных, хранящихся в АЗУ, с данными, поступившими извне. Данный способ осуществляется устройством, содержащим схему восстановления линий совпадения, сконфигурированную предотвращать восстановление, по меньшей мере, одной из линий совпадения более низкого уровня в пределах первой группы в состояние, предшествующее определению, в ответ на информацию разрешения, ассоциированную с линиями совпадения более низкого уровня в пределах первой группы (патент RU №2414014, кл. G11C 15/00, опублик. 2011).

Недостатком описанного способа является сложность системы управления предзарядом и необходимость трассировки дополнительных сигнальных проводников для включения р-канальных транзисторов предзаряда внутри АЗУ, что отрицательно сказывается на занимаемой площади.

Наиболее близкими по технической сути и достигаемому результату к патентуемым объектам изобретения являются способ предзаряда линии совпадения регистра ассоциативного запоминающего устройства (АЗУ), включающий восстановление потенциала линии совпадения до потенциала шины питания АЗУ в период после завершения очередного цикла сравнения хранящихся в ячейке данных с внешними данными и до начала следующего цикла сравнения путем протекания тока между шиной питания АЗУ и линией совпадения через транзисторы одинакового типа проводимости, последовательно включенные между шиной питания АЗУ и линией совпадения, а также модуль предзаряда, включающий два транзистора с одинаковым типом проводимости, последовательно включенные между шиной питания АЗУ и линией совпадения (патент US №7,852,652 кл. G11C 15/04, опублик. 2010 г.).

Недостатком описанных выше способа и модуля является необходимость размещения на кристалле устройства, генерирующего сигналы управления транзисторами предзаряда, а также трассировка дополнительных сигналов от этого устройства к транзисторам предзаряда внутри каждого регистра АЗУ, что приводит к увеличению площади, занимаемой АЗУ на кристалле. Кроме того, передача сигналов управления по проводникам к схеме предзаряда приводит к появлению дополнительных помех и наводок на соседние сигнальные проводники внутри регистра АЗУ.

Техническим результатом, ожидаемым от использования патентуемого изобретения, является уменьшение площади АЗУ и повышение его помехоустойчивости путем исключения сигналов, предназначенных только для управления предзарядом внутри регистра, и устройств, генерирующих эти сигналы.

Указанный технический результат достигается тем, что в способе предзаряда линии совпадения регистра АЗУ, включающем восстановление потенциала линии совпадения до потенциала шины питания АЗУ в период после завершения очередного цикла сравнения хранящихся в ячейке данных с внешними данными и до начала следующего цикла сравнения путем протекания тока между шиной питания АЗУ и линией совпадения через транзисторы одинакового типа проводимости, последовательно включенные между шиной питания АЗУ и линией совпадения, согласно изобретению указанное восстановление потенциала линии совпадения осуществляют путем установления обоих парафазных сигналов сравнения данных в низкий логический уровень на затворах указанных транзисторов.

Для осуществления способа предназначено устройство, состоящее из двух транзисторов с одинаковым типом проводимости, последовательно включенных между шиной питания АЗУ и линией совпадения, к затворам которых согласно изобретению подключены соответственно прямой и инверсный выходы усилителя сигналов на линиях сравнения данных АЗУ, открывающие указанные транзисторы при низком логическом уровне обоих парафазных сигналов сравнения данных АЗУ.

В результате при установлении низкого логического уровня на обеих шинах сравнения данных становится возможным протекание тока между шиной питания и линией совпадения и осуществляется предзаряд линии совпадения к потенциалу питания только за счет проводников, необходимых для функционирования ячейки ассоциативной памяти, без использования дополнительных управляющих сигналов, что приводит к снижению уровня помех и наводок и снижению площади кристалла за счет исключения отдельных устройств и проводников, предназначенных для управления предзарядом линии совпадения.

Изобретение поясняется чертежами, где

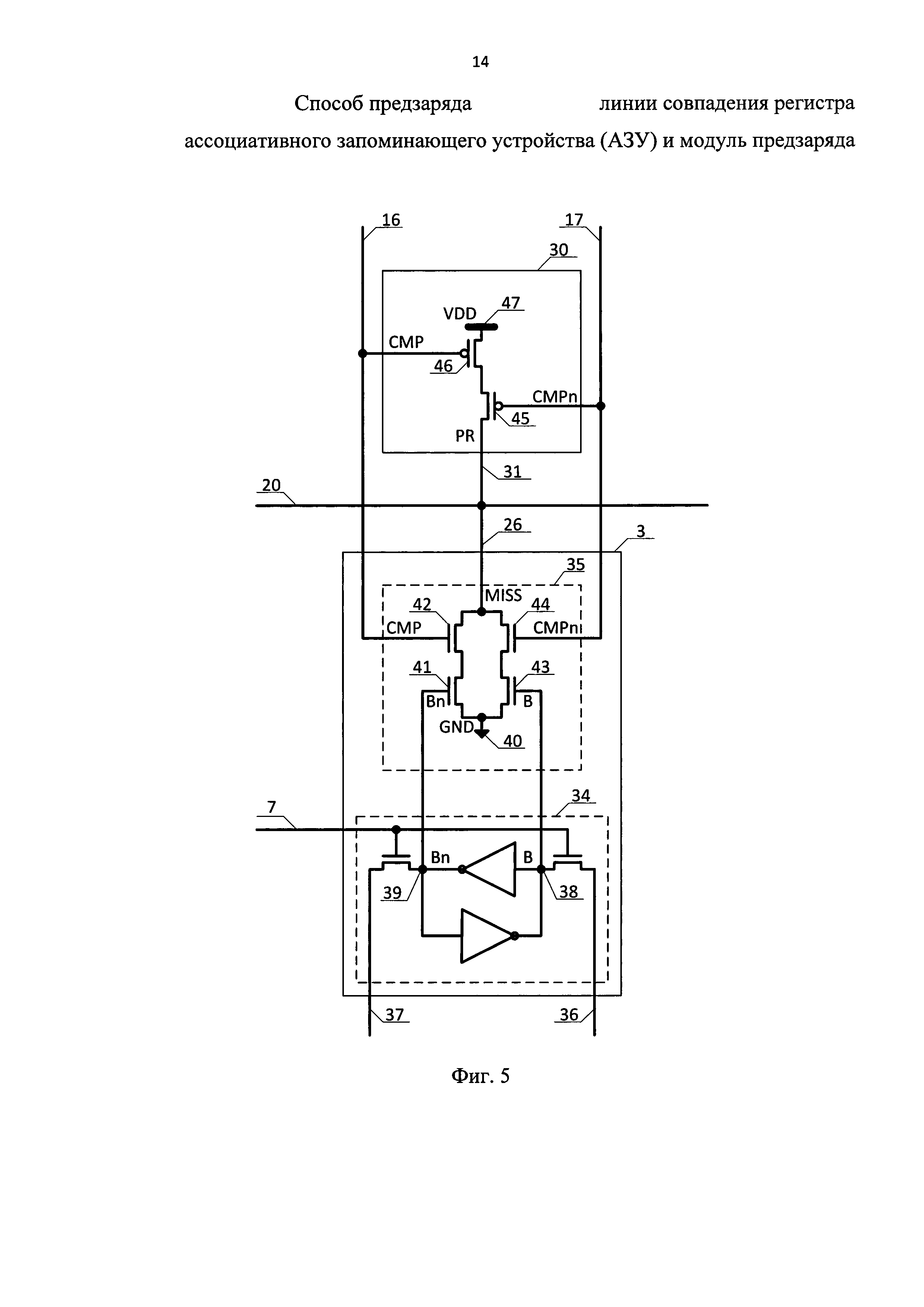

на фиг. 1 представлен неограничивающий пример схемы массива ассоциативной памяти,

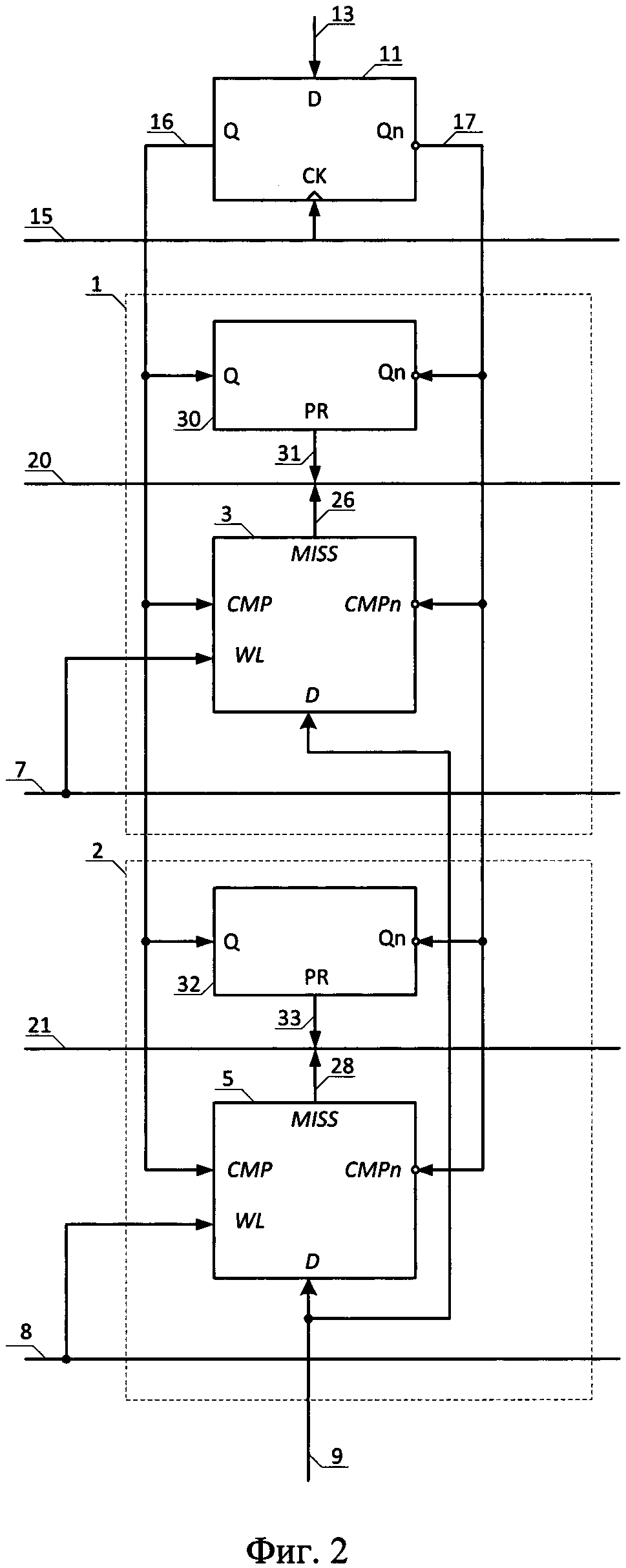

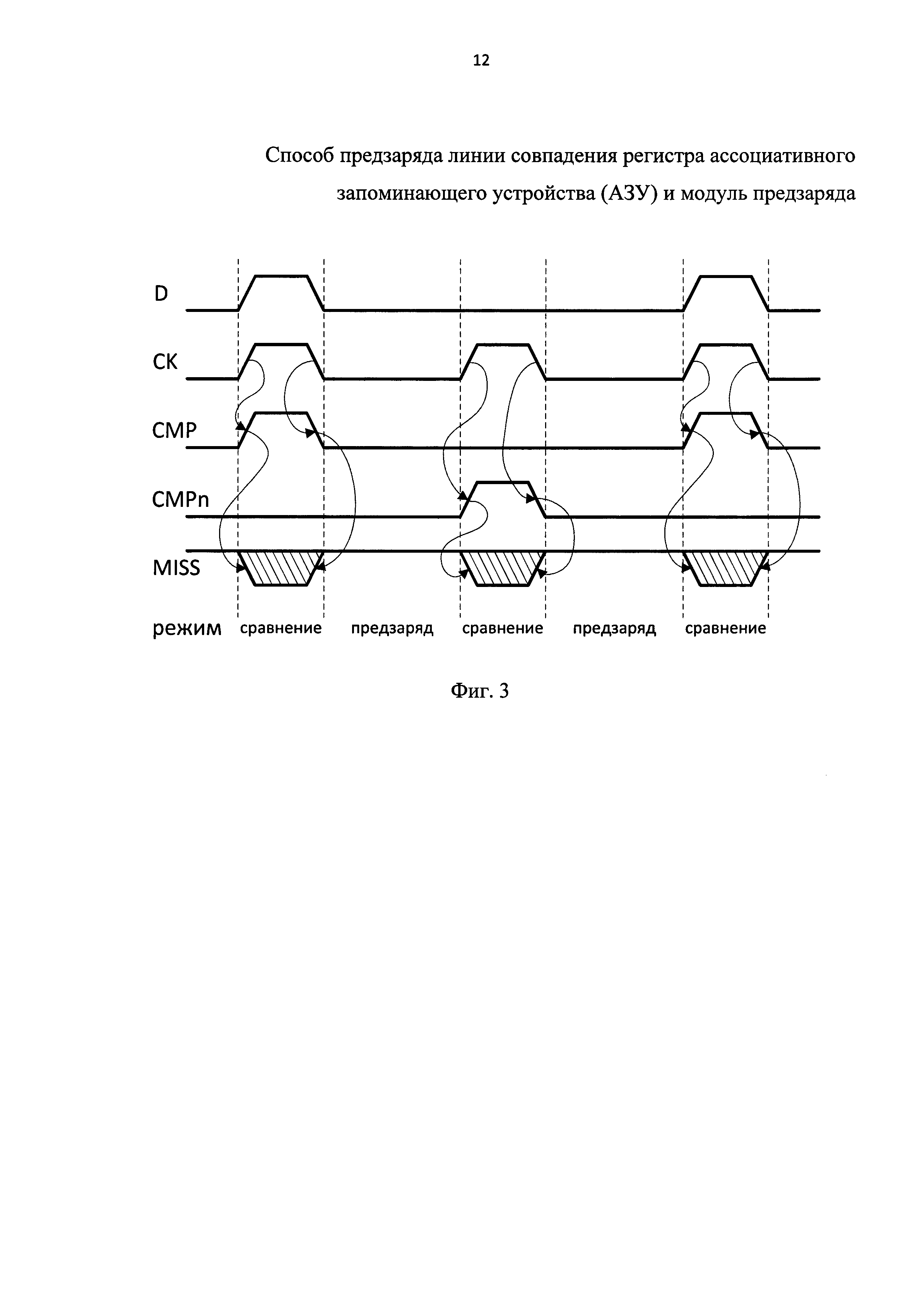

на фиг. 2 - схема патентуемого способа предзаряда линии совпадения регистра АЗУ,

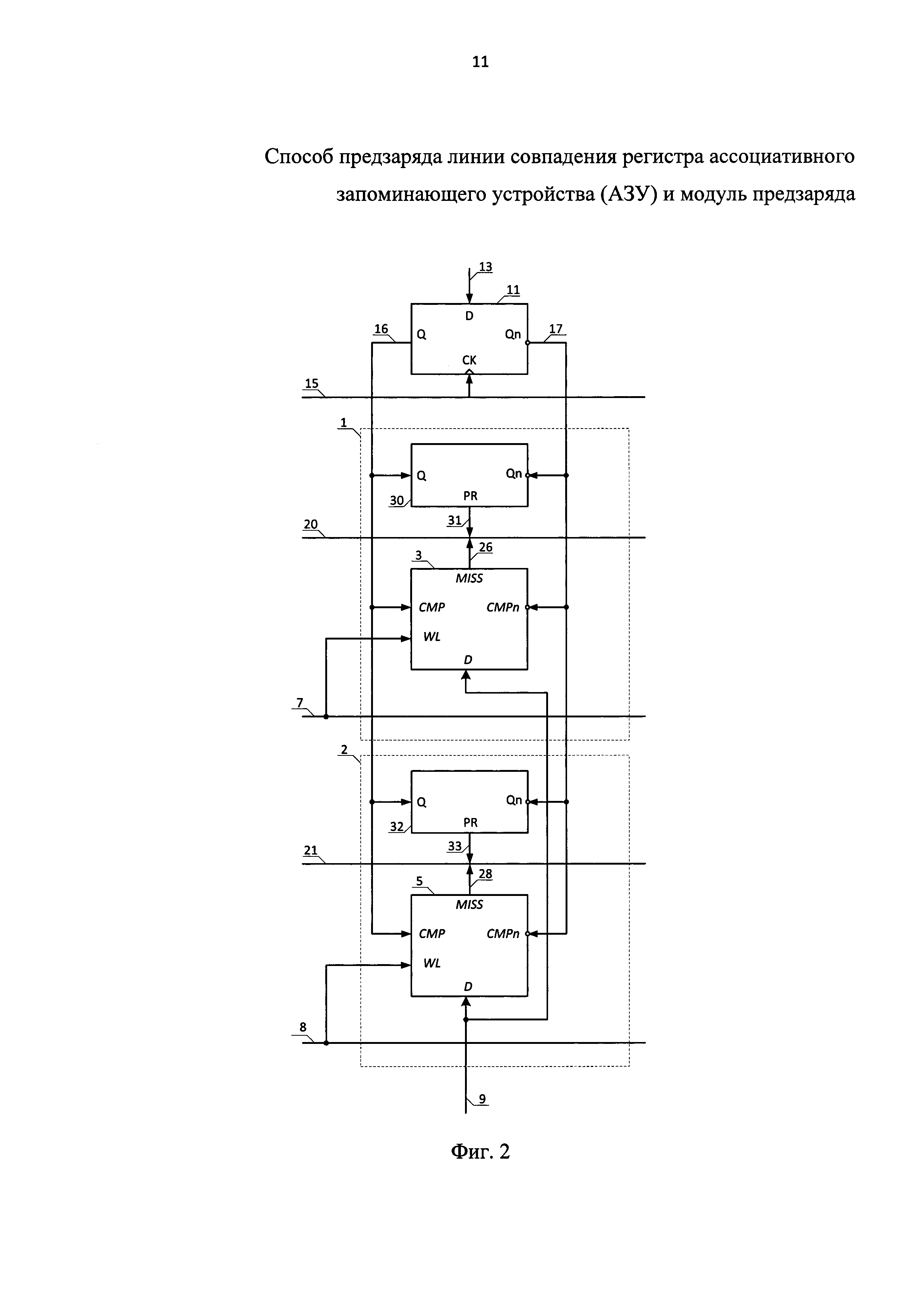

на фиг. 3 - временная диаграмма работы АЗУ на основе патентуемого способа,

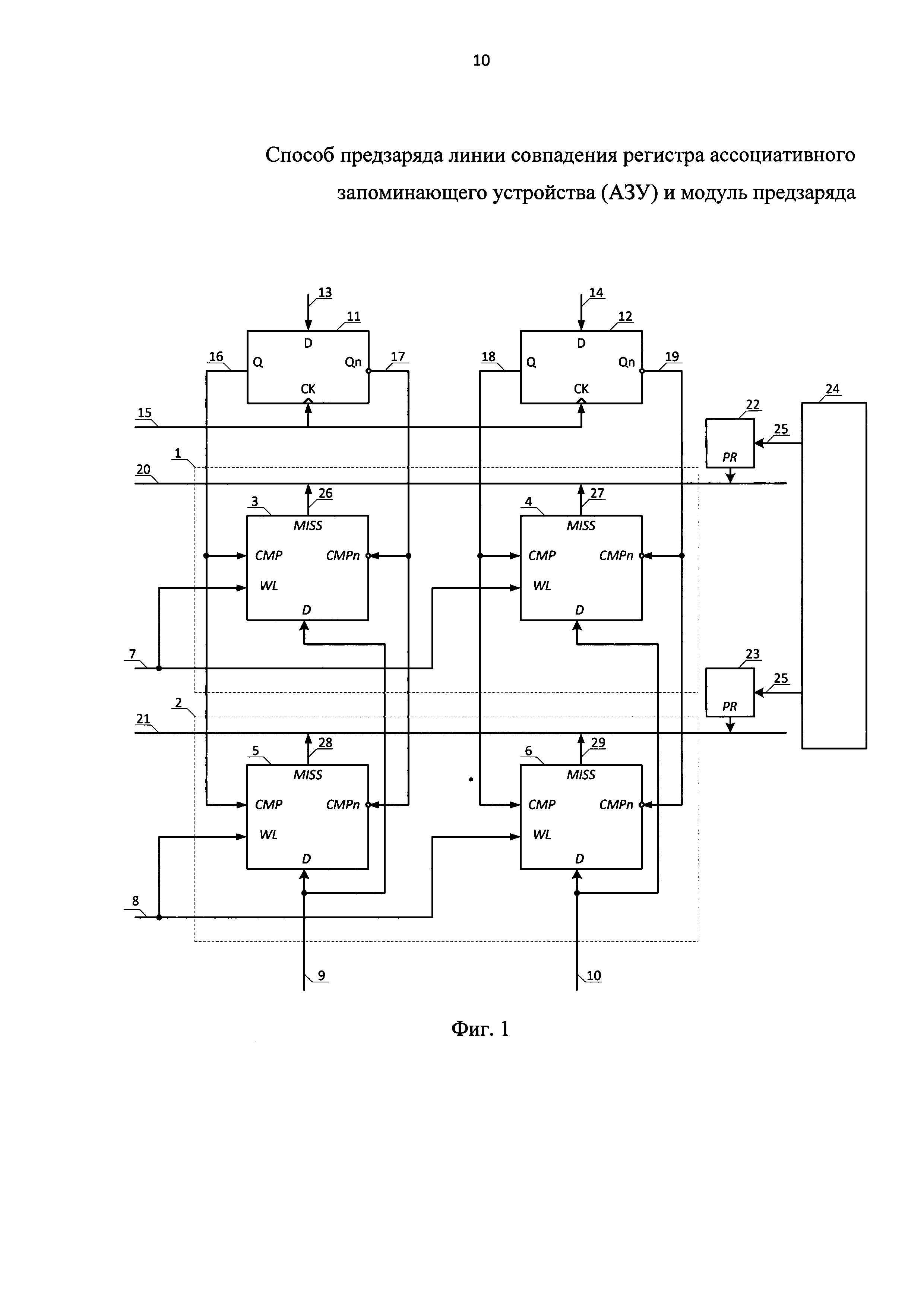

на фиг. 4 - схема устройства, реализующего патентуемый способ,

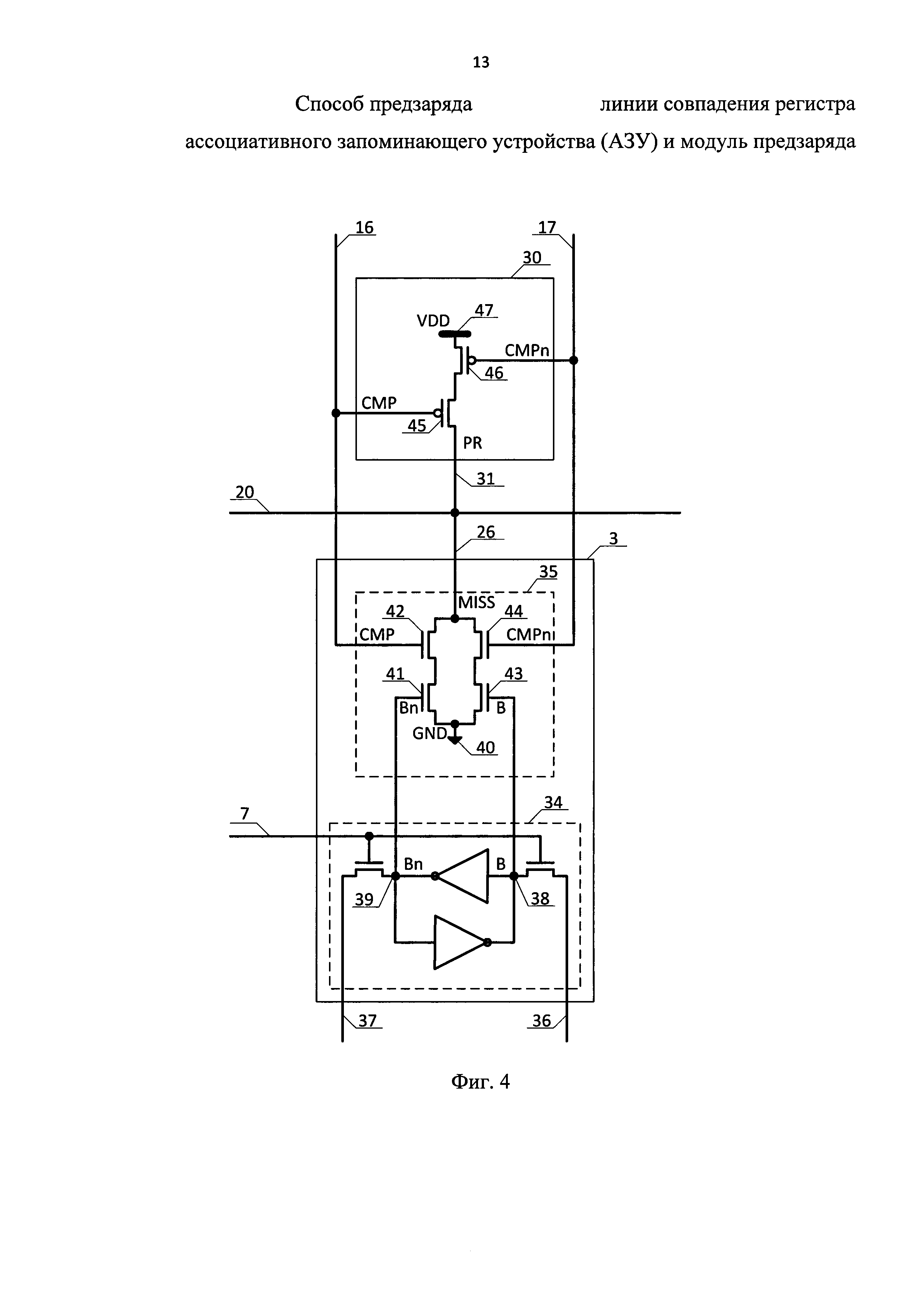

на фиг. 5 - схема другого варианта устройства, реализующего патентуемый способ.

Массив памяти АЗУ содержит несколько регистров с определенным количеством бит в каждом. Неограничивающий пример, известный из уровня техники и приведенный на фиг. 1, содержит, например, два регистра: верхний 1 и нижний 2. Верхний регистр 1 в данном примере содержит две ячейки ассоциативной памяти: левая 3 и правая 4. Нижний регистр 2 в данном примере содержит также две ячейки ассоциативной памяти: левая 5 и правая 6. Ячейки ассоциативной памяти 3, 4, 5, 6 могут иметь как идентичные, так и разные схемы. Через верхний регистр 1 проходят одна или несколько сквозных словарных шин 7, управляющих чтением и записью данных в ячейки ассоциативной памяти 3 и 4. Через нижний регистр 2 проходят одна или несколько сквозных словарных шин 8, управляющих чтением и записью данных в ячейки ассоциативной памяти 5 и 6. Записываемые и считываемые данные по одной или нескольким битовым шинам 9 подаются к ячейкам ассоциативной памяти 3 и 5, а по одной или нескольким битовым шинам 10 - к ячейкам ассоциативной памяти 4 и 6. Над ячейками ассоциативной памяти 3 и 5 находится усилитель 11. А над ячейками ассоциативной памяти 4 и 6 находится усилитель 12. Бит внешних данных для сравнения с данными, записанными в ячейках ассоциативной памяти 3 и 5, подается на вход 13 усилителя 11. Бит внешних данных для сравнения с данными, записанными в ячейках ассоциативной памяти 4 и 6, подается на вход 14 усилителя 12. Все усилители управляются синхросигналом 15. Усилитель 11 имеет парафазные выходы - прямой 16 и инверсный 17 - подключенные к парафазным входам сравнения в ячейках ассоциативной памяти 3 и 5. Усилитель 12 имеет парафазные выходы -прямой 18 и инверсный 19 - подключенные к парафазным входам сравнения в ячейках ассоциативной памяти 4 и 6. Через регистр 1 проходит сквозная линия совпадения 20, а через регистр 2 - линия совпадения 21. К линии совпадения 20 подключена схема предзаряда 22, а к линии совпадения 21 подключена схема предзаряда 23. Устройство управления предзарядом 24 генерирует один или несколько сигналов 25, запускающих схемы предзаряда 22 и 23. Также к линии совпадения 20 подключен выход сравнения 26 ячейки ассоциативной памяти 3 и выход сравнения 27 ячейки ассоциативной памяти 4. А к линии совпадения 21 подключен выход сравнения 28 ячейки ассоциативной памяти 5 и выход сравнения 29. Сигналы 25, во-первых, необходимо трассировать внутри кристалла, занимая этими проводниками дополнительную площадь в каждом регистре, а во-вторых, для их генерации необходимо разместить на кристалле устройство управления предзарядом 24.

На фиг. 2 представлена схема, поясняющая способ предзаряда по патентуемому изобретению, не требующая специальных сигналов, подобных сигналам 25, и дополнительных устройств для их генерации, подобных устройству управления предзарядом 24. Возле каждой или части ячеек, входящих в каждый отдельно взятый регистр ассоциативной памяти 1 и 2, размещается модуль предзаряда, управляемый прямыми и инверсными выходами усилителей 11 и 12. Так, возле ячейки ассоциативной памяти 3 находится модуль 30, выход предзаряда 31 которого подключен к линии совпадения 20. А возле ячейки ассоциативной памяти 5 находится модуль 32, выход предзаряда 33 которого подключен к линии совпадения 21.

Временная диаграмма работы АЗУ, представленная на фиг. 3, изображена для случая, при котором бит данных, поступивший на вход 13, передается на выходы 16 и 17 по высокому уровню синхросигнала разрешения 15, а по низкому уровню синхросигнала 15 напряжение на выходах 16 и 17 устанавливается в низкий уровень. При этом напряжение на линиях совпадения 20 и 21 предзаряжается до высокого логического уровня. Когда один из сигналов на выходах 16 или 17 переключается в высокий логический уровень, модули предзаряда 30 и 32 отключаются, в ячейках ассоциативной памяти происходит сравнение данных, хранящихся в ячейках, с данными, поступившими с выходов 16 и 17 усилителя 11, что или разряжает линию совпадения до низкого логического уровня в случае несовпадения, или не изменяет ее потенциал в случае совпадения.

Осуществление способа предзаряда линии совпадения регистра АЗУ показано на работе устройства, состоящего из известной из уровня техники ячейки ассоциативной памяти 3 и из модуля предзаряда 30, неограничивающий пример которых приведен на фиг. 4 и фиг. 5. Ячейка ассоциативной памяти 3 состоит из двух модулей, известных из уровня техники: триггера ячейки 34 и компаратора 35. Сигнал словарной шины 7 разрешает запись данных, поступившим по прямой битовой шине 36 и инверсной битовой шине 37 в проводники ячейки ассоциативной памяти, образующие узлы хранения прямого бита данных 38 и инверсного бита данных 39. Сравнение данных, записанных в триггер 34 в узлах хранения прямого бита данных 38 и инверсного бита данных 39, с данными, поступившими в ячейку ассоциативной памяти с выходов 16 и 17 усилителя 11, производится в компараторе 35. К шине земли 40 подключен исток n-канального транзистора 41, сток которого подключен к истоку n-канального транзистора 42. На затвор транзистора 41 приходит сигнал с узла хранения инверсного бита данных 39, а на затвор транзистора 42 - сигнал с прямого выхода 16 усилителя 11. Аналогично к шине земли 40 подключен исток n-канального транзистора 43, сток которого подключен к истоку n-канального транзистора 44. На затвор транзистора 43 приходит сигнал с узла хранения прямого бита данных 38, а на затвор транзистора 44 - сигнал с инверсного выхода 17 усилителя 11. Стоки транзисторов 42 и 44 подключены к выходу 26 компаратора 35.

Модуль предзаряда 30 (см. фиг. 4) состоит из двух транзисторов с одинаковым типом проводимости, последовательно включенных между шиной питания АЗУ и линией совпадения. Так, например, указанный модуль может состоять из первого р-канального транзистора 45, сток которого подключен к выходу 31 модуля предзаряда 30, а исток - к стоку второго р-канального транзистора 46. Исток транзистора 46 подключен к шине питания 47. На затвор транзистора 45 подается сигнал с прямого выхода 16 усилителя 11, а на затвор транзистора 46 подается сигнал с инверсного выхода 17 усилителя 11.

Другой вариант устройства для осуществления способа предзаряда линии совпадения регистра АЗУ показан на фиг. 5. Модуль предзаряда 30 состоит из р-канального транзистора 45, сток которого подключен к выходу 31 модуля предзаряда 30, а исток - к стоку р-канального транзистора 46. Исток транзистора 46 подключен к шине питания 47. На затвор транзистора 45 подается сигнал с инверсного выхода 17 усилителя 11, а на затвор транзистора 46 подается сигнал с прямого выхода 16 усилителя 11.

Модуль предзаряда 30 может быть выполнен на транзисторах, имеющих пороговое напряжение, отличающееся от порогового напряжения остальных транзисторов ячейки ассоциативной памяти 3 в большую сторону для снижения величины токов утечки.

Устройство работает следующим образом. Подключенные к шине земли 40 n-канальные транзисторы 41 и 42 разряжают линию совпадения 20 до потенциала шины земли 40 через выход 26 компаратора 35, только если на оба их затвора одновременно подается высокий логический уровень. Аналогично, подключенные к шине земли 40 n-канальные транзисторы 43 и 44 разряжают линию совпадения 20 до потенциала шины земли 40 через выход 36 компаратора 35, только если на оба их затвора одновременно подается высокий логический уровень. Таким образом, потенциал линии совпадения 20 может быть равен нулю только в случае несовпадения бита данных, записанных в триггер ячейки 34, с битом данных, поступившим на вход усилителя 11, и при высоком логическом уровне хотя бы на одном из выходов 16 или 17 усилителя 11. Таким образом, осуществляется сравнение бита данных, хранящегося в узлах 38 и 39 триггера 34, с битом данных, поступившим на вход 13 усилителя 11.

При одновременной установке на выходах 16 и 17 усилителя 11 низкого логического уровня выход 26 компаратора 35 отключается от линии совпадения 20. Одновременно с этим оба транзистора 45 и 46 начинают проводить ток от шины питания 47 к линии совпадения 20 через выход 31 модуля предзаряда 30, заряжая, тем самым, ее до потенциала шины питания 47 и подготавливая к новому циклу сравнения. Таким образом, осуществляется предзаряд линии совпадения 20 к высокому логическому уровню без использования дополнительных управляющих сигналов.

Изобретение позволяет уменьшить площадь, занимаемую ассоциативным запоминающим устройством (АЗУ) на кристалле за счет исключения дополнительных трасс сигналов управления предзарядом в каждом регистре и специальных устройств, генерирующих сигналы управления предзарядом, а также повысить помехоустойчивость АЗУ за счет отсутствия помех и наводок от трасс сигналов управления предзарядом в каждом регистре.