Результат интеллектуальной деятельности: ГИБРИДНЫЙ ПОТОКОВЫЙ МИКРОПРОЦЕССОР

Вид РИД

Изобретение

Изобретение относится к области вычислительной техники и может быть использовано в высокопроизводительных микропроцессорных системах.

Известен блок декодирования двух наборов команд, входящий в состав ядра процессора, состоящий из двух декодеров команд, каждый из которых предназначен для декодирования своего набора инструкций, и управляющей логики, которая выбирает выход одного или второго декодера в зависимости от флага типа команды для исполнения в конвейере (патент US №5.568.646, кл. G06F 9/00, опубл. 22.10.1996 г.).

Недостатком блока является использование двух наборов команд, из которых один является поднабором второго (16-разрядный набор инструкций Thumb, являющийся поднабором 32-разрядногоАКМ).

Известен микропроцессор, содержащий блок преобразования CISC команд архитектуры ×86 и RISC команд архитектуры ARM в микроинструкции, определенные для процессора. Блок входит в состав микропроцессора, имеет двухуровневый транслятор инструкций из входного формата во внутренние инструкции, единый исполнительный конвейер и общий регистровый файл, разделенный на 3 части: общие архитектурные регистры, доступные в обоих (×86 и ARM) архитектурах, регистры, специфичные для ×86 архитектуры, и регистры, специфичные для ARM архитектуры. При этом регистры из общей (разделяемой) части регистрового файла доступны на чтение и запись инструкциям обоих архитектур(3аявка US №2012/0260065 A1, кл. G06F 9/06, опублик. 11.10.2012 г.).

Недостатком блока является использование двух наборов команд для доступа к разделяемым (общим) ресурсам и возможность одновременного выполнения команд разных архитектур, что трудно реализуемо. Операционные системы не поддерживают одновременного выполнения двух независимых наборов команд на общих регистрах. Использование данного метода невозможно без изменения исходных текстов программ.

Наиболее близким по технической сути и достигаемому результату является гибридный микропроцессор RISC архитектуры, содержащий системный контроллер, кэш-память второго уровня, блок управления памятью, буфер инструкций, целочисленное АЛУ и блок вещественной арифметики (Патент RU №2359315, кл. G06F 9/30, опубл. 20.06.2009 г.).

Недостатком его является то, что описанный гибридный микропроцессор может декодировать только набор команд одной архитектуры.

Техническим результатом от использования данного изобретения является расширение технологических возможностей путем трансляции инструкций RISC архитектуры в команды управления потокового вычислителя и повышение производительности микропроцессора путем независимого выполнения команд в потоковом вычислителе без блокировки основного конвейера микропроцессора.

Указанный технический результат достигается тем, что гибридный потоковый микропроцессор, содержащий системный контроллер, кэш-память второго уровня, блок управления памятью, буфер инструкций, целочисленное АЛУ и блок вещественной арифметики, согласно изобретению дополнительно снабжен блоком передекодирования инструкций, потоковым вычислителем и блоком управления потоковым вычислителем, при этом блок передекодирования инструкций связан с кэш-памятью второго уровня и блоком управления памятью для трансляции инструкций во внутреннюю кодировку процессора или передекодирования их в инструкцию потокового вычислителя, блок управления потоковым вычислителем связан с буфером инструкций, блоком управления памятью, кэш-памятью второго уровня для получения команд и обмена данными, а также с потоковым вычислителем для управления им и обмена данными, причем связи между блоками осуществляются посредством шин.

Описанная совокупность признаков позволяет достичь указанный технический результат путем использования дополнительных сложных инструкций расширенного формата, увеличения количества регистров во внутреннем формате и возможность трансляции инструкций из RISC формата в инструкцию управления потоковым вычислителем.

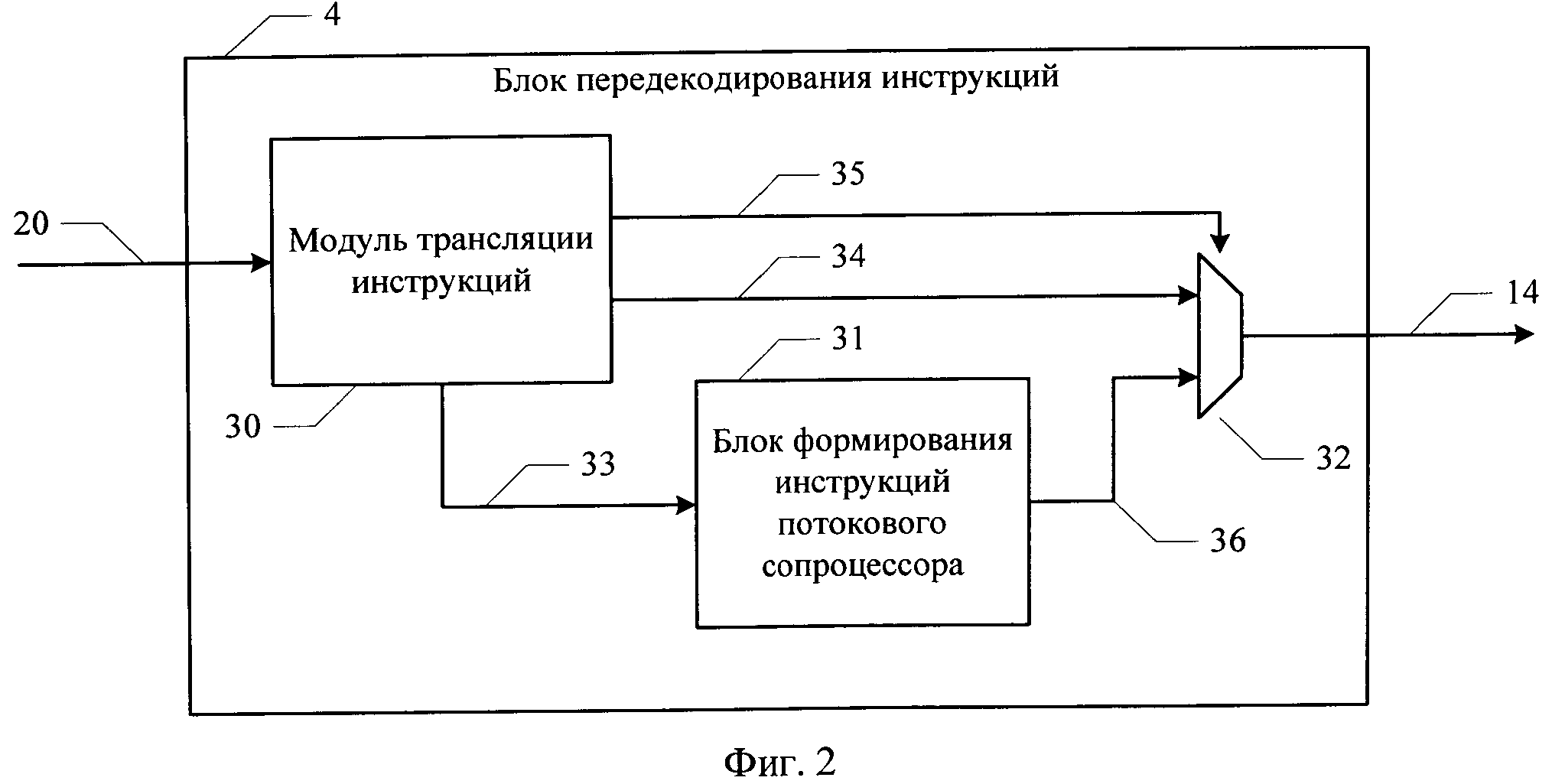

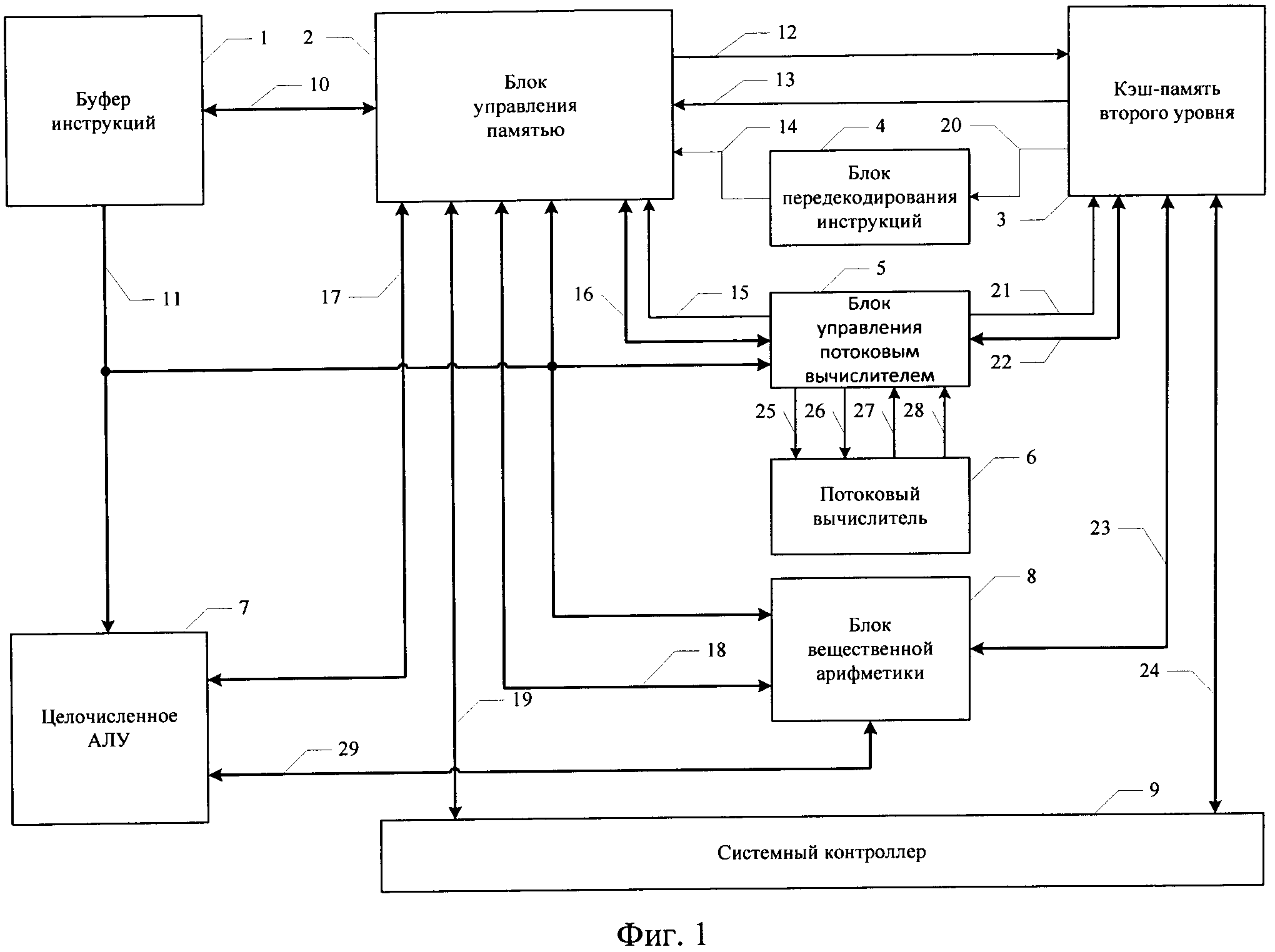

Изобретение поясняется чертежами, где на фиг.1 изображена общая схема гибридного потокового микропроцессора, на фиг.2 - схема блока передекодирования инструкций.

Устройство состоит из буфера инструкций 1, блока управления памятью 2, кэш-памяти второго уровня 3, блока передекодирования инструкций 4, блока управления потоковым вычислителем 5, потокового вычислителя 6, целочисленного АЛУ 7, блока вещественной арифметики 8 и системного контроллера 9. Буфер инструкций 1 связан с блоком управления памятью 2 для запроса инструкций интерфейсом 10 и с блоками 2, 5, 7 и 8 для выдачи инструкций на выполнение интерфейсом 11. Блок управления памятью 2 связан шинами 12 для запроса данных/инструкций и 13 для получения данных из кэш-памяти второго уровня 3; шиной 14 с блоком передекодирования инструкций 4 для получения инструкций; шиной 15 с блоком управления потоковым вычислителем 5 для получения запросов чтения/записи данных, шиной 15 с блоком управления потоковым вычислителем 5 для обмена данными между блокам; шиной 17 с блоком целочисленного АЛУ 7 и шиной 18 с блоком вещественной арифметики 8 для обмена данными между блоками; интерфейсом 19 с системным контроллером 9 для реализации протокола когерентности. Кэш-память второго уровня 3 также связана шиной 20 с блоком передекодирования инструкций 4 для выдачи инструкций; шиной 21 с блоком управления потоковым вычислителем 5 для получения запросов чтения/записи данных, шиной 22 с блоком управления потоковым вычислителем 5 для обмена данными между блокам; дополнительной шиной данных 23 с блоком вещественной арифметики 8 для обмена данными при работе с накристальной памятью; интерфейсом 24 с системным контроллером 9 для реализации канала прямого доступа к памяти. Потоковый вычислитель 6 соединен шинами 25, 26, 27 и 28 только с блоком управления потоковым вычислителем 5. Блок целочисленного АЛУ 7 также связан шиной 29 с блоком вещественной арифметики 8 для обмена данными между блоками.

Блок передекодирования инструкций 4 состоит из модуля трансляции инструкций 30, блока формирования инструкций потокового сопроцессора 31 и выходного мультиплексора 32. Модуль трансляции инструкций 30 подключен к входной шине 20 для получения инструкций; связан шиной 33 с блоком формирования инструкций потокового сопроцессора 31 для передачи ему инструкций; шиной 34 с входом данных и шиной 35 с входом управления мультиплексора 32. Блок формирования инструкций потокового сопроцессора 31 связан шиной 36 с входом данных мультиплексора 32. Выход мультиплексора 32 соединен с выходной шиной 14.

Механизм использования потокового вычислителя 6 в составе RISC микропроцессора с использованием блоков передекодирования инструкций 4 и блока управления потоковым вычислителем 5 работает следующим образом.

Работу устройства можно разделить на 2 независимых параллельных процесса: запрос инструкций и их выполнение. Процесс запроса инструкций выполняется следующим образом. Буфер инструкций 1, используя стандартный протокол запроса инструкций, по интерфейсу 10 запрашивает инструкции в кэш-памяти инструкций, входящей в состав блока управления памятью 2. В случае отсутствия инструкций в кэш-памяти инструкций запрос от блока управления памятью 2 по шине 12 передается в кэш-память второго уровня 3. В случае отсутствия инструкций в кэш-памяти второго уровня 3 запрос передается в системный контроллер 9, используя шину 24, по которой с использованием стандартных протоколов обмена к системному контроллеру 9 передается запрос, а к кэш-памяти второго уровня 3 - считанные инструкции. Считанные системным контроллером 9 инструкции записываются в кэш-память второго уровня 3 и передаются по шине 20 в блок передекодирования инструкций 4, который производит их преобразование во внутренний формат или команду управления потоковым вычислителем и выдает их по шине 14 в блок управления памятью 2. После записи в кэш-память инструкций блока управления памятью 2 инструкции передаются по шине 10 в буфер инструкций 1, который их запрашивал.

Преобразование инструкций во внутренний формат заключается в изменении битовой кодировки инструкций, изменении порядка следования полей инструкции и/или изменении номеров архитектурных регистров на номера физических регистров, используемых для хранения данных, и в случае возможности преобразования нескольких инструкций в инструкции управления потоковым вычислителем. Размер кода инструкции при этом увеличивается, дополнительные биты используются для расширения количества используемых физических регистров и задания параметров работы потокового вычислителя. Это дает возможность использования как команд RISC архитектуры, так и команд управления потоковым вычислителем в одном потоке инструкций. Блок передекодирования инструкций 4 работает следующим образом. Поступающие из кэш-памяти второго уровня 3 инструкции по шине 20 подаются на модуль трансляции инструкций 30, который декодируют инструкции и анализирует возможность преобразования их в команды потокового сопроцессора. В случае если полученные инструкции можно преобразовать в команды потокового сопроцессора, модуль трансляции инструкций 30 передает их по шине 33 в блок формирования инструкций потокового сопроцессора 31, а по шине 35 переключает мультиплексор 32 для выбора инструкций с шины 36, связанной с выходом блока формирования инструкций потокового сопроцессора 31. В случае если полученные инструкции нельзя преобразовать в команды потокового сопроцессора, модуль трансляции инструкций 30 транслируют их во внутреннее представление, заменяя, в случае необходимости, используемые в инструкциях номера архитектурных регистров на физические, и передает их по шине 34 на вход данных мультиплексора 32, а по шине 35 переключает его (мультиплексор 32) для выбора инструкций с шины 34. В соответствии со значением на управляющей шине 35 мультиплексор 32 выбирает для передачи на выходную шину 14 инструкции, преобразованные модулем трансляции инструкций 30 или блоком формирования инструкций потокового сопроцессора 31. В результате инструкции, считанные из системного контроллера 9, сохраняются в кэш-памяти второго уровня 3 в исходной кодировке, определяемой архитектурой команд; в кэш-памяти инструкций первого уровня, входящей в состав блока управления памятью 2, во внутренней кодировке (или преобразованные в команды управления потоковым сопроцессором); в буфере инструкций 1 и при выдаче их на выполнение - во внутренней кодировке (или преобразованные в команды управления потоковым сопроцессором).

После получения инструкций буфером инструкций 1 начинается их выполнение. Процесс выполнения инструкций осуществляется следующим образом. Инструкции из буфера инструкций 1 во внутренней кодировке выдаются на шину 11 и поступают на исполнение в блок управления памятью 2, в блок управления потоковым вычислителем 5, в целочисленное АЛУ 7 и в блок вещественной арифметики 8. Исполнительные блоки 2, 5, 7 и 8, получив инструкции, начинают их декодирование и выполнение. Для обмена данными между блоками используются шины, связывающие блоки между собой. Целочисленное АЛУ 7 может передавать и считывать данные кэш-памяти первого уровня, входящей в состав блока управления памятью 2, по шине 17 и регистровых файлов блока вещественной арифметики 8 по шине 29. Блок вещественной арифметики 8 может передавать и считывать данные кэш-памяти первого уровня, входящей в состав блока управления памятью 2, по шине 18, из кэш-памяти второго уровня 3 по шине 23 и регистрового файла целочисленного АЛУ 7 по шине 29. Блок управления потоковым вычислителем 5 может передавать и считывать данные из кэш-памяти первого уровня, входящей в состав блока управления памятью 2, по шине 16, используя отдельную шину запросов 15, и из кэш-памяти второго уровня 3 по шине 22, используя отдельную шину запросов 21. Блок управления памятью 2 передает и принимает данные от целочисленного АЛУ 7 по шине 17, блока вещественной арифметики 8 по шине 18 и блока управления потоковым вычислителем 5 по шине 16. При этом для приема и передачи данных между блоком управления памятью 2 и блоками целочисленного АЛУ 7 и вещественной арифметики 8 не требуется дополнительного управления, т.к. команды обмена данными выполняются в конвейере. Для выполнения обмена данными между блоком управления потоковым вычислителем 5 и блоком управления памятью 2 и кэш-памятью второго уровня 3 используются дополнительные шина запросов 15 и 21 соответственно, по которым блок управления потоковым вычислителем 5 может запрашивать данные независимо от конвейера.

Если запрошенных данных нет в кэш-памяти первого уровня, входящей в состав блока управления памятью 2, блок выставляет запрос на шину 12 на чтение этих данных из кэш-памяти второго уровня 3. В случае отсутствия данных в кэш памяти второго уровня 3, запрос передается в системный контроллер 9, используя шину 24, по которой с использованием стандартных протоколов обмена к системному контроллеру 9 передается запрос, а к кэш-памяти второго уровня 3 - считанные данные. Считанные системным контроллером 9 данные записываются в кэш-память второго уровня 3 и передаются по шине 12 в блок управления памятью 2. После записи в кэш-память данных блока управления памятью 2 данные передаются по шинам 16, 17 и 18 в блок, который их запрашивал.

Такой же механизм запроса данных используется блоком управления памятью 2 при выполнении команд управления кэш-памятями, полученных по шине 11 от буфера инструкций 1. Интерфейс 19 служит для реализации стандартного протокола когерентности.

Блок управления потоковым вычислителем 5 синхронизирует работу потокового вычислителя 6 с остальным конвейером микропроцессора. На основании полученной по шине 11 инструкции, блок управления потоковым вычислителем 5 выдает по шине 25 данные для вычислений и по шине 26 дополнительные параметры для потокового вычислителя 6. На основании обратной связи, получаемой по шине 27, блок управления потоковым вычислителем 5 определяет время выставления на шину 25 следующих данных для вычислений или записи готовых данных, поступающих по шине 28. Если для выполнения вычислений необходимы дополнительные данные, блок управления потоковым вычислителем 5 запрашивает их по шинам 15 и 21, получая их с шин 16 и 22 соответственно. Эти же шины используются для записи в кэш-памяти результатов вычислений.

В результате, если поступающие в блок передекодирования инструкций 4 могут быть преобразованы в команды управления потоковым сопроцессором, они транслируются в них, если нет - они перекодируются во внутренний формат без изменения исполнительных блоков. Блок управления потоковым вычислителем 5 синхронизует работу потокового вычислителя 6 с конвейером, производя обмены данными с блоком управления памятью 2 и кэш-памятью второго уровня 3 независимо от остального конвейера, но используя стандартные протоколы, и подавая данные на потоковый вычислитель 6 асинхронно, на основании обратной связи, получаемой по шине 27. Таким образом, возможно подключение потокового вычислителя как сопроцессора в конвейер микропроцессора RISC архитектуры.

Гибридный потоковый микропроцессор, содержащий системный контроллер, связанный шинами с кэш-памятью второго уровня и с блоком управления памятью, связанным, в свою очередь, шинами с буфером инструкций для запроса им инструкций, целочисленным АЛУ и блоком вещественной арифметики, связанным шиной с кэш-памятью второго уровня, при этом буфер инструкций связан шинами с целочисленным АЛУ, блоком вещественной арифметики и дополнительной шиной с блоком управления памятью для выдачи им инструкций, отличающийся тем, что микропроцессор дополнительно снабжен блоком передекодирования инструкций для преобразования инструкций во внутреннюю кодировку микропроцессора и передекодирования инструкций для потокового вычислителя с входной и выходной шинами, потоковым вычислителем и блоком управления потоковым вычислителем для синхронизации работы потокового вычислителя с конвейером микропроцессора и обмена данными с кэш-памятями, при этом указанный блок передекодирования инструкций связан входной шиной с кэш-памятью второго уровня для получения инструкций и выходной шиной с блоком управления памятью для передачи преобразованных инструкций во внутренней кодировке микропроцессора и передекодированных инструкций для потокового вычислителя, при этом указанный блок управления потоковым вычислителем связан шинами с буфером инструкций для получения инструкций, с блоком управления памятью и с кэш-памятью второго уровня для обмена данными, а также с потоковым вычислителем для управления им и обмена данными.