Результат интеллектуальной деятельности: МОДУЛЬ СИНХРОСТРАТУМА, КООРДИНИРУЮЩИЙ ПАРАЛЛЕЛЬНУЮ РАБОТУ УПРАВЛЯЕМОГО БЛОКА В ГЛОБАЛЬНО АСИНХРОННОЙ СИСТЕМЕ

Вид РИД

Изобретение

Изобретение относится к области вычислительной техники и цифровой автоматики.

При проектировании асинхронных систем, содержащих множество взаимодействующих блоков, а также ГАЛС (Глобально Асинхронных Локально Синхронных) или ГАЛП (Глобально Асинхронных Локально Произвольных) систем, удобно систему разбивать на два слоя, или стратума, один из которых состоит из управляемых блоков и называется процессорным стратумом, а другой осуществляет управление блоками, координируя их взаимодействие, и называется синхростатумом. Такое представление систем позволяет строить подсистему управления, абстрагируясь от конкретных реализаций системных блоков. При этом каждому блоку системы ставится в соответствие модуль синхростратума, который связан с управляемым блоком и с соседними модулями синхростратума парами управляющих сигналов по принципу запрос-ответ.

Моделью управляемого блока в общем случае может служить автомат Мура Ai, работой которого управляет модуль синхростратума с помощью фазового сигнала ai. На изменение значения сигнала ai управляемый блок после завершения в нем переходных процессов отвечает модулю синхростратума изменением значения сигнала от управляемого блока. Сам синхростратум является самосинхронной схемой, поведение которой инвариантно к величинам задержек ее элементов. Таким образом, для модуля синхростратума управляемый им блок представляет собой просто задержку, которую, в частности, можно положить равной нулю и рассматривать синхростратум как самостоятельную схему, не зависящую от конструкции управляемых блоков в том случае, если при этом не нарушается принцип взаимодействия управляемых блоков друг с другом.

Известен наиболее близкий по технической сущности и назначению к патентуемому модулю модуль синхростратума, координирующий параллельную работу управляемого блока в глобально асинхронной системе, включающий первый логический элемент с основным входом, с по крайней мере одним дополнительным входом для сигналов запроса и одним выходом, образующим выход фазового сигнала модуля для управления управляемым блоком, второй логический элемент с входом и выходом, соединенным с основным входом первого логического элемента, и третий логический элемент с основным входом, образующим вход модуля для сигнала индикации окончания переходных процессов в управляемом блоке с по крайней мере одним дополнительным входом для сигналов запроса и выходом, соединенным с входом второго логического элемента, в качестве логических элементов использованы элементы ИЛИ-НЕ или могут быть использованы элементы И-НЕ (см. Varshavsky V.L, Marakhovsky V.В., Chu Т.-А. 4. Logical Timing (Global Synchronization of Asynchronous Arrays) // Parallel Algorithm / Architecture Synthesis: Intern. Symp., Aizu-Wakamatsu, Japan. IEEE CS Press, Mar. 1995. P. 130-138, fig. 10).

Синхростратум, построенный на основе этого известного модуля (см. вышеуказанный источник информации, fig. 9), обладает рядом недостатков:

1) Поскольку синхростратум должен быть схемой, не зависящей от задержек в логических элементах и соединительных проводах, многовходовые элементы ИЛИ-НЕ (И-НЕ) труднореализуемы в современных технологических базисах.

2) Если узел графа межсоединения управляемых блоков имеет k непосредственных соседей, то число связей модуля с другими модулями синхростратума равно 6k.

3) При использовании такого синхростратума каждый управляемый блок работает в противофазе со своими непосредственными соседями, т.е. если он находится в фазе перехода, то непосредственные соседи находятся в фазе перезаписи информации из основного регистра в вспомогательный и наоборот. С помощью таких модулей может быть построен синхростратум для графа межсоединений типа графа Кенига, т.е. бихроматического графа, допускающего раскраску его вершин в два цвета. Если граф не является бихроматическим, то необходимо его привести к бихроматическому виду путем добавления вершин, что равноценно добавлению модулей в синхростратум, что усложняет схему синхростратума.

Задачей патентуемого изобретения является упрощение физической реализации модуля в современных технологических базисах.

Техническим результатом является сокращение числа межмодульных связей в синхростратуме на основе патентуемого модуля и расширение области применения такого синхростратума за счет снятия требования использования только бихроматического графа.

Указанная задача и технический результат достигаются с помощью модуля синхростратума, координирующего параллельную работу управляемого блока в глобально асинхронной системе, включающего первый логический элемент с основным входом, с по крайней мере одним дополнительным входом для сигналов запроса и одним выходом, образующим выход фазового сигнала модуля для управления управляемым блоком, второй логический элемент с входом и выходом, соединенным с основным входом первого логического элемента, и третий логический элемент с основным входом, образующим вход модуля для сигнала индикации окончания переходных процессов в управляемом блоке с по крайней мере одним дополнительным входом для сигналов запроса и выходом, соединенным с входом второго логического элемента, и в котором первый и третий логические элементы выполнены в виде С-элементов Маллера, а второй логический элемент - в виде инвертора, при этом модуль выполнен с дополнительными выходами, один из которых - выход сигнала ответа на сигналы запроса с по крайней мере одного дополнительного входа в первый С-элемент Маллера - соединен с основным входом второго С-элемента Маллера и с входом модуля для сигнала индикации окончания переходных процессов в управляемом блоке, а другой - выход сигнала ответа на сигналы запроса с по крайней мере одного дополнительного входа во второй С-элемент Маллера - соединен с основным входом первого С-элемента Маллера.

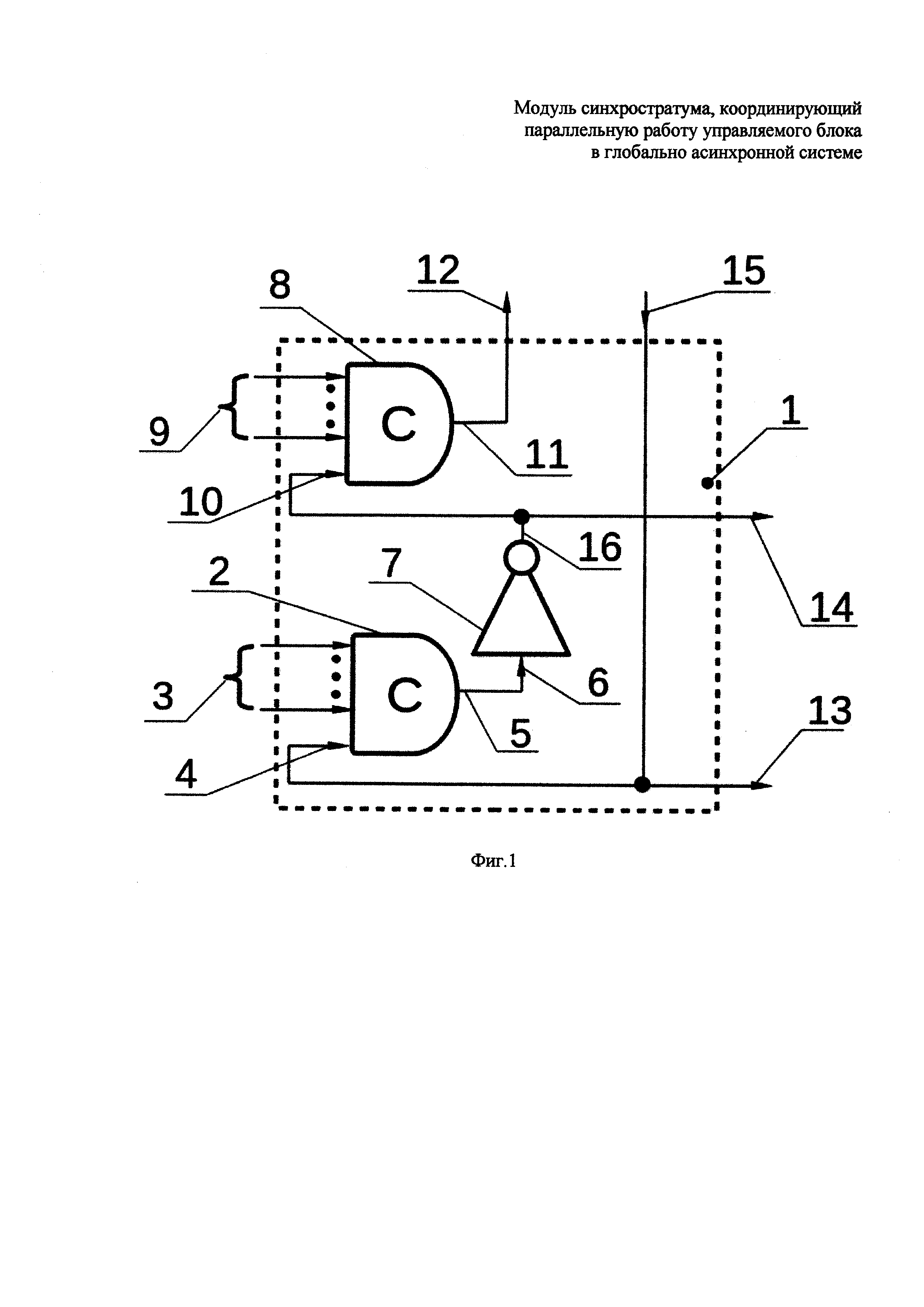

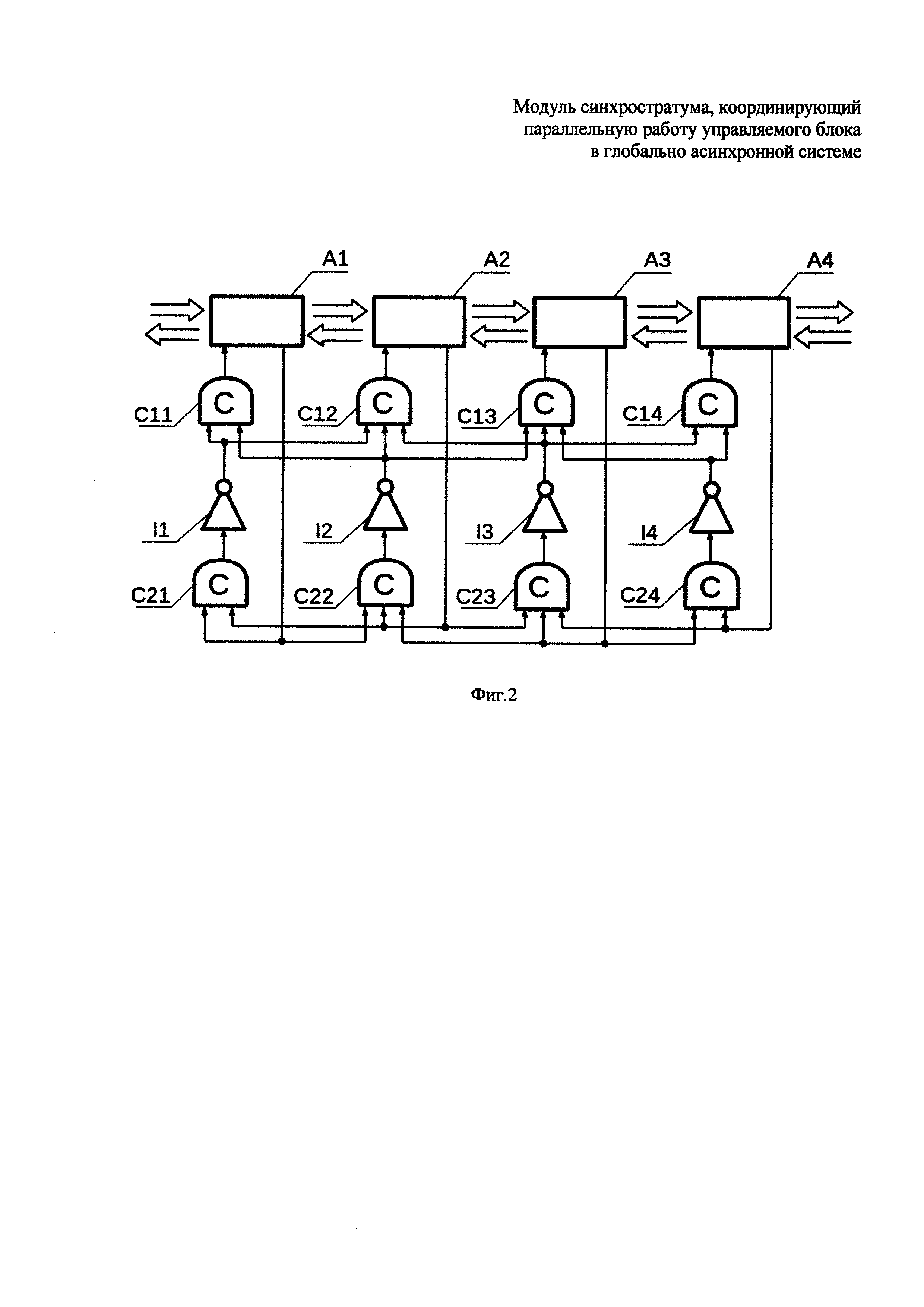

На фиг. 1 изображен патентуемый модуль синхростратума.

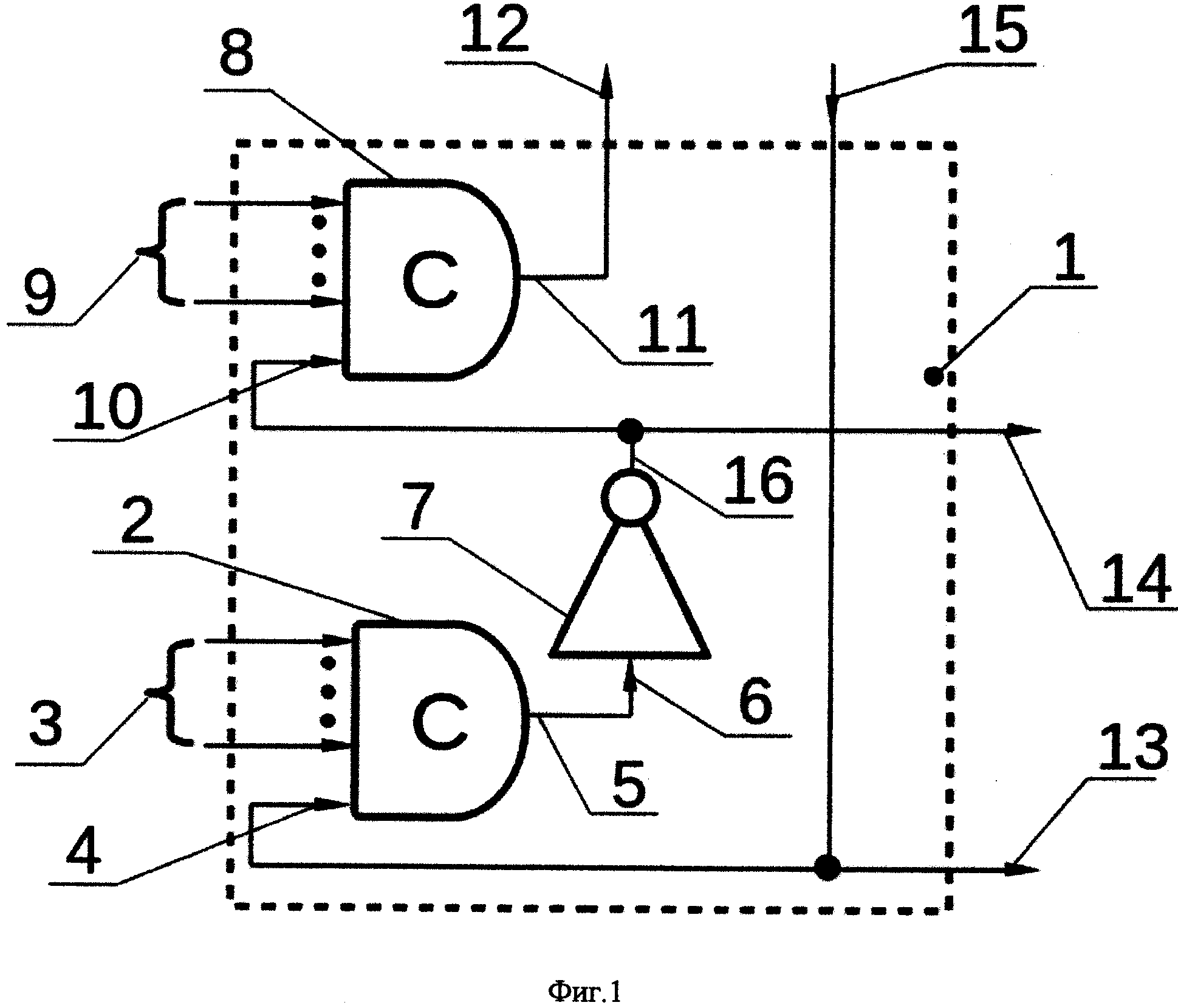

На фиг. 2 - синхростратум на основе патентуемого модуля.

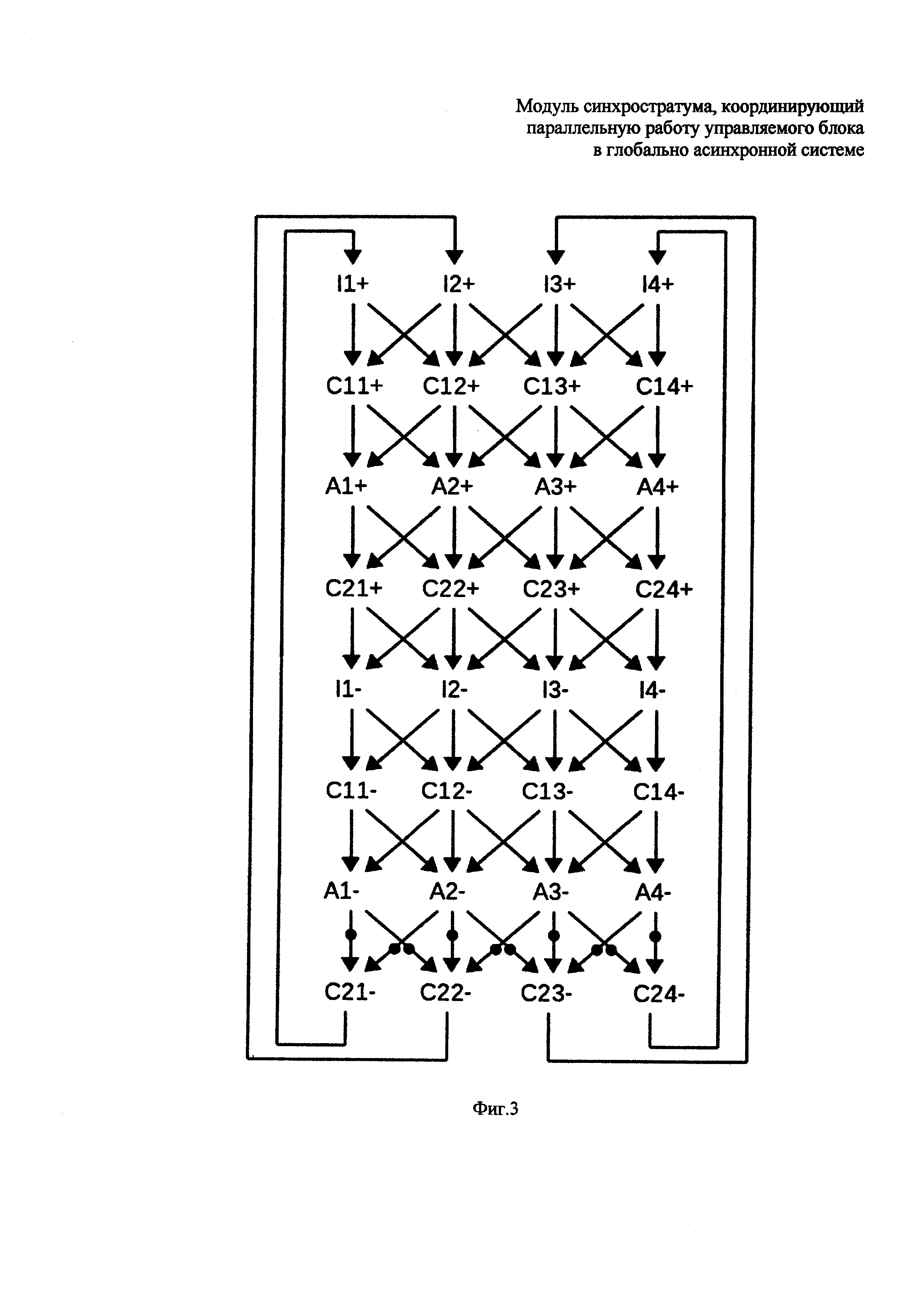

На фиг. 3 - сигнальный граф, специфицирующий работу синхростратума, изображенного на фиг. 2.

Модуль 1 синхростратума содержит два С-элемента Маллера, один из которых - С-элемент Маллера 2 - выполнен с по крайней мере одним дополнительным входом 3 сигналов запроса, с основным входом 4 и выходом 5, соединенным с входом 6 второго логического элемента, выполненного в виде инвертора 7. Другой С-элемент Маллера 8 выполнен с по крайней мере одним дополнительным входом 9 сигналов запроса, с основным входом 10 и выходом 11, образующим (соединенным с ним) выход 12 фазового сигнала модуля 1 для управления управляемым блоком (не показан). Модуль 1 имеет дополнительный выход 13 сигнала ответа на сигналы запроса по крайней мере одного дополнительного входа 9 С-элемента Маллера 8, дополнительный выход 14 сигнала ответа на сигналы запроса по крайней мере одного дополнительного входа 3 в С-элемент Маллера 2 и вход 15 сигнала индикации окончания переходных процессов в управляемом блоке (не показан), подключенный к основному входу 4 С-элемента Маллера 2 и выходу 13 модуля 1, причем выход 16 инвертора 7 соединен с основным входом 10 С-элемента Маллера 8 и выходом 14 модуля 1.

В модуле синхростратума используются С-элементы Маллера. С-элемент - это триггерное устройство, выход которого принимает значение "лог.1", если все его входы имеют значение "лог.1", и значение "лог.0", когда все его входы имеют значение "лог.0", в противном случае выход устройства сохраняет предыдущее значение. Таким образом, С-элементы выполняют функцию синхронизаторов.

Патентуемый модуль, в отличие от модуля на основе многовходовых элементов И-НЕ и ИЛИ-НЕ по прототипу, просто реализуется из двухвходовых или трехвходовых С-элементов Малера, и при этом сохраняется свойство независимости поведения модуля от их задержек. Таким образом, упрощается физическая реализация модуля в современных технологиях.

Патентуемый модуль, соответствующий вершине графа с k непосредственными соседями, соединяется с соседними модулями 4k связями, в отличие от прототипа, имеющего 6k связей, т.е. сокращается количество межмодульных связей.

Работу патентуемого модуля удобно пояснить на примере простейшего синхростратума для одномерного массива из четырех управляемых блоков, в качестве которых использованы, например, автоматы Мура (см. фиг. 2).

Автомат Мура в модели Хаффмана состоит из комбинационной схемы, реализующей функции переходов, и двух регистров: основного и вспомогательного. Работа автомата Мура состоит из двух фаз, соответствующих значениям фазового сигнала. В первой фазе вычисляется новое состояние и записывается в основной регистр, а во второй фазе происходит перепись данных из основного регистра во вспомогательный.

Перед началом работы синхростратум устанавливается в исходное состояние с помощью специального сигнала начальной установки. В начальном состоянии выходы С-элементов С21, С22, С23 и С24 имеют значение "лог.1", при этом выходы С-элементов C11, С12, С13, С14 и инверторов I1, I2, I3, I4 принимают значение "лог.0". После снятия сигнала начальной установки синхростратум начинает функционировать.

Работа синхростратума удобно описывается с помощью сигнального графа, приведенного на фиг. 3.

В этом графе все сигналы со знаком "+" и со знаком "-", за исключением сигналов Ai+, Ai-, означают переключение выходов соответствующих им элементов из состояния "лог.0" в состояние "лог.1" и из состояния "лог.1" в состояние "лог.0" соответственно. Сигналы Ai+ означают завершение переходных процессов в i-x управляемых блоках (i=1, 2, 3, 4) в фазе смены их состояний, а сигналы Ai- - завершение переходных процессов в фазе переписи информации из основных регистров во вспомогательные.

Начальная маркировка графа указана точками (маркерами) на дугах. Граф функционирует путем смены маркировок. Каждая вершина срабатывает при появлении точек на всех ее входных дугах. Срабатывание вершины является неделимым актом, который ведет к изъятию точек из всех входных дуг и размещению по одной точке в каждую выходную дугу.

Работа каждого модуля синхростратума, представленного на фиг. 2, описывается соответствующим этому модулю столбцом графа на фиг. 3. Из графа видно, что все С-элементы работают как синхронизаторы. В общем случае, когда структура связей между автоматами системы имеет вид произвольного графа, просто увеличивается число дополнительных входов С-элементов до значения степени соответствующей вершины изображающего графа. При этом сам принцип работы схемы каждого модуля не меняется.

Итак, синхростратум, построенный на основе модуля, представленного на фиг. 2, позволяет достигнуть все указанные технические результаты и, тем самым, решить поставленную задачу.

Модуль синхростратума, координирующий параллельную работу управляемого блока в глобально асинхронной системе, включающий первый логический элемент с основным входом, с по крайней мере одним дополнительным входом для сигналов запроса и одним выходом, образующим выход фазового сигнала модуля для управления управляемым блоком, второй логический элемент с входом и выходом, соединенным с основным входом первого логического элемента, и третий логический элемент с основным входом, образующим вход модуля для сигнала индикации окончания переходных процессов в управляемом блоке с по крайней мере одним дополнительным входом для сигналов запроса и выходом, соединенным с входом второго логического элемента, отличающийся тем, что первый и третий логические элементы выполнены в виде С-элементов Маллера, а второй логический элемент - в виде инвертора, при этом модуль выполнен с дополнительными выходами, один из которых - выход сигнала ответа на сигналы запроса с по крайней мере одного дополнительного входа в первый С-элемент Маллера - соединен с основным входом второго С-элемента Маллера и с входом модуля для сигнала индикации окончания переходных процессов в управляемом блоке, а другой - выход сигнала ответа на сигналы запроса с по крайней мере одного дополнительного входа во второй С-элемент Маллера - соединен с основным входом первого С-элемента Маллера.