Результат интеллектуальной деятельности: СХЕМА СДВИГОВОГО РЕГИСТРА, СХЕМА GOA И УСТРОЙСТВО ОТОБРАЖЕНИЯ И СПОСОБ ЕГО ВОЗБУЖДЕНИЯ

Вид РИД

Изобретение

ПЕРЕКРЕСТНАЯ ССЫЛКА НА РОДСТВЕННУЮ ЗАЯВКУ

[0001] Данная заявка базируется на и испрашивает приоритет китайской патентной заявки № 201720080616.3, поданной 22 января 2017 г., которая включена в данное описание в порядке ссылки в полном объеме.

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

[0002] Настоящее изобретение относится к области технологии возбуждения дисплея, и, в частности, к схеме сдвигового регистра, схеме GOA, устройству отображения и способу его возбуждения.

УРОВЕНЬ ТЕХНИКИ

[0003] Экраны жидкокристаллических дисплеев, объединенные с функцией касания для мобильных телефонов и планшетных компьютеров приобрели популярность для панелей малого и среднего размера. Однако схемы возбудителя затвора экранов жидкокристаллических дисплеев малого и среднего размера обычно выполнены в форме затвора на матрице (GOA), т.е. схемы возбудителя затвора на подложке матрицы, и реализация функции касания может подвергаться серьезному негативному влиянию, если схема GOA выводит сигнал возбуждения затвора в фазе касания, что может снижать чувствительность к касанию и даже приводить к отказу функции касания.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

[0004] Одной основной задачей настоящего изобретения является обеспечение схемы сдвигового регистра, схемы GOA и устройства отображения, которые позволяют решить проблемы в уровне техники, состоящие в том, что сигнал от контакта вывода сигнала затвора обычно принудительно снижается в фазе касания, в то время как схема GOA остается в рабочем состоянии, что увеличивает общее энергопотребление схемы GOA и отображающей панели, включающей в себя схему GOA.

[0005] Для решения вышеупомянутой задачи, один вариант осуществления настоящего изобретения обеспечивает схему сдвигового регистра, которая включает в себя подсхему сдвигового регистра с контактом вывода, подключенным к линии сигнала возбуждения затвора. Подсхема сдвигового регистра включает в себя повышающий узел, понижающий узел, схему управления повышающим узлом, схему управления понижающим узлом и схему вывода. Схема управления повышающим узлом подключена к повышающему узлу; схема управления понижающим узлом подключена к повышающему узлу и понижающему узлу, соответственно; и схема вывода подключена к повышающему узлу, понижающему узлу и контакту вывода подсхемы сдвигового регистра, соответственно. Схема сдвигового регистра дополнительно включает в себя схему управления потенциалом касания; и схема управления потенциалом касания подключена к контакту управления потенциалом касания, контакту вывода подсхемы сдвигового регистра, повышающему узлу, понижающему узлу и контакту вывода низкого уровня, соответственно; и схема управления потенциалом касания выполнена с возможностью, под управлением контакта управления потенциалом касания в фазе касания, управления подключением каждого из повышающего узла и понижающего узла к контакту вывода низкого уровня.

[0006] В одном варианте осуществления, схема управления потенциалом касания дополнительно выполнена с возможностью, под управлением контакта управления потенциалом касания в фазе касания, управления подключением контакта вывода подсхемы сдвигового регистра к контакту вывода низкого уровня.

[0007] В одном варианте осуществления, схема управления потенциалом касания включает в себя: первый транзистор управления потенциалом касания, который включает в себя первый электрод, подключенный к контакту управления потенциалом касания, второй электрод, подключенный к контакту вывода низкого уровня, и третий электрод, подключенный к контакту вывода подсхемы сдвигового регистра; второй транзистор управления потенциалом касания, который имеет первый электрод, подключенный к контакту управления потенциалом касания, второй электрод, подключенный к контакту вывода низкого уровня, и третий электрод, подключенный к повышающему узлу; и третий транзистор управления потенциалом касания, который включает в себя первый электрод, подключенный к контакту управления потенциалом касания, второй электрод, подключенный к понижающему узлу, и третий электрод, подключенный к контакту вывода низкого уровня.

[0008] В одном варианте осуществления, каждый из первого транзистора управления потенциалом касания, второго транзистора управления потенциалом касания и третьего транзистора управления потенциалом касания является транзистором N-типа, и контакт управления потенциалом касания выполнен с возможностью вывода высокого уровня в фазе касания и вывода низкого уровня в фазе отображения.

[0009] В одном варианте осуществления, каждый из первого транзистора управления потенциалом касания, второго транзистора управления потенциалом касания и третьего транзистора управления потенциалом касания является транзистором P-типа, и контакт управления потенциалом касания выполнен с возможностью вывода низкого уровня в фазе касания и вывода высокого уровня в фазе отображения.

[0010] В одном варианте осуществления, Схема управления повышающим узлом включает в себя первую подсхему управления повышающим узлом и вторую подсхему управления повышающим узлом. Первая подсхема управления повышающим узлом подключена к первому контакту управления сканированием, второму контакту управления сканированием, первому контакту уровня сканирования, второму контакту уровня сканирования и повышающему узлу, соответственно. Вторая подсхема управления повышающим узлом подключена к повышающему узлу, понижающему узлу и контакту вывода низкого уровня, соответственно.

[0011] В одном варианте осуществления, схема вывода дополнительно подключена к контакту вывода первого тактового сигнала и контакту вывода низкого уровня, соответственно; схема управления понижающим узлом включает в себя первую подсхему управления понижающим узлом и вторую подсхему управления понижающим узлом; первая подсхема управления понижающим узлом подключена к первому контакту уровня сканирования, второму контакту уровня сканирования, контакту вывода второго тактового сигнала, контакту вывода третьего тактового сигнала, контакту вывода высокого уровня, понижающему узлу и узлу управления понижением, соответственно; и вторая подсхема управления понижающим узлом подключена к повышающему узлу, понижающему узлу и контакту вывода низкого уровня, соответственно.

[0012] В одном варианте осуществления, схема вывода выполнена с возможностью, когда потенциал на повышающем узле находится на высоком уровне, управления подключением контакта вывода подсхемы сдвигового регистра к контакту вывода первого тактового сигнала; когда потенциал на понижающем узле находится на высоком уровне, управления подключением контакта вывода подсхемы сдвигового регистра к контакту вывода низкого уровня; вторая подсхема управления понижающим узлом выполнена с возможностью, когда потенциал на повышающем узле находится на высоком уровне, управления подключением понижающего узла к контакту вывода низкого уровня; и вторая подсхема управления повышающим узлом выполнена с возможностью, когда потенциал на понижающем узле находится на высоком уровне, управления подключением повышающего узла к контакту вывода низкого уровня.

[0013] В одном варианте осуществления, первая подсхема управления понижающим узлом включает в себя: первый транзистор управления понижающим узлом, который включает в себя первый электрод, подключенный к первому контакту уровня сканирования, второй электрод, подключенный к контакту вывода второго тактового сигнала, и третий электрод, подключенный к узлу управления понижением; второй транзистор управления понижающим узлом, который включает в себя первый электрод, подключенный ко второму контакту уровня сканирования, второй электрод, подключенный к узлу управления понижением, и третий электрод, подключенный к контакту вывода третьего тактового сигнала; и третий транзистор управления понижающим узлом, который включает в себя первый электрод, подключенный к узлу управления понижением, второй электрод, подключенный к контакту вывода высокого уровня и третий электрод, подключенный к понижающему узлу.

[0014] В одном варианте осуществления, вторая подсхема управления понижающим узлом включает в себя четвертый транзистор управления понижающим узлом и конденсатор управления понижающим узлом; четвертый транзистор управления понижающим узлом включает в себя первый электрод, подключенный к повышающему узлу, второй электрод, подключенный к понижающему узлу, и третий узел, подключенный к контакту вывода низкого уровня; и конденсатор управления понижающим узлом включает в себя первый конец, подключенный к контакту вывода низкого уровня, и второй конец, подключенный к понижающему узлу.

[0015] в одном варианте осуществления, схема вывода включает в себя: первый повышающий транзистор, который включает в себя первый электрод, подключенный к контакту вывода высокого уровня, и второй электрод, подключенный к повышающему узлу; второй повышающий транзистор, который включает в себя первый электрод, подключенный к третьему электроду первого повышающего транзистора, второй электрод, подключенный к контакту вывода подсхемы сдвигового регистра, и третий электрод, подключенный к контакту вывода тактового сигнала; и понижающий транзистор, который включает в себя первый электрод, подключенный к понижающему узлу, второй электрод, подключенный к контакту вывода низкого уровня, и третий электрод, подключенный к контакту вывода подсхемы сдвигового регистра.

[0016] В одном варианте осуществления, при сканировании в прямом направлении, первый контакт управления сканированием является контактом ввода, второй контакт управления сканированием является контактом сброса, первый контакт уровня сканирования является контактом высокого уровня, и второй контакт уровня сканирования является контактом вывода низкого уровня; при сканировании в обратном направлении, первый контакт управления сканированием является контактом сброса, второй контакт управления сканированием является контактом ввода, первый контакт уровня сканирования является контактом вывода низкого уровня, и второй контакт уровня сканирования является контактом вывода высокого уровня. Первая подсхема управления повышающим узлом выполнена с возможностью, под управлением контакта ввода в фазе ввода, управления потенциалом на повышающем узле для перевода его на высокий уровень; и под управлением контакта сброса в фазе сброса, управления потенциалом на повышающем узле для перевода его на низкий уровень.

[0017] В одном варианте осуществления, первая подсхема управления повышающим узлом включает в себя: первый транзистор сканирования, который включает в себя первый электрод, подключенный к первому контакту управления сканированием, второй электрод, подключенный к первому контакту уровня сканирования, и третий электрод, подключенный к повышающему узлу; и второй транзистор сканирования, который включает в себя первый электрод, подключенный ко второму контакту управления сканированием, второй электрод, подключенный к повышающему узлу, и третий электрод, подключенный ко второму контакту уровня сканирования.

[0018] В одном варианте осуществления, вторая подсхема управления повышающим узлом включает в себя транзистор управления повышающим узлом. Транзистор управления повышающим узлом включает в себя первый электрод, подключенный к понижающему узлу, второй электрод, подключенный к контакту вывода низкого уровня, и третий электрод, подключенный к повышающему узлу.

[0019] В одном варианте осуществления, схема сдвигового регистра дополнительно включает в себя зарядо-разрядную схему. Зарядо-разрядная схема подключена к повышающему узлу и контакту вывода подсхемы сдвигового регистра, соответственно.

[0020] В одном варианте осуществления, зарядо-разрядная схема включает в себя накопительный конденсатор, и накопительный конденсатор включает в себя первый конец, подключенный к повышающему узлу, и второй конец, подключенный к контакту вывода подсхемы сдвигового регистра.

[0021] Один вариант осуществления настоящего изобретения дополнительно обеспечивает схему GOA, включающую в себя множество вышеупомянутых каскадных схем сдвигового регистра.

[0022] Один вариант осуществления настоящего изобретения дополнительно обеспечивает устройство отображения, включающее в себя вышеупомянутую схему GOA.

[0023] Один вариант осуществления настоящего изобретения дополнительно обеспечивает способ возбуждения вышеупомянутого устройства отображения, включающий в себя: в фазе касания, управление, схемой управления потенциалом касания под управлением контакта управления потенциалом касания, подключением каждого из повышающего узла и понижающего узла к контакту вывода низкого уровня.

[0024] В одном варианте осуществления, способ дополнительно включает в себя: в фазе касания, управление, схемой управления потенциалом касания под управлением контакта управления потенциалом касания, подключением контакта вывода подсхемы сдвигового регистра к контакту вывода низкого уровня.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

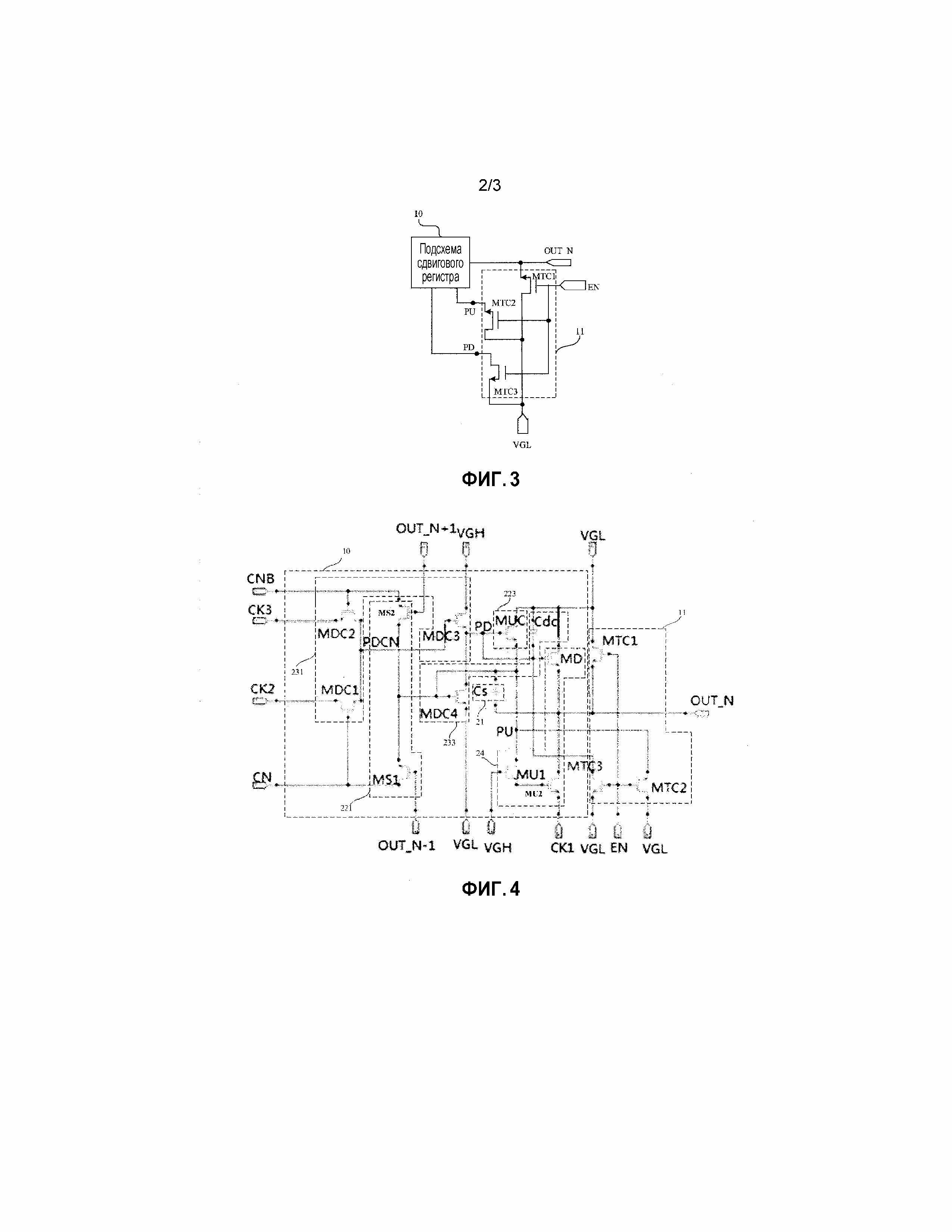

[0025] Фиг. 1 - схема схемы сдвигового регистра согласно варианту осуществления настоящего изобретения;

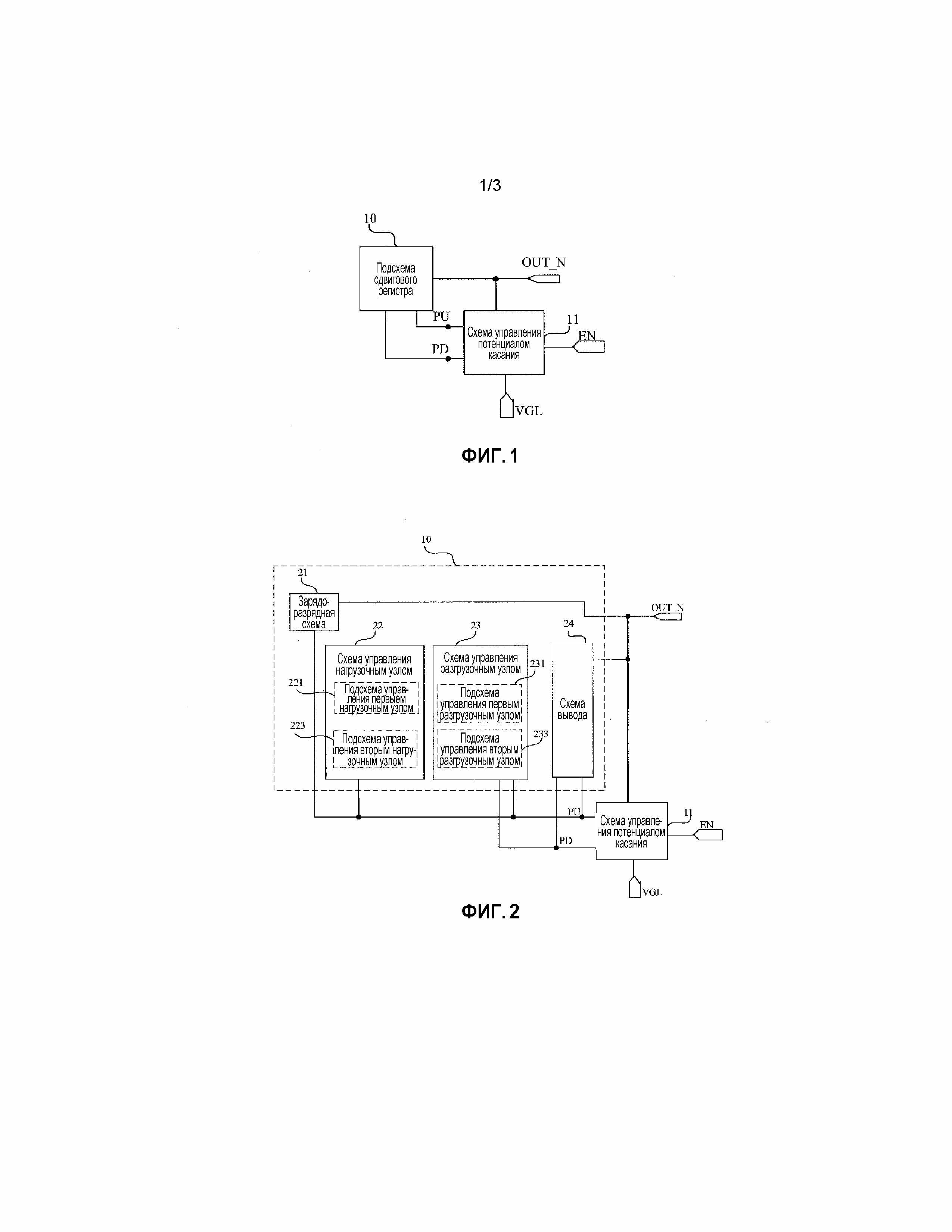

[0026] фиг. 2 - схема схемы сдвигового регистра согласно другому варианту осуществления настоящего изобретения;

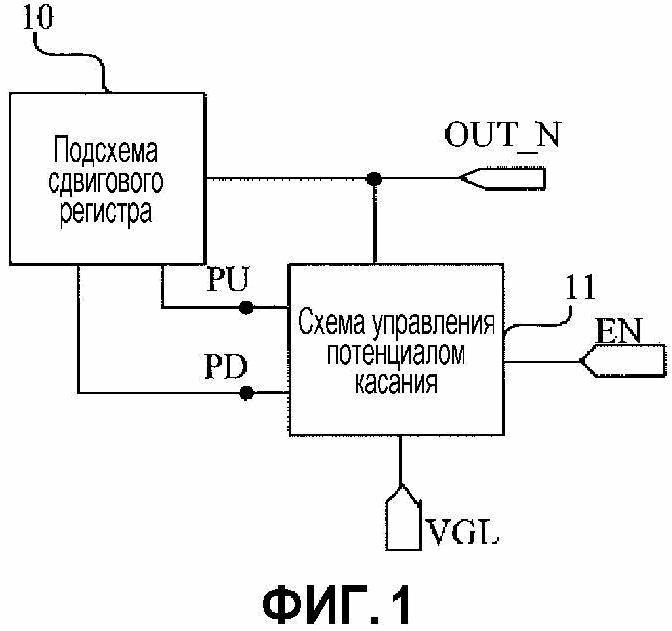

[0027] фиг. 3 - схема схемы сдвигового регистра согласно еще одному варианту осуществления настоящего изобретения;

[0028] фиг. 4 - схема схемы сдвигового регистра согласно варианту осуществления настоящего изобретения; и

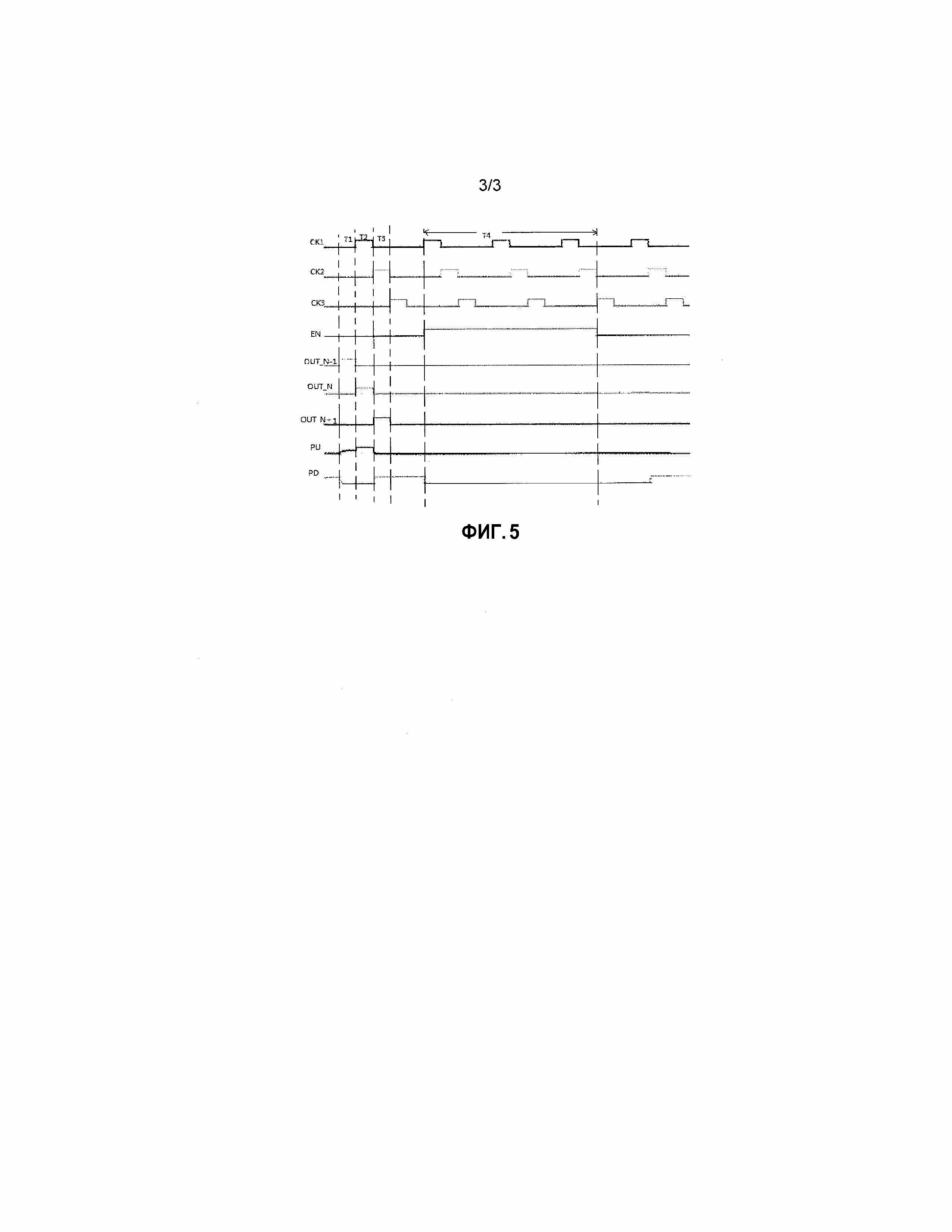

[0029] фиг. 5 - временная диаграмма схемы сдвигового регистра, показанной на фиг. 4.

ПОДРОБНОЕ ОПИСАНИЕ

[0030] Технические решения вариантов осуществления настоящего изобретения будут подробно описаны ниже совместно с чертежами вариантов осуществления. Очевидно, нижеследующие варианты осуществления относятся лишь к части, а не ко всем вариантам осуществления настоящего изобретения, и на основании этих вариантов осуществления, специалист в данной области техники может, без использования творческих способностей, получать другие варианты осуществления, которые также укладываются в объем настоящего изобретения.

[0031] Транзисторы, применяемые во всех вариантах осуществления настоящего изобретения, могут быть тонкопленочными транзисторами, полевыми транзисторами или другими устройствами с одинаковыми или аналогичными характеристиками. В некоторых вариантах осуществления настоящего изобретения, затворный электрод может именоваться первым электродом; чтобы различать два других электрода одного транзистора кроме затворного электрода, два других электрода могут именоваться вторым электродом и третьим электродом, соответственно. В фактическом применении, вторым электродом может быть стоковый электрод, и третьим электродом может быть истоковый электрод; или вторым электродом может быть истоковый электрод, и третьим электродом может быть стоковый электрод.

[0032] На фиг. 1 показана схема схемы сдвигового регистра согласно варианту осуществления настоящего изобретения. Согласно фиг. 1, схема сдвигового регистра включает в себя подсхему 10 сдвигового регистра. Контакт OUT_N вывода подсхемы 10 сдвигового регистра подключен к линии сигнала возбуждения затвора. Подсхема сдвигового регистра включает в себя повышающий узел PU, понижающий узел PD, зарядо-разрядную схему, схему управления повышающим узлом, схему управления понижающим узлом и схему вывода. Схема управления повышающим узлом подключена к повышающему узлу PU. Схема управления понижающим узлом подключена к повышающему узлу и понижающему узлу, соответственно. Зарядо-разрядная схема подключена к повышающему узлу и контакту OUT_N вывода подсхемы сдвигового регистра, соответственно. Схема вывода подключена к повышающему узлу, понижающему узлу и контакту OUT_N вывода подсхемы сдвигового регистра, соответственно.

[0033] Схема сдвигового регистра дополнительно включает в себя схему 11 управления потенциалом касания. Схема 11 управления потенциалом касания подключена к контакту EN управления потенциалом касания, контакту OUT_N вывода подсхемы 10 сдвигового регистра, повышающему узлу PU, понижающему узлу PD и контакту вывода низкого уровня для вывода низкого уровня VGL, соответственно. Схема 11 управления потенциалом касания выполнена с возможностью, под управлением контакта EN управления потенциалом касания в фазе касания, управления подключения каждого из контакта OUT_N вывода подсхемы 10 сдвигового регистра, повышающего узла PU и понижающего узла PD к контакту вывода низкого уровня для вывода низкого уровня VGL.

[0034] В подсхеме сдвигового регистра одного варианта осуществления настоящего изобретения, в фазе касания, схема 11 управления потенциалом касания может понижать каждый из сигнала возбуждения затвора, выводимого из контакта OUT_N вывода подсхемы 10 сдвигового регистра, потенциала на повышающем узле PU и потенциала на понижающем узле PD до низкого уровня. В результате, в фазе касания, схема GOA не выводит сигнал возбуждения затвора, и подсхема сдвигового регистра не находится в рабочем состоянии, что снижает общее энергопотребление схемы GOA и отображающей панели, включающей в себя схему GOA, повышая таким образом точность касания.

[0035] Для повышения точности касания, необходимо для поддержания сигнала возбуждения затвора на низком уровне в фазе касания. Другими словами, в фазе касания, схема сдвигового регистра находится в заблокированном состоянии, т.е. потенциалы на повышающем узле и понижающем узле понижаются, что снижает общее энергопотребление схемы возбуждения затвора (которая включает в себя множественные каскады схем сдвигового регистра) и отображающей панели.

[0036] Как показано на фиг. 2, подсхема 10 сдвигового регистра включает в себя повышающий узел PU, понижающий узел PD, зарядо-разрядную схему 21, схему 22 управления повышающим узлом, схему 23 управления понижающим узлом и схему 24 вывода.

[0037] Схема 22 управления повышающим узлом подключена к повышающему узлу PU.

[0038] Схема 23 управления понижающим узлом подключена к повышающему узлу и понижающему узлу, соответственно.

[0039] Зарядо-разрядная схема 21 подключена к повышающему узлу и контакту OUT_N вывода подсхемы сдвигового регистра, соответственно.

[0040] Схема 24 вывода подключена к повышающему узлу PU, понижающему узлу PD и контакту OUT_N вывода подсхемы сдвигового регистра, соответственно.

[0041] Схема сдвигового регистра дополнительно включает в себя схему управления потенциалом касания. В частности, схема управления потенциалом касания может включать в себя первый транзистор управления потенциалом касания, второй транзистор управления потенциалом касания и третий транзистор управления потенциалом касания.

[0042] Первый электрод первого транзистора управления потенциалом касания подключен к контакту управления потенциалом касания. Второй электрод первого транзистора управления потенциалом касания подключен к контакту вывода низкого уровня. Третий электрод первого транзистора управления потенциалом касания подключен к контакту вывода подсхемы сдвигового регистра.

[0043] Первый электрод второго транзистора управления потенциалом касания подключен к контакту управления потенциалом касания. Второй электрод второго транзистора управления потенциалом касания подключен к контакту вывода низкого уровня. Третий электрод второго транзистора управления потенциалом касания подключен к повышающему узлу.

[0044] Первый электрод третьего транзистора управления потенциалом касания подключен к контакту управления потенциалом касания. Второй электрод третьего транзистора управления потенциалом касания подключен к понижающему узлу. Третий электрод третьего транзистора управления потенциалом касания подключен к контакту вывода низкого уровня.

[0045] В фактическом применении, каждый из первого транзистора управления потенциалом касания, второго транзистора управления потенциалом касания и третьего транзистора управления потенциалом касания может быть транзистором N-типа, и контакт управления потенциалом касания выполнен с возможностью вывода высокого уровня в фазе касания и вывода низкого уровня в фазе отображения. Альтернативно, каждый из первого транзистора управления потенциалом касания, второго транзистора управления потенциалом касания и третьего транзистора управления потенциалом касания может быть транзистором P-типа, и контакт управления потенциалом касания выполнен с возможностью вывода низкого уровня в фазе касания и вывода высокого уровня в фазе отображения.

[0046] В фактическом применении, первым электродом может быть затворный электрод, вторым электродом может быть истоковый электрод, и третьим электродом может быть стоковый электрод. Альтернативно, первым электродом может быть затворный электрод, вторым электродом может быть стоковый электрод, и третьим электродом может быть истоковый электрод.

[0047] Как показано на фиг. 3, в подсхеме сдвигового регистра одного варианта осуществления настоящего изобретения, схема управления потенциалом касания может включать в себя первый транзистор MTC1 управления потенциалом касания, второй транзистор MTC2 управления потенциалом касания и третий транзистор MTC3 управления потенциалом касания.

[0048] Затворный электрод первого транзистора MTC1 управления потенциалом касания подключен к контакту EN управления потенциалом касания. Истоковый электрод первого транзистора MTC1 управления потенциалом касания подключен к контакту вывода низкого уровня для вывода низкого уровня VGL. Стоковый электрод первого транзистора MTC1 управления потенциалом касания подключен к контакту OUT_N вывода подсхемы 10 сдвигового регистра.

[0049] Затворный электрод второго транзистора MTC2 управления потенциалом касания подключен к контакту EN управления потенциалом касания. Истоковый электрод второго транзистора MTC2 управления потенциалом касания подключен к контакту вывода низкого уровня для вывода низкого уровня VGL. Стоковый электрод второго транзистора MTC2 управления потенциалом касания подключен к повышающему узлу PU.

[0050] Затворный электрод третьего транзистора MTC3 управления потенциалом касания подключен к контакту EN управления потенциалом касания. Истоковый электрод третьего транзистора MTC3 управления потенциалом касания подключен к понижающему узлу PD. Стоковый электрод третьего транзистора MTC3 управления потенциалом касания подключен к контакту вывода низкого уровня для вывода низкого уровня VGL.

[0051] В фактическом применении, в фазе касания, контакт EN управления потенциалом касания выводит высокий уровень, что позволяет включать MTC1, MTC2 и MTC3, и позволяет OUT_N, PU и PD принимать низкий уровень VGL.

[0052] В частности, схема вывода подключена к повышающему узлу, понижающему узлу, контакту вывода первого тактового сигнала, контакту вывода низкого уровня и контакту вывода подсхемы сдвигового регистра, соответственно.

[0053] Первый контакт зарядо-разрядной схемы подключен к повышающему узлу, и второй контакт зарядо-разрядной схемы подключен к контакту вывода подсхемы сдвигового регистра.

[0054] Схема управления повышающим узлом включает в себя первую подсхему управления повышающим узлом и вторую подсхему управления повышающим узлом. Схема управления понижающим узлом включает в себя первую подсхему управления понижающим узлом и вторую подсхему управления понижающим узлом.

[0055] Первая подсхема управления повышающим узлом подключена к первому контакту управления сканированием, второму контакту управления сканированием, первому контакту уровня сканирования, второму контакту уровня сканирования и повышающему узлу, соответственно.

[0056] Вторая подсхема управления повышающим узлом подключена к повышающему узлу, понижающему узлу и контакту вывода низкого уровня, соответственно.

[0057] Первая подсхема управления понижающим узлом подключена к первому контакту уровня сканирования, второму контакту уровня сканирования, контакту вывода второго тактового сигнала, контакту вывода третьего тактового сигнала, контакту вывода высокого уровня для вывода высокого уровня, понижающему узлу и узлу управления понижением, соответственно. Первая подсхема управления понижающим узлом выполнена с возможностью, при сканировании в прямом направлении, управления подключением узла управления понижением к контакту вывода второго тактового сигнала под управлением первого контакта уровня сканирования, и управления подключением понижающего узла к контакту вывода высокого уровня, когда контакт вывода второго тактового сигнала выводит высокий уровень; при сканировании в обратном направлении, управления подключением узла управления понижением к контакту вывода третьего тактового сигнала под управлением второго контакта уровня сканирования, и управления подключением понижающего узла к контакту вывода высокого уровня, когда контакт вывода третьего тактового сигнала выводит высокий уровень.

[0058] Вторая подсхема управления понижающим узлом подключена к повышающему узлу, понижающему узлу и контакту вывода низкого уровня, соответственно.

[0059] В частности, первая подсхема управления понижающим узлом может включать в себя: первый транзистор управления понижающим узлом, который имеет первый электрод, подключенный к первому контакту уровня сканирования, второй электрод, подключенный к контакту вывода второго тактового сигнала, и третий электрод, подключенный к узлу управления понижением; второй транзистор управления понижающим узлом, который имеет первый электрод, подключенный ко второму контакту уровня сканирования, второй электрод, подключенный к узлу управления понижением, и третий электрод, подключенный к контакту вывода третьего тактового сигнала; и третий транзистор управления понижающим узлом, который имеет первый электрод, подключенный к узлу управления понижением, второй электрод, подключенный к контакту вывода высокого уровня, и третий электрод, подключенный к понижающему узлу.

[0060] В фактическом применении, при сканировании в прямом направлении, первый контакт управления сканированием является контактом ввода, второй контакт управления сканированием является контактом сброса, первый контакт уровня сканирования является контактом высокого уровня, и второй контакт уровня сканирования является контактом вывода низкого уровня; при сканировании в обратном направлении, первый контакт управления сканированием является контактом сброса, второй контакт управления сканированием является контактом ввода, первый контакт уровня сканирования является контактом вывода низкого уровня, и второй контакт уровня сканирования является контактом вывода высокого уровня.

[0061] Первая подсхема управления повышающим узлом выполнена с возможностью, под управлением контакта ввода в фазе ввода, управления потенциалом на повышающем узле для перевода его на высокий уровень; и под управлением контакта сброса в фазе сброса, управления потенциалом на повышающем узле для перевода его на низкий уровень.

[0062] В частности, первая подсхема управления повышающим узлом может включать в себя: первый транзистор сканирования, который имеет первый электрод, подключенный к первому контакту управления сканированием, второй электрод, подключенный к первому контакту уровня сканирования, и третий электрод, подключенный к повышающему узлу; и второй транзистор сканирования, который имеет первый электрод, подключенный ко второму контакту управления сканированием, второй электрод, подключенный к повышающему узлу, и третий электрод, подключенный ко второму контакту уровня сканирования.

[0063] В частности, схема вывода выполнена с возможностью, когда потенциал на повышающем узле находится на высоком уровне, управления подключением контакта вывода подсхемы сдвигового регистра к контакту вывода первого тактового сигнала; когда потенциал на понижающем узле находится на высоком уровне, управления подключением контакта вывода подсхемы сдвигового регистра к контакту вывода низкого уровня.

[0064] Вторая подсхема управления понижающим узлом выполнена с возможностью, когда потенциал на повышающем узле находится на высоком уровне, управления подключением понижающего узла к контакту вывода низкого уровня.

[0065] Вторая подсхема управления повышающим узлом выполнена с возможностью, когда потенциал на понижающем узле находится на высоком уровне, управления подключением повышающего узла к контакту вывода низкого уровня.

[0066] В частности, схема вывода может включать в себя: первый повышающий транзистор, который имеет первый электрод, подключенный к контакту вывода высокого уровня, и второй электрод, подключенный к повышающему узлу; второй повышающий транзистор, который имеет первый электрод, подключенный к третьему электроду первого повышающего транзистора, второй электрод, подключенный к контакту вывода подсхемы сдвигового регистра, и третий электрод, подключенный к контакту вывода тактового сигнала; и понижающий транзистор, который имеет первый электрод, подключенный к понижающему узлу, второй электрод, подключенный к контакту вывода низкого уровня, и третий электрод, подключенный к контакту вывода подсхемы сдвигового регистра.

[0067] Вторая подсхема управления понижающим узлом может включать в себя: четвертый транзистор управления понижающим узлом, который имеет первый электрод, подключенный к повышающему узлу, второй электрод, подключенный к понижающему узлу, и третий электрод, подключенный к контакту вывода низкого уровня; и конденсатор управления понижающим узлом, который имеет первый конец, подключенный к контакту вывода низкого уровня, и второй конец, подключенный к понижающему узлу.

[0068] Вторая подсхема управления повышающим узлом может включать в себя: транзистор управления повышающим узлом, который имеет первый электрод, подключенный к понижающему узлу, второй электрод, подключенный к контакту вывода низкого уровня, и третий электрод, подключенный к повышающему узлу.

[0069] Зарядо-разрядная схема может включать в себя накопительный конденсатор, который имеет первый конец, подключенный к повышающему узлу, и второй конец, подключенный к контакту вывода подсхемы сдвигового регистра.

[0070] Схема сдвигового регистра одного варианта осуществления настоящего изобретения будет описана ниже на примере.

[0071] Как показано на фиг. 2 и фиг. 4, схема сдвигового регистра одного варианта осуществления настоящего изобретения включает в себя подсхему 10 сдвигового регистра и схему 11 управления потенциалом касания.

[0072] Схема 11 управления потенциалом касания включает в себя: первый транзистор MTC1 управления потенциалом касания, второй транзистор MTC2 управления потенциалом касания и третий транзистор MTC3 управления потенциалом касания.

[0073] Затворный электрод первого транзистора MTC1 управления потенциалом касания подключен к контакту EN управления потенциалом касания. Истоковый электрод первого транзистора MTC1 управления потенциалом касания подключен к контакту вывода низкого уровня для вывода низкого уровня VGL. Стоковый электрод первого транзистора MTC1 управления потенциалом касания подключен к контакту OUT_N вывода подсхемы сдвигового регистра.

[0074] Затворный электрод второго транзистора MTC2 управления потенциалом касания подключен к контакту EN управления потенциалом касания. Истоковый электрод второго транзистора MTC2 управления потенциалом касания подключен к контакту вывода низкого уровня для вывода низкого уровня VGL. Стоковый электрод второго транзистора MTC2 управления потенциалом касания подключен к повышающему узлу PU.

[0075] Затворный электрод третьего транзистора MTC3 управления потенциалом касания подключен к контакту EN управления потенциалом касания. Истоковый электрод третьего транзистора MTC3 управления потенциалом касания подключен к понижающему узлу PD. Стоковый электрод третьего транзистора MTC3 управления потенциалом касания подключен к контакту вывода низкого уровня для вывода низкого уровня VGL.

[0076] Как показано на фиг. 2 и фиг. 4, подсхема 10 сдвигового регистра включает в себя повышающий узел PU, понижающий узел PD, зарядо-разрядную схему 21, схему 22 управления повышающим узлом, схему 23 управления понижающим узлом и схему 24 вывода. Схема 22 управления повышающим узлом включает в себя первую подсхему 221 управления повышающим узлом и вторую подсхему 223 управления повышающим узлом. Схема 23 управления понижающим узлом включает в себя первую подсхему 231 управления понижающим узлом и вторую подсхему 233 управления понижающим узлом.

[0077] Как показано на фиг. 4, первая подсхема 231 управления понижающим узлом включает в себя: первый транзистор MDC1 управления понижающим узлом, второй транзистор MDC2 управления понижающим узлом и третий транзистор MDC3 управления понижающим узлом.

[0078] Затворный электрод первого транзистора MDC1 управления понижающим узлом подключен к первому контакту CN уровня сканирования. Истоковый электрод первого транзистора MDC1 управления понижающим узлом подключен к контакту вывода второго тактового сигнала CK2. Стоковый электрод первого транзистора MDC1 управления понижающим узлом подключен к узлу управления понижением PDCN.

[0079] Затворный электрод второго транзистора MDC2 управления понижающим узлом подключен ко второму контакту уровня сканирования CNB. Истоковый электрод второго транзистора MDC2 управления понижающим узлом подключен к узлу управления понижением PDCN. Стоковый электрод второго транзистора MDC2 управления понижающим узлом подключен к контакту вывода третьего тактового сигнала CK3.

[0080] Затворный электрод третьего транзистора MDC3 управления понижающим узлом подключен к узлу управления понижением PDCN. Истоковый электрод третьего транзистора MDC3 управления понижающим узлом подключен к контакту вывода высокого уровня для вывода высокого уровня VGH. Стоковый электрод третьего транзистора MDC3 управления понижающим узлом подключен к понижающему узлу PD.

[0081] Первая подсхема 221 управления повышающим узлом включает в себя: первый транзистор MS1 сканирования и второй транзистор MS2 сканирования.

[0082] Затворный электрод первого транзистора MS1 сканирования подключен к контакту OUT_N-1 вывода. Истоковый электрод первого транзистора MS1 сканирования подключен к первому контакту CN уровня сканирования. Стоковый электрод первого транзистора MS1 сканирования подключен к повышающему узлу PU.

[0083] Затворный электрод второго транзистора MS2 сканирования подключен к контакту OUT_N+1 сброса. Истоковый электрод второго транзистора MS2 сканирования подключен к повышающему узлу PU. Стоковый электрод второго транзистора MS2 сканирования подключен ко второму контакту уровня сканирования CNB.

[0084] Схема 24 вывода включает в себя: первый повышающий транзистор MU1, второй повышающий транзистор MU2 и понижающий транзистор MD.

[0085] Затворный электрод первого повышающего транзистора MU1 подключен к контакту вывода высокого уровня для вывода высокого уровня VGH. Истоковый электрод первого повышающего транзистора MU1 подключен к повышающему узлу PU.

[0086] Затворный электрод второго повышающего транзистора MU2 подключен к стоковому электроду первого повышающего транзистора MU1. Истоковый электрод второго повышающего транзистора MU2 подключен к контакту OUT_N вывода подсхемы сдвигового регистра. Стоковый электрод второго повышающего транзистора MU2 подключен к контакту вывода тактового сигнала CK1.

[0087] Затворный электрод понижающего транзистора MD подключен к понижающему узлу PD. Истоковый электрод понижающего транзистора MD подключен к контакту вывода низкого уровня для вывода низкого уровня VGL. Стоковый электрод понижающего транзистора MD подключен к контакту OUT_N вывода подсхемы сдвигового регистра.

[0088] Вторая подсхема 233 управления понижающим узлом включает в себя: четвертый транзистор MDC4 управления понижающим узлом и конденсатор Cdc управления понижающим узлом. Затворный электрод четвертого транзистора MDC4 управления понижающим узлом подключен к повышающему узлу PU. Истоковый электрод четвертого транзистора MDC4 управления понижающим узлом подключен к понижающему узлу PD. Стоковый электрод четвертого транзистора MDC4 управления понижающим узлом подключен к контакту вывода низкого уровня для вывода низкого уровня VGL.

[0089] Первый конец конденсатора Cdc управления понижающим узлом подключен к контакту вывода низкого уровня для вывода низкого уровня VGL. Второй конец конденсатора Cdc управления понижающим узлом подключен к понижающему узлу PD.

[0090] Вторая подсхема 223 управления повышающим узлом включает в себя транзистор MUC управления повышающим узлом. Затворный электрод транзистора MUC управления повышающим узлом подключен к понижающему узлу PD. Истоковый электрод транзистора MUC управления повышающим узлом подключен к контакту вывода низкого уровня для вывода низкого уровня VGL. Стоковый электрод транзистора MUC управления повышающим узлом подключен к повышающему узлу PU.

[0091] Зарядо-разрядная схема 21 включает в себя накопительный конденсатор Cs. Накопительный конденсатор Cs имеет первый конец, подключенный к повышающему узлу PU, и второй конец, подключенный к контакту OUT_N вывода подсхемы сдвигового регистра.

[0092] В схеме сдвигового регистра одного варианта осуществления настоящего изобретения, как показано на фиг. 4, первый контакт CN уровня сканирования выводит высокий уровень, и второй контакт уровня сканирования CNB выводит низкий уровень.

[0093] На фиг. 5 показана временная диаграмма схемы сдвигового регистра, показанной на фиг. 4. Как показано на фиг. 5, в первой фазе T1, т.е. фазе ввода, контакт OUT_N-1 вывода выводит высокий уровень, первый транзистор MS1 сканирования включается, потенциал на повышающем узле PU растет, четвертый транзистор MDC4 управления понижающим узлом включается, потенциал на понижающем узле PD понижается, и накопительный конденсатор Cs заряжается.

[0094] Во второй фазе T2, т.е. фазе вывода, первый транзистор MS1 сканирования отключается, потенциал на повышающем узле PU непрерывно растет вследствие эффекта вольтодобавки накопительного конденсатора Cs, второй повышающий транзистор MU2 включается, контакт OUT_N вывода подсхемы сдвигового регистра выводит высокий уровень, потенциал на понижающем узле PD все еще понижен.

[0095] В третьей фазе T3, т.е. фазе сброса, второй транзистор MS2 сканирования включается, потенциал на повышающем узле PU все еще понижен, поскольку контакт вывода второго тактового сигнала CK2 выводит высокий уровень, потенциал на узле PDCN управления понижением находится на высоком уровне, третий транзистор MDC3 управления понижающим узлом включается, потенциал на понижающем узле PD повышается, оба четвертый транзистор MDC4 управления понижающим узлом и понижающий транзистор MD включаются, потенциал на повышающем узле PU и сигнал возбуждения затвора, выводимый из контакта OUT_N вывода подсхемы сдвигового регистра, понижаются, и конденсатор Cdc управления понижающим узлом заряжается.

[0096] В четвертой фазе T4, т.е. фазе касания, контакт EN управления потенциалом касания выводит высокий уровень, каждый из первого транзистора MTC1 управления потенциалом касания, второго транзистора MTC2 управления потенциалом касания и третьего транзистора MTC3 управления потенциалом касания включается, и каждый из сигнала возбуждения затвора, выводимого из контакта OUT_N вывода подсхемы сдвигового регистра, потенциал на повышающем узле PU и потенциал на понижающем узле PD понижается. Это может не только повышать чувствительность к касанию, но и снижать энергопотребление отображающей панели.

[0097] Схема GOA одного варианта осуществления настоящего изобретения включает в себя множественные вышеописанные каскадные схемы сдвигового регистра.

[0098] Устройство отображения одного варианта осуществления настоящего изобретения включает в себя вышеупомянутую схему возбуждения затвора.

[0099] Выше описаны предпочтительные варианты осуществления настоящего изобретения. Следует отметить, что специалисты в данной области техники могут предлагать различные усовершенствования и замены, не выходя за рамки принципа изобретения, и все эти усовершенствования и замены попадают в объем защиты настоящего изобретения.