Результат интеллектуальной деятельности: ДИНАМИЧЕСКИЙ D-ТРИГГЕР

Вид РИД

Изобретение

Изобретение относится к области цифровой микроэлектроники, а именно к динамическим D-триггерам, и предназначено для использования в качестве конструктивного элемента быстродействующих цифровых интегральных схем. Например, в качестве цифрового библиотечного элемента в системах автоматизированного проектирования аналого-цифровых устройств.

Триггер синхронизируется тактовым сигналом CLK и выполняет автоматную функцию задержки на 1 такт: Qt+1=Dl, где D - информационный вход, Q - выход триггера.

Входной D и выходной Q сигналы изменяются по положительному перепаду CLK.

Высокие скоростные характеристики динамических триггеров обусловлены динамическим хранением информации на "паразитных" емкостях - в сочетании с каскадами "сквозного" тока (с "отношением крутизн").

Наличие нижней граничной частоты исключает применение динамического триггера в качестве элемента длительного хранения информации.

Важными характеристиками для оценки конструкции динамического триггера являются его быстродействие и площадь на кристалле. Данные характеристики взаимно обратимы: при постоянной нагрузке увеличение площади способствует повышению быстродействия.

Объективная информация для оценки содержится в принципиальной (электрической) схеме триггера. Стандартный интегральный КМОП транзистор с n-каналом характеризуется током, превышающим приблизительно в 3 раза ток p-канального КМОП транзистора равных размеров. Соответственно, для выравнивания времени разряда "паразитной" емкости через n-канал и времени заряда через p-канал в ключевой схеме требуется отношение размеров Wp/Wn≈3.

Совокупная характеристика "быстродействие/площадь" существенно ухудшается в зарядной цепи с последовательно соединенными p-канальными транзисторами. Для поддержания нагрузочной способности (быстродействия) двухтранзисторной последовательной цепи требуется вдвое увеличить размер каждого транзистора, и т.п. Площадь такой p-канальной конструкции равна площади двенадцати одиночных n-канальных транзисторов. Пропорциональное увеличение нагрузочной емкости попутно снижает динамику n-канальной цепи разряда.

Для ключевых каскадов с "отношением крутизн" характерны статические состояния со "сквозным" током: одновременно открыты зарядная (p) и разрядная (n) цепи. Логическое значение выхода зависит от доминации: 0 - доминирует n-канал, 1 - доминирует p-канал (отклонение логических уровней не превышает порогового напряжения транзистора). Для доминации n-канала достаточно равных размеров пир транзисторов: эквивалентный ток разряда равен 2/3 тока In (n-канал). Аналогичная доминация p-канала требует Wp/Wn«9, что отрицательно сказывается на характеристиках "быстродействие/площадь".

В общем случае "сквозной" ток (в том числе динамический) снижает быстродействие каскада. Каскад с раздельным управлением транзисторами n, p позволяет исключить сквозной ток, что обеспечивает максимальное быстродействие ключа и преимущество даже перед обычным инвертором.

Зарядно-разрядное время в отдельных каскадах триггера ограничивается длительностью полутакта (логические CLK=0 или CLK=1). В существующих конструкциях имеются каскады, требующие переключения на интервале задержки входного перепада D относительно CLK, что может быть значительно меньше полутакта и критически отражается на быстродействии.

Указанные особенности приняты во внимание при разработке заявленного D-триггера и сравнительной оценке существующих технических решений.

Дополнительное качество конструкции заявленного D-триггера (присущее некоторым аналогам и не связанное с целью изобретения) - простота модификаций, обеспечивающих введение логических функций И, ИЛИ, ИСКЛ-ИЛИ на входе триггера без существенной потери быстродействия. Открывается возможность разработки семейства библиотечных динамических триггеров с встроенными логическими функциями.

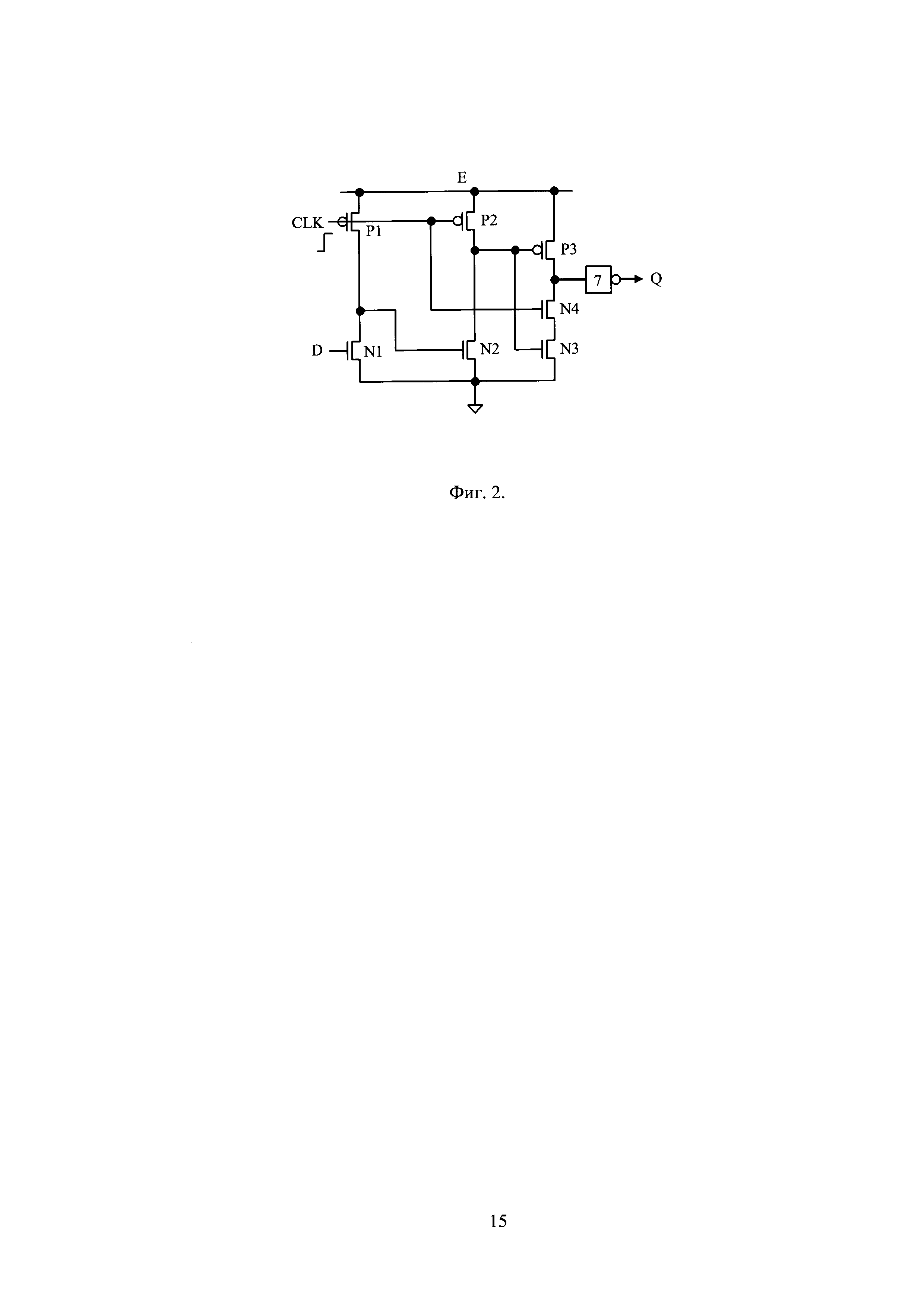

В качестве аналога заявленного изобретения рассмотрим простую конструкцию динамического D-триггера с инверсным выходом  , представленную на Фиг. 1 [1]. Обычной практикой является подключение дополнительного выходного инвертора, что поддерживает прямую функцию D-триггера.

, представленную на Фиг. 1 [1]. Обычной практикой является подключение дополнительного выходного инвертора, что поддерживает прямую функцию D-триггера.

Перепады данных D, Q синхронизируются отрицательными перепадами CLK.

Представлены логические модификации D-триггера: замена Р1 группой p-канальных транзисторов. Возможности модификации ограничены из-за существенного снижения быстродействия и увеличения занимаемой площади (не решает этой проблемы зеркальная взаимная замена n, p и шин "земля, питание").

Каждый из 3-х каскадов имеет состояния статического "сквозного" тока (в полутактах) с доминацией n-канального транзистора.

В полутакте CLK=1 выходные напряжения 1-го (U1) и 2-го (U2) каскадов устанавливаются на низком уровне (независимо от значения D): не выше порогового напряжения транзистора. 3-й каскад - в состоянии динамического хранения информации: транзисторы N3, Р3 заперты.

В полутакте CLK=0 в каскадах устанавливаются напряжения, соответствующие вновь защелкнутым данным. Длина параллельных цепей, распространяющих активный (отрицательный) перепад CLK, не превышает 2-х каскадов. Особенности процесса установления напряжений позволяют определить требования к динамическим параметрам отдельных каскадов и D-триггера в целом, а также оценить конструкцию по характеристикам "быстродействие/площадь".

Время формирования положительного перепада U1 не превышает задержку D относительно CLK (положительный перепад D прерывает процесс повышения U1). Это указывает на высокие требования быстродействия транзистора Р1 (задержка D может быть существенно меньше длительности полутакта).

При D=0 (полутакт CLK=0) транзистор Р2 запирается раньше, чем отпирается N3: гонки напряжений U1, U2 (повышение U2 является фиксируемой помехой). Это означает: скорость повышения U1 существенно выше скорости повышения U2 (условно Р1>>Р2 и абсолютно при равенстве узловых "паразитных" емкостей).

При D=l (полутакт CLK=0) процесс завершается установкой U3 ( ) на значение логического нуля в состоянии статического "сквозного" тока. Однако, на начальном этапе (в процессе формирования положительного перепада U2 после активного перепада CLK) на выходе

) на значение логического нуля в состоянии статического "сквозного" тока. Однако, на начальном этапе (в процессе формирования положительного перепада U2 после активного перепада CLK) на выходе  формируется динамическая помеха положительной полярности: Р3 открыт полностью, N3 заперт или открыт не полностью. В гонке нарастающих напряжений U2, U3 малая амплитуда помехи обеспечивается высокой скоростью повышения U2: условно Р2>>Р3.

формируется динамическая помеха положительной полярности: Р3 открыт полностью, N3 заперт или открыт не полностью. В гонке нарастающих напряжений U2, U3 малая амплитуда помехи обеспечивается высокой скоростью повышения U2: условно Р2>>Р3.

Задержка перепадов  относительно CLK - 1 или 2 каскада (положительный или отрицательный перепад

относительно CLK - 1 или 2 каскада (положительный или отрицательный перепад  ). Дополнительный выходной инвертор Q увеличивает задержку на 1 каскад.

). Дополнительный выходной инвертор Q увеличивает задержку на 1 каскад.

Система условных неравенств Р1>>Р2>>Р3 показывает невысокое качество D-триггера первого аналога по совокупному критерию "быстродействие/площадь". Кроме того, каждый из каскадов прохождения перепадов CLK на выход  работает со "сквозным" током, что препятствует достижению максимального быстродействия.

работает со "сквозным" током, что препятствует достижению максимального быстродействия.

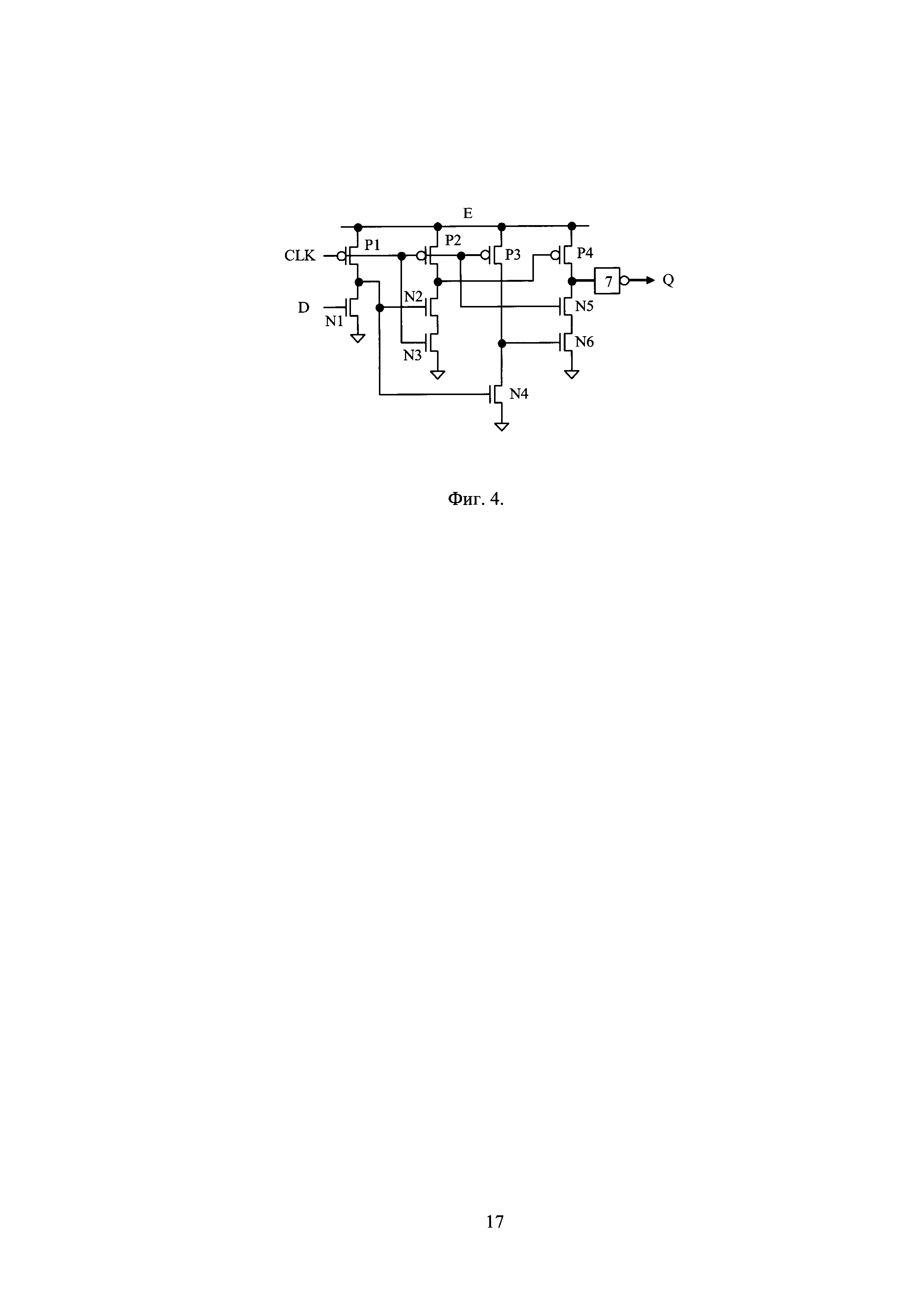

Вторым аналогом заявленного изобретения является динамический D-триггер, представленный на Фиг. 2 [2].

Перепады данных D, Q синхронизируются положительными перепадами CLK.

Логические модификации D-триггера: замена N1 группой n-канальных транзисторов. Возможности модификации благоприятны: n-канальные транзисторы обладают высоким быстродействием при минимальной занимаемой площади.

1-й и 2-й каскады имеют состояния (в полутактах) со статическим "сквозным" током.

В 1-ом каскаде доминирует n-канальный транзистор N1: в полутакте CLK=0 при логическом D=l транзисторы N1, Р1 открыты (статический "сквозной" ток) - выходное напряжение U1 каскада устанавливается на уровне не выше порогового напряжения n-канала (N2 заперт).

Во 2-м каскаде доминирует p-канальный транзистор Р2: в полутакте CLK=0 при логическом D=0 (U1=E) транзисторы N2, Р2 открыты (статический "сквозной" ток) - выходное напряжение U2 каскада устанавливается на уровне не ниже E-Uпор, где Uпор - порогового напряжение p-канала (Р3 заперт).

3-й каскад в полутакте CLK=0 имеет состояние динамического хранения данных: N4, Р3 заперты (не зависимо от D).

В полутакте CLK=1 в каскадах устанавливаются напряжения, соответствующие вновь защелкнутым данным. Длина параллельных цепей, распространяющих активный (положительный) перепад CLK, не превышает 2-х каскадов (+выходной инвертор).

Основным недостатком динамического D-триггера второго аналога является низкое быстродействие или большая занимаемая площадь интегральной схемы ввиду наличия каскада с доминирующим p-канальным транзистором. Кроме того, выходной каскад (N3, Р3) формирует перепады напряжения при наличии динамического "сквозного" тока, что препятствует достижению максимального быстродействия.

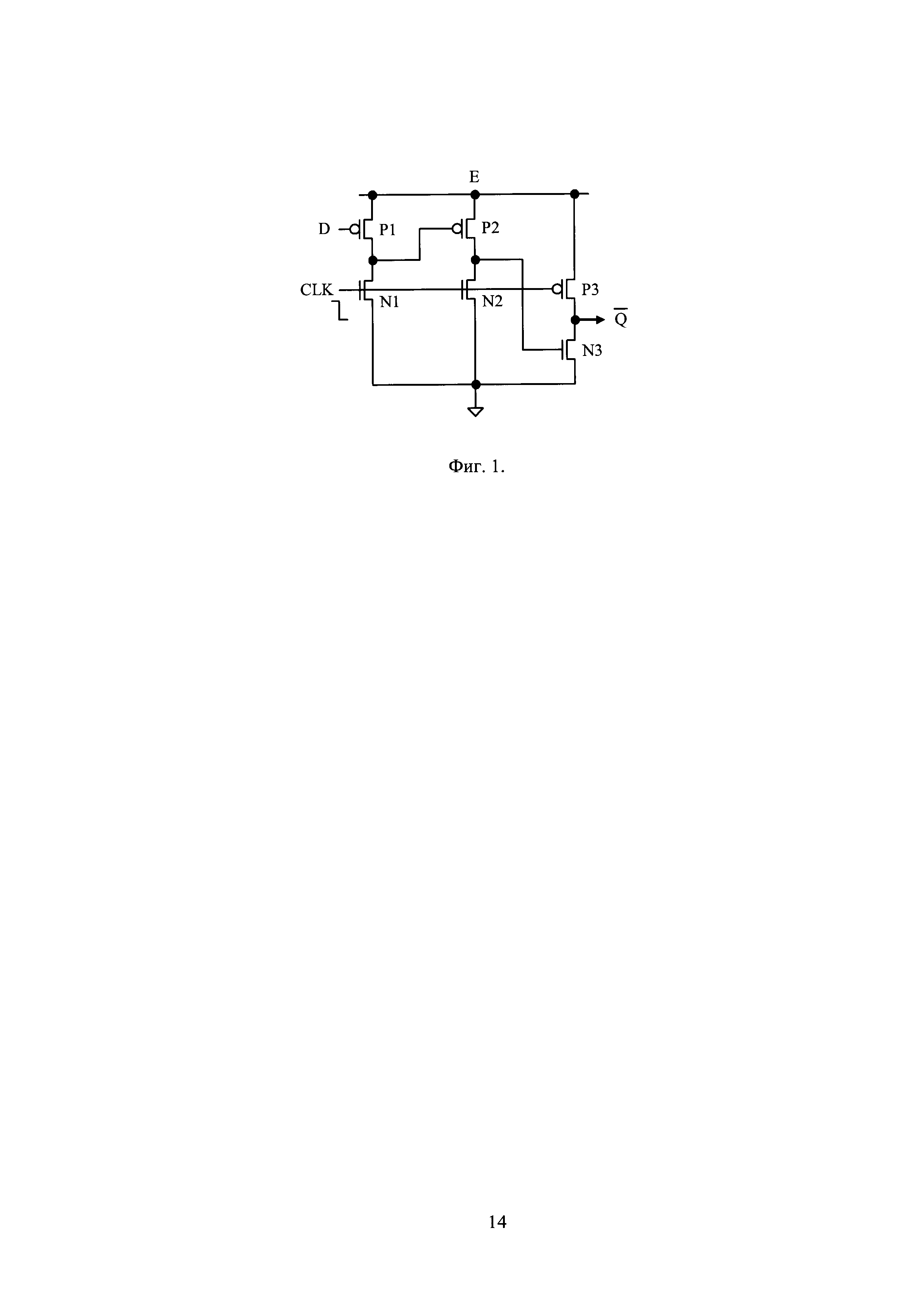

Наиболее близким к заявленному изобретению является высокочастотный динамический D-триггер [3], схема которого показана на Фиг. 3.

В состоянии CLK=0 значение D и Q не изменяется. Первый каскад Р1, N1 работает как инвертор с отношением крутизн: доминирует n-канальный транзистор N1. Входной узел выходного инвертора 7 - в подвешенном состоянии (заперты транзисторы Р4, N6): динамическое хранение старой информации.

По положительному перепаду CLK (CLK=1) исходное значение D защелкивается во внутренних узлах и поступает на выход Q триггера в качестве нового значения. Для этого необходимо, чтобы отрицательный перепад на выходе 2-го каскада (сток N2) формировался раньше, чем отрицательный перепад на выходе 1-го каскада (сток N1). Этому способствует задержка перепадов D относительно CLK, аналогичная задержке перепадов Q.

Длина параллельных цепей, распространяющих активный (положительный) перепад CLK, не превышает 2-х каскадов (+выходной инвертор).

В состоянии CLK=1 динамическое хранение информации (в зависимости от D) осуществляется в первом и втором каскадах. Выход 4-го каскада (вход инвертора 7) активно подключается к шине питания или "земля".

Данный D-триггер выбран в качестве прототипа заявленного изобретения.

Недостаток D-триггера прототипа связан с тем, что положительный перепад на входе D отрицательно воздействует (с задержкой) на состояние 4-го каскада (Р4, N5, N6), уже установленного на значение Q=0: отпирает транзистор N5. В результате оказываются открытыми все транзисторы (Р4, N5, N6) выходного каскада в условиях формирования высокого уровня напряжения - доминация транзистора Р4.

Доминация p-канального транзистора в цифровых каскадах со сквозным током (с учетом современной интегральной технологии) требует увеличения занимаемой им площади или ведет к понижению его быстродействия.

Техническим результатом заявленного изобретения является создание динамического D-триггера с малой занимаемой площадью и с увеличенным быстродействием, за счет работы выходного каскада, состоящего из четвертого p-канального транзистора и пятого и шестого n-канальных транзисторов, без "сквозного" тока.

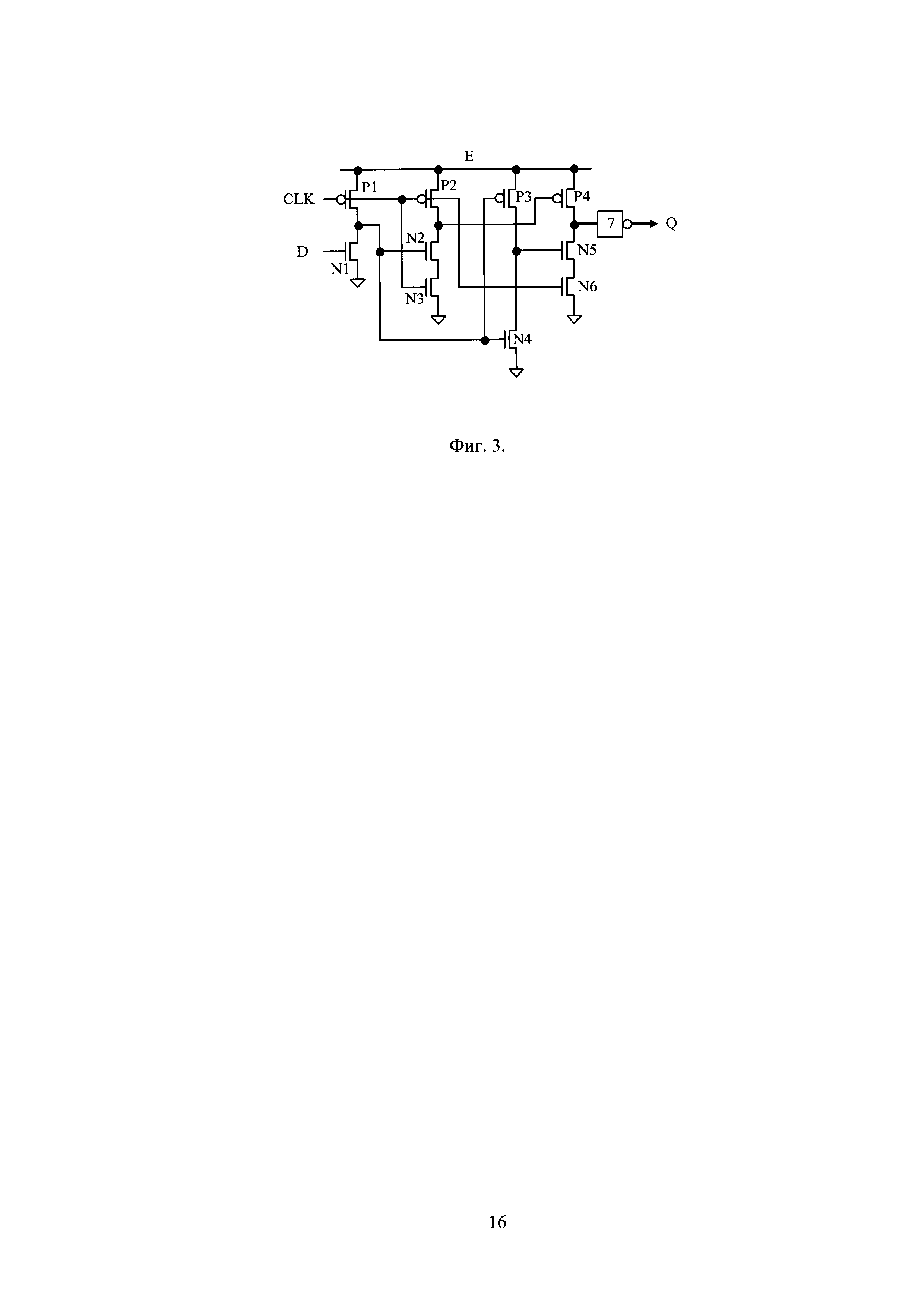

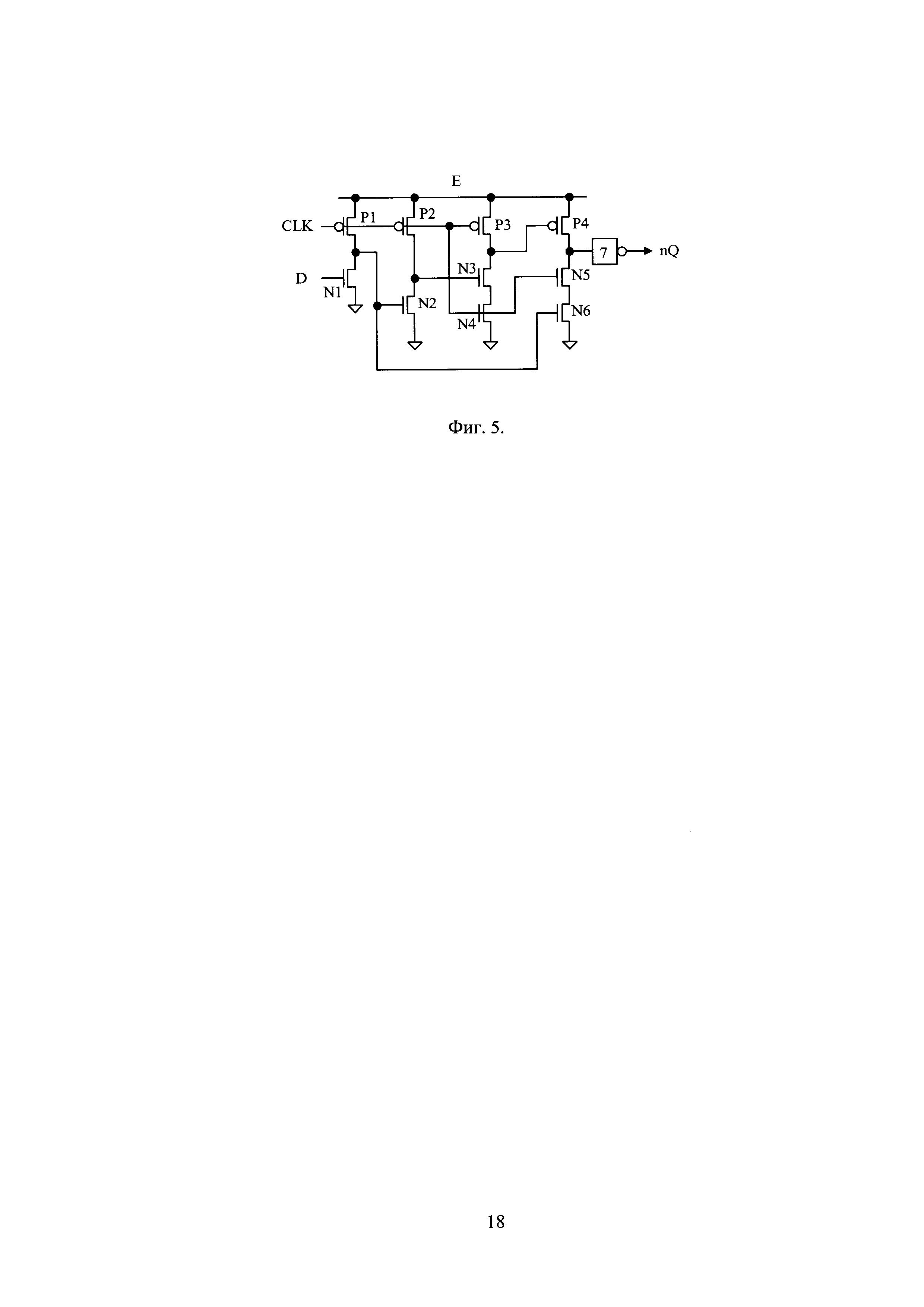

Во время работы варианта выполнения заявленного D-триггера с прямым выходом Q (Фиг. 4) в первом (транзисторы Р1, N1 - как и в прототипе) и третьем (Р3, N4) каскадах доминируют n-канальные транзисторы N1, N4: в идеале, при полностью открытых транзисторах, выходное напряжение каскада не должно превышать порогового напряжения n-канала. В состоянии CLK=1, помимо 1-го и 2-го каскадов (транзисторы Р1, N1 и Р2, N2, N3 - как в прототипе), динамическое хранение обеспечивает 3-й каскад (транзисторы Р3, N4). Выходной каскад (транзисторы Р4, N5, N6) работает без "сквозного" тока, что способствует повышению быстродействия динамического D-триггера и уменьшению занимаемой площади.

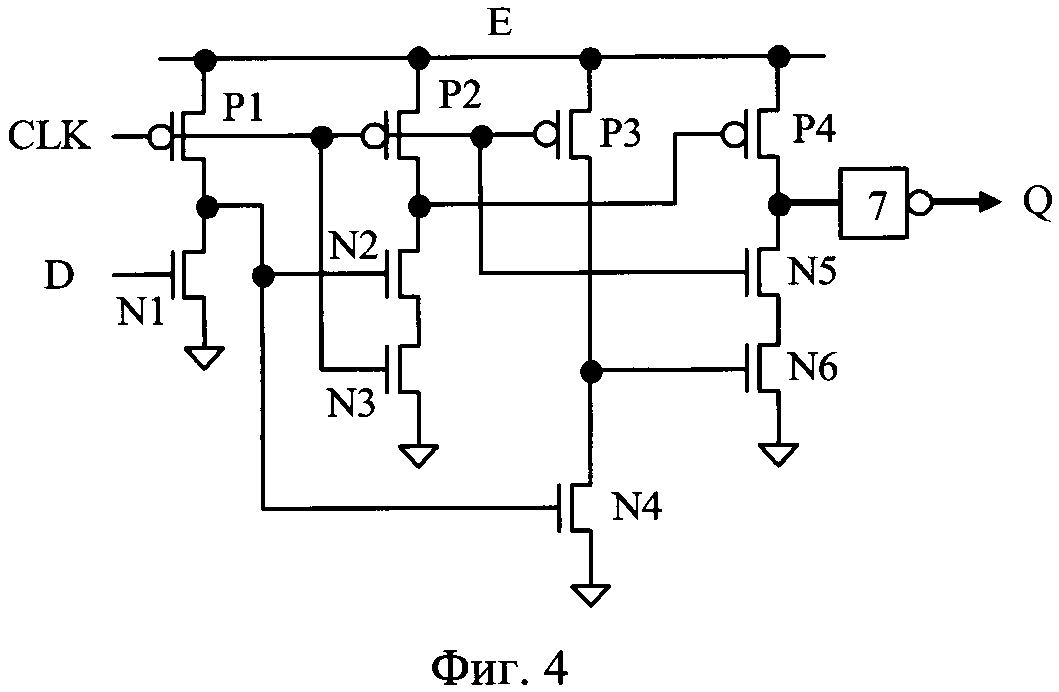

В варианте выполнения заявленного D-триггера с инверсным выходом nQ:  (Фиг. 5), наличие инверсного выхода не понижает быстродействие триггера, так как не требует дополнительного инвертирующего каскада.

(Фиг. 5), наличие инверсного выхода не понижает быстродействие триггера, так как не требует дополнительного инвертирующего каскада.

В двух первых каскадах (транзисторы Р1, N1 и Р2, N2) доминируют n-канальные транзисторы N1 и N2.

Динамическое хранение выполняется в каждом каскаде. Выходной каскад (транзисторы Р4, N5, N6) работает без сквозного тока.

Поставленный технический результат достигнут путем создания динамического D-триггера, содержащего четыре p-канальных транзистора, шесть n-канальных транзисторов и инвертор, причем затворы первого и второго p-канальных транзисторов, а также третьего n-канального транзистора подключены к входу синхронизации D-триггера, затвор первого n-канального транзистора является информационным входом D-триггера, выход инвертора является прямым информационным выходом D-триггера, истоки всех p-канальных транзисторов подключены к шине питания D-триггера, истоки первого, третьего, четвертого и шестого n-канальных транзисторов подключены к шине "земля" D-триггера, сток первого p-канального транзистора, а также затворы второго и четвертого n-канальных транзисторов подключены к стоку первого n-канального транзистора, сток второго и затвор четвертого p-канальных транзисторов подключены к стоку второго n-канального транзистора, исток второго n-канального транзистора соединен со стоком третьего n-канального транзистора, сток третьего p-канального транзистора соединен со стоком четвертого n-канального транзистора, стоки четвертого p-канального и пятого n-канального транзисторов подключены к входу инвертора, исток пятого n-канального транзистора соединен со стоком шестого n-канального транзистора, о т л и чающегося тем, что затворы третьего p-канального транзистора и пятого n-канального транзистора подключены к входу синхронизации D-триггера, затвор шестого n-канального транзистора соединен со стоком четвертого n-канального транзистора.

Поставленный технический результат достигнут также путем создания динамического D-триггера, содержащего четыре p-канальных транзистора, шесть n-канальных транзисторов и инвертор, причем затворы первого и второго p-канальных транзисторов подключены к входу синхронизации D-триггера, затвор первого n-канального транзистора является информационным входом D-триггера, выход инвертора является инверсным информационным выходом D-триггера, истоки всех p-канальных транзисторов подключены к шине питания D-триггера, истоки первого, четвертого и шестого n-канальных транзисторов подключены к шине "земля" D-триггера, сток первого p-канального транзистора, а также затвор второго n-канального транзистора подключены к стоку первого n-канального транзистора, сток второго p-канального транзистора соединен со стоком второго n-канального транзистора, стоки четвертого p-канального транзистора и пятого n-канального транзистора подключены к входу инвертора, исток пятого n-канального транзистора соединен со стоком шестого n-канального транзистора, отличающегося тем, что затворы третьего p-канального, четвертого n-канального и пятого n-канального транзисторов подключены к входу синхронизации D-триггера, исток второго n-канального транзистора подключен к шине "земля" D-триггера, сток второго n-канального транзистора соединен с затвором третьего n-канального транзистора, сток третьего и затвор четвертого p-канальных транзисторов подключены к стоку третьего n-канального транзистора, исток которого соединен со стоком четвертого n-канального транзистора, затвор шестого n-канального транзистора подключен к стоку первого n-канального транзистора.

Для лучшего понимания заявленного изобретения далее приводится его подробное описание с соответствующими графическими материалами.

Фиг. 1. Динамический D-триггер, выполненный согласно первому аналогу [1].

Фиг. 2. Динамический D-триггер, выполненный согласно второму аналогу [2].

Фиг. 3. Динамический D-триггер, выполненный согласно прототипу [3].

Фиг. 4. Динамический D-триггер с прямым выходом Q, выполненный согласно изобретению.

Фиг.5. Динамический D-триггер с инверсным выходом nQ, выполненный согласно изобретению.

Элементы:

P1-Р4 - p-канальные транзисторы;

N1-N6 - n-канальные транзисторы;

7 - инвертор.

Рассмотрим вариант выполнения заявленного динамического D-триггера с прямым выходом Q (Фиг. 4). Динамический D-триггер содержит четыре p-канальных транзистора P1-Р4, шесть n-канальных транзисторов N1-N6 и инвертор 7. Затворы первого и второго p-канальных транзисторов P1, Р2, а также третьего n-канального транзистора N3 подключены к входу синхронизации D-триггера. Затвор первого n-канального транзистора N1 является информационным входом D-триггера. Выход инвертора 7 является прямым информационным выходом D-триггера. Истоки всех p-канальных транзисторов P1-Р4 подключены к шине питания D-триггера, истоки первого, третьего, четвертого и шестого n-канальных транзисторов N1, N3, N4, N6 подключены к шине "земля" D-триггера. Сток первого p-канального транзистора PI, а также затворы второго и четвертого n-канальных транзисторов N2, N4 подключены к стоку первого n-канального транзистора N1. Сток второго и затвор четвертого p-канальных транзисторов Р2, Р4 подключены к стоку второго n-канального транзистора N2. Исток второго n-канального транзистора N2 соединен со стоком третьего n-канального транзистора N3. Сток третьего p-канального транзистора Р3 соединен со стоком четвертого n-канального транзистора N4. Стоки четвертого p-канального транзистора Р4 и пятого n-канального транзистора N5 подключены к входу инвертора 7. Исток пятого n-канального транзистора N5 соединен со стоком шестого n-канального транзистора N6. Затворы третьего p-канального транзистора Р3 и пятого n-канального транзистора N5 подключены к входу синхронизации D-триггера. Затвор шестого n-канального транзистора N6 соединен со стоком четвертого n-канального транзистора N4.

Рассмотрим вариант выполнения заявленного динамического D-триггера с инверсным выходом nQ (Фиг. 5). Динамический D-триггер содержит четыре p-канальных транзистора PI - Р4, шесть n-канальных транзисторов N1-N6 и инвертор 7. Затворы первого и второго p-канальных транзисторов P1, Р2 подключены к входу синхронизации D-триггера. Затвор первого n-канального транзистора N1 является информационным входом D-триггера. Выход инвертора 7 является инверсным информационным выходом D-триггера. Истоки всех p-канальных транзисторов Р1 -Р4 подключены к шине питания D-триггера. Истоки первого, четвертого и шестого n-канальных транзисторов N1, N4, N6 подключены к шине "земля" D-триггера. Сток первого p-канального транзистора Р1, а также затвор второго n-канального транзистора N2 подключены к стоку первого n-канального транзистора N1. Сток второго p-канального транзистора Р2 соединен со стоком второго n-канального транзистора N2. Стоки четвертого p-канального транзистора Р4 и пятого n-канального транзистора N5 подключены к входу инвертора 7. Исток пятого n-канального транзистора N5 соединен со стоком шестого n-канального транзистора N6. Затворы третьего p-канального, четвертого n-канального и пятого n-канального транзисторов Р3, N4, N5 подключены к входу синхронизации D-триггера. Исток второго n-канального транзистора N2 подключен к шине "земля" D-триггера. Сток второго n-канального транзистора N2 соединен с затвором третьего n-канального транзистора N3. Сток третьего и затвор четвертого p-канальных транзисторов Р3, Р4 подключены к стоку третьего n-канального транзистора N3. Исток третьего n-канального транзистора N3 соединен со стоком четвертого n-канального транзистора N4. Затвор шестого n-канального транзистора N6 подключен к стоку первого n-канального транзистора N1.

В приведенных триггерных схемах не допустимо менять местами последовательно соединенные n-канальные транзисторы: возникают эффекты перераспределения заряда при замыкании "подвешенных" узлов, влекущие искажение передаваемого напряжения.

Замена входного n-канального транзистора D на входную логическую группу n-канальных транзисторов Dl, D2 … обеспечивает логическое расширение функции D-триггера (это относится и к прототипу). Например, последовательное соединение транзисторов - встроенная входная функция И, параллельное соединение - ИЛИ, и т.п.В варианте типа ab+cd обнаруживаются возможности реализации D-триггера с входным мультиплексором.

Хотя описанный выше вариант выполнения изобретения был изложен с целью иллюстрации настоящего изобретения, специалистам ясно, что возможны разные модификации, добавления и замены, не выходящие из объема и смысла настоящего изобретения, раскрытого в прилагаемой формуле изобретения.

Литература

1. Патент США US 6,737,900 В1, 2004 г.

2. Патент США US 6,060,927, 2000 г.

3. Yang C.-Y., Dehng G.-K, Hsu J.-M, Liu S.-I. New Dynamic Flip-Flops for High-Speed Dual-Modulus Prescaler // IEEE J. Solid-State Circuits. - 1998. - Vol. 33. - №10.-PP. 1568-1571.