Результат интеллектуальной деятельности: ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ

Вид РИД

Изобретение

Изобретение относится к области радиотехники и электроники может быть использовано в качестве устройства усиления аналоговых сигналов в структуре быстродействующих аналоговых микросхем различного функционального назначения и аналоговых интерфейсов на их основе (например, быстродействующих операционных усилителях (ОУ), мультидифференциальных ОУ и т.п.).

Известны схемы комплементарных дифференциальных входных каскадов (ДК) на биполярных, BiJFet и КМОП транзисторах [1-15]. ДК данного класса (так называемые dual-input-stage) стали основным усилительным элементом многих аналоговых устройств.

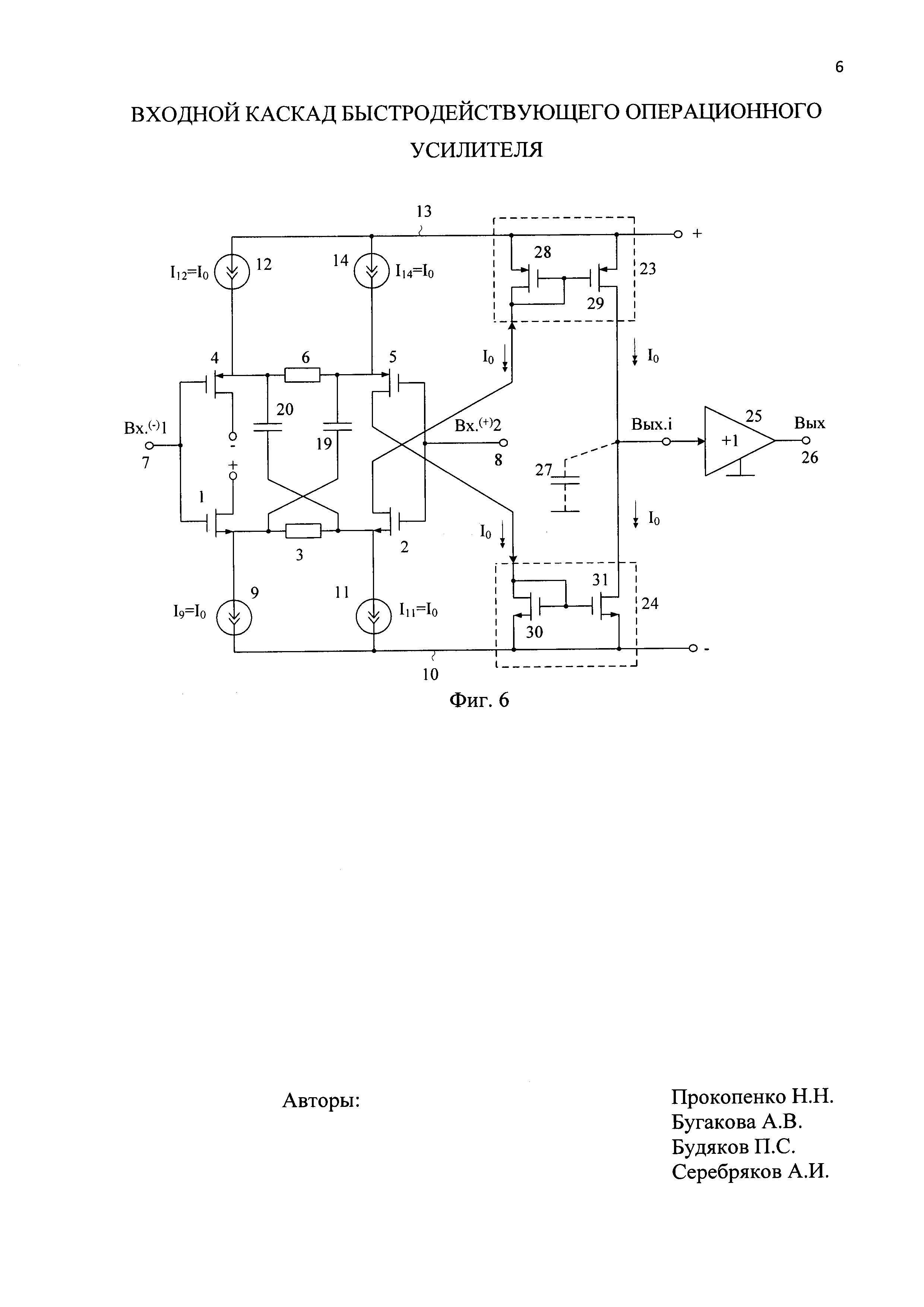

Ближайшим прототипом (фиг. 1) заявляемого устройства является входной каскад операционного усилителя, описанный в патенте US 5.770.972, содержащий первый 1 и второй 2 входные транзисторы одного типа проводимости, между эмиттерами которых включен первый 3 резистор местной отрицательной обратной связи, третий 4 и четвертый 5 входные транзисторы другого типа проводимости, между эмиттерами которых включен второй 6 резистор местной отрицательной обратной связи, первый 7 вход устройства, с которым связаны базы первого 1 и третьего 4 входных транзисторов, второй 8 вход устройства, с которым связаны базы второго 2 и четвертого 5 входных транзисторов, первый 9 токостабилизирующий двухполюсник, включенный между эмиттером первого 1 входного транзистора и первой 10 шиной источника питания, второй 11 токостабилизирующий двухполюсник, включенный между эмиттером второго 2 входного транзистора и первой 10 шиной источника питания, третий 12 токостабилизирующий двухполюсник, включенный между эмиттером третьего 4 входного транзистора и второй 13 шиной источника питания, четвертый 14 токостабилизирующий двухполюсник, включенный между эмиттером четвертого 5 входного транзистора и второй 13 шиной источника питания, причем коллектор первого 1 входного транзистора связан с первым 15 токовым выходом устройства, согласованным со второй 13 шиной источника питания, коллектор второго 2 входного транзистора соединен со вторым 16 токовым выходом устройства, согласованным со второй 13 шиной источника питания, коллектор третьего 4 входного транзистора соединен с третьим 17 токовым выходом устройства, согласованным с первой 10 шиной источника питания, коллектор четвертого 5 входного транзистора соединен с четвертым 18 токовым выходом устройства, согласованным с первой 10 шиной источника питания.

Существенный недостаток известного входного каскада состоит в том, что во время переходных процессов при большом импульсном входном дифференциальном сигнале он не обеспечивает большие приращения выходных токов, что не позволяет реализовать на его основе быстродействующие операционные усилители, непрерывные стабилизаторы напряжения с малыми уровнями «всплесков» и «провалов» выходного напряжения при импульсных токах нагрузки и т.д.

Основная задача предполагаемого изобретения состоит в формировании различных (заданных разработчиком) уровней выходных динамических токов устройства, пропорциональных производной входного дифференциального напряжения (напряжения между входами 7 и 8). Это позволяет существенно повысить быстродействие многих подклассов аналоговых микросхем (операционные усилители, стабилизаторы напряжения и т.п.) и обеспечить идентичность переднего и заднего фронтов переходного процесса в схемах с отрицательной обратной связью.

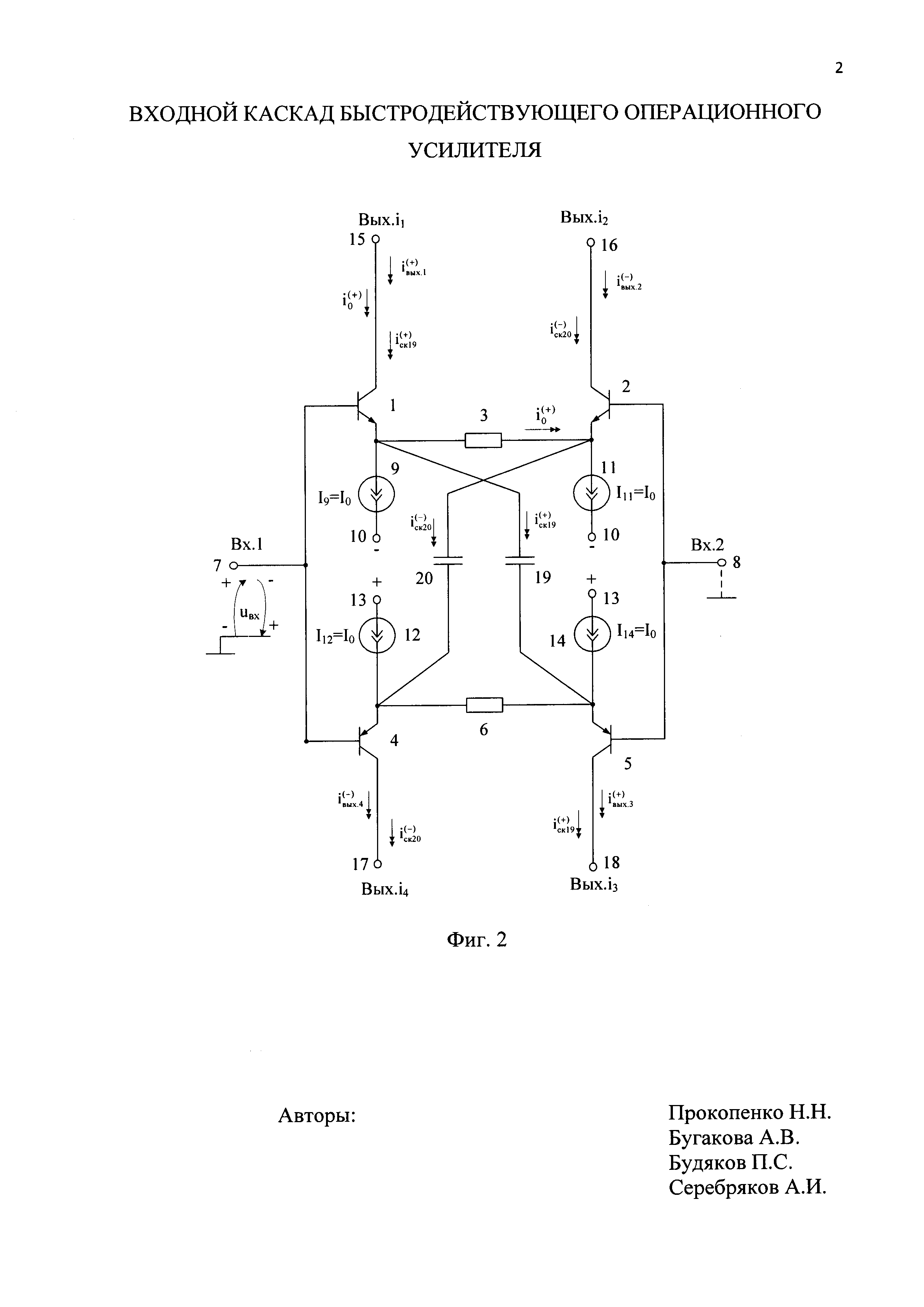

Поставленная задача достигается тем, что во входном каскаде операционного усилителя фиг. 1, содержащем первый 1 и второй 2 входные транзисторы одного типа проводимости, между эмиттерами которых включен первый 3 резистор местной отрицательной обратной связи, третий 4 и четвертый 5 входные транзисторы другого типа проводимости, между эмиттерами которых включен второй 6 резистор местной отрицательной обратной связи, первый 7 вход устройства, с которым связаны базы первого 1 и третьего 4 входных транзисторов, второй 8 вход устройства, с которым связаны базы второго 2 и четвертого 5 входных транзисторов, первый 9 токостабилизирующий двухполюсник, включенный между эмиттером первого 1 входного транзистора и первой 10 шиной источника питания, второй 11 токостабилизирующий двухполюсник, включенный между эмиттером второго 2 входного транзистора и первой 10 шиной источника питания, третий 12 токостабилизирующий двухполюсник, включенный между эмиттером третьего 4 входного транзистора и второй 13 шиной источника питания, четвертый 14 токостабилизирующий двухполюсник, включенный между эмиттером четвертого 5 входного транзистора и второй 13 шиной источника питания, причем коллектор первого 1 входного транзистора связан с первым 15 токовым выходом устройства, согласованным со второй 13 шиной источника питания, коллектор второго 2 входного транзистора соединен со вторым 16 токовым выходом устройства, согласованным со второй 13 шиной источника питания, коллектор третьего 4 входного транзистора соединен с третьим 17 токовым выходом устройства, согласованным с первой 10 шиной источника питания, коллектор четвертого 5 входного транзистора соединен с четвертым 18 токовым выходом устройства, согласованным с первой 10 шиной источника питания, предусмотрены новые элементы и связи - между эмиттером первого 1 и четвертого 5 входных транзисторов включен первый 19 корректирующий конденсатор, а между эмиттером второго 2 и эмиттером третьего 4 входных транзисторов включен второй 20 корректирующий конденсатор.

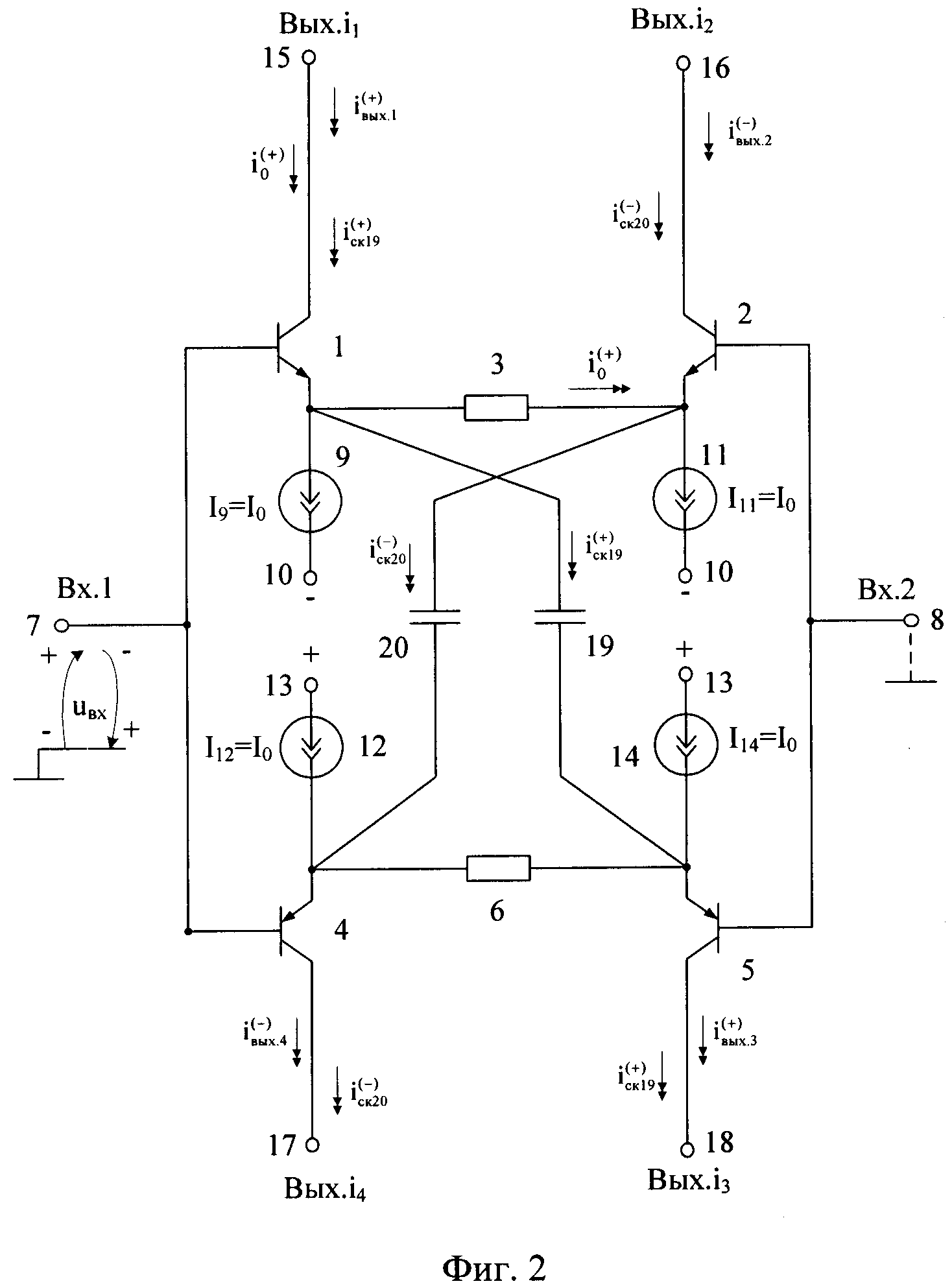

Схема усилителя-прототипа представлена на чертеже фиг. 1. На чертеже фиг. 2 показано заявляемое устройство в соответствии с п. 1 формулы изобретения.

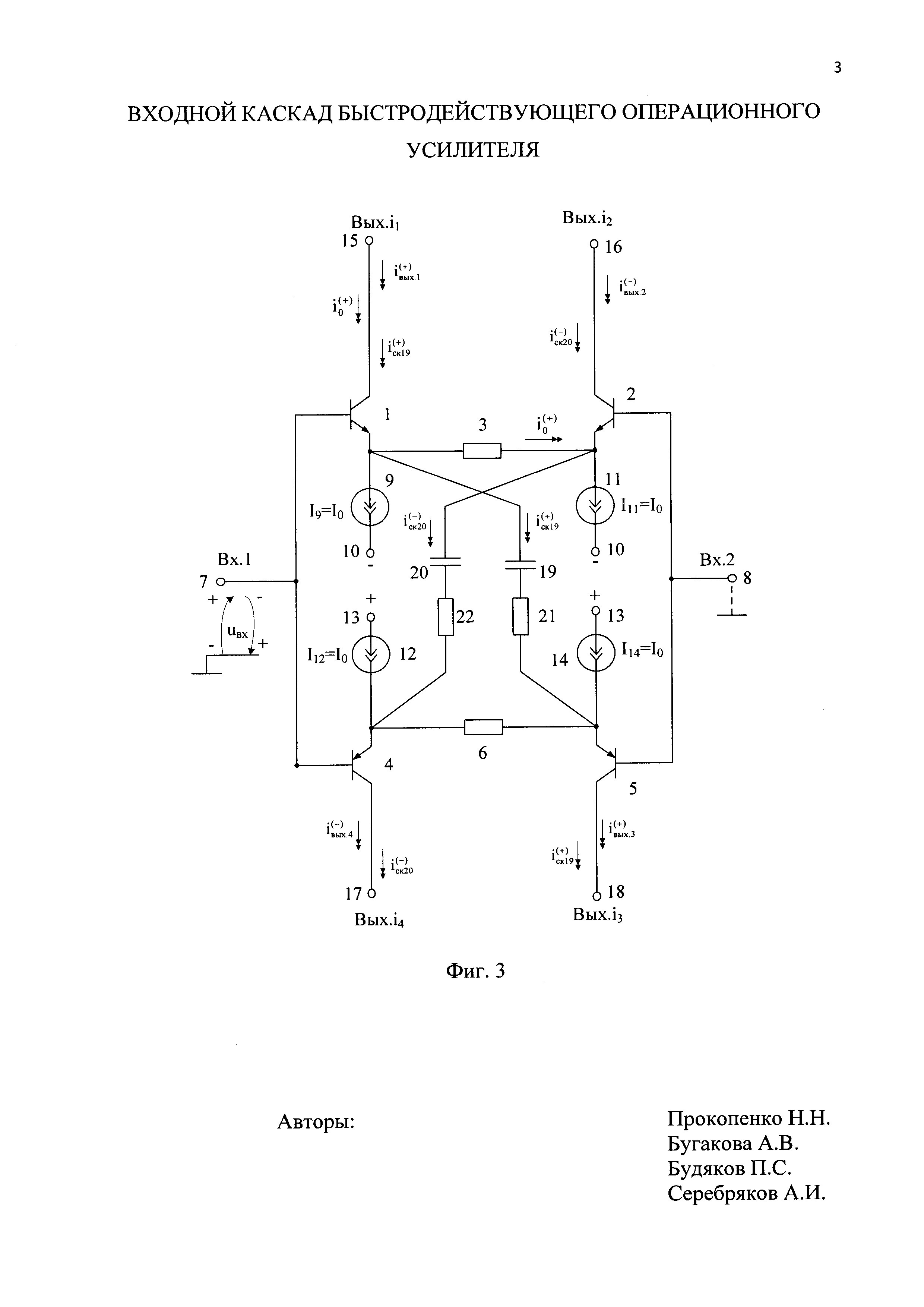

На чертеже фиг. 3 приведена схема заявляемого входного каскада в соответствии с п. 2 формулы изобретения.

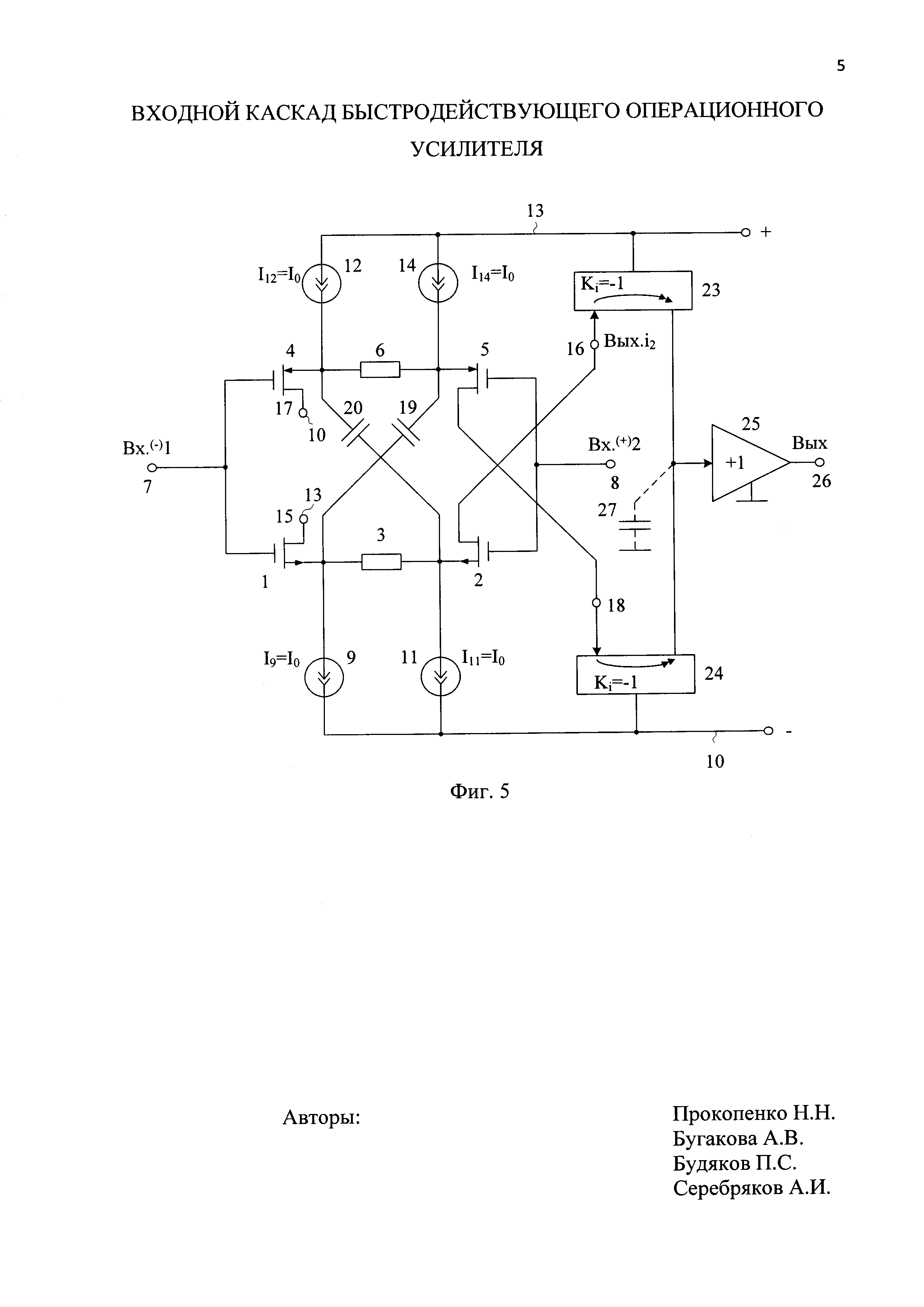

На чертеже фиг. 4 приведена схема заявляемого входного каскада при его реализации на основе КМОП транзисторов.

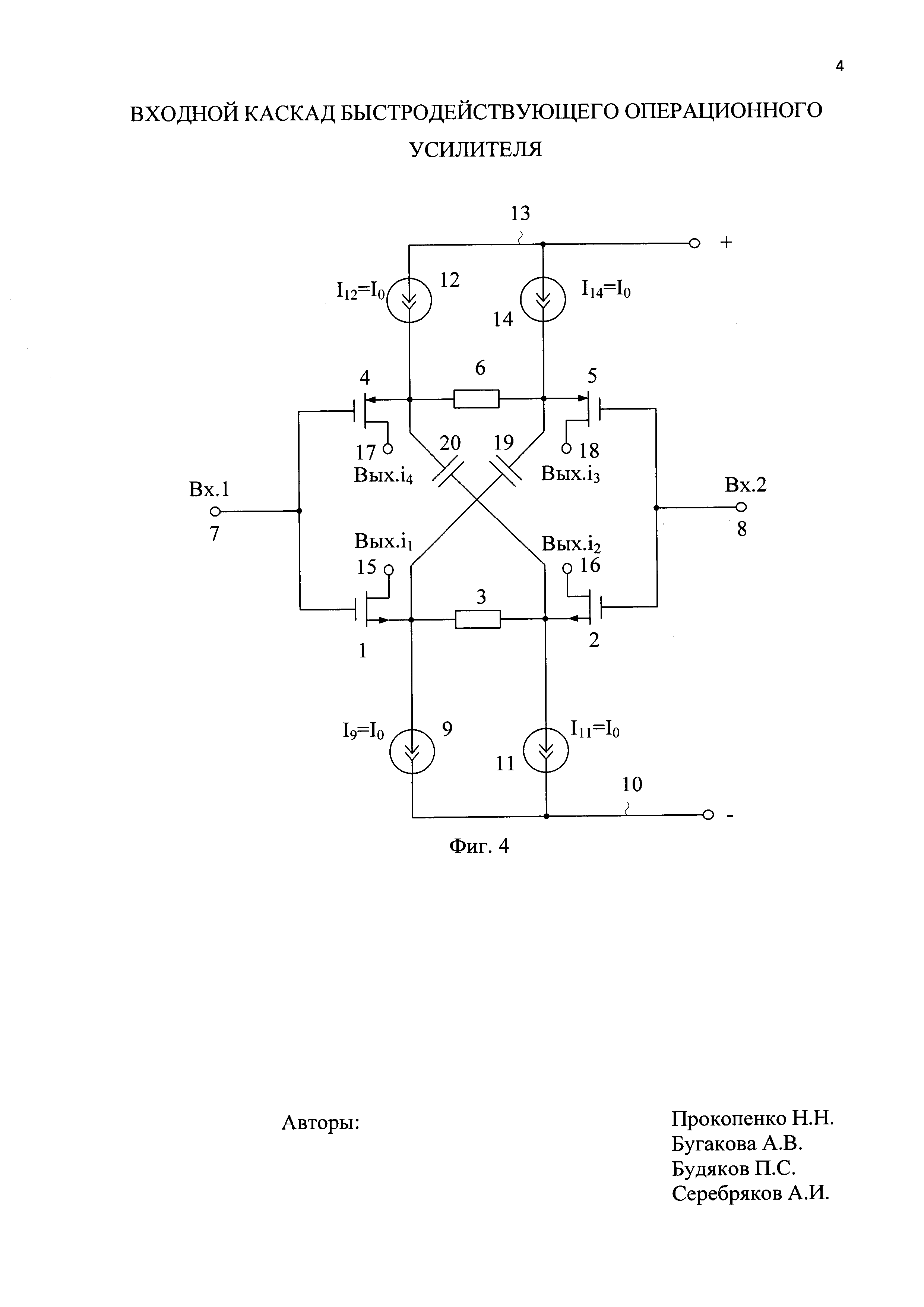

На чертеже фиг. 5 показана схема заявляемого входного каскада в структуре быстродействующего КМОП ОУ.

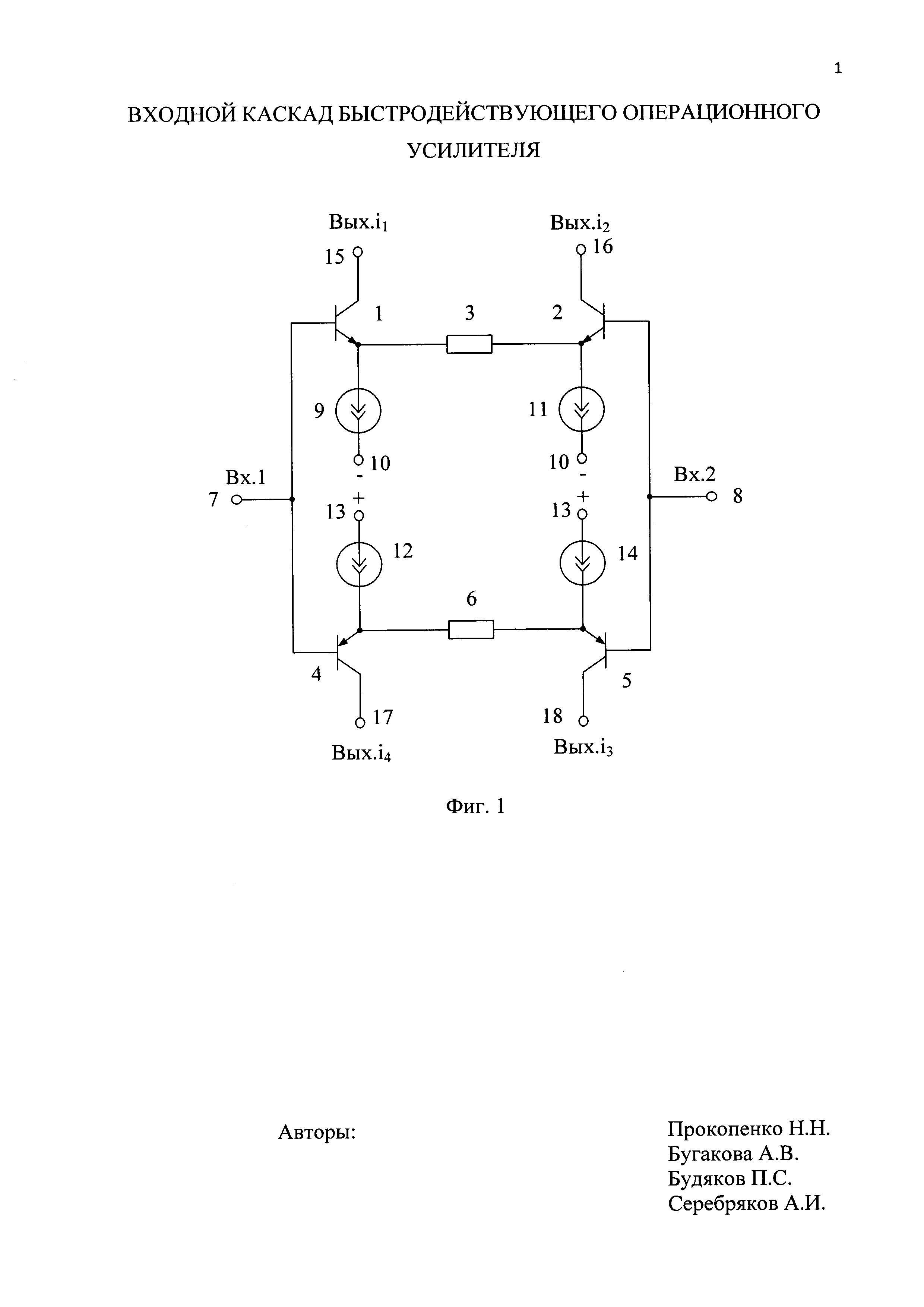

На чертеже фиг. 6 представлена схема заявляемого входного каскада в структуре быстродействующего КМОП ОУ с конкретным выполнением токовых зеркал 23 и 24.

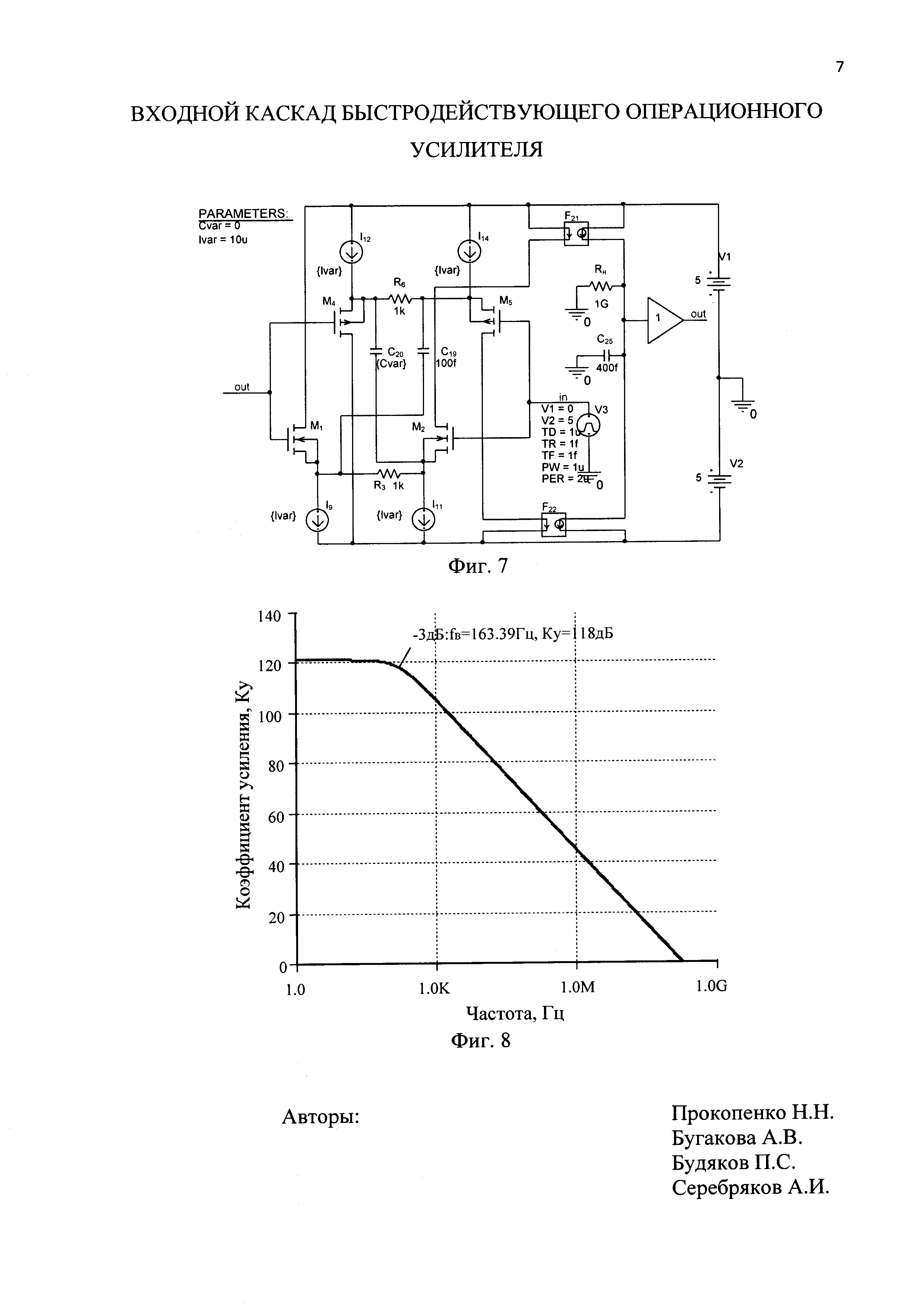

На чертеже фиг. 7 приведена схема заявляемого входного каскада в структуре быстродействующего ОУ в среде Orcad на моделях транзисторов tsmc035_t65.

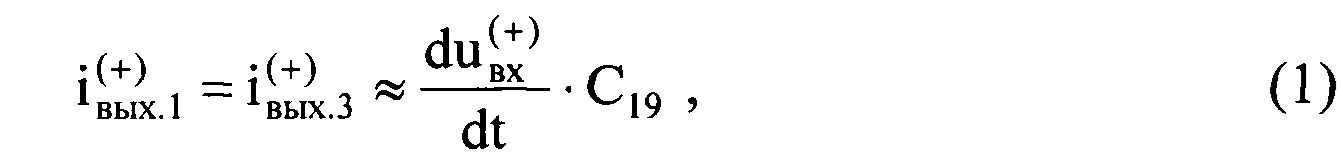

На чертеже фиг. 8 показана амплитудно-частотная характеристика (АЧХ) коэффициента усиления схемы разомкнутого ОУ фиг. 7 при следующих емкостях корректирующих конденсаторов 19, 20 и 27: C19=C20=0, С27=1 пФ.

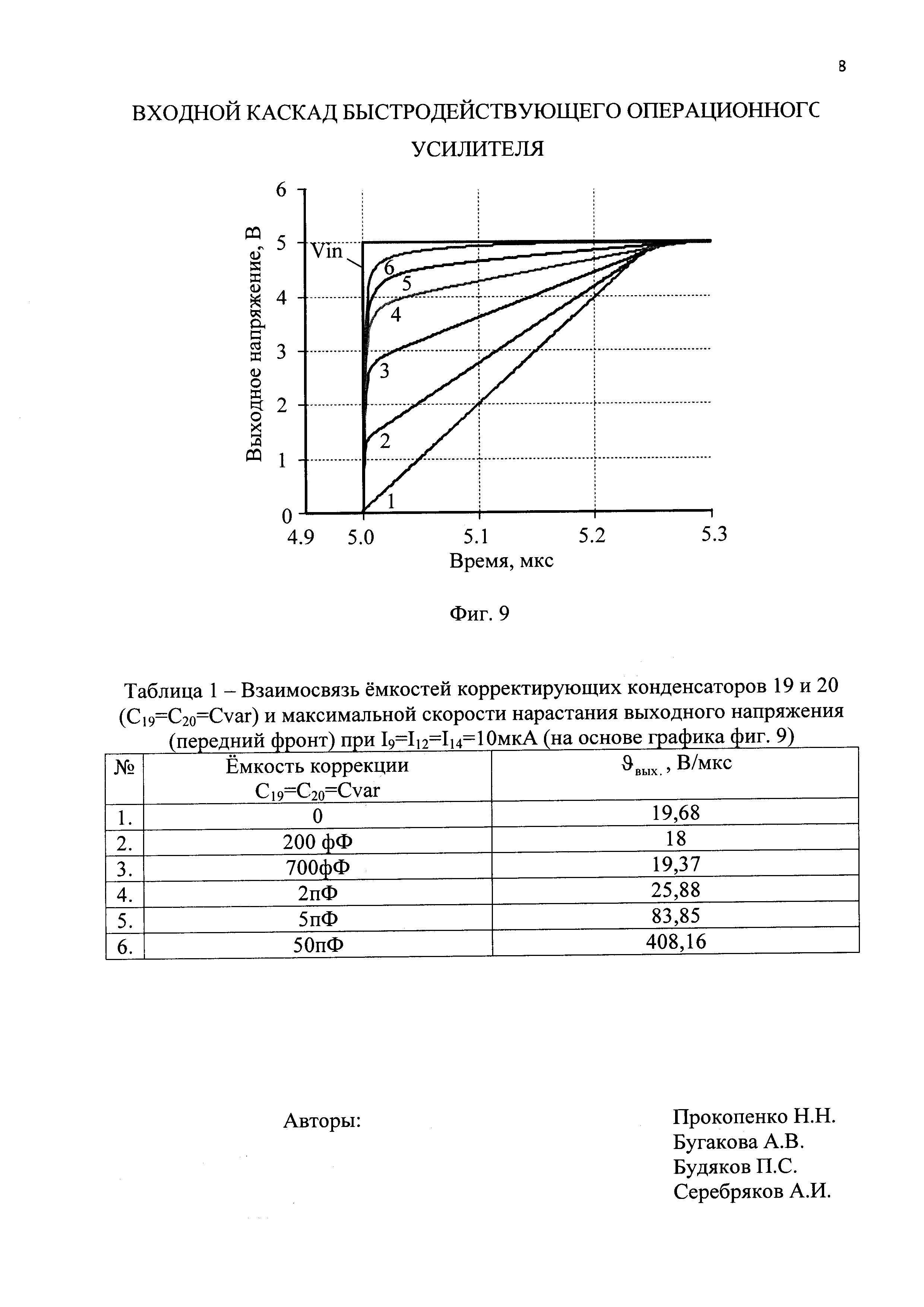

На чертеже фиг. 9 представлены осциллограммы входного и выходного напряжений ОУ (передний фронт) при разных значениях емкостей корректирующих конденсаторов 19 и 20 (C19=C20=Cvar), а также при емкости основного корректирующего конденсатора 27 С27=1 пФ, токах I9=I12=I14=10 мкA, ширине импульса 1 мкс.

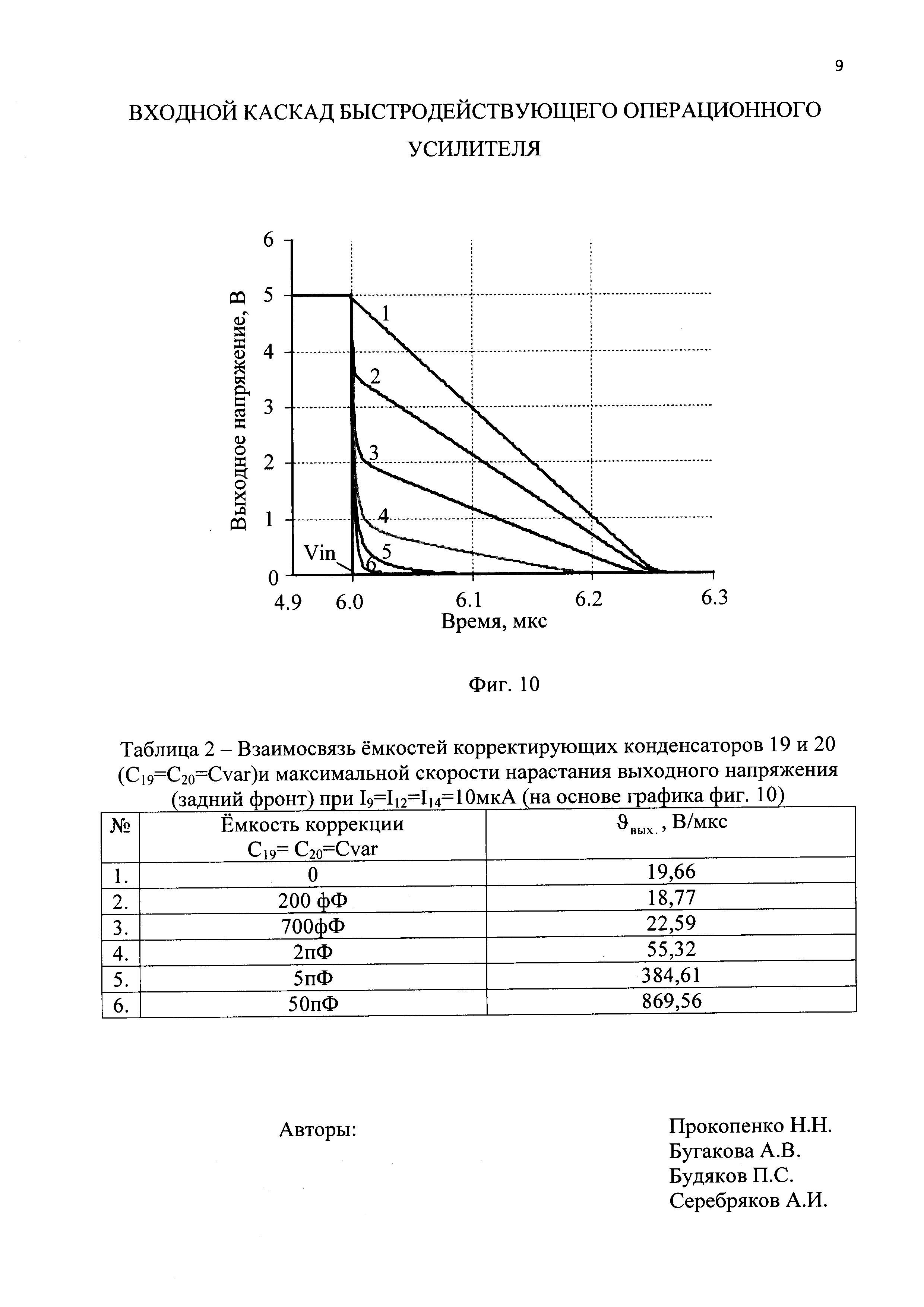

На чертеже фиг. 10 показаны осциллограммы входного и выходного напряжений ОУ (задний фронт) при разных значениях емкостей корректирующих конденсаторов 19 и 20 (C19=C20=Cvar), а также при емкости основного корректирующего конденсатора 27 С27=1 пФ, токах I9=I12=I14=10 мкA, ширине импульса 1 мкс.

Входной каскад быстродействующего операционного усилителя фиг. 2 содержит первый 1 и второй 2 входные транзисторы одного типа проводимости, между эмиттерами которых включен первый 3 резистор местной отрицательной обратной связи, третий 4 и четвертый 5 входные транзисторы другого типа проводимости, между эмиттерами которых включен второй 6 резистор местной отрицательной обратной связи, первый 7 вход устройства, с которым связаны базы первого 1 и третьего 4 входных транзисторов, второй 8 вход устройства, с которым связаны базы второго 2 и четвертого 5 входных транзисторов, первый 9 токостабилизирующий двухполюсник, включенный между эмиттером первого 1 входного транзистора и первой 10 шиной источника питания, второй 11 токостабилизирующий двухполюсник, включенный между эмиттером второго 2 входного транзистора и первой 10 шиной источника питания, третий 12 токостабилизирующий двухполюсник, включенный между эмиттером третьего 4 входного транзистора и второй 13 шиной источника питания, четвертый 14 токостабилизирующий двухполюсник, включенный между эмиттером четвертого 5 входного транзистора и второй 13 шиной источника питания, причем коллектор первого 1 входного транзистора связан с первым 15 токовым выходом устройства, согласованным со второй 13 шиной источника питания, коллектор второго 2 входного транзистора соединен со вторым 16 токовым выходом устройства, согласованным со второй 13 шиной источника питания, коллектор третьего 4 входного транзистора соединен с третьим 17 токовым выходом устройства, согласованным с первой 10 шиной источника питания, коллектор четвертого 5 входного транзистора соединен с четвертым 18 токовым выходом устройства, согласованным с первой 10 шиной источника питания. Между эмиттером первого 1 и четвертого 5 входных транзисторов включен первый 19 корректирующий конденсатор, а между эмиттером второго 2 и эмиттером третьего 4 входных транзисторов включен второй 20 корректирующий конденсатор.

На чертеже фиг. 3, в соответствии с п. 2 формулы изобретения, последовательно с первым 19 корректирующим конденсатором включен первый 21 корректирующий резистор, а последовательно со вторым 20 корректирующим конденсатором включен второй 22 корректирующий резистор.

На чертеже фиг. 4 приведена схема заявляемого входного каскада при его реализации на основе КМОП транзисторов.

На чертеже фиг. 5 показана схема заявляемого входного каскада в структуре быстродействующего КМОП ОУ, который содержит дополнительные токовые зеркала 23 и 24, буферный усилитель 25, выход которого 26 является выходом операционного усилителя, и основной корректирующий конденсатор 27, обеспечивающий устойчивость ОУ и формирующих его частоту единичного усиления.

На чертеже фиг. 6 представлена схема заявляемого входного каскада в структуре быстродействующего КМОП ОУ с конкретным выполнением дополнительных токовых зеркал 23 и 24, которые реализованы соответственно на транзисторах 28, 29 и 30, 31.

Рассмотрим работу заявляемого устройства фиг. 2.

Основная особенность предлагаемого дифференциального каскада - формирование больших импульсных токов на втором 16 и третьем 17, а также первом 15 и четвертом 18 токовых выходах при импульсном изменении входного дифференциального напряжения (напряжения между первым 7 и вторым 8 входами) как для положительной, так и для отрицательной полярности uвх.

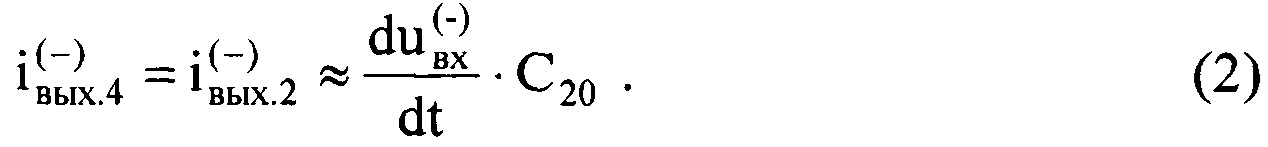

Для положительной полярности  амплитуда выходного токового импульса определяется первым 19 корректирующим конденсатором, а для отрицательной

амплитуда выходного токового импульса определяется первым 19 корректирующим конденсатором, а для отрицательной  - вторым 20 корректирующим конденсатором

- вторым 20 корректирующим конденсатором

При этом максимальное значение токов выходов зависит от сопротивлений эмиттерных переходов первого 1 и четвертого 5, а также второго 2 и третьего 4 входных транзисторов. Введение (в соответствии с п. 2 формулы изобретения) последовательно с первым 19 и вторым 20 конденсаторами корректирующих резисторов 21 и 22, а также путем выбора численных значений емкости первого 19 и второго 20 конденсаторов (С19, С20) позволяет управлять численными значениями максимальных выходных токов, в частности выбирать их неодинаковыми для разных полярностей входного напряжения. Это важное свойство заявляемой схемы способствует устранению так называемой динамической асимметрии, проявляющейся в неодинаковых переходных процессах при положительном и отрицательном импульсном входном сигнале, например, в операционных усилителях. При этом в схеме фиг. 3 максимальные токи выходов могут ограничиваться на заданном уровне.

где R21, R22 - сопротивления первого 21 и второго 22 корректирующих резисторов.

Схема фиг. 4, соответствующая фиг. 2, реализована на КМОП транзисторах, у которых затвор соответствует базе, исток - эмиттеру, а сток - коллектору биполярного транзистора.

Схемы фиг. 5 и фиг. 6 показывает возможность применения заявляемой схемы входного каскада в структуре КМОП быстродействующего ОУ.

Компьютерное моделирование схемы фиг. 6 в среде Orcad (фиг. 7) на моделях транзисторов tsmc035_t65 показывает (фиг. 9, таблица 1 и фиг. 10, таблица 2), что максимальная скорость нарастания выходного напряжения ОУ фиг. 6 увеличивается (для переднего фронта) более чем в 20 раз, а для заднего - более чем в 40 раз. При необходимости данная асимметрия может быть уменьшена за счет выбора разных сопротивлений первого 21 и второго 22 корректирующих резисторов. Важно заметить, что такой выигрыш обеспечивается при работе входного каскада в режиме микротоков (I9=I11=I12=I14=10 мкА).

Таким образом, заявляемое устройство характеризуется более высоким быстродействием в сравнении с прототипом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент ЕР 1150423 А2, fig. 3

2. Патент US 6194962

3. Патент US 5714906, fig. 9а

4. Патент US 6433637

5. Патентная заявка US 2001/0052818, fig. 1, fig. 9

6. Патент US 6822513

7. Патентная заявка US 2005/0001681

8. Патентная заявка US 2007/0159248, fig. 2

9. Патент US 5714906

10. Патент US 4636743

11. Патент US 4783637

12. Патент US 5291149

13. Патент US 4649352, fig. 1

14. Патент US 5512859, fig. 1

15. Патент US 5770972.