Результат интеллектуальной деятельности: БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ

Вид РИД

Изобретение

Изобретение относится к области радиотехники и аналоговой микроэлектроники и может быть использовано в различных быстродействующих интерфейсах, устройствах преобразования сигналов, инструментальных усилителях и т.п.

Быстродействие операционных усилителей (ОУ), которое характеризуется максимальной скоростью нарастания выходного напряжения (ϑвых.) и временем установления переходного процесса (tуст.), определяет динамические параметры многих аналоговых интерфейсов датчиков, буферных каскадов, АЦП, драйверов линий связи и т.п.

В современной радиоэлектронной аппаратуре находят применение ОУ, реализованные по классической архитектуре на биполярных (или полевых) транзисторах с одним токовым зеркалом и буферным усилителем [1-20]. Благодаря простоте такое схемотехническое решение наиболее популярно как в зарубежных, так и в российских аналоговых микросхемах. На основе ОУ данного класса возможно построение прецизионных усилителей, имеющих малое напряжение смещения нуля и повышенный коэффициент ослабления входного синфазного сигнала.

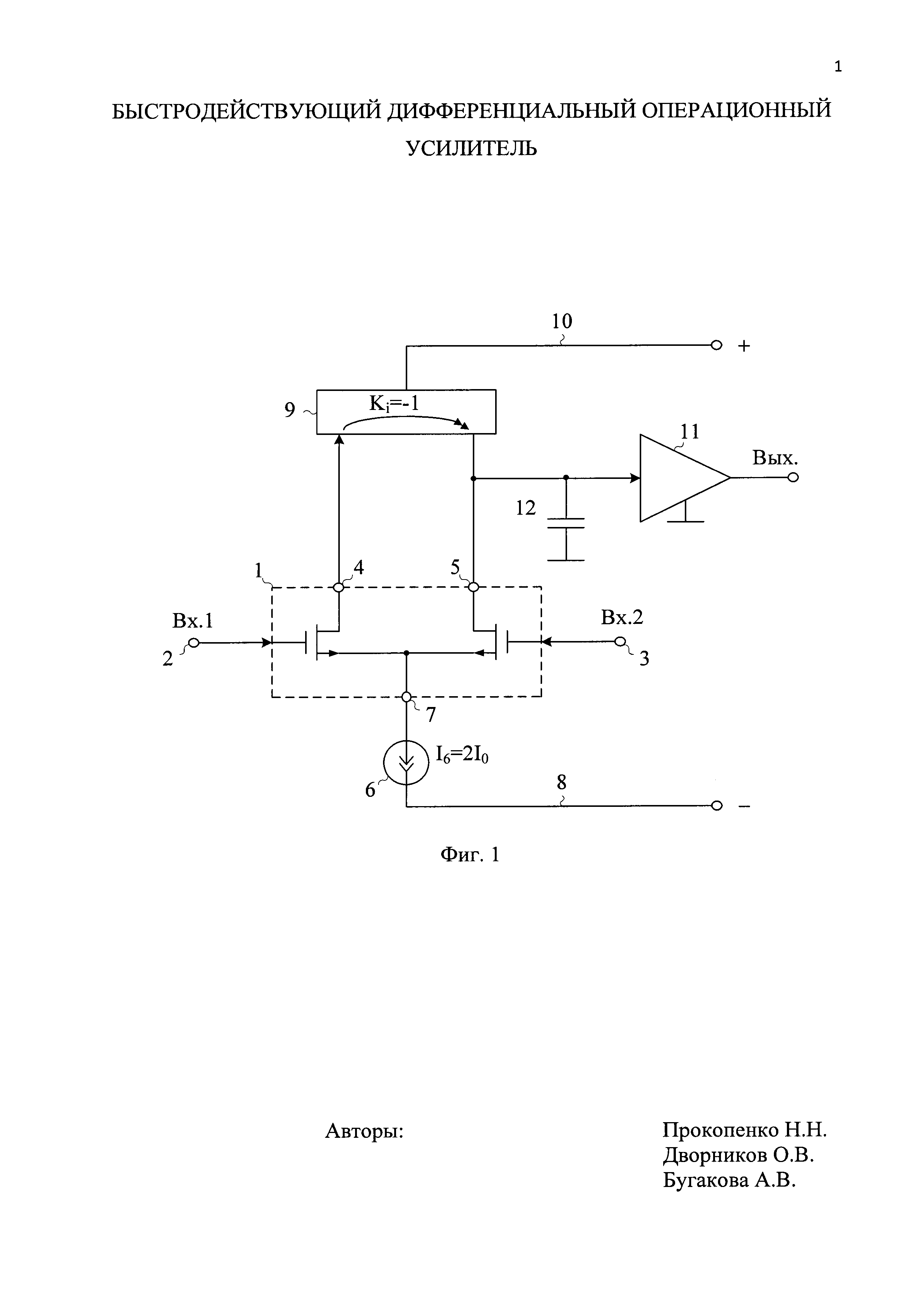

Ближайшим прототипом (фиг. 1) заявляемого устройства является дифференциальный операционный усилитель по патенту US 6.249.153 (fig. 4). Он содержит (фиг. 1) входной дифференциальный каскад 1 с первым 2 и вторым 3 входами, первым 4 и вторым 5 противофазными токовыми выходами, первый источник опорного тока 6, включенный между входом 7 входного дифференциального каскада 1 для установления его статического режима по току и первой 8 шиной источника питания, первое токовое зеркало 9, согласованное со второй 10 шиной источника питания, вход которого соединен с первым 4 токовом выходом входного дифференциального каскада 1, а выход подключен ко второму 5 токовому выходу входного дифференциального каскада 1 и связан со входом буферного усилителя 11, первый 12 корректирующий конденсатор, связанный со входом буферного усилителя 11.

Существенный недостаток известного ОУ состоит в том, что при работе его входного каскада в режиме микротоков (1÷10 мкА) его максимальная скорость нарастания выходного напряжения получается небольшой (1÷3 В/мкс).

Основная задача предлагаемого изобретения состоит в повышении (на 1-2 порядка) максимальной скорости нарастания выходного напряжения при работе входных транзисторов ОУ с микроамперными статическими токами (1÷10 мкА).

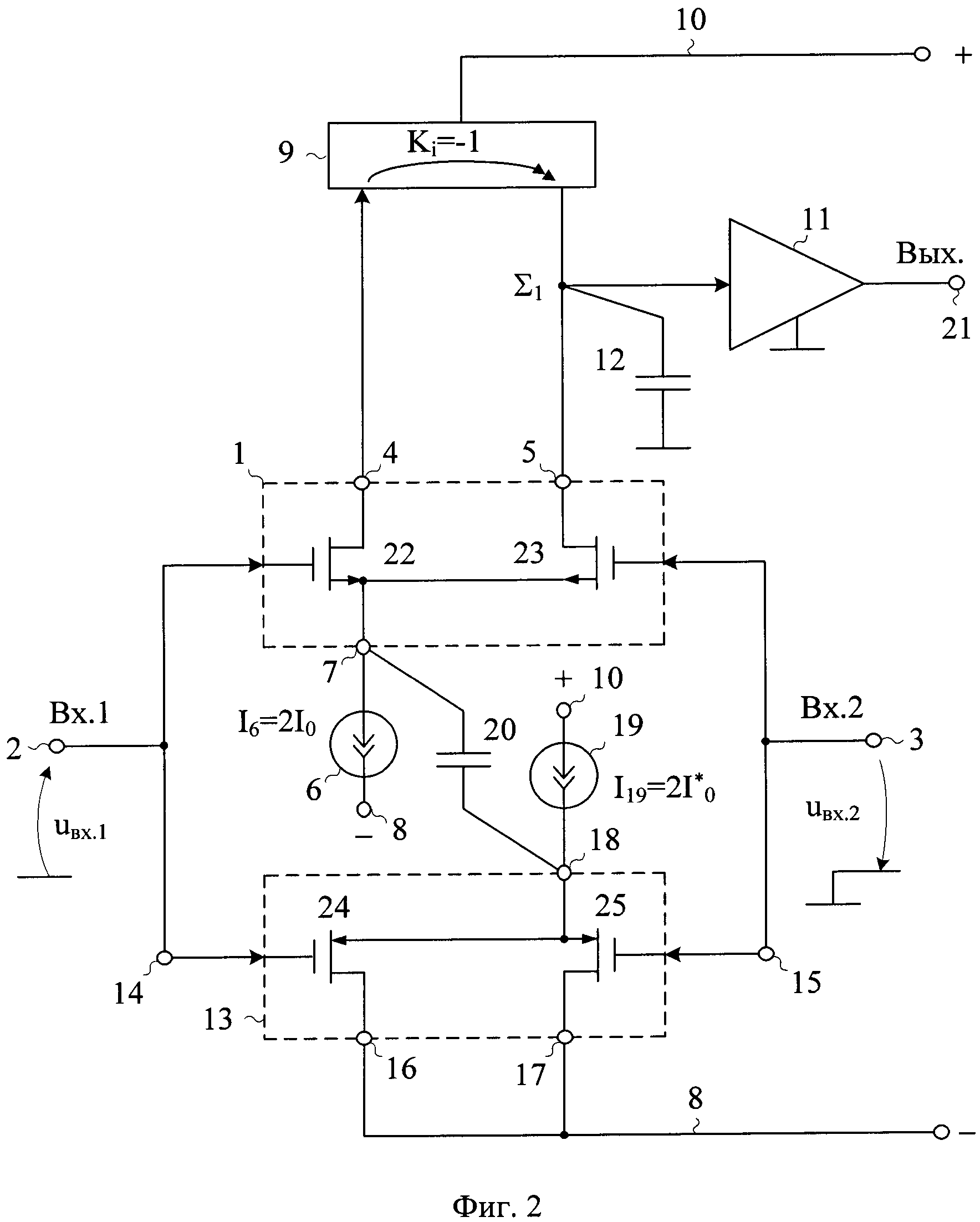

Поставленная задача достигается тем, что в операционном усилителе фиг. 1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 входами, первым 4 и вторым 5 противофазными токовыми выходами, первый источник опорного тока 6, включенный между входом 7 входного дифференциального каскада 1 для установления его статического режима по току и первой 8 шиной источника питания, первое токовое зеркало 9, согласованное со второй 10 шиной источника питания, вход которого соединен с первым 4 токовом выходом входного дифференциального каскада 1, а выход подключен ко второму 5 токовому выходу входного дифференциального каскада 1 и связан со входом буферного усилителя 11, первый 12 корректирующий конденсатор, связанный со входом буферного усилителя 11, предусмотрены новые элементы и связи - в схему введен дополнительный дифференциальный каскад 13, содержащий первый 14 и второй 15 входы, первый 16 и второй 17 противофазные токовые выходы, согласованные с первой 8 шиной источника питания, вход 18 дополнительного дифференциального каскада 13 для установления его статического режима по току, причем первый 14 вход дополнительного дифференциального каскада 13 связан с первым 2 входом входного дифференциального каскада 1, второй 15 вход дополнительного дифференциального каскада 13 связан со вторым 3 входом входного дифференциального каскада 1, между входом 18 дополнительного дифференциального каскада 13 для установления его статического режима по току и второй 10 шиной источника питания включен второй 19 источник опорного тока, между входом 7 входного дифференциального каскада 1 для установления его статического режима по току и входом 18 дополнительного дифференциального каскада 13 для установления его статического режима по току включен второй 20 корректирующий конденсатор.

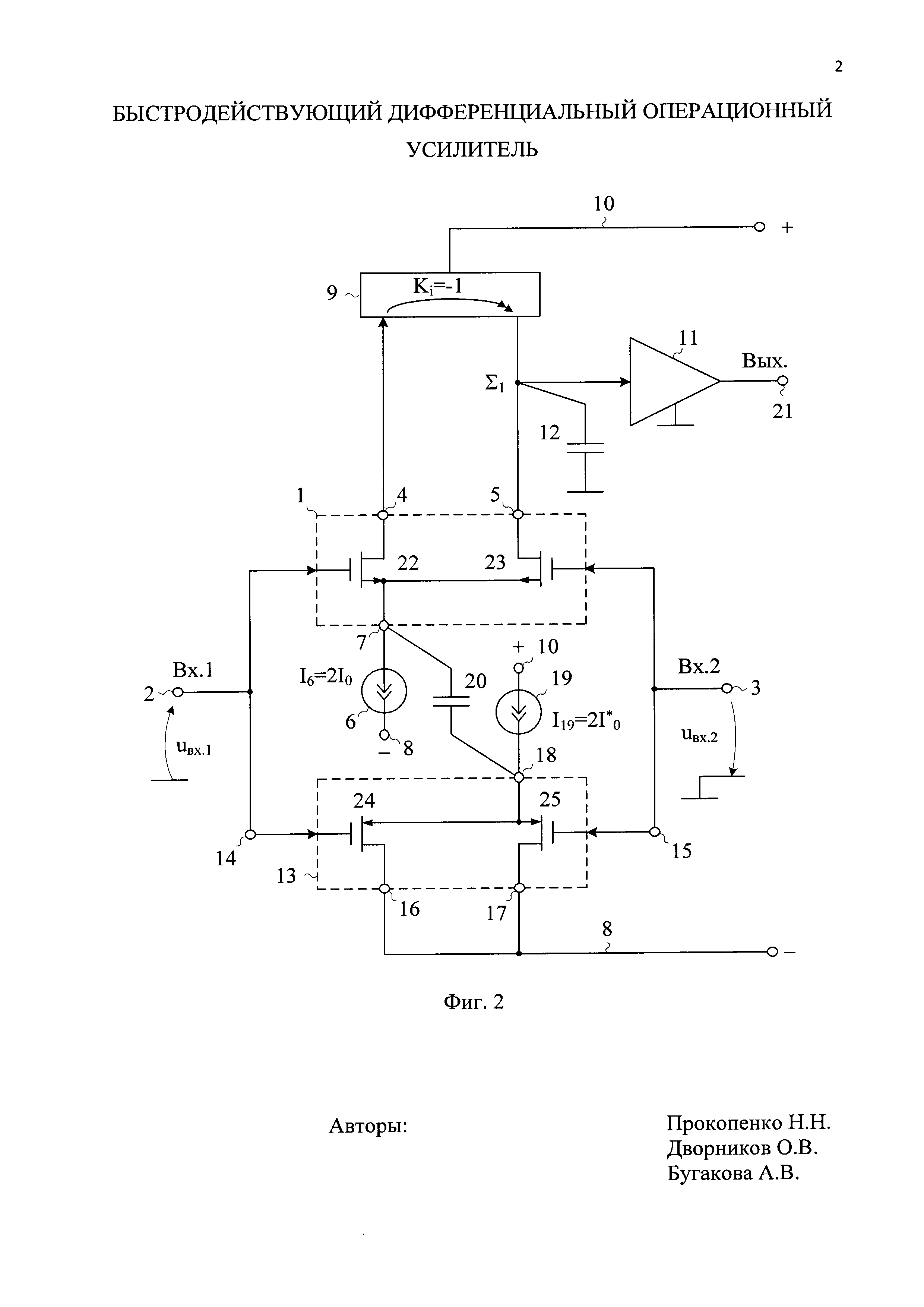

На фиг. 1 показана схема ОУ-прототипа, а на фиг. 2 - схема заявляемого устройства в соответствии с п. 1, п. 2 и п. 3 формулы изобретения.

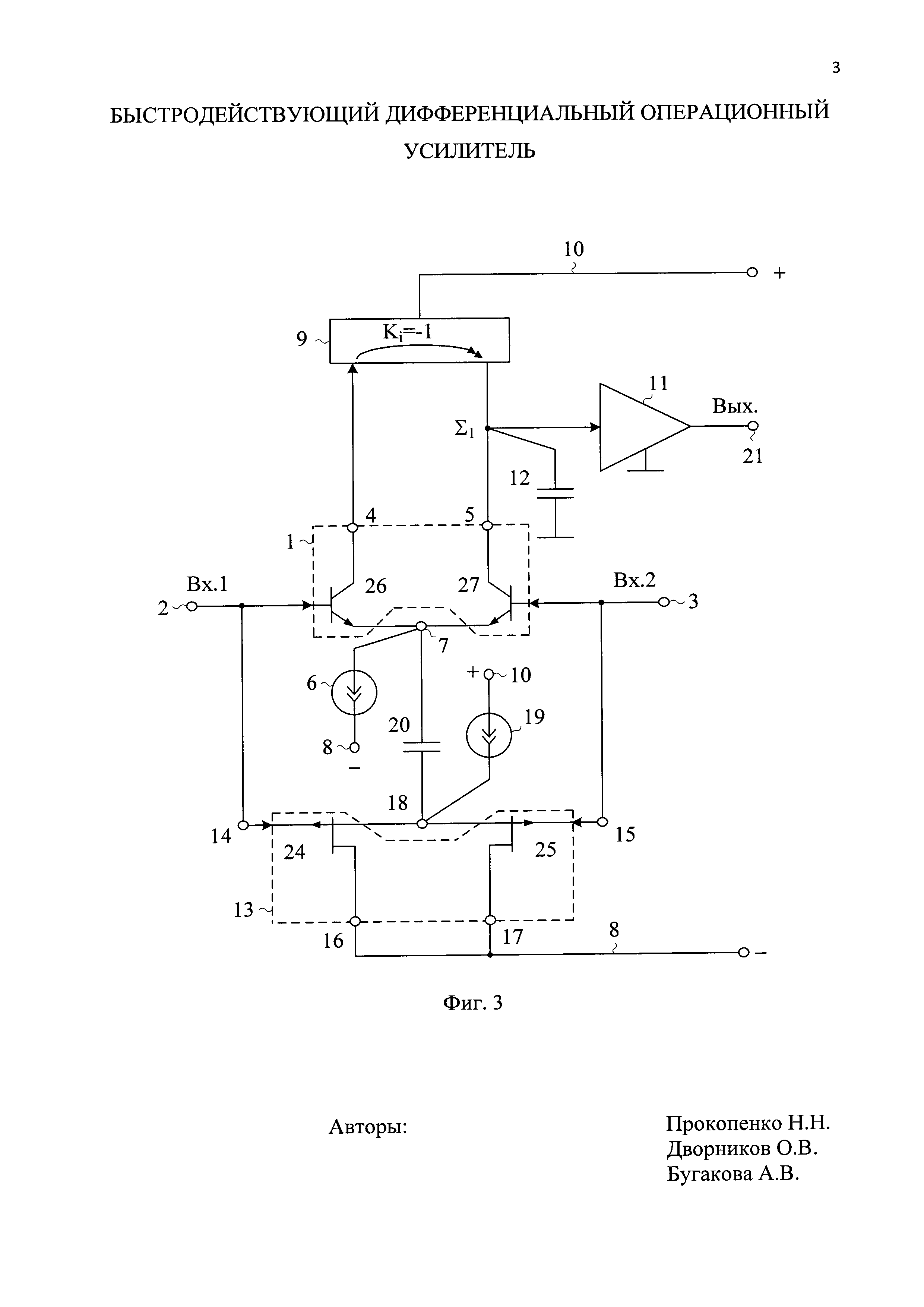

На фиг. 3 приведена схема заявляемого устройства фиг. 2, для случая, когда входной дифференциальный каскад (1) и дополнительный дифференциальный каскад (13) реализованы на основе BiJFet радиационного-стойкого технологического процесса 3КБТ ОАО «Интеграл» (г. Минск), обеспечивающего также работу активных элементов при достаточно низких, в том числе криогенных температурах.

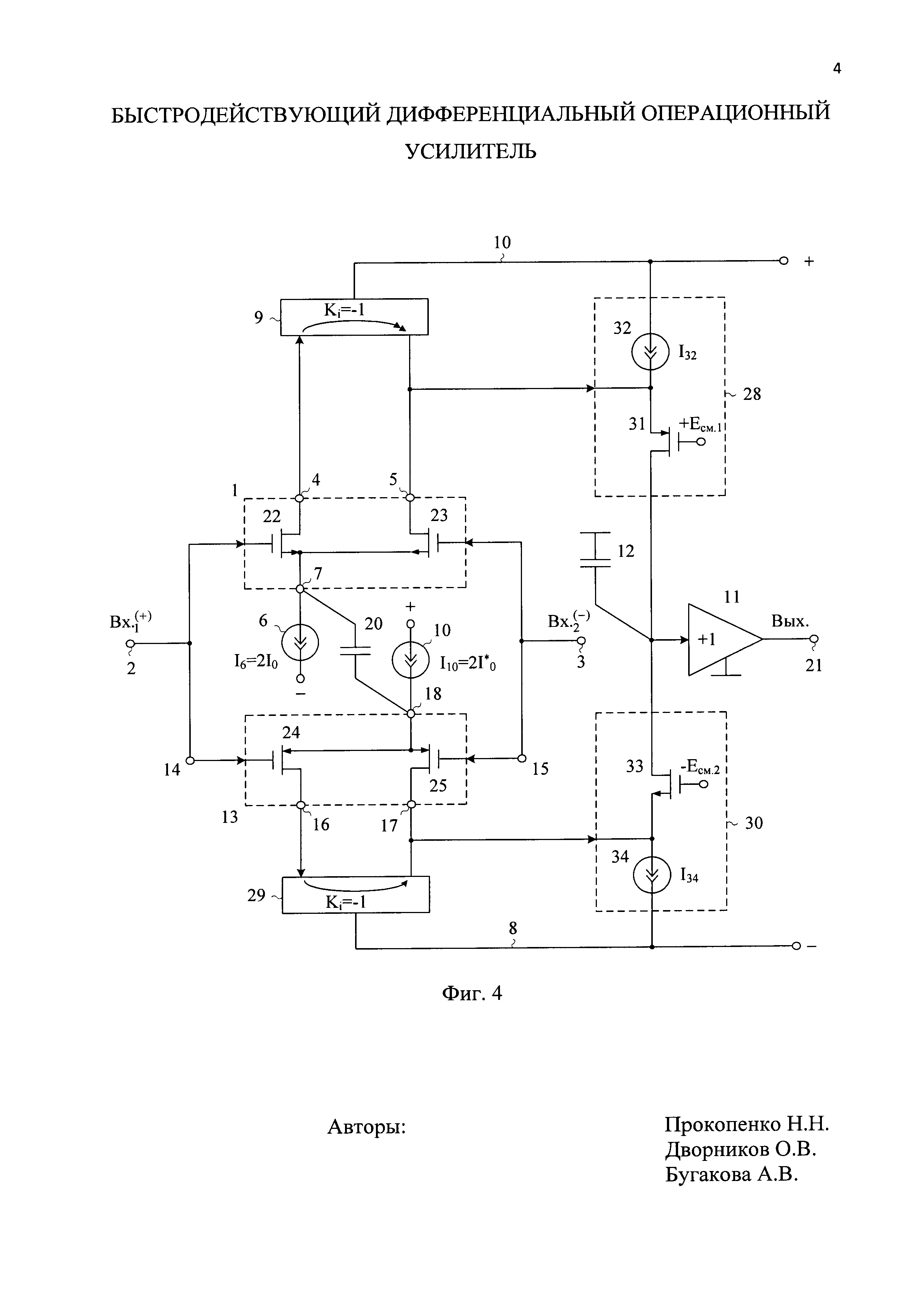

На фиг. 4 приведена схема заявляемого устройства фиг. 2 в соответствии с п. 4 формулы изобретения.

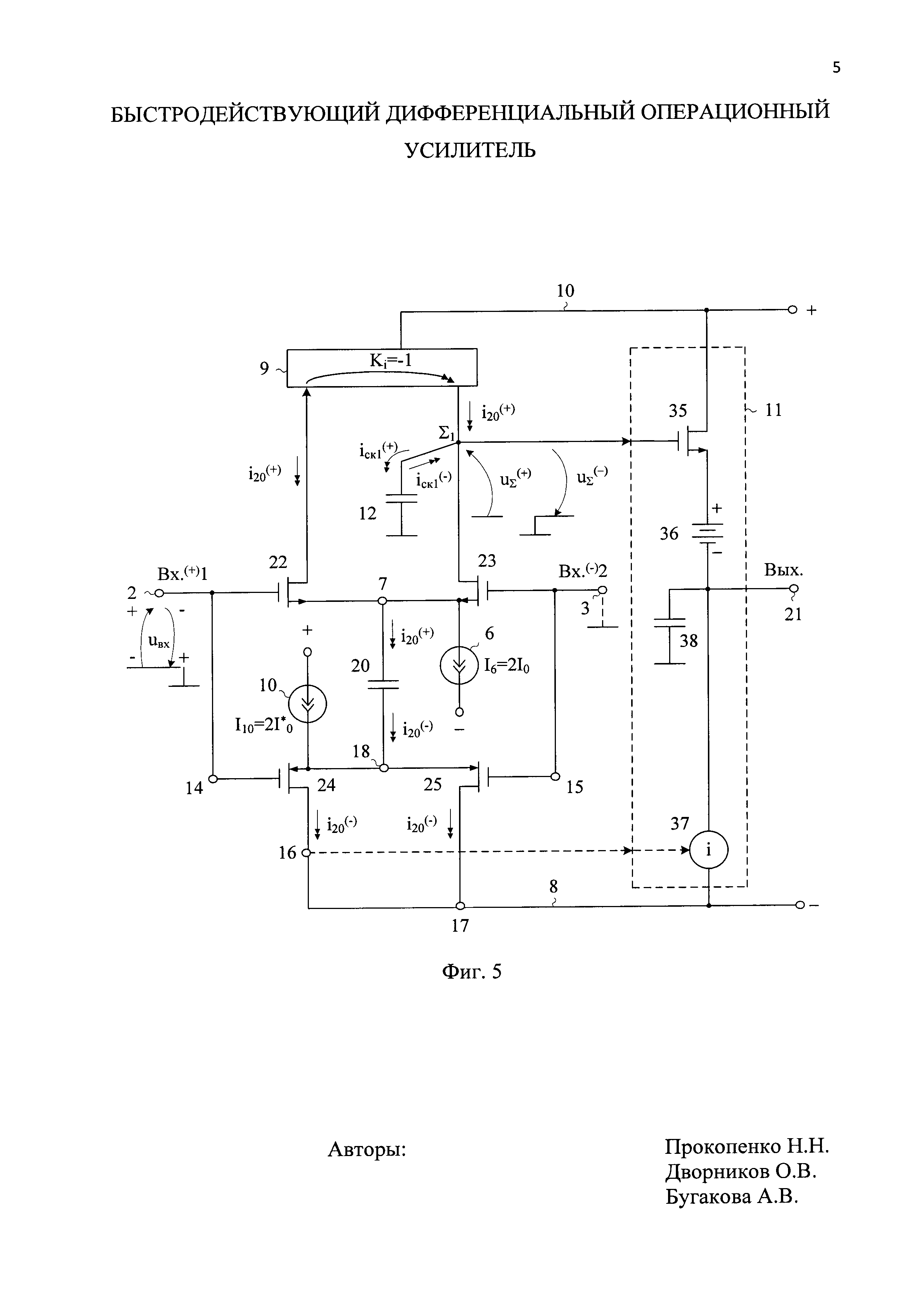

На фиг. 5, в качестве примера, приведена схема быстродействующего КМОП ОУ, соответствующего фиг. 2 с конкретным выполнением буферного усилителя (11).

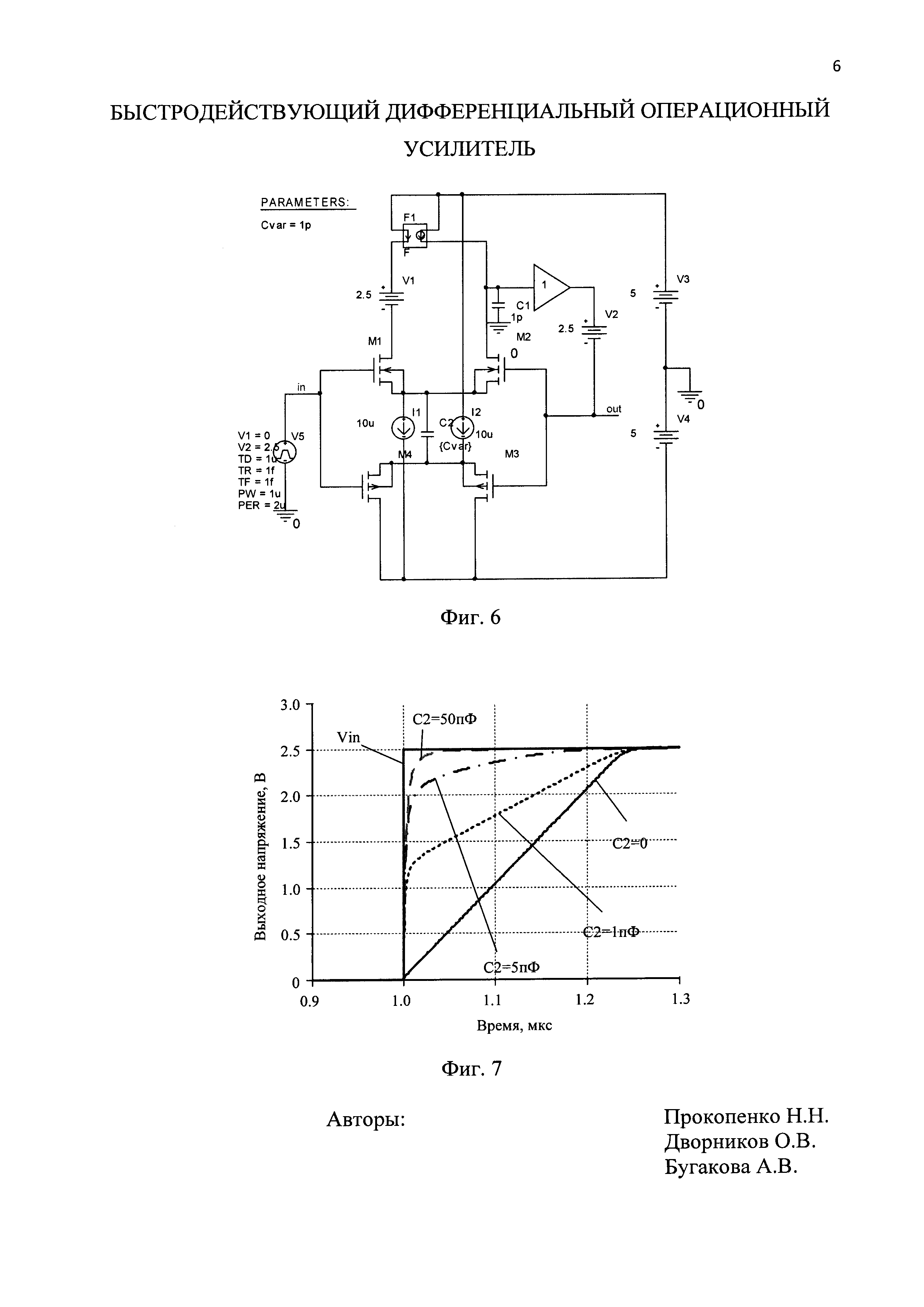

На фиг. 6 приведена схема ОУ фиг. 2 в среде Orcad на моделях КМОП транзисторов техпроцесса tsmc_035_t65.

На фиг. 7 представлены осциллограмма входного и выходного напряжений КМОП ОУ фиг. 6 (передний фронт) при разных значениях емкости конденсатора С2= Cvar, при I1=I2=10 мкА, С1=1пФ (ширина импульса 1 мкс, амплитуда входного напряжения 3 В, комнатная температура t=27°C).

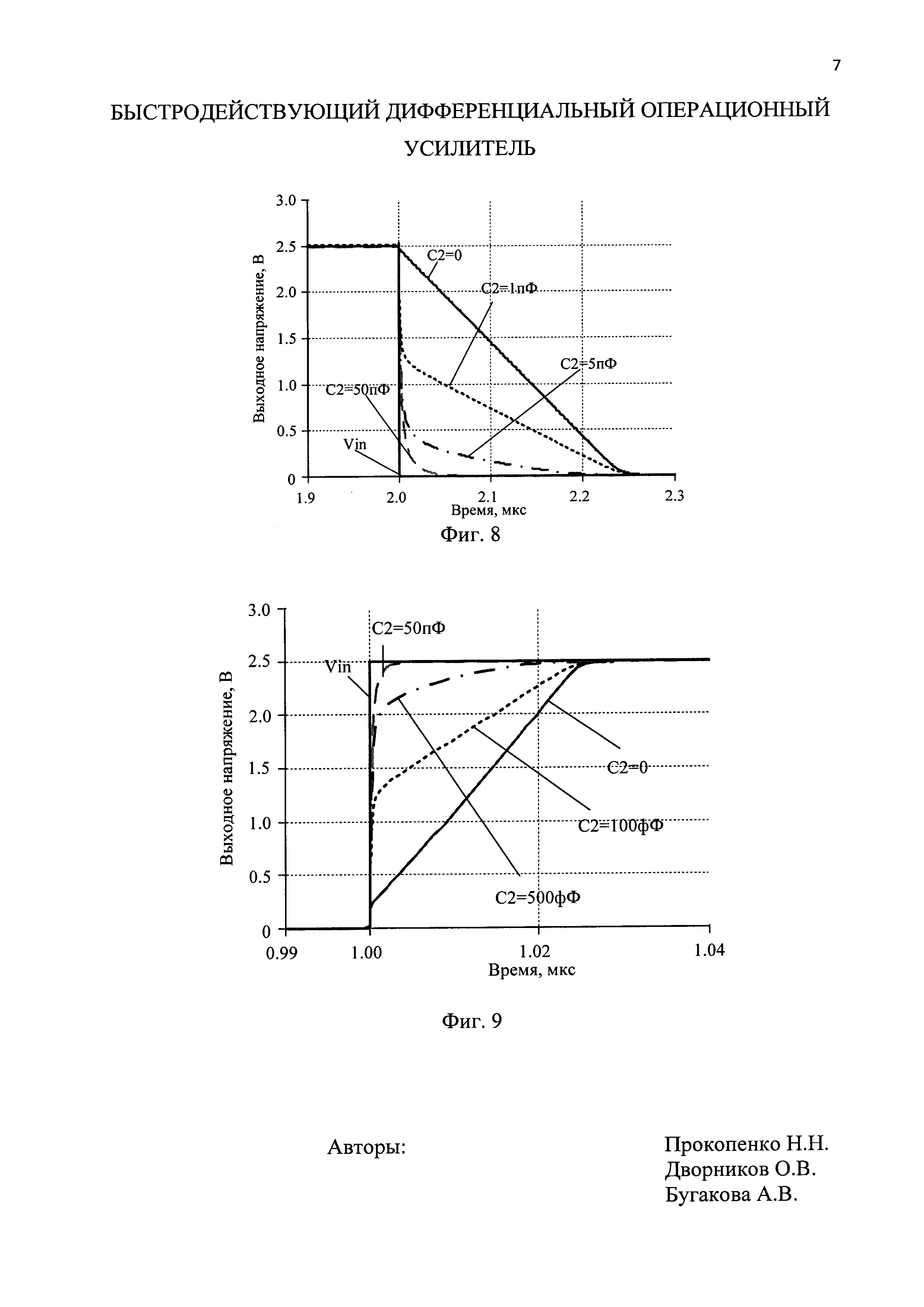

На фиг. 8 приведена осциллограмма входного и выходного напряжений КМОП ОУ фиг. 6 (задний фронт) при разных значениях емкости конденсатора С2=Cvar, при I1=I2=10 мкА, С1=1пФ (ширина импульса 1 мкс, амплитуда входного напряжения 3 В, комнатная температура t=27°C).

На фиг. 9 показана осциллограмма входного и выходного напряжений КМОП ОУ фиг. 6 (передний фронт) при разных значениях емкости конденсатора C2=Cvar, при I1=I2=10 мкА и С1=100фФ (ширина импульса 1 мкс, амплитуда входного напряжения 3 В, комнатная температура t=27°C).

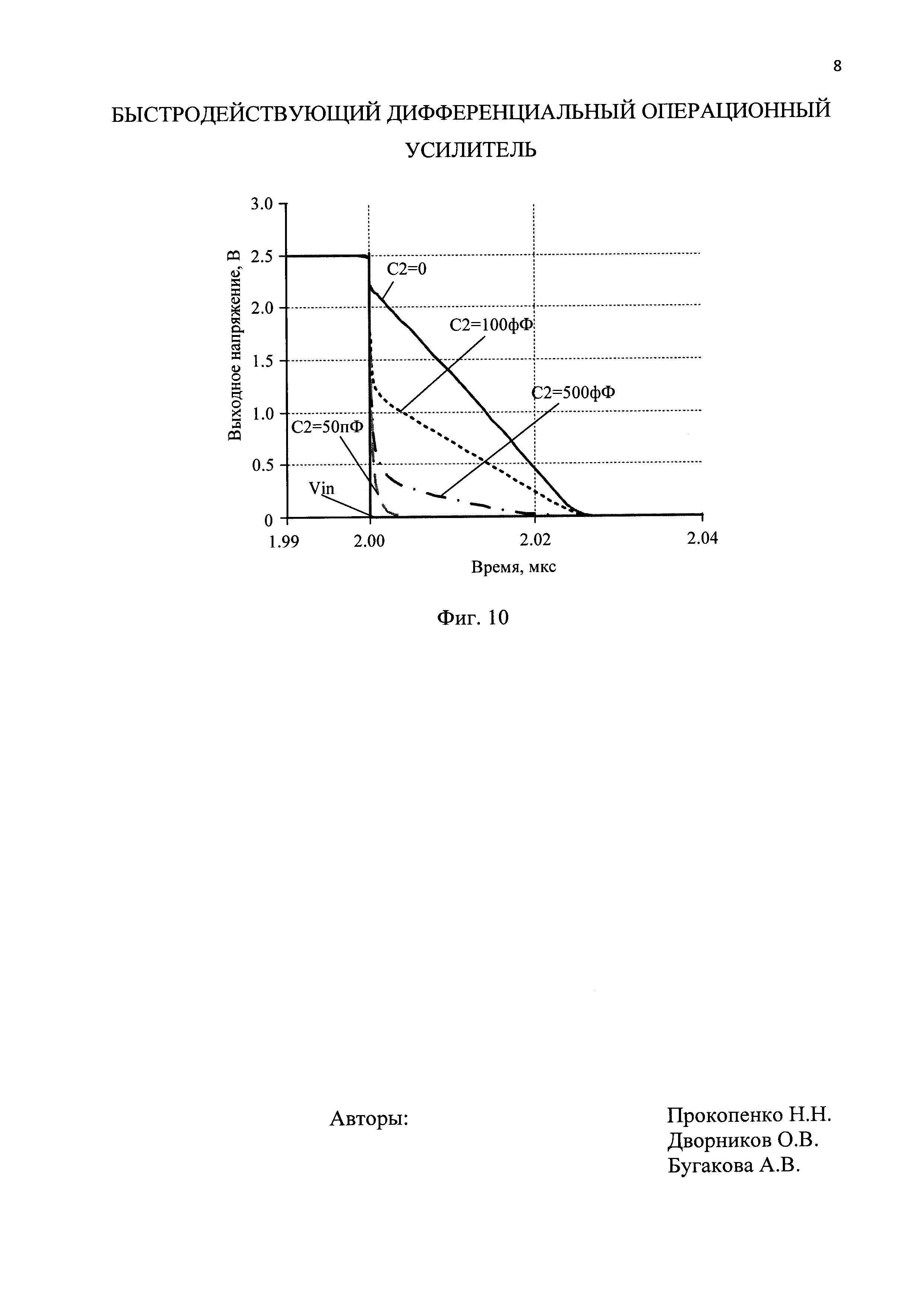

На фиг. 10 приведена осциллограмма входного и выходного напряжений КМОП ОУ фиг. 6 (задний фронт) при разных значениях емкости конденсатора С2=Cvar, при I1=I2=10 мкА и С1=100фФ.

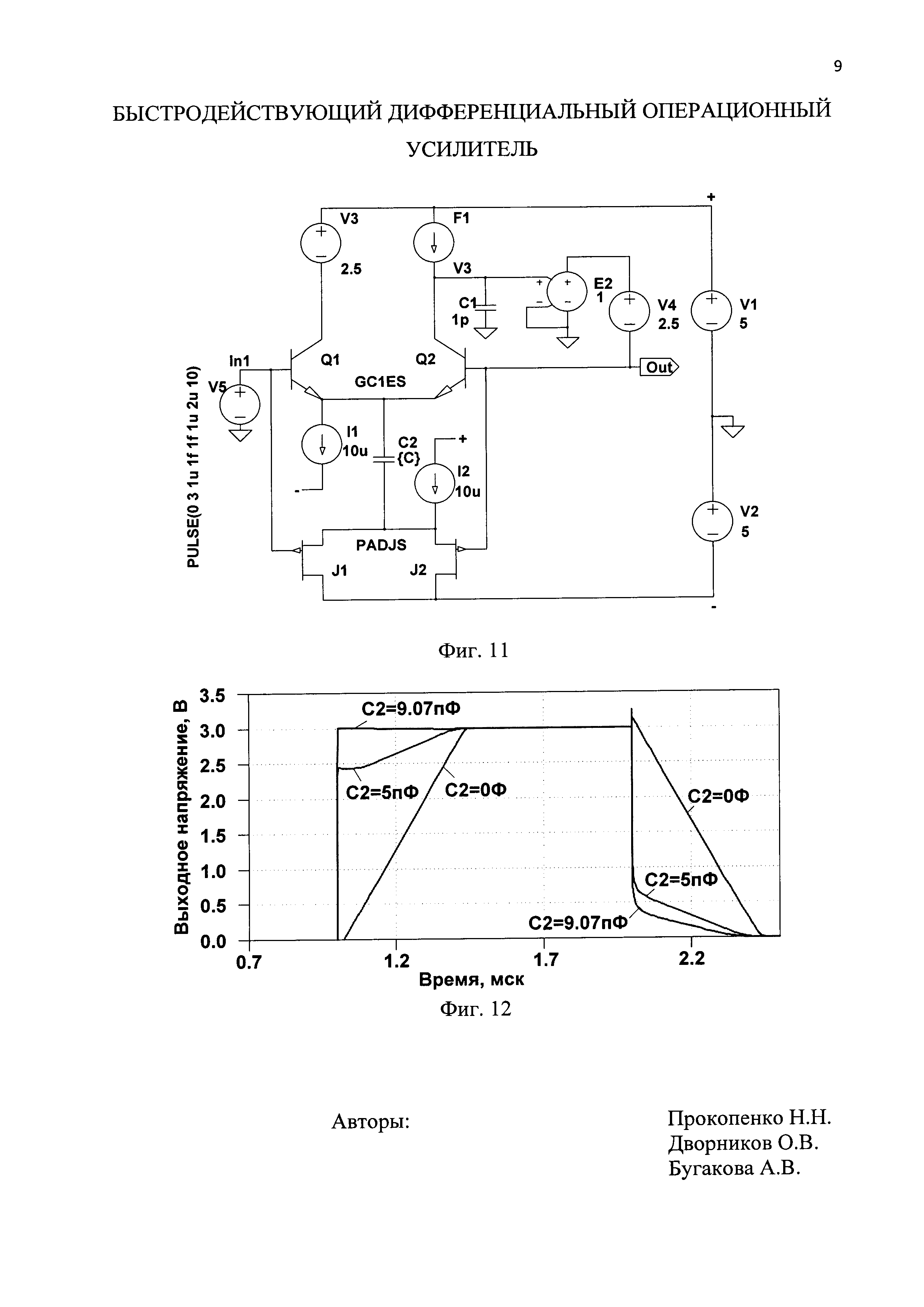

На фиг. 11 показана схема BiJFet ОУ фиг. 3 в среде LTSpice для моделирования его характеристик при низких температурах.

На фиг. 12 представлена осциллограмма выходного напряжения ОУ фиг. 11 (передний и задние фронты) при емкости конденсатора С2=0/5п/9.07пФ (амплитуда входного напряжения 3В, ширина импульса 1 мкс, t=27°C).

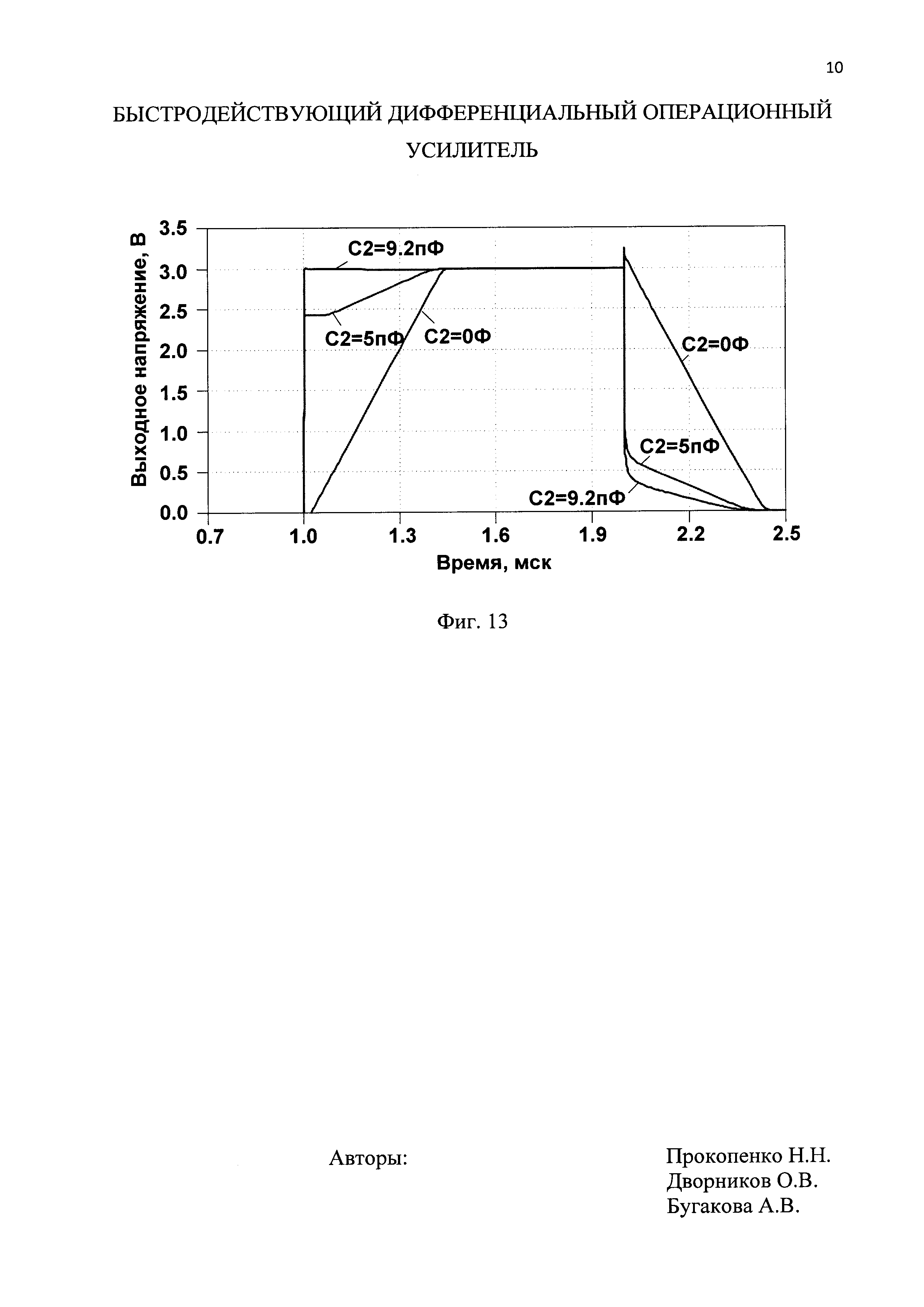

На фиг. 13 приведена осциллограмма выходного напряжения ОУ (передний и задние фронты) при емкости конденсатора С2=0/5п/9.07пФ (амплитуда входного напряжения 3В, ширина импульса 1 мкс, отрицательная температура t=-197°C).

Быстродействующий дифференциальный операционный усилитель фиг. 2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 входами, первым 4 и вторым 5 противофазными токовыми выходами, первый источник опорного тока 6, включенный между входом 7 входного дифференциального каскада 1 для установления его статического режима по току и первой 8 шиной источника питания, первое токовое зеркало 9, согласованное со второй 10 шиной источника питания, вход которого соединен с первым 4 токовом выходом входного дифференциального каскада 1, а выход подключен ко второму 5 токовому выходу входного дифференциального каскада 1 и связан со входом буферного усилителя 11, первый 12 корректирующий конденсатор, связанный со входом буферного усилителя 11. В схему введен дополнительный дифференциальный каскад 13, содержащий первый 14 и второй 15 входы, первый 16 и второй 17 противофазные токовые выходы, согласованные с первой 8 шиной источника питания, вход 18 дополнительного дифференциального каскада 13 для установления его статического режима по току, причем первый 14 вход дополнительного дифференциального каскада 13 связан с первым 2 входом входного дифференциального каскада 1, второй 15 вход дополнительного дифференциального каскада 13 связан со вторым 3 входом входного дифференциального каскада 1, между входом 18 дополнительного дифференциального каскада 13 для установления его статического режима по току и второй 10 шиной источника питания включен второй 19 источник опорного тока, между входом 7 входного дифференциального каскада 1 для установления его статического режима по току и входом 18 дополнительного дифференциального каскада 13 для установления его статического режима по току включен второй 20 корректирующий конденсатор. На фиг. 2 буферный усилитель 11 имеет потенциальный (низкоомный) выход 21.

Кроме этого на фиг. 2, в соответствии с п. 2 формулы изобретения, входной дифференциальный каскад 1 содержит первый 22 и второй 23 полевые транзисторы, объединенные истоки которых подключены ко входу 7 входного дифференциального каскада 1 для установления его статического режима по току, затвор первого 22 полевого транзистора соединен с первым 2 входом входного дифференциального каскада 1, затвор второго 23 полевого транзистора соединен с вторым 3 входом входного дифференциального каскада 1, сток первого 22 полевого транзистора соединен с первым 4 токовом выходом входного дифференциального каскада 1, сток второго 23 полевого транзистора соединен со вторым 5 токовым выходом входного дифференциального каскада 1.

На фиг. 2 в соответствии с п. 3 формулы изобретения дополнительный дифференциальный каскад 13 содержит третий 24 и четвертый 25 полевые транзисторы, объединенные истоки которых подключены ко входу 18 дополнительного дифференциального каскада 13 для установления его статического режима по току, затвор третьего 24 полевого транзистора соединен с первым 14 входом дополнительного дифференциального каскада 13, затвор четвертого 25 полевого транзистора соединен со вторым 15 входом дополнительного дифференциального каскада 13, сток третьего 24 полевого транзистора соединен с первым 16 токовом выходом дополнительного дифференциального каскада 13, сток четвертого 25 полевого транзистора соединен со вторым 17 токовом выходом дополнительного дифференциального каскада 13.

На фиг. 3 входной дифференциальный каскад 1 содержит пятый 26 и шестой 27 биполярные транзисторы, объединенные эмиттеры которых подключены к входу 7 входного дифференциального каскада 1 для установления его статического режима по току, коллектор пятого 26 биполярного транзистора соединен с первым 4 токовом выходом дифференциального каскада 1, коллектор шестого 27 биполярного транзистора соединен со вторым 5 токовым выходом входного дифференциального каскада 1, база пятого 26 биполярного транзистора соединена с первым 2 входом входного дифференциального каскада 1, база шестого 27 биполярного транзистора соединена со вторым 3 входом входного дифференциального каскада 1.

На фиг. 4 приведена схема заявляемого устройства в соответствии с п. 5 формулы изобретения, в которой выход первого 9 токового зеркала связан со входом буферного усилителя 11 через первый 28 неинвертирующий усилитель тока, первый 16 токовый выход дополнительного дифференциального каскада 13 соединен со входом дополнительного токового зеркала 29, согласованного с первой 8 шиной источника питания, выход которого подключен ко второму 17 токовому выходу дополнительного дифференциального каскада 13 и через второй 30 неинвертирующий усилитель тока связан со входом буферного усилителя 11.

Кроме этого, в схеме фиг. 4 первый 28 неинвертирующий усилитель тока реализован на транзисторе 31, включенном по схеме с общим затвором, и токостабилизирующем двухполюснике 32, а второй 30 неинвертирующий усилитель тока выполнен на основе транзистора 33, включенного по схеме с общим затвором, и токостабилизирующем двухполюснике 34.

На фиг. 5 представлено (в качестве примера) конкретное выполнение буферного усилителя 11, который содержит входной полевой транзистор 35, цепь смещения статического потенциала 36, конденсатор нагрузки 38 и источник опорного тока 37, устанавливающий статический режим буферного усилителя 11 по току. В частном случае, для ускорения процесса перезаряда конденсатора нагрузки 38, первый 16 токовый выход дополнительного дифференциального каскада 13 может подключаться к управляющему входу токостабилизирующего двухполюсника 37.

Рассмотрим работу предлагаемого ОУ на примере анализа схемы фиг. 5 при 100% отрицательной обратной связи на инвертирующий вход 3.

Максимальная скорость нарастания выходного напряжения ОУ фиг. 5 определяется скоростью перезаряда емкости первого 12 корректирующего конденсатора [18-20]. Так как ток первого 6 источника опорного тока измеряется микроамперами, то и скорость перезаряда первого 12 корректирующего конденсатора будет крайне мала.

При введении дополнительных элементов, в соответствии с п. 1 формулы изобретения, скорость перезаряда первого 12 корректирующего конденсатора существенно возрастает. Это объясняется тем, что при скачке входного напряжения ОУ, поданного на первый 2 неинвертирующих вход входного дифференциального каскада 1, через второй 20 корректирующий конденсатор появляется сравнительно большой импульс тока, который передается через транзистор 22 и токовое зеркало 9 в первый 12 корректирующий конденсатор. Как следствие, скорость перезаряда первого 12 корректирующего конденсатора существенно возрастает, что и приводит к увеличению ϑвых. ОУ на 2÷3 порядка.

Аналогично, при отрицательном импульсном сигнале на первом 2 неинвертирующем входе входного дифференциального каскада 1 через второй 20 корректирующий конденсатор формируется большой импульс тока, который через транзистор 23 поступает в высокоимпедансный узел Σ1 (на вход буферного усилителя 11) и форсирует процесс перезаряда первого 12 корректирующего конденсатора. В конечном итоге, в предлагаемом ОУ существенно (на 1÷2 порядка) повышается максимальная скорость выходного напряжения (фиг. 7 - фиг. 10, фиг. 12, фиг. 13).

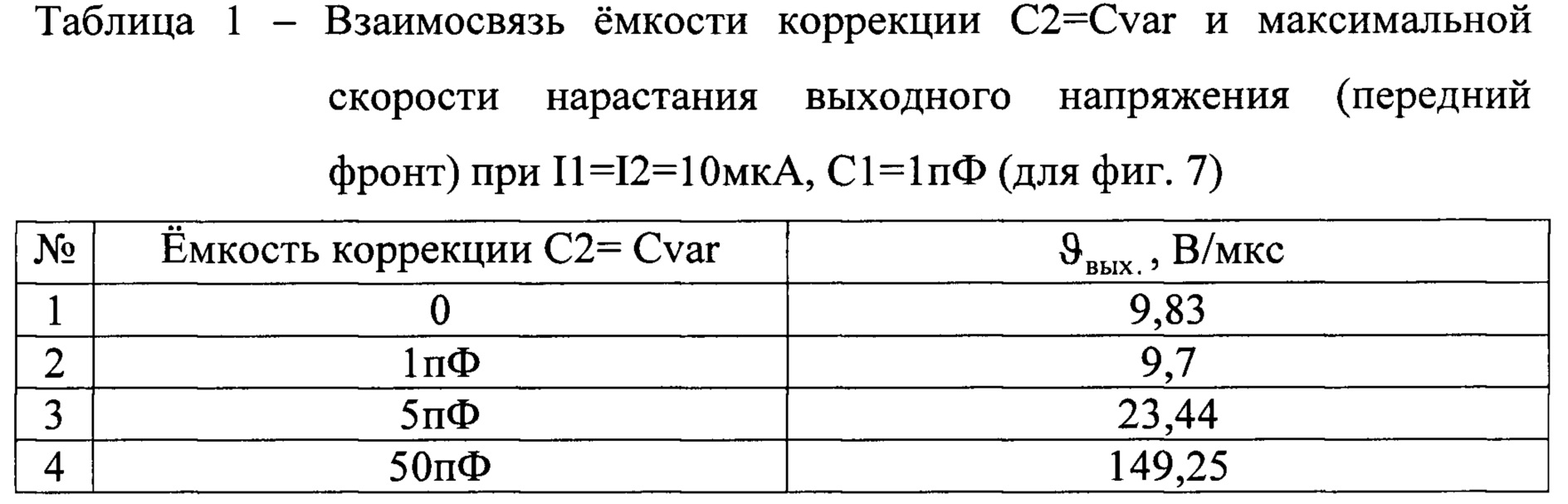

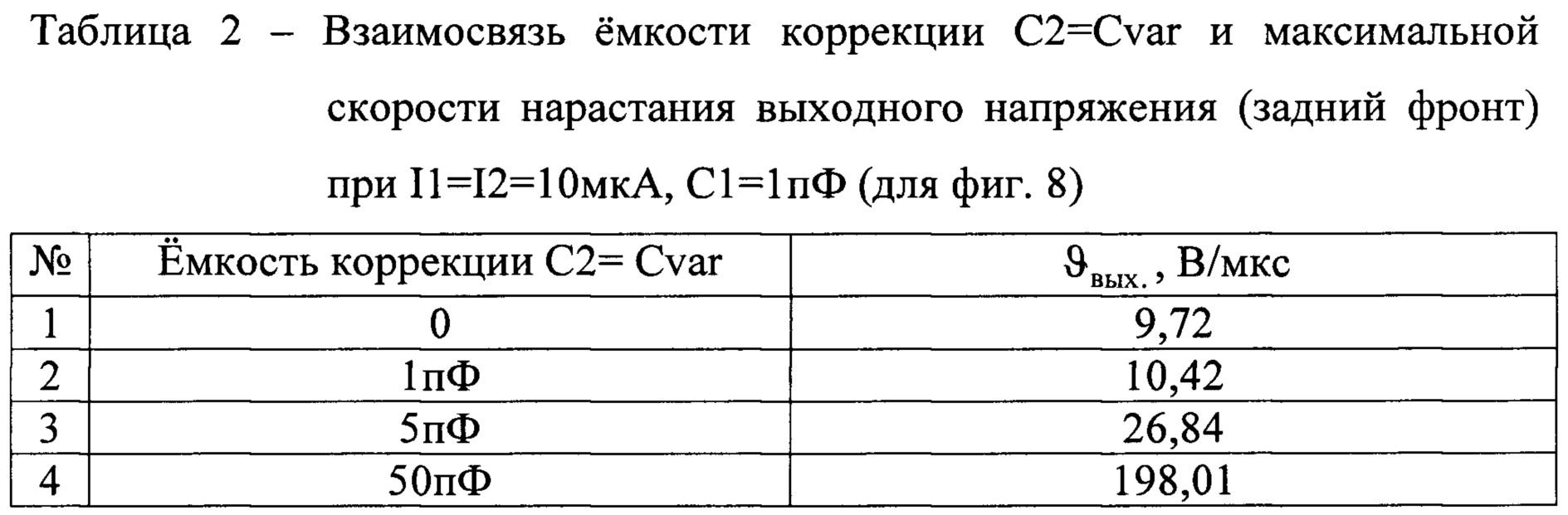

В таблицах 1 и 2 приведены результаты компьютерного моделирования (фиг. 7, фиг. 8) влияния емкости второго 20 корректирующего конденсатора КМОП ОУ фиг. 6 (техпроцесс tsmc_035_t65) на максимальную скорость нарастания входного напряжения при I1=I16=I2=I19=10 мкА, C1=C12=1пФ, при t=27°C для переднего (табл. 1) и заднего (табл. 2) фронтов.

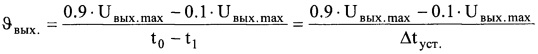

При этом среднее значение максимальной скорости нарастания выходного напряжения ОУ определялось по формуле:

.

.

где t0, t1 - время при амплитуде выходного сигнала 0.9⋅Uвых.max и 0.1⋅Uвых.max соответственно; Δtуст.=t0-t1.

Из таблиц 1, 2 следует, что для КМОП варианта ОУ фиг. 6 при С1=1 пФ выигрыш по быстродействию составляет 15-20 раз.

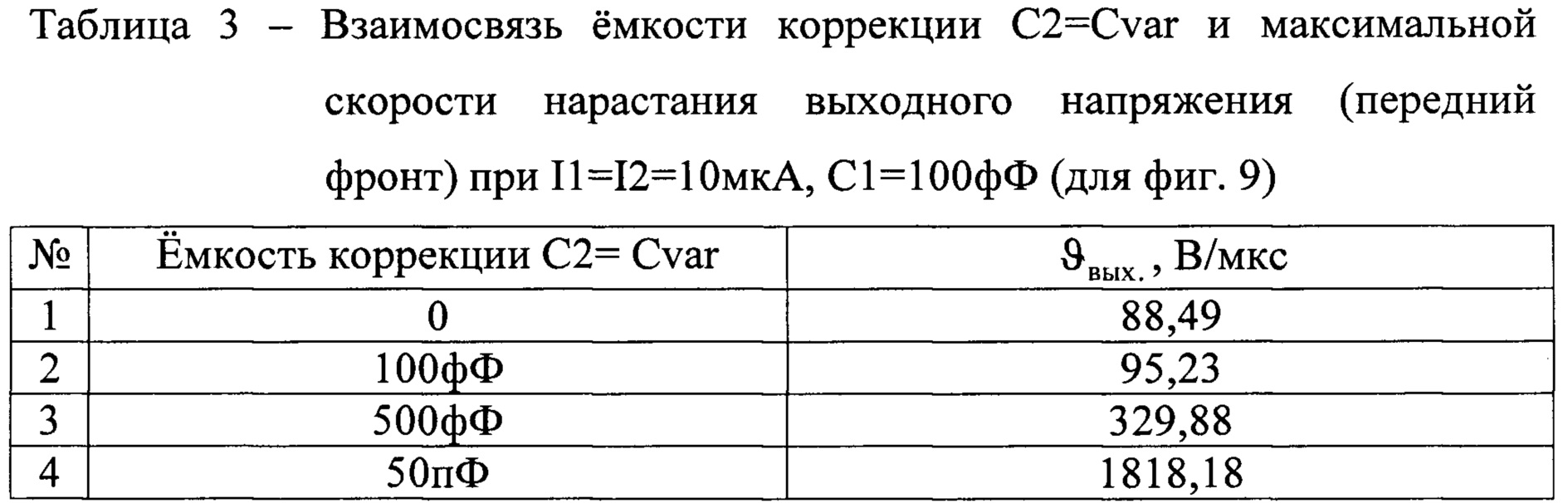

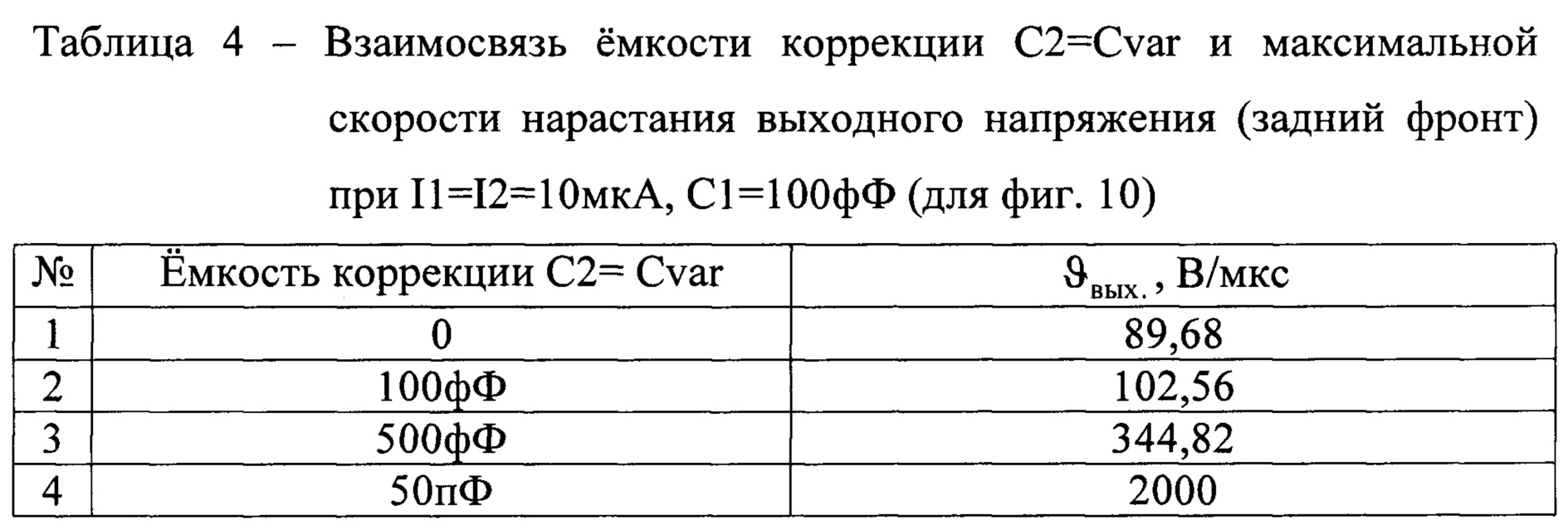

В таблицах 3 и 4 приведены результаты компьютерного моделирования (фиг. 9, фиг. 10) влияния емкости второго 20 корректирующего конденсатора КМОП ОУ фиг. 6 (техпроцесс tsmc_035_t65) на максимальную скорость нарастания входного напряжения при I1=I16=I2=I19=10 мкА при t=27°C для переднего (табл. 3) и заднего (табл. 4) фронтов и уменьшенной емкости коррекции С1=С12=100фФ.

Из таблиц 3, 4 следует, что для КМОП варианта ОУ (техпроцесс tsmc_035_t65) при С1=100 фФ выигрыш по быстродействию также составляет более 20 раз.

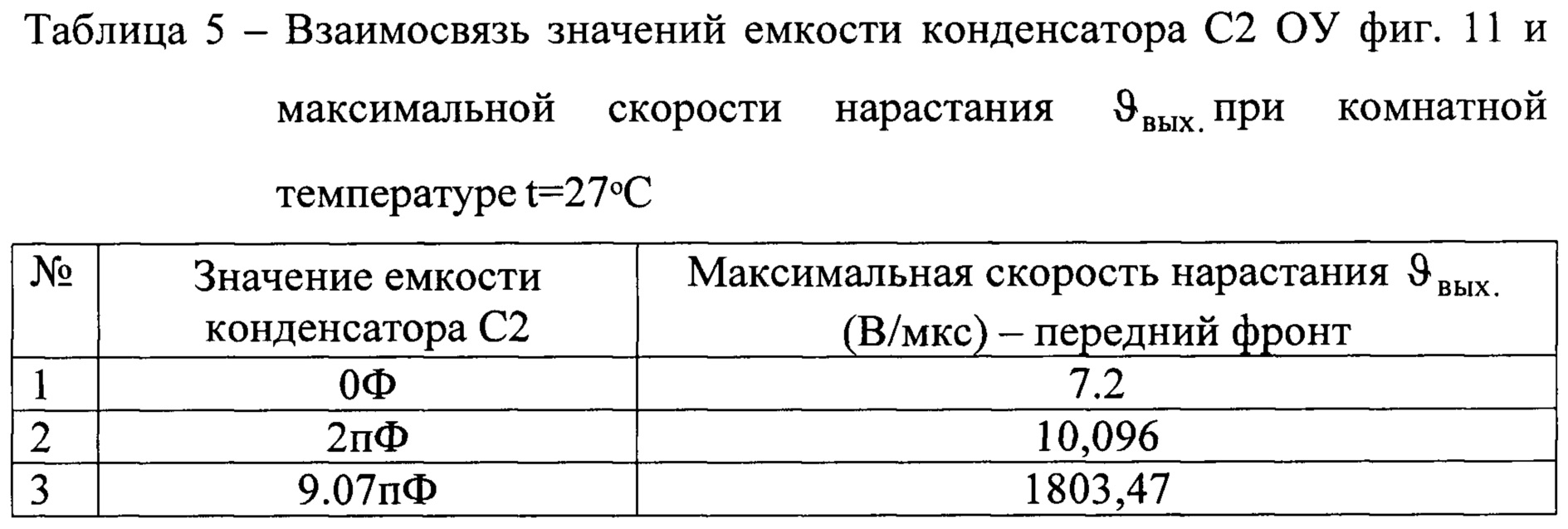

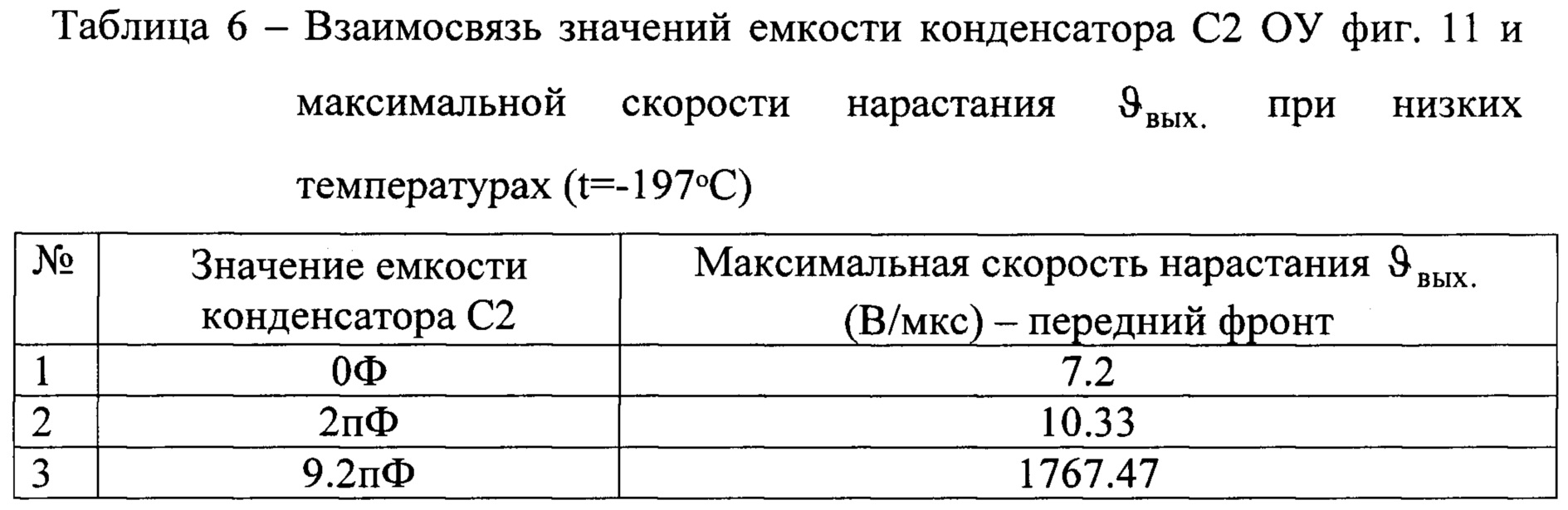

В таблицах 5-6 приведены результаты компьютерного моделирования BiJFet ОУ фиг. 11 (техпроцесс 3КБТ ОАО «Интеграл», г. Минск) влияния емкости второго 20 корректирующего конденсатора ОУ фиг. 6 на максимальную скорость нарастания входного напряжения при I1=I16=I2=I19=10 мкА, C1=C12=1 пФ, для переднего фронта при комнатной температуре t=27°C (табл. 5) и низких температурах t=-197°C (табл. 6).

Из таблицы 5 следует, что при комнатной температуре для BiJFet варианта ОУ при С 1=1 пФ выигрыш по быстродействию составляет более 250 раз.

Из таблицы 6 следует, что для BiJFet варианта ОУ при С1=1 пФ выигрыш по быстродействию при низких температурах составляет более 240 раз.

Из таблиц 1-6 следует, что быстродействие заявляемого ОУ при работе его входных транзисторов в микрорежиме повышается, в зависимости от используемого технологического процесса, на 1-2 порядка.

Причем, для BiJFet ОУ низкие температуры (-190°C) не оказывают существенного влияния на ϑвых, что обусловлено особенностями схемотехники BiJFet ОУ фиг. 3 и свойствами BiJFet технологического процесса ОАО «Интеграл» (г. Минск).

Таким образом, заявляемое устройство обладает существенными преимуществами по сравнению с прототипом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 5,343,164.

2. Патент US 6,822, 505.

3. Патент US 4,335,355.

4. Патент US 4, 912,425.

5. Патент US 6,794,840, фиг. 3.

6. Патент US 7, 167,052.

7. Патент US 5,289,058.

8. Патент US 6,822,505, фиг. 4.

9. Патент US 4,524,329, фиг. 1 - фиг. 4.

10. Заявка на патент US 2010/0085344.

11. Заявка на патент ЕР 2007/054914.

12. Заявка на патент WO 2007/135139.

13. Патент US 4,464, 588.

14. Патент US 7,646,247.

15. Патент US 5,990,742, фиг. 2.

16. Патент US 6,774,722, фиг. 2.

17. О.V. Dvornikov, V.L. Dziatlau, N.N. Prokopenko, K.О. Petrosiants, N.V. Kozhukhov and V.A. Tchekhovski, "The accounting of the simultaneous exposure of the low temperatures and the penetrating radiation at the circuit simulation of the BiJFET analog interfaces of the sensors," 2017 International Siberian Conference on Control and Communications (SIBCON), Astana, 2017, pp. 1-6. DOT. 10.1109/SIBCON.2017.7998507.

18. Анисимов В.И., Капитонов M.B., Соколов Ю.М., Прокопенко Н.Н. Операционные усилители с непосредственной связью каскадов (монография) // Л.: «Энергия», 1979. - 148 с.

19. Прокопенко Н.Н., Будяков А.С. Архитектура и схемотехника быстродействующих операционных усилителей (монография) // Шахты: ЮРГУЭС, 2006. - 232 с.

20. Прокопенко Н.Н. Нелинейная активная коррекция в прецизионных аналоговых микросхемах (монография) // Ростов-на-Дону: Изд-во Северо-Кавказского научного центра высшей школы, 2000. 222 с.