Результат интеллектуальной деятельности: Устройство для цикловой синхронизации

Вид РИД

Изобретение

Изобретение относится к технике цифровой связи, а именно к устройствам для цикловой синхронизации цифровых систем передачи информации с временным уплотнением, передаваемых в транспортных блоках оптических каналов оптической транспортной иерархии.

Битовая скорость цифровых передач, передаваемых по оптическим каналам, в настоящее время достигает примерно до 45 Гбит/с, что соответствует при однопроводном входе частоте 45 ГГц. Ведутся работы по многократному увеличению битовой скорости сигналов, передаваемых по оптоволоконным линиям связи.

Применяемые при создании устройств для цикловой синхронизации программируемые пользователем логические интегральные схемы (ППЛИС) обеспечивают работоспособность устройств при тактовой частоте сигнала до 200 МГц. Поэтому требуется распараллеливание сигналов на информационных входах устройств при высоких скоростях передач, передаваемых по оптоволоконным линиям связи.

Например, при обработке передач, передаваемых в транспортных блоках оптического канала OTU1, OTU2, OTU3, коэффициенты распараллеливания информационных сигналов соответственно равны 16, 64, 256.

Так как передачи, передаваемые в транспортных блоках OTU1, OTU2, OTU3, имеют байтовую структуру, то коэффициенты распараллеливания должны быть кратны байту (восемь бит).

Известны устройства для цикловой синхронизации (Патент РФ №2787210, H04L 7/08, Патент РФ №2224378, H04L 7/08), которые осуществляют цикловую синхронизацию различных цифровых передач при виде модуляции ФМ-2, при которой одному тактовому сигналу на входе соответствует один информационный вход. Однако эти устройства не обеспечивают цикловую синхронизацию передач с видами фазовой модуляцией ФМ-4, ФМ-8, различными видами квадратурно-амплитудной модуляции и передач, передаваемых по оптоволоконным линиям связи, когда одному тактовому сигналу соответствует k информационных сигналов, где k - коэффициент распараллеливания.

Наиболее близким по технической сущности к заявленному изобретению является выбранное в качестве прототипа устройство для цикловой синхронизации (Патент РФ №2237374, H04L 7/08), содержащее оперативные запоминающие устройства, устройство настройки и диагностики, дешифратор синхрокомбинации, генераторное оборудование, фазирующее устройство, элементный перестроитель сигналов, дешифратор и счетчик.

Недостатком данного устройства является большое количество применяемых функциональных узлов при высоких значения коэффициента распараллеливания при цикловой синхронизации передач, передаваемых в оптоволоконных линиях связи.

Технической задачей изобретения является сокращение количества функциональных узлов устройства для цикловой синхронизации передач, передаваемых в оптоволоконных линиях связи, при высоких значениях коэффициента распараллеливания.

Указанная задача решается тем, что в устройство для цикловой синхронизации, содержащее блок дешифрации синхрокомбинации, счетчик длины цикла, блок фазирования, блок восьмибитного перестроения информационных сигналов, причем информационные выходы блока восьмибитного перестроения информационных сигналов соединены с соответствующими входами блока дешифрации синхрокомбинации и являются информационными выходами устройства для цикловой синхронизации, выход блока дешифрации синхрокомбинации соединен с соответствующими входами счетчика длины цикла и блока фазирования, выход наличия фазы которого является соответствующим выходом устройства для цикловой синхронизации, а выход поиска фазы соединен с соответствующим входом счетчика длины цикла, выход конца цикла которого является соответствующим выходом устройства для цикловой синхронизации, а выход конца синхрокомбинации соединен с соответствующим входом блока фазирования, тактовый вход устройства для цикловой синхронизации соединен с соответствующими входами блока дешифрации синхрокомбинации, счетчика длины цикла и блока восьмибитного перестроения информационных сигналов, согласно изобретению введены блок байтных перестроений информационных сигналов, содержащий от однобайтного до N-байтного блоков перестроения информационных сигналов, и устройство управления блоками восьмибитного перестроения и байтных перестроений информационных сигналов, при этом информационные и тактовый входы устройства для цикловой синхронизации соединены с соответствующими входами блока байтных перестроений информационных сигналов, входы блока байтных перестроений информационных сигналов являются входами блока N-байтного перестроения информационных сигналов, выходы каждого блока байтного перестроения информационных сигналов, имеющего большее значение байтности перестроения соединены с входами блока байтного перестроения информационных сигналов, имеющего меньшее числовое значение байтности перестроения, выходы блока байтных перестроений информационных сигналов соединены с соответствующими входами блока восьмибитного перестроения информационных сигналов, входы конца синхрокомбинации и поиска фазы устройства управления блоками восьмибитного перестроения и байтных перестроений информационных сигналов соединены соответственно с соответствующими выходами счетчика длины цикла и блока фазирования, тактовые входы устройства управления блоками восьмибитного перестроения и байтных перестроений информационных сигналов соединены с тактовым входом устройства для цикловой синхронизации, выходы 1, …, 8 и А3, …, An устройства управления блоками восьмибитного перестроения и байтных перестроений информационных сигналов соединены с соответствующими входами блока восьмибитного перестроения и блока байтных перестроений информационных сигналов.

Новизна технического решения заключается в введение в заявленное устройство новых схемных элементов: блока байтных перестроений информационных сигналов и устройства управления блоком восьмибитного перестроения и блоком байтных перестроений информационных сигналов.

Таким образом, изобретение соответствует критерию "новизна".

Анализ известных технических решений в исследуемой и смежных областях позволяет сделать вывод, что введенные функциональные узлы известны. Однако введение их в устройство для цикловой синхронизации с указанными связями придает этому устройству новые свойства. Введенные функциональные узлы взаимодействуют таким образом, что позволяют осуществить сокращение функциональных узлов устройства для синхронизации передач, передаваемых в оптоволоконных линиях связи при высоких значениях коэффициента распараллеливания.

Таким образом, изобретение соответствует критерию "изобретательский уровень", т.к. оно для специалиста явным образом не следует из уровня техники.

Изобретение может быть использовано для синхронизации передач с большими битовыми скоростями при распараллеливании сигналов на входе устройств.

Таким образом, изобретение соответствует критерию "промышленная применимость".

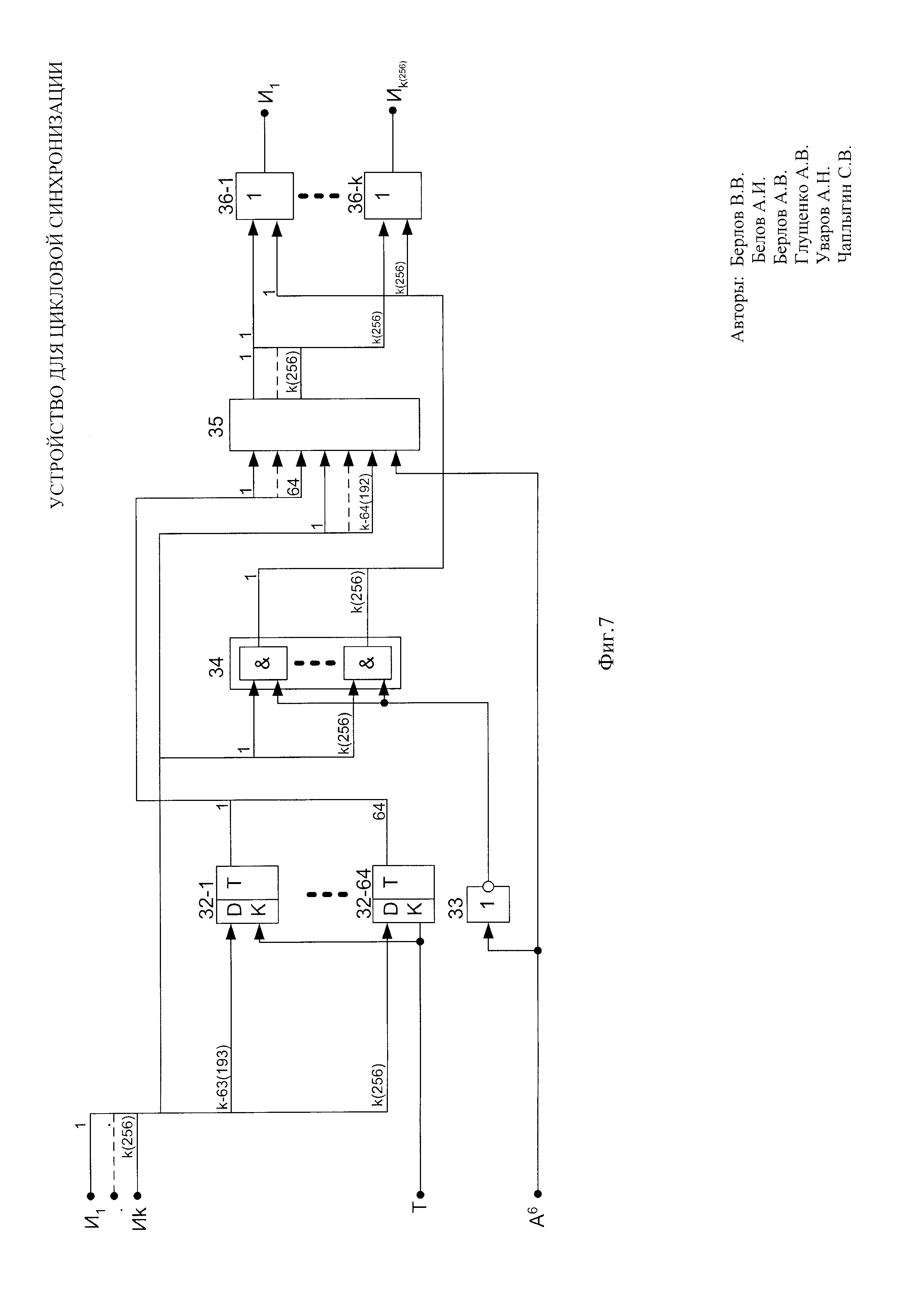

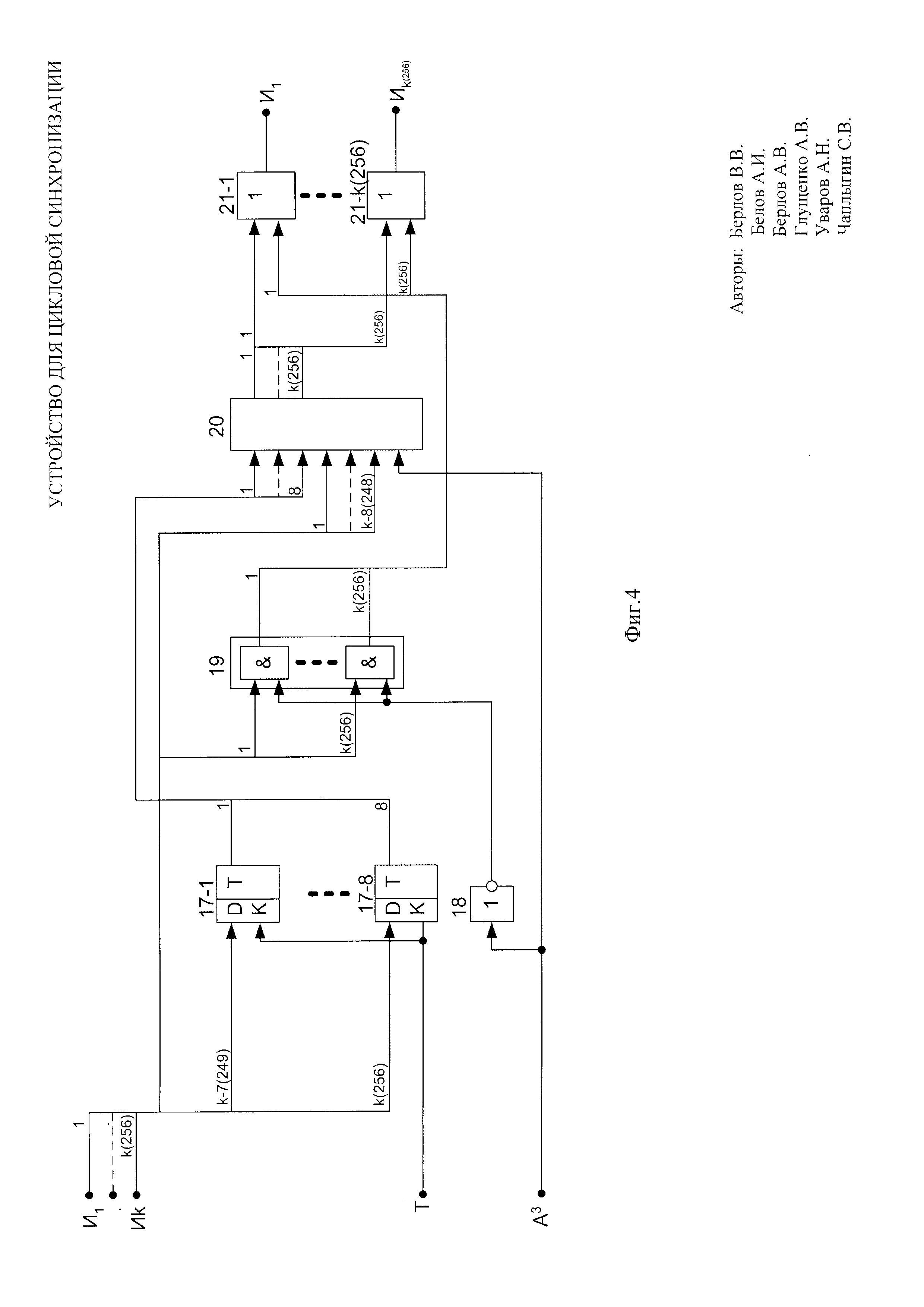

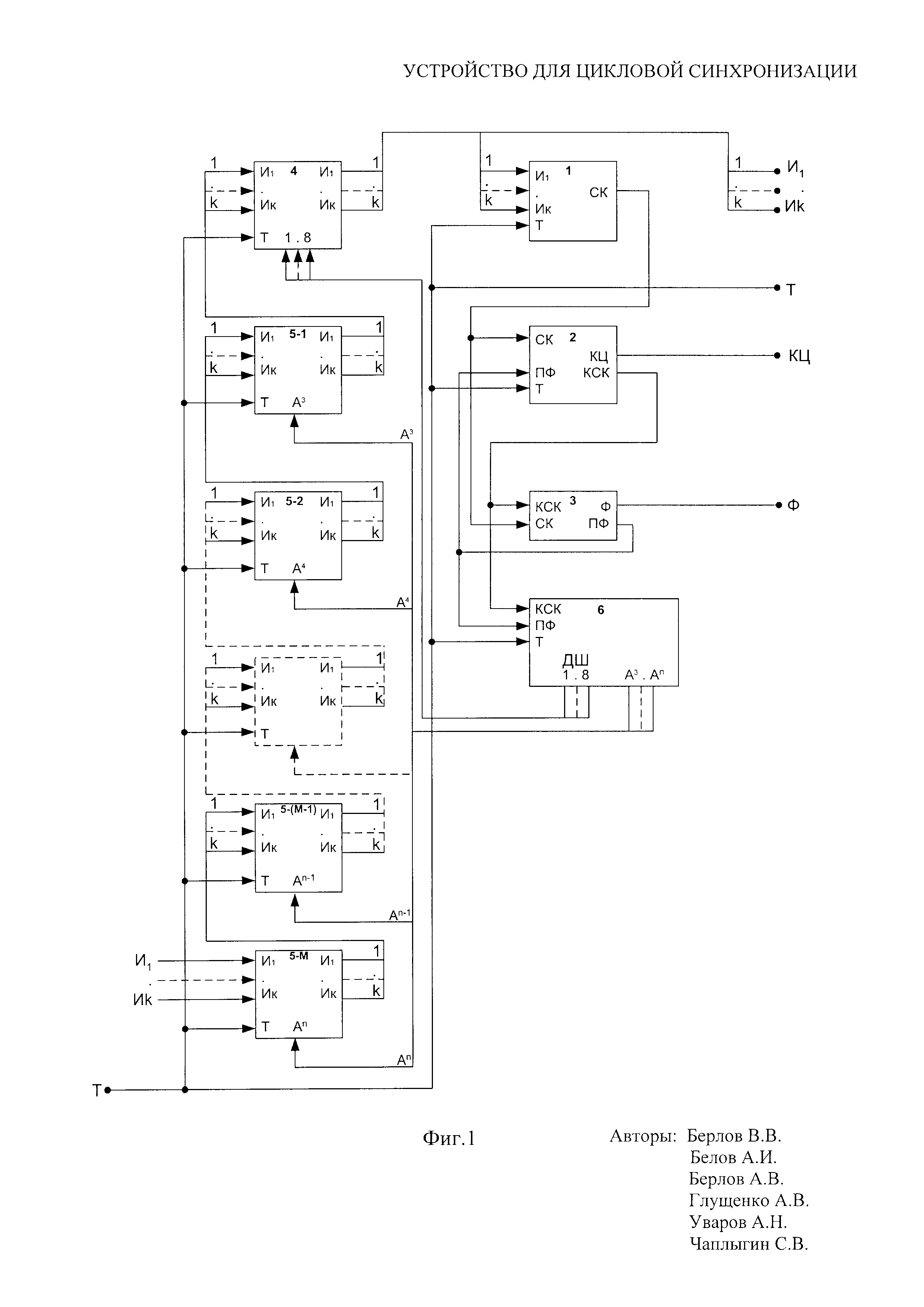

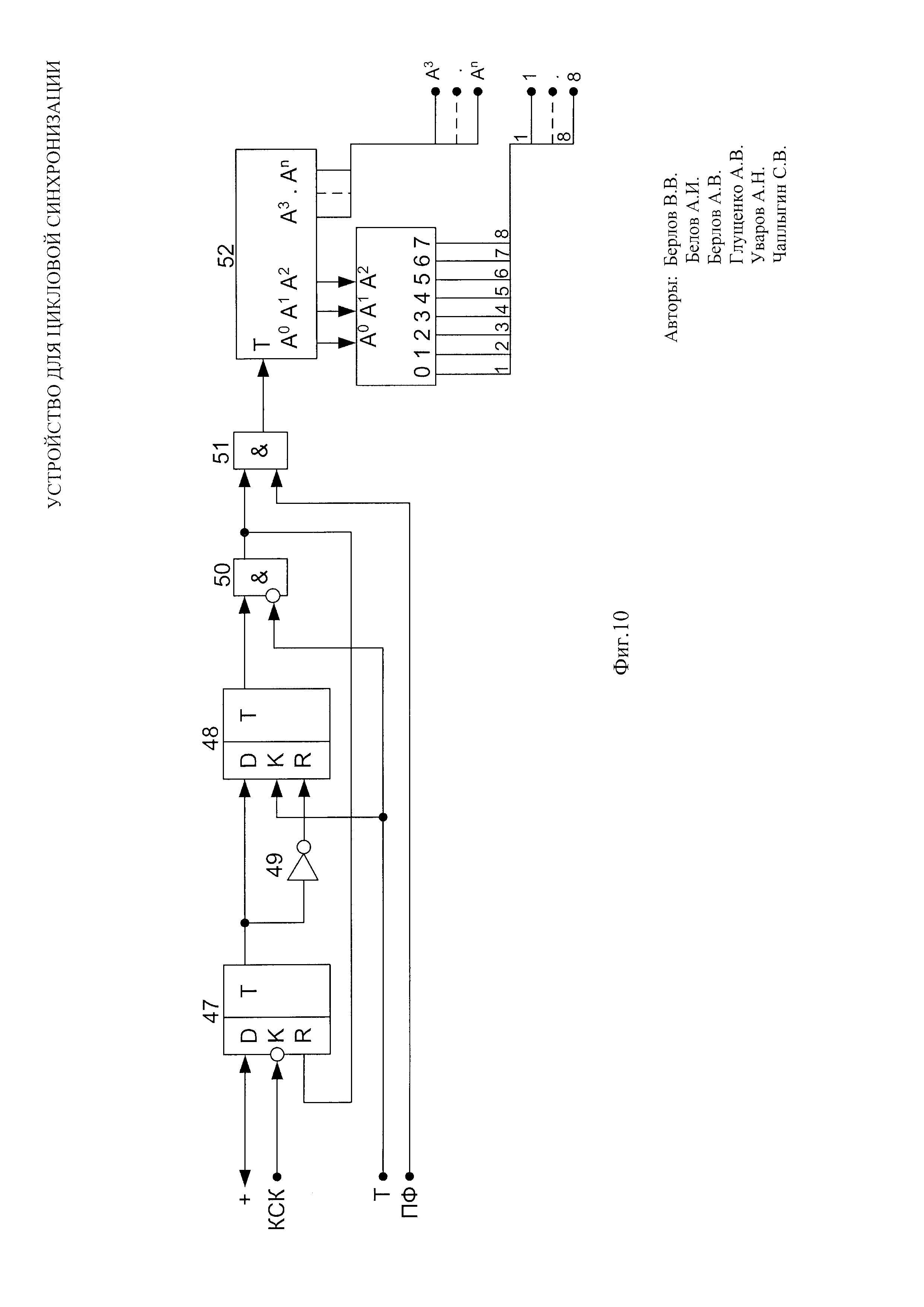

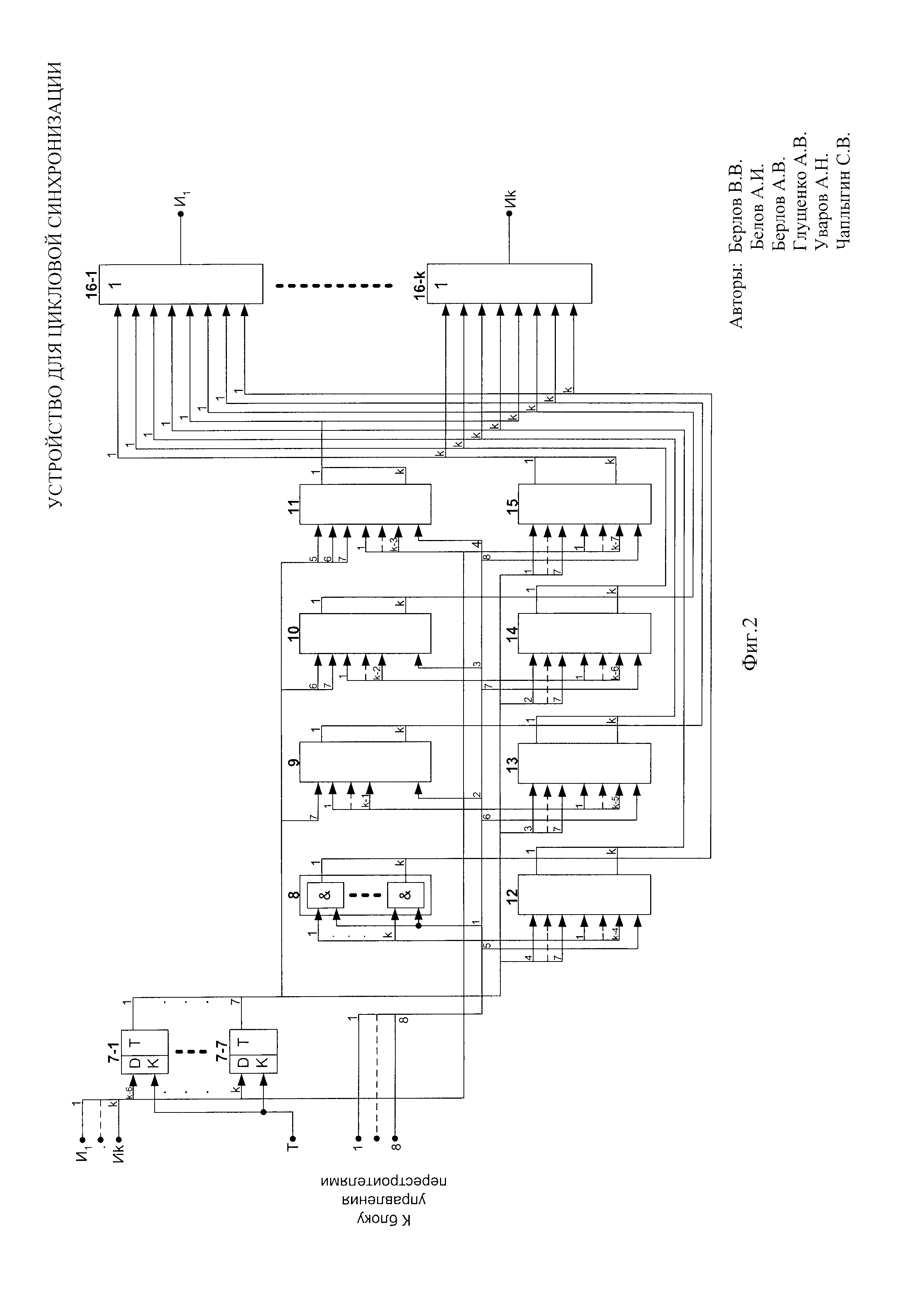

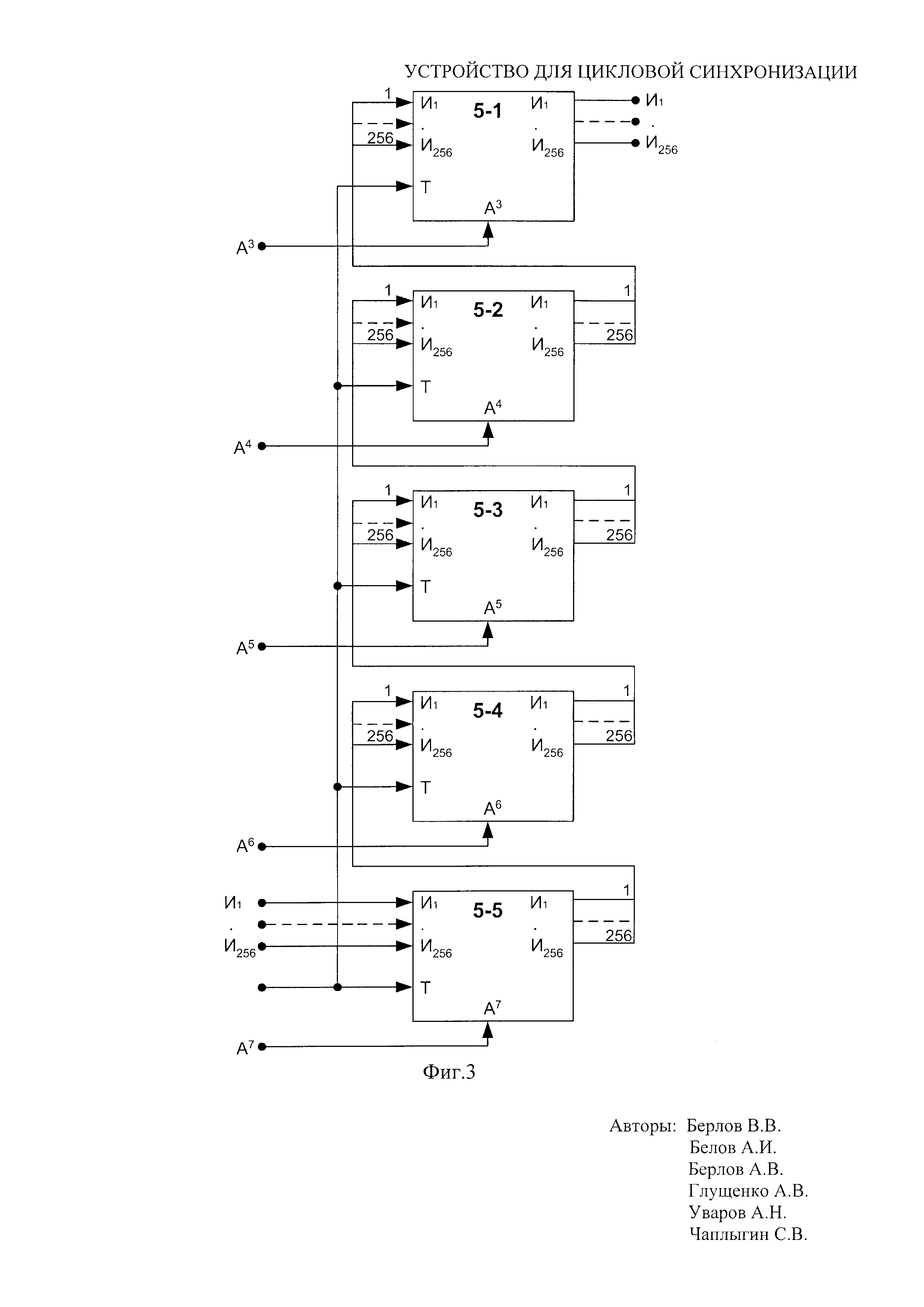

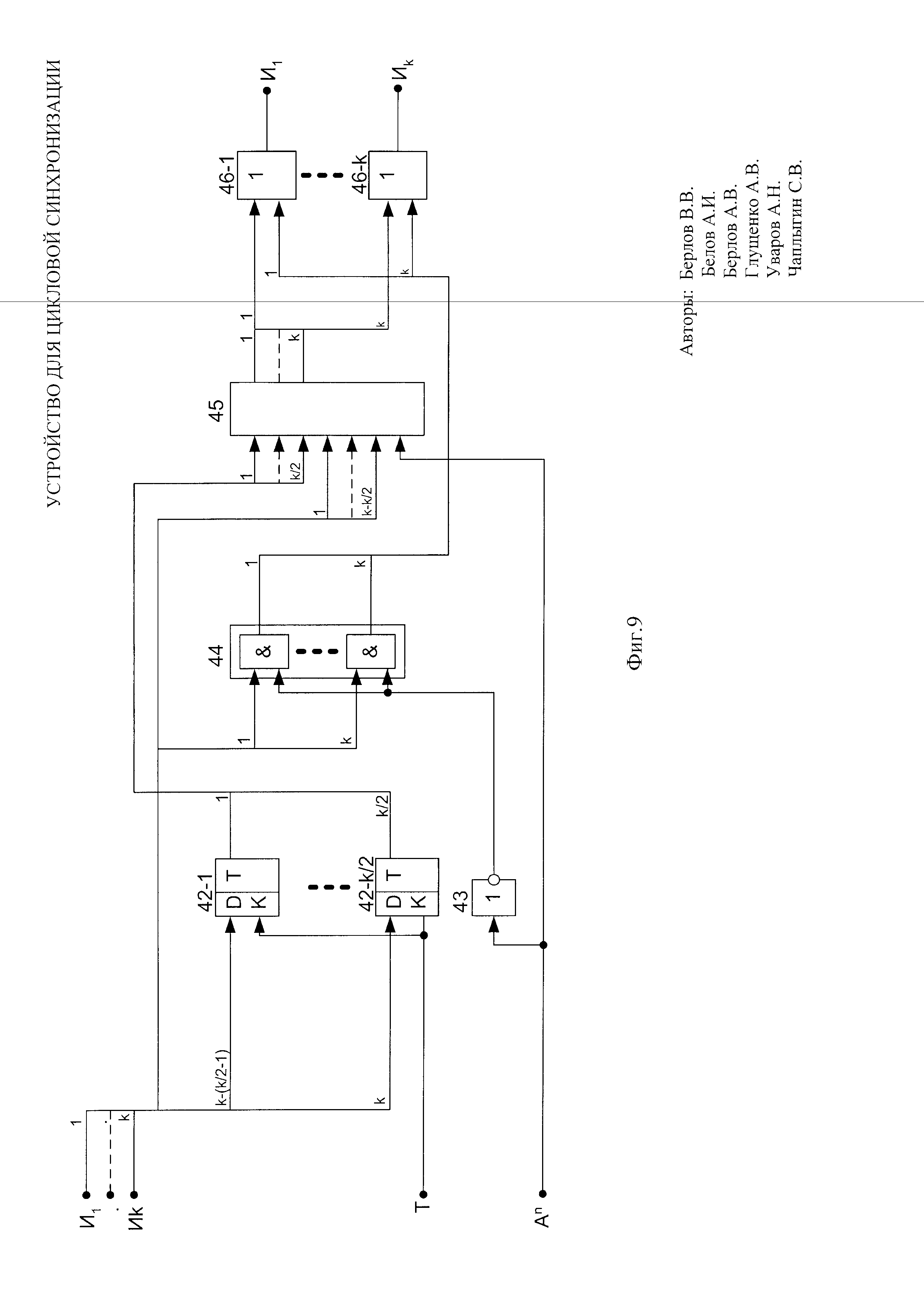

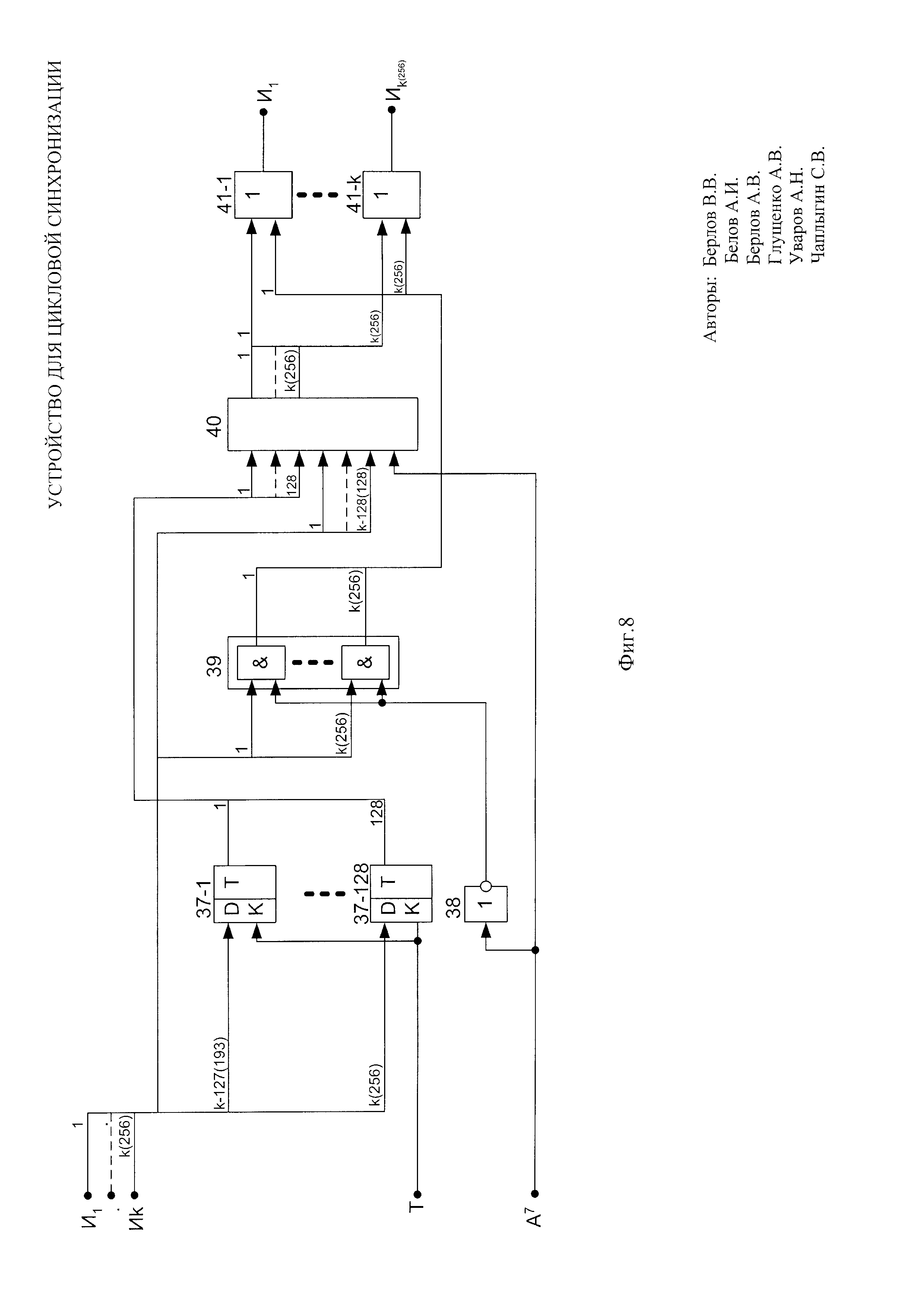

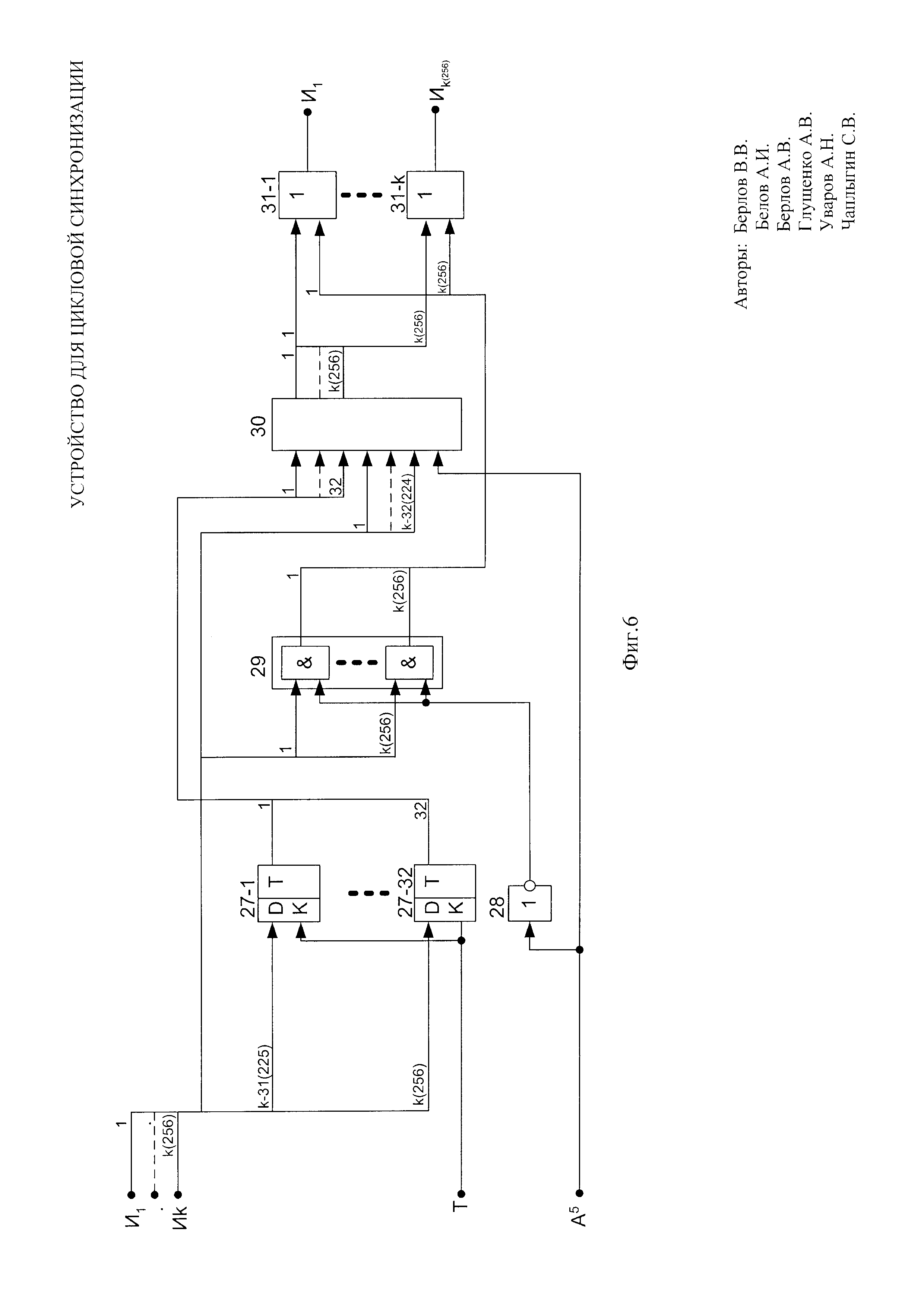

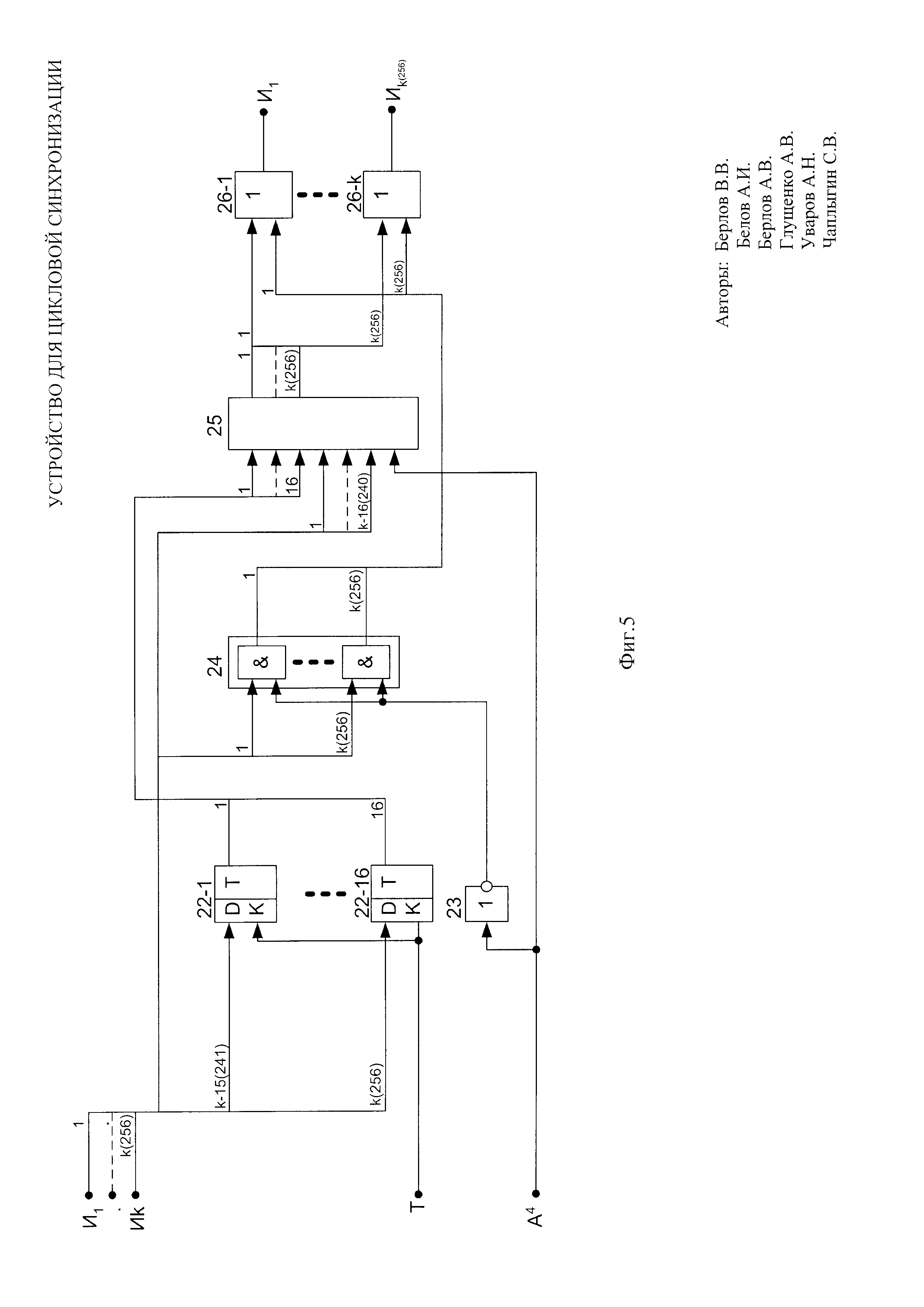

На фиг. 1 представлена структурная схема предлагаемого устройства для цикловой синхронизации (устройства для ЦС), на фиг. 2 - принципиальная электрическая схема блока восьмибитного перестроения информационных сигналов (блок восьмибитного ПИС), на фиг. 3 - пример структурной схемы блока байтных перестроений информационных сигналов (блок байтных ПИС) при коэффициенте распараллеливания информационных сигналов равном 256, на фиг. 4 - принципиальная электрическая схема блока однобайтного перестроения информационных сигналов (блок однобайтного ПИС), на фиг. 5 - принципиальная электрическая схема блока двухбайтного перестроения информационных сигналов (блок двухбайтного ПИС), на фиг. 6 - принципиальная электрическая схема блока четырехбайтного перестроения информационных сигналов (блок четырехбайтного ПИС), на фиг. 7 - принципиальная электрическая схема блока восьмибайтного перестроения информационных сигналов (блок восьмибайтных ПИС), на фиг. 8 -принципиальная электрическая схема блока шестнадцатибайтного перестроения информационных сигналов (блок шестнадцатибайтного ПИС), на фиг. 9 - принципиальная электрическая схема блока n-байтного перестроения информационных сигналов (блок n-байтного ПИС), на фиг. 10 - структурная схема устройства управления блоками восьмибитного и байтных перестроений информационных сигналов (устройство У).

Устройство для цикловой синхронизации (фиг. 1) содержит блок дешифрации синхрокомбинации 1, счетчик длины цикла 2, блок фазирования 3, блок восьмибитного перестроения информационных сигналов 4, блок байтных перестроений информационных сигналов 5, устройство управления блоками восьмибитного перестроения и байтных перестроений информационных сигналов 6, причем тактовый вход (вход Т) устройства для цикловой синхронизации (устройство для ЦС) соединен с соответствующими входами счетчика длины цикла 2, блока восьмибитного перестроения информационных сигналов (блок восьмибитного ПИС) 4, блока байтных перестроений информационных сигналов (блок байтных ПИС) 5, устройства управления блоками восьмибитного и байтных перестроений информационных сигналов (устройство У) 6, информационные входы (входы И1, …, Ик) устройства для ЦС соединены с соответствующими входами блока байтных ПИС 5, информационные выходы (выходы И1, …, Ик) которого соединены с соответствующими входами блока восьмибитного ПИС 4, информационные выходы (выходы И1, …, Ик) блока восьмибитного ПИС 4 соединены с соответствующими входами блока дешифрации синхрокомбинации 1 и являются информационными выходами устройства для ЦС, выход блока дешифрации синхрокомбинации 1 (выход СК) соединен с соответствующими входами счетчика длины цикла 2 и блока фазирования 3, выход наличия фазы (выход Ф) которого является соответствующим выходом устройства для ЦС, а выход поиска фазы (выход ПФ) - соединен с соответствующим входом счетчика длины цикла 2 и устройства У 6, выход конца цикла (выход КЦ) счетчика длины цикла 2 является соответствующим выходом устройства для ЦС, а выход конца синхрокомбинации (выход КСК) соединен с соответствующими входами блока фазирования 3 и устройства У 6, выходы 1, …, 8 и А3, …, An устройства У 6 соединены с соответствующими входами блока восьмибитных ПИС 4 и блока байтных ПИС 5.

Блок восьмибитного перестроения информационных сигналов (блок восьмибитного ПИС) 4 (фиг. 2) содержит с первого по седьмой триггеры запоминания (триггеры 7-1, …, 7-7), с первого по восьмой (8, …, 15) коммутаторы, каждый из которых содержит К двухвходовых элементов И, и с первого по К-й (16-1, …, 16-К) восьмивходовые элементы ИЛИ, при этом информационные входы триггеров 7-1, …7-7 соединены соответственно с информационными входами Ик-6, …, Ик блока восьмибитного ПИС 4, входы 1, …, К первого коммутатора 8 соединены соответственно с информационными входами И1, …, Ик блока восьмибитного ПИС 4, входы 1, …, К-1 второго коммутатора 9 соединены соответственно с информационными входами И, …, Ик-1 блока восьмибитного ПИС 4, а вход 7 коммутатора 9 соединен с выходом триггера запоминания 7-7, входы 1, …К-2 третьего коммутатора 10 соединены соответственно с информационными входами И1, …, Ик-2 блока восьмибитного ПИС 4, а входы 6, 7 коммутатора 10 соединены с выходами соответственно триггеров 7-6 и 7-7, входы 1, …, К-3 четвертого коммутатора 11 соединены соответственно с информационными входами И1, …, Ик-3 блока восьмибитного ПИС 4, а входы 5, …, 7 коммутатора 11 соединены с выходами соответственно триггеров 7-5, …, 7-7, входы 1, …, К-4 пятого коммутатора 12 соединены соответственно с информационными входами И1, …, Ик-4 блока восьмибитного ПИС 4, а входы 4, …, 7 коммутатора 12 соединены с выходами соответственно триггеров 7-4, …, 7-7, входы 1, …, К-5 шестого коммутатора 13 соединены соответственно с информационными входами И1, …, Ик-5 блока восьмибитного ПИС 4, а входы 3, …, 7 коммутатора 13 соединены с выходами соответственно триггеров 7-3, …7-7, входы 1, …, К-6 седьмого коммутатора 14 соединены соответственно с информационными входами И1, …, Ик-6 блока восьмибитного ПИС 4, а входы 2, …, 7 коммутатора 14 соединены с выходами соответственно триггеров 7-2, …7-7, входы 1, …, К-7 восьмого коммутатора 15 соединены соответственно с информационными входами И1, …, Ик-7 блока восьмибитного ПИС 4, а входы 1, …, 7 коммутатора 15 соединены с выходами соответственно триггеров 7-1, …, 7-7, входы управления коммутаторов 8, …, 15 соединены соответственно с входами 1 …, 8 блока восьмибитного ПИС 4, выходы 1, …, К коммутаторов 8, …, 15 соединены соответственно с входами восьмивходовых элементов ИЛИ 16-1, …, ИЛИ 16-К, выходы элементов ИЛИ 16-1, …, ИЛИ 16-К соединены соответственно с выходами И1, …, Ик блока восьмибитного ПИС 4.

Блок байтных перестроений информационных сигналов (блок байтных ПИС) 5 (фиг. 3) при коэффициенте распараллеливания информационных сигналов, равном 256, содержит блок однобайтного ПИС 5-1, блок двухбайтного ПИС 5-2, блок четырехбайтного ПИС 5-3, блок восьмибайтного ПИС 5-4 и блок шестнадцатибайтного ПИС 5-5, при этом информационные входы И1, …, И256 блока байтных ПИС 5 соединены с соответствующими входами блока шестнадцатибайтного ПИС 5-5, выходы которого соединены с соответствующими входами блока восьмибайтного ПИС 5-4, выходы блока восьмибайтного ПИС 5-4 соединены с соответствующими входами блока четырехбайтного ПИС 5-3, выходы которого соединены с соответствующими входами блока двухбайтного ПИС 5-2, выходы блока двухбайтного ПИС 5-2 соединены с соответствующими входами блока однобайтного ПИС 5-1, выходы блока однобайтного ПИС 5-1 соединены соответственно с информационными выходами блока байтовых ПИС 5, тактовый вход Т которого соединен с соответствующими входами блоков однобайтного ПИС 5-1, двухбайтного ПИС 5-2, четырехбайтного ПИС 5-4, восьмибайтного ПИС 5-4 и шестнадцатибайтного ПИС 5-5, входы управления А3, А4, А5, А6, А7 соответственно блоков однобайтного ПИС 5-1, двухбайтного ПИС 5-2, четырехбайтного ПИС 5-3, восьмибайтного ПИС 5-4 и шестнадцатибайтного ПИС 5-5 соединены с соответствующими входами блока байтных ПИС 5.

Блок однобайтного ПИС 5-1 (фиг. 4) содержит триггеры запоминания 17-1, …, 17-8, инвертор 18, коммутаторы 19, 20, каждый из которых состоит из К двухвходовых элементов И, и К двухвходовых элементов ИЛИ 21-1, …, 21-К, при этом информационные входы триггеров запоминания 17-1, …, 17-8 и их тактовые входы соединены соответственно с информационными входами Ик-7, …, Ик и тактовым входом Т блока однобайтного ПИС 5-1, информационные входы 1, …, К коммутатора 19 соединены с информационными входами И1, …, Ик блока однобайтного ПИС 5-1, информационные входы И1, …, Ик-8 которого соединены соответственно с входами коммутатора 20, выходы триггеров запоминания 17-1, …, 17-8 соединены с соответствующими входами коммутатора 20, вход управления А3 блока однобайтного ПИС 5-1 соединен со входом инвертора 18 и входом управления коммутатора 20, выход инвертора 18 соединен с входом управления коммутатора 19, выходы коммутаторов 19, 20 соединены с соответствующими входами двухвходовых элементов ИЛИ 21-1, …, 21-К, выходы которых являются информационными выходами И1, …, Ик блока однобайтного ПИС 5-1.

Блок двухбайтного ПИС 5-2 (фиг. 5) содержит триггеры запоминания 21-1, …, 22-16, инвертор 23, коммутаторы 24, 25, каждый из которых состоит из К двухвходовых элементов И, и К двухвходовых элементов ИЛИ 26-1, …, 26-К, при этом информационные входы триггеров запоминания 22-1, …, 22-16 и их тактовые входы соединены соответственно с информационными входами Ик-15, …, Ик и тактовым входом Т блока двухбайтного ПИС 5-2, информационные входы коммутатора 24 соединены соответственно с информационными входами И1, …, Ик блока двухбайтного ПИС 5-2, информационные входы И1, …, Ик-16 которого соединены соответственно с входами коммутатора 25, выходы триггеров запоминания 22-1, …, 26-16 соединены с соответствующими входами коммутатора 25, вход управления А4 блока двухбайтного ПИС 5-2 соединен с входом инвертора 23 и входом управления коммутатора 25, выход инвертора 23 соединен с входом управления коммутатора 24, выходы коммутаторов 24, 25 соединены с соответствующими входами двухвходовых элементов ИЛИ 26-1, …, 26-К, выходы которых являются информационными выходами И1, …, Ик блока двухбайтного ПИС 5-2.

Блок четырехбайтного ПИС 5-3 (фиг. 6) содержит триггеры запоминания 27-1, …, 27-32, инвертор 28, коммутаторы 29, 30, каждый из которых состоит из К двухвходовых элементов И, и К двухвходовых элементов ИЛИ 31-1, …, 31-К, при этом информационные входы триггеров запоминания 27-1, …, 27-32 и их тактовые входы соединены соответственно с информационными входами Ик-31 …, Ик и тактовым входом Т блока четырехбайтного ПИС 5-3, информационные входы коммутатора 29 соединены соответственно с информационными входами И1, …, Ик блока четырехбайтного ПИС 5-3, информационные входы И1, …, Ик-32 которого соединены соответственно с входами коммутатора 30, выходы триггеров запоминания 27-1, …, 27-32 соединены с соответствующими входами коммутатора 30, вход управления А5 блока четырехбайтного ПИС 5-3 соединен с входом инвертора 28 и входом управления коммутатора 30, выход инвертора 28 соединен с входом управления коммутатора 29, выходы коммутаторов 29, 30 соединены с соответствующими входами двухвходовых элементов ИЛИ 31-1, …, 31-К, выходы которых являются информационными выходами И1, …, Ик блока четырехбайтного ПИС 5-3.

Блок восьмибайтного ПИС 5-4 (фиг. 7) содержит триггеры запоминания 32-1, …, 32-64, инвертор 33, коммутаторы 34, 35, каждый из которых состоит из К двухвходовых элементов И, и К двухвходовых элементов ИЛИ 36-1, …, 36-К, при этом информационные входы триггеров запоминания 32-1, …, 34-64 и их тактовые входы соединены соответственно с информационными входами Ик-63, …, Ик и тактовым входом Т блока восьмибайтного ПИС 5-4, информационные входы коммутатора 34 соединены соответственно с информационными входами И1, …, Ик блока восьмибайтного ПИС 5-4, информационные входы И1, …, Ик-64 которого соединены соответственно с входами коммутатора 25, выходы триггеров запоминания 32-1, …, 32-64 соединены с соответствующими входами коммутатора 35, вход управления А6 блока восьмибайтного ПИС 5-4 соединен с входом инвертора 33 и входом управления коммутатора 35, выход инвертора 33 соединен с входом управления коммутатора 34, выходы коммутаторов 34, 35 соединены с соответствующими входами двухвходовых элементов 36-1, …, 36-К, выходы которых являются информационными выходами И1, …, Ик блока восьмибайтного ПИС 5-4.

Блок шестнадцатибайтного ПИС 5-5 (фиг. 8) содержит триггеры запоминания 31-1, …, 37-128, инвертор 38, коммутаторы 39, 40, каждый из которых состоит из К двухвходовых элементов И, и К двухвходовых элементов ИЛИ 41-1, …, 41-К, при этом информационные входы триггеров запоминания 37-1, …, 37-128 и их тактовые входы соединены соответственно с информационными входами Ик-127, …, Ик и тактовым входом Т блока шестнадцатибайтного ПИС 5-5, информационные входы коммутатора 39 соединены соответственно с информационными входами И1, …, Ик блока шестнадцатибайтного ПИС 5-5, информационные входы И1, …, Ик-128 которого соединены соответственно с входами коммутатора 40, выходы триггеров запоминания 37-1, …, 37-128 соединены с соответствующими входами коммутатора 40, вход управления А7 блока шестнадцатибайтного ПИС 5-5 соединен с входом инвертора 38 и входом управления коммутатора 40, выход инвертора 40 соединен с входом управления коммутатора 39, выходы коммутаторов 39, 40 соединены с соответствующими входами двухвходовых элементов ИЛИ 41-1, …, 41-К, выходы которых являются информационными выходами И1, …, Ик блока шестнадцатибайтного ПИС 5-5.

Блок N-байтного ПИС 5-М (фиг. 9) содержит триггеры запоминания 42-1, …, 42-к/2, инвертор 43, коммутаторы 44, 45, каждый из которых состоит из К двухвходовых элементов И, и К двухвходовых элементов ИЛИ 46-1, …, 46-К, при этом информационные входы триггеров запоминания 42-1, …, 42-к/2 и их тактовые входы соединены соответственно с информационными входами Ик-(-к/2-1), …, Ик и тактовым входом Т блока N-байтного ПИС 5-М, информационные входы коммутатора 44 соединены соответственно с информационными входами И1, …, Ик блока N-байтного ПИС 5-М, информационные входы И1, …, Ик-к/2, которого соединены соответственно с входами коммутатора 45, выходы триггеров запоминания 42-1, …, 42-к/2, соединены с соответствующими входами коммутатора 45, вход управления An блока N-байтного ПИС 5-М соединен с входом инвертора 43 и входом управления коммутатора 45, выход инвертора 43 соединен с входом управления коммутатора 44, выходы коммутаторов 44, 45 соединены с соответствующими входами двухвходовых элементов ИЛИ 41-1, …, 41-К, выходы которых являются информационными выходами И1, …, Ик блока N-байтного ПИС 5-М.

Устройство управления блоками восьмибитного перестроения и байтных перестроений информационных сигналов (устройство У) 6 (фиг. 10) содержит триггеры 47, 48, инвертор 49, двухвходовые элементы И50, 51, счетчик 52 и дешифратор 53, при этом Д-вход триггера 47 соединен с шиной "Лог. 1", вход К триггера 47 соединен с входом КСК устройства У 6, выход триггера 47 соединен с Д-входом триггера 48 и входом инвертора 49, выход которого соединен с входом R триггера 48, выход триггера 48 соединен с первым входом элемента И50, второй вход которого, а также вход К триггера 48 соединен с тактовым входом Т устройства У 6, выход элемента И50 соединен с выходом R триггера 47 и первым входом элемента И51, второй вход которого подключен К входу ПФ устройства У 6, выход элемента И51 соединен с тактовым входом счетчика 52, выходы разрядов А0, А1, А2 которого соединены с соответствующими входами дешифратора 53, а выходы разрядов А3, …, А11 счетчика 52 и выходы дешифратора 53 являются выходами устройства У6.

Устройство для цикловой синхронизации (устройство для ЦС) (фиг. 1) работает следующим образом.

Тактовый сигнал Т с входа устройства для ЦС поступает на соответствующие входы блока байтных ПИС 5, блока восьмибитного ПИС 4, блока дешифрации синхрокомбинации 1, счетчика длины цикла 2 и устройства У6.

Информационные сигналы с выходов И1, …, Ик устройства для ЦС поступают на соответствующие входы блока байтных ПИС 5, который осуществляет от одного до N-байтного перестроения информационных сигналов по сигналам управления А3, …, An, поступающим с соответствующих выходов устройства У6.

Работа блока байтных ПИС 5 и устройства У 6 будет приведена далее.

С информационных выходов И1, …, Ик блока байтных ПИС 5 сигналы поступают на соответствующие входы блока восьмибитного ПИС 4, который осуществляет битовое перестроение информационных сигналов, по сигналам управления 1, …, 8, поступающим с соответствующих выходов устройства У6.

Работа блока восьмибитного ПИС 4 будет приведена далее.

С соответствующих информационных выходах И1, …, Ик блока восьмибитного ПИС 4 сигналы поступают на входы блока дешифрации синхрокомбинации 1. Блок дешифрации синхрокомбинации 1 осуществляет сравнение информационных сигналов с заданными значениями синхрокомбинации и формирование результата сравнения на его выходе отклика (выход СК). В случае положительного отклика на выходе СК формируется сигнал Лог. "1", а в случае отрицательного отклика - сигнал Лог. "0". Сигнал с выхода СК блока дешифрации синхрокомбинации 1 поступает на соответствующие входы счетчика длины цикла 2 и блока фазирования 3.

Счетчик длины цикла 2 осуществляет подсчет длины цикла и формирование на его выходах сигнала конца цикла (выход КЦ) и сигнала конца синхрокомбинации (выход КСК). Длина цикла определяется как наименьшее общее кратное между длиной цикла передачи (в битах) и количеством информационных сигналов К на один тактовый сигнал.

Счетчик длины цикла работает следующим образом.

Пока блок фазирования 3 находится в режиме отсутствия фазирования на его выходе поиска фазы (выход ПФ) формируется сигнал Лог. "1". Этот сигнал, поступая на соответствующий вход счетчика длины цикла 2, разрешает его установку в состояние, соответствующее положению конца синхрокомбинации в цикле передачи при положительном отклике на выходе СК блока дешифрации синхрокомбинации 1.

Блок фазирования 3 работает следующим образом.

До поступления первого положительного отклика с выхода СК блока дешифрации синхрокомбинации 1 на соответствующий вход блока фазирования 3, последний находится в режиме отсутствия фазирования. При этом на его выходе ПФ формируется сигнал Лог. "1", а на выходе наличия фазы (выход Ф) - сигнал Лог. "0". При поступлении на вход СК блока фазирования 3 первого положительного отклика реверсивный счетчик этого блока устанавливается в режим положительного счета и увеличивает свое состояние на единицу. При этом сигналом Лог. "0", сформированном на выходе ПФ блока фазирования 3, при следующих положительных откликах запрещается установка счетчика длины цикла 2 в состояние, соответствующее положению конца синхрокомбинации в цикле передачи. Теперь, при наличии положительного отклика на СК входе блока фазирования и сигнала конца синхрокомбинации на его входе СКС, реверсивный счетчик последнего увеличивает свое состояние на единицу, а при отсутствии положительного отклика - уменьшает на единицу. Когда разность количества сигналов положительного и отрицательного откликов достигает заданного значения в блоке фазирования 3, устройство для ЦС переходит в режим синхронизма, о чем свидетельствует сигнал Лог. "1" на выходе наличия фазы (выход Ф) блока фазирования 3. В этом режиме устройство для ЦС находится до тех пор, пока разность количества сигналов отрицательного и положительного откликов не достигнет заданного в блоке фазирования 3 значения. При этом реверсивный счетчик блока фазирования 3 устанавливается в нулевое состояние и устройство для ЦС переходит в режим поиска синхронизма, как было описано ранее.

В начале работы устройства для ЦС, а также при сбоях в системе энергопитания или в аппаратуре на передающем конце линии связи, фаза работы устройства для ЦС не соответствует фазе сигнала передачи.

В режиме синхронизма с помощью блоков восьмибитного 4 и байтного 5 ПИС, управляемых сигналами устройства У6, информационные сигналы перестроены и поступают на выход устройства для ЦС в порядке, когда первый бит передачи расположен на первом информационном выходе.

Блок восьмибитного перестроения информационных сигналов (блок восьмибитного ПИС) 4 (фиг. 2) работает следующим образом.

При наличии сигнала на входе 1 разрешается работа коммутатора 8, и текущие сигналы с входов И1, …, Ик восьмибитного ПИС 4 через этот коммутатор поступают на соответствующие входы восьмивходовых элементов ИЛИ 16-1, …, 16К. При наличии сигнала на входе 2 разрешается работа коммутатора 9, и задержанный на один такт сигнал с выхода Ик блока восьмибитного ПИС 4 через триггер задержки 7-7 поступает на первый вход коммутатора 9, а текущие значения сигналов с входов И1, …, Ик-1 - на входы 1, …, К-1 коммутатора 9. С выходов 1, …, К коммутатора 9 сигналы поступают на соответствующие входы восьмивходовых элементов ИЛИ 16-1, …, 16-К. При наличии сигнала на входе 3 разрешается работа коммутатора 10, и задержанные на один такт сигналы с выходов Ик-1 …, Ик блока восьмибитного ПИС 4 через триггеры задержки 7-6, 7-7 соответственно поступают на первый и второй входы коммутатора 10, а текущие значения сигналов с входов И1, …, Ик-2 - на входы 1, …, К-2 коммутатора 10. С выходов 1, …, К коммутатора 10 сигналы поступают на соответствующие входы восьмивходовых элементов ИЛИ 16-1, …, 16-К. При наличии сигнала на входе 4 разрешается работа коммутатора 11, и задержанные на один такт сигналы с выходов Ик-2, …, Ик через триггеры задержки 7-5, …, 7-7 соответственно поступают на первый, …, третий входы коммутатора 11, а текущие значения сигналов с входов И1, …, Ик-3 - на входы 1, …, К-3 коммутатора 11. С выходов 1, …, К коммутатора 11 сигналы поступают на соответствующие входы восьмивходовых элементов ИЛИ 16-1, …, 16-К. При наличии сигнала на входе 5 разрешается работа коммутатора 12, и задержанные на один такт сигналы с выходов Ик-3, …, Ик через триггеры задержки 7-4, …, 7-7 соответственно поступают на первый, …, четвертый входы коммутатора 12, а текущие значения сигналов с входов И1, …, Ик-4 - на входы 1, …, К-4 коммутатора 12. С выходов 1, …, К коммутатора 12 сигналы поступают на соответствующие входы восьмивходовых элементов ИЛИ 16-1, …, 16-К. При наличии сигнала на входе 6 разрешается работа коммутатора 13, и задержанные на один такт сигналы с выходов Ик-4, …, Ик через триггеры задержки 7-3, …, 7-7 соответственно поступают на первый, …, пятый входы коммутатора 13, а текущие значения сигналов с входов И1, …, Ик-5 - на входы 1, …, К-5 коммутатора 13. С выходов 1, …, К коммутатора 13 сигналы поступают на соответствующие входы восьмивходовых элементов ИЛИ 16-1, …, 16-К. При наличии сигнала на входе 7 разрешается работа коммутатора 14, и задержанные на один такт сигналы с выходов Ик-5, …, Ик через триггеры задержки 7-2, …, 7-7 соответственно поступают на первый, …, шестой входы коммутатора 14, а текущие значения сигналов с входов И1, …, Ик-6 - на входы 1, …, К-6 коммутатора 14. С выходов 1, …, К коммутатора 14 сигналы поступают на соответствующие входы восьмивходовых элементов ИЛИ 16-1, …, 16-К. При наличии сигнала на входе 8 разрешается работа коммутатора 15, и задержанные на один такт сигналы с выходов Ик-6, …, Ик через триггеры задержки 7-1, …, 7-7 соответственно поступают на первый, …, седьмой входы коммутатора 15, а текущие значения сигналов с входов И1, …, Ик-7 - на входы 1, …, К-6 коммутатора 15. С выходов 1, …, К коммутатора 15 сигналы поступают на соответствующие входы восьмивходовых элементов ИЛИ 16-1, …, 16-К, выходы которых являются информационными выходами блока восьмибитного ПИС 4.

Работа блока байтных перестроений информационных сигналов (блок байтных ПИС) 5 приведена на примере, когда на входах устройства для ЦС одному тактовому сигналу соответствует 256 информационных сигналов (коэффициент распараллеливания равен числу 256).

Блок байтных ПИС 5 (фиг. 3) при коэффициенте распараллеливания, равном числу 256 содержит блок однобайтного ПИС 5-1 (фиг. 4), блок двухбайтного ПИС 5-2 (фиг. 5), блок четырехбайтного ПИС 5-3 (фиг. 6), блок восьмибайтного ПИС 5-4 (фиг. 7) и блок шестнадцатибайтного ПИС 5-5 (фиг. 8). Управление работой блока байтных ПИС 5 осуществляется с помощью сигналов А3, А4, А5, А6, А7, поступающих с выходов устройства У.

Сигналы с информационных входов И1, …, И256 блока байтных ПИС 5 поступают на соответствующие входы шестнадцатибайтного ПИС 5-5, который осуществляет перестроение информационных сигналов группой, состоящей из шестнадцати байт. Сигналы с информационных выходов И1, …, И256 блока шестнадцатибайтного ПИС 5-5 поступают на соответствующие входы восьмибайтного ПИС 5-4, который осуществляет перестроение информационных сигналов группой, состоящей из восьми байт. Сигналы с информационных выходов И1, …, И256 блока восьмибайтного ПИС 5-4 поступают на соответствующие входы блока четырехбайтного ПИС 5-3, который осуществляет перестроение информационных сигналов группой, состоящей из четырех байт. Сигналы с информационных выходов И1, …, И256 блока четырехбайтного ПИС 5-3 поступают на соответствующие входы блока двухбайтного ПИС 5-2, который осуществляет перестроение информационных сигналов группой, состоящей из двух байт. Сигналы с информационных выходов И1, …, И256 блока двухбайтного ПИС 5-2 поступают на соответствующие входы однобайтного ПИС 5-1, который осуществляет перестроение информационных сигналов группой, состоящей из одного байта.

Как известно, один байт содержит восемь информационных бит. Сигналы с информационных выходов И1, …, И256 блока однобайтного ПИС 5-1 блока байтных ПИС 5 поступают на входы восьмибитного ПИС 4, который осуществляет перестроение информационных сигналов, как было описано ранее.

На фиг. 4, 5, 6, 7, 8 в скобках указаны номера входов/выходов блоков байтных перестроений информационных сигналов при коэффициенте распараллеливания, равном числу 256.

Блок однобайтного ПИС 5-1 (фиг. 4) работает следующим образом.

При значении сигнала управления А3, равном Лог. "0", сигналом Лог. "1" с выхода инвертора 18 разрешается работа коммутатора 19, содержащего 256 двухвходовых элементов И, и сигналы с информационных входов И1, …, И256 однобайтного ПИС 5-1 через открытый коммутатор 19 поступают на соответствующие входы двухвходовых элементов ИЛИ 21-1, …, 21-256. При значении сигнала управления А3, равном Лог. "1", разрешается работа коммутатора 20. В этом случае сигналы с информационных входов И249, …, И256, задержанные на один такт триггерами задержки 17-1, …., 17-8, поступают на 1, …, 8 входы коммутатора 20, текущие значения с информационных входов И1, …, И248 поступают на 9, …, 256 входы коммутатора 20. С выходов коммутатора 20 сигналы поступают на соответствующие входы двухвходовых элементов ИЛИ 21-1, …, 21-256, выходы которых являются информационными выходами И1, …, И256 блока однобайтного ПИС 5-1.

Блок двухбайтного ПИС 5-2 (фиг. 5) работает следующим образом.

При значении сигнала управления А4, равном Лог. "0", сигналом Лог. "1" с выхода инвертора 23 разрешается работа коммутатора 24, и сигналы с информационных входов И1, …, И256 двухбайтного ПИС 5-2 через открытый коммутатор 24 поступают на соответствующие входы двухвходовых элементов ИЛИ 26-1, …, 26-256. При значении сигнала управления А4, равном Лог. "1", разрешается работа коммутатора 25. В этом случае сигналы с информационных входов И241, …, И256, задержанные на один такт триггерами задержки 22-1, …., 22-16, поступают на 1, …, 16 входы коммутатора 25, а текущие значения с информационных входов И1, …, И240 поступают на 17, …, 256 входы коммутатора 25. С выходов коммутатора 25 сигналы поступают на соответствующие входы двухвходовых элементов ИЛИ 26-1, …, 26-256, выходы которых являются информационными выходами И1, …, H256 блока двухбайтного ПИС 5-2.

Блок четырехбайтного ПИС 5-3 (фиг. 6) работает следующим образом.

При значении сигнала управления А5, равном Лог. "0", сигналом Лог. "1" с выхода инвертора 28 разрешается работа коммутатора 29, и сигналы с информационных входов И1, …, И256 четырехбайтного ПИС 5-3 через открытый коммутатор 29 поступают на соответствующие входы двухвходовых элементов ИЛИ 31-1, …, 31-256. При значении сигнала управления А5, равном Лог. "1", разрешается работа коммутатора 30. В этом случае сигналы с информационных входов И225, …, И256, задержанные на один такт триггерами задержки 27-1, ….,27-32, поступают на 1, …, 32 входы коммутатора 30, а текущие значения с информационных входов И1, …, И224 поступают на 33, …, 256 входы коммутатора 30. С выходов коммутатора 30 сигналы поступают на соответствующие входы двухвходовых элементов ИЛИ 31-1, …, 31-256, выходы которых являются информационными выходами И1, …, И256 блока четырехбайтного ПИС 5-3.

Блок восьмибайтного ПИС 5-4 (фиг. 7) работает следующим образом.

При значении сигнала управления А6, равном Лог. "0", сигналом Лог. "1" с выхода инвертора 33 разрешается работа коммутатора 34, и сигналы с информационных входов И1, …, И256 восьмибайтного ПИС 5-4, через открытый коммутатор 34 поступают на соответствующие входы двухвходовых элементов ИЛИ 36-1, …, 36-256. При значении сигнала управления А6, равном Лог. "1", разрешается работа коммутатора 35. В этом случае сигналы с информационных входов И193, …, И256, задержанные на один такт триггерами задержки 32-1, …, 32-64, поступают на 1, …, 64 входы коммутатора 35, а текущие значения с информационных входов И1, …, И192 поступают на 65, …, 256 входы коммутатора 35. С выходов коммутатора 35 сигналы поступают на соответствующие входы двухвходовых элементов ИЛИ 36-1, …, 36-256, выходы которых являются информационными выходами И1, …, И256 блока восьмибайтного ПИС 5-4.

Блок шестнадцатибайтного ПИС 5-5 (фиг. 8) работает следующим образом.

При значении сигнала управления А7, равном Лог. "0", сигналом Лог. "1" с выхода инвертора 38 разрешается работа коммутатора 39, и сигналы с информационных входов И1, …, И256 шестнадцатибайтного ПИС 5-5 через открытый коммутатор 39 поступают на соответствующие входы двухвходовых элементов ИЛИ 41-1, …, 41-256. При значении сигнала управления А7, равном Лог. "1", разрешается работа коммутатора 40. В этом случае сигналы с информационных входов И129, …, И256, задержанные на один такт триггерами задержки 37-1, …, 37-128, поступают на 1, …, 128 входы коммутатора 40, а текущие значения с информационных входов И1, …, H128 поступают на 129, …, 256 входы коммутатора 40. С выходов коммутатора 40 сигналы поступают на соответствующие входы двухвходовых элементов ИЛИ 41-1, …, 41-256, выходы которых являются информационными выходами И1, …, И256 блока шестнадцатибайтного ПИС 5-5.

В общем случае максимальное значение байтности блока ПИС определяется соотношением

N=K/16,

где

N - максимальное значение байтности;

К - коэффициент распараллеливания информационных сигналов.

Байтность следующих блоков ПИС, в порядке ее уменьшения, определяется результатом деления на 2 числового значения байтности предыдущего блока ПИС, имеющего большую байтность перестроения информационных сигналов.

Блок N-байтного ПИС (фиг. 9) работает следующим образом.

При значении сигнала управления An, равном Лог. "0", сигналом Лог. "1" с выхода инвертора 43 разрешается работа коммутатора 44, и сигналы с информационных входов И1, …, Ик N-байтного ПИС через открытый коммутатор 44 поступают на соответствующие входы двухвходовых элементов ИЛИ 46-1, …, 46-К. При значении сигнала управления An, равном Лог. "1", разрешается работа коммутатора 45. В этом случае сигналы с входов И1, …, Ик-(к/2-1), задержанные на один такт триггерами задержки 42-1, …, 42-К/2 поступают на 1, …, К/2 входы коммутатора 45, а текущие значения с информационных входов 1, …, К-К/2 поступают на К/2+1, …, К входы коммутатора 45. С выходов коммутатора 45 сигналы поступают на соответствующие входы двухвходовых элементов ИЛИ 46-1, …, 41К, выходы которых являются информационными выходами И1, …, Ик блока N-байтного ПИС.

Таким образом, с помощью блока восьмибитного ПИС 4 и блока байтных ПИС 5 приводится в соответствие фаза работы устройства для ЦС с фазой передачи.

Устройство управления блоками восьмибитного перестроения и байтных перестроений информационных сигналов (устройство У) 6 (фиг. 10) работает следующим образом.

Задним фронтом сигнала конца синхрокомбинации (сигнал КСК) триггер 47 устанавливается в единичное состояние. Сигнал с выхода триггера 47 поступает на вход D триггера 48, работа которого разрешается сигналом Лог. "1", поступающим с выхода инвертора 49 на вход R триггера 48. Далее по переднему фронту тактового сигнала Т, триггер 48 устанавливается в единичное состояние, разрешая по первому входу работу двухвходового элемента И50. На второй вход элемента И50 поступает инверсный тактовый сигнал Т. Сигналом с выхода элемента И50 триггер 47 устанавливается в нулевое состояние. Сигналом с выхода триггера 47, через инвертор 49 триггер 48 также устанавливается в нулевое состояние, запрещая работу элемента И50. Тактовый сигнал с выхода открытого элемента И50 поступает на первый вход элемента И51. На второй вход элемента И51 поступает сигнал ПФ. Как было описано ранее, пока не появится сигнал положительного отклика с выхода СК блока дешифрации синхрокомбинации 1, сигнал ПФ, поступающий с соответствующего выхода блока фазирования 3 на вход устройства У6, имеет значение Лог. "1". При этом разрешается работа элемента И51, и один тактовый сигнал за цикл передачи поступает на вход Т счетчика 52 устройства У6. Сигналы с выходов разрядов А0, А1, А2 счетчика 52 поступают на входы дешифратора 53. Сигналы с выходов дешифратора 53 поступают на входы управления блока восьмибитного ПИС 4. Сигналы с выходов разрядов А3, …, An счетчика 52 поступают на входы управления блока байтных ПИС 5.

Для технической реализации устройства для цикловой синхронизации использована программируемая пользователем логическая интегральная схема (ППЛИС) импортного производства типа Virtex XC6VSX315t-1FF1156 фирмы Xilinx.

Предлагаемое изобретение позволяет значительно сократить количество функциональных узлов устройства для цикловой синхронизации.

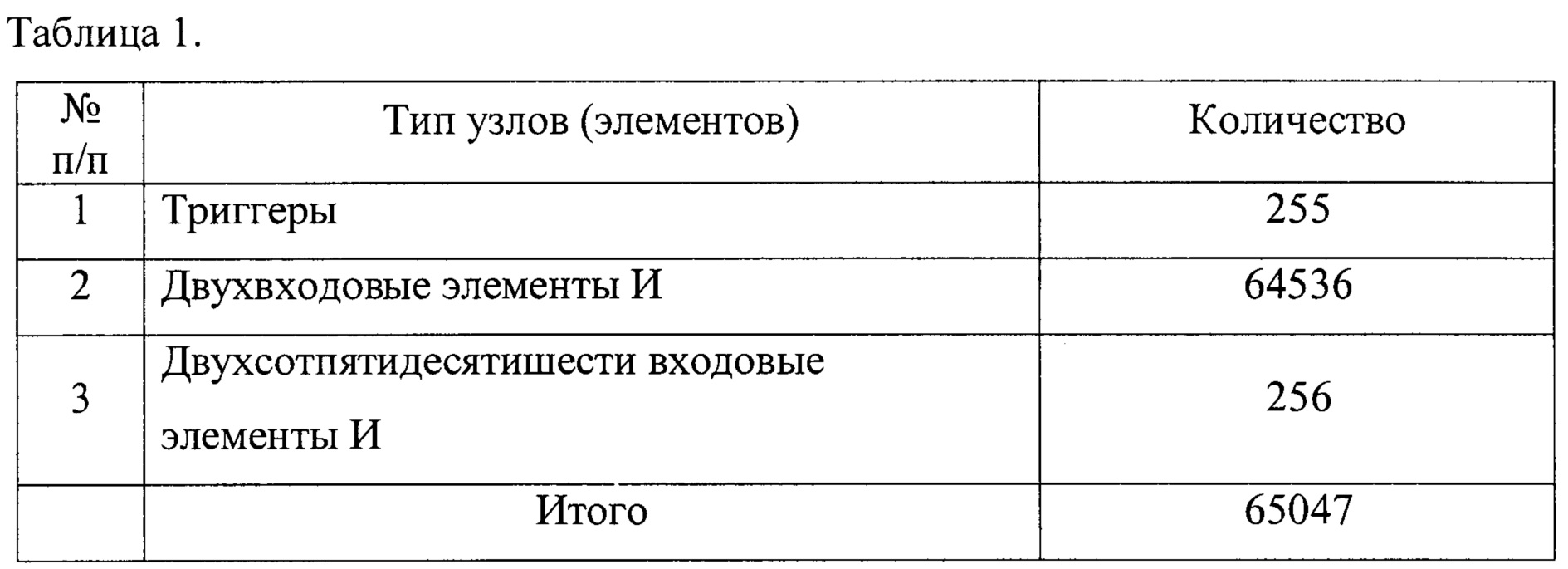

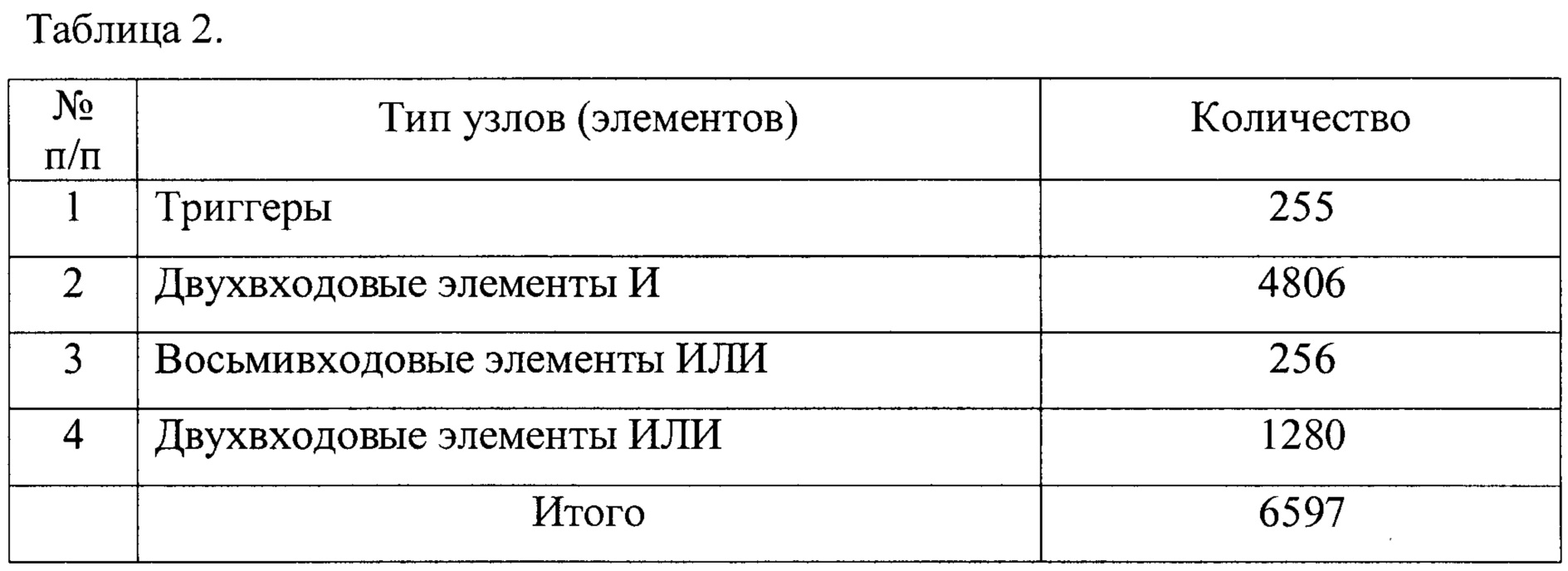

Ниже в таблице 1 и таблице 2 приводятся сравнительные данные по требуемому количеству функциональных узлов для создания прототипа и предлагаемого устройства для цикловой синхронизации при коэффициенте распараллеливания равном 256, для передачи, передаваемой в транспортном блоке OTU3 оптической иерархии с битовой скоростью, равной ≈44 ГГбит/с. Основное количество функциональных узлов (более 95%) требуется для создания блоков перестроения.

В таблице 1 приведены данные по требуемому количеству функциональных узлов для создания блока битного перестроения информационных сигналов прототипа устройства для цикловой синхронизации.

В таблице 2 приведены данные по требуемому количеству функциональных узлов для создания блоков битного и байтных перестроений информационных сигналов предлагаемого устройства для цикловой синхронизации.

Как видно из таблиц для создания предлагаемого устройства для цикловой синхронизации при коэффициенте распараллеливания, равном 265, требуется функциональных узлов в девять с лишним раз меньше, чем при создании прототипа.

Устройство для цикловой синхронизации, содержащее блок дешифрации синхрокомбинации, счетчик длины цикла, блок фазирования, блок восьмибитного перестроения информационных сигналов, причем информационные выходы блока восьмибитного перестроения информационных сигналов соединены с соответствующими входами блока дешифрации синхрокомбинации и являются информационными выходами устройства для цикловой синхронизации, выход блока дешифрации синхрокомбинации соединен с соответствующими входами счетчика длины цикла и блока фазирования, выход наличия фазы которого является соответствующим выходом устройства для цикловой синхронизации, а выход поиска фазы соединен с соответствующим входом счетчика длины цикла, выход конца цикла которого является соответствующим выходом устройства для цикловой синхронизации, а выход конца синхрокомбинации соединен с соответствующим входом блока фазирования, тактовый вход устройства для цикловой синхронизации соединен с соответствующими входами блока дешифрации синхрокомбинации, счетчика длины цикла и блока восьмибитного перестроения информационных сигналов, отличающееся тем, что введены блок байтных перестроений информационных сигналов, содержащий от однобайтного до N-байтного блоков перестроения информационных сигналов, и устройство управления блоками восьмибитного и байтных перестроений информационных сигналов, при этом информационные и тактовый входы устройства для цикловой синхронизации соединены с соответствующими входами блока байтных перестроений информационных сигналов, входы блока байтных перестроений информационных сигналов являются входами блока N-байтного перестроения информационных сигналов, выходы каждого блока перестроения информационных сигналов, имеющего большее числовое значение байтности перестроения, соединены с входами блока перестроения информационных сигналов, имеющего меньшее числовое значение байтности перестроения, выходы блока байтных перестроений информационных сигналов соединены с соответствующими входами блока восьмибитного перестроения информационных сигналов, входы конца синхрокомбинации и поиска фазы устройства управления блоками восьмибитного перестроения и байтных перестроений информационных сигналов соединены соответственно с соответствующими выходами счетчика длины цикла и блока фазирования, тактовый вход устройства управления блоками восьмибитного перестроения и байтных перестроений информационных сигналов соединены с тактовым входом устройства для цикловой синхронизации, выходы 1, …, 8 и A, …, A устройства управления блоками восьмибитного перестроения и байтных перестроений информационных сигналов соединены с соответствующими входами блока восьмибитного перестроения и блока байтных перестроений информационных сигналов.