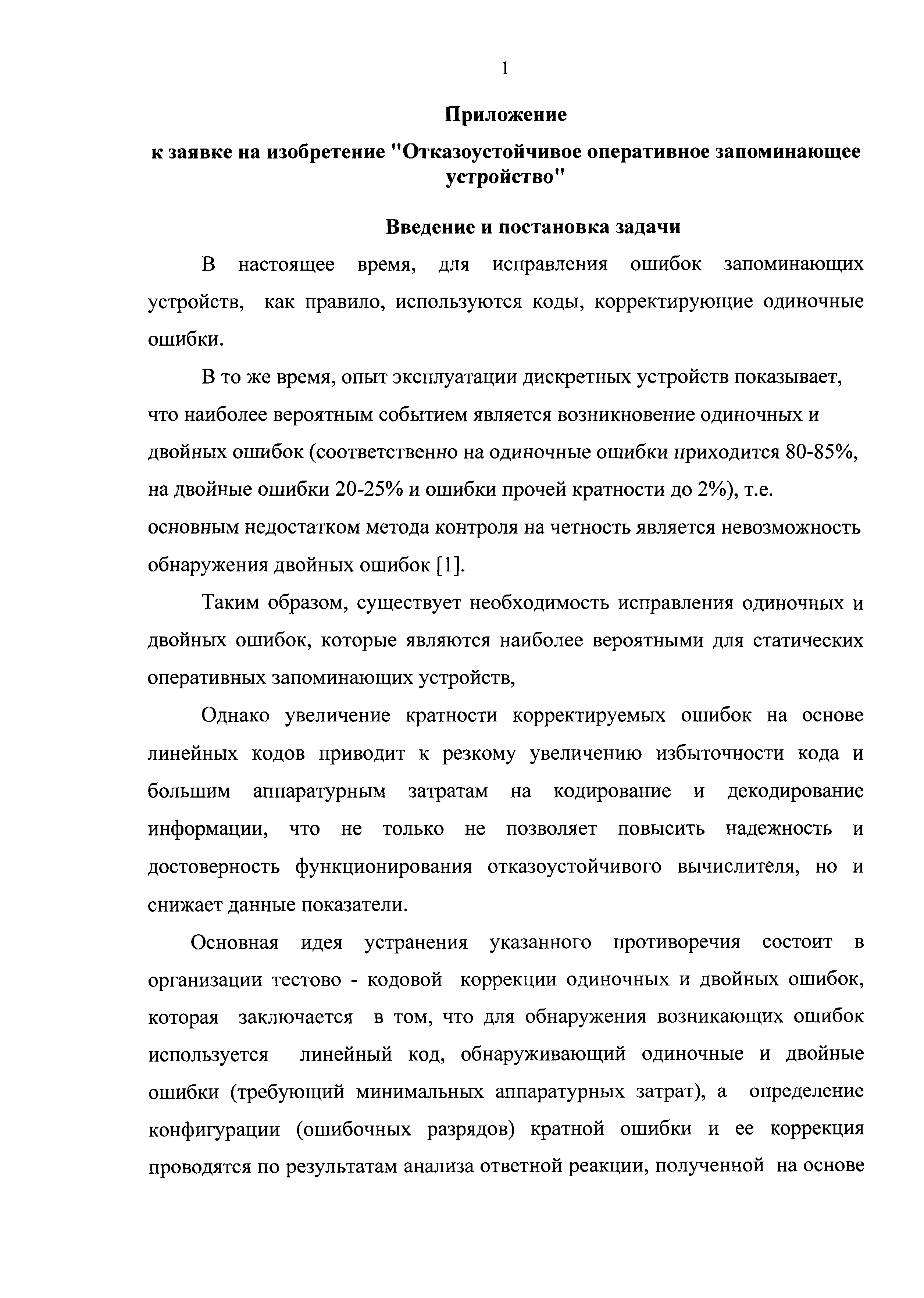

Результат интеллектуальной деятельности: ОТКАЗОУСТОЙЧИВОЕ ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Вид РИД

Изобретение

Изобретение относится к вычислительной технике и может быть использовано для обеспечения отказоустойчивости оперативных запоминающих устройств.

Известно устройство хранения информации [1], содержащее узел памяти, входной блок кодирования, формирующий значения контрольных разрядов r1 и r2 путем сложения по модулю 2 информационных символов x1, x2, x3, y1, y2, y3, поступающих на входы входного блока кодирования, в соответствии с правилом: r1=х1⊕х2⊕y1⊕y2; r2=х2⊕х3⊕y2⊕y3, выходной блок кодирования, формирующий значения проверочных контрольных разрядов r1П, r2П путем сложения по модулю 2 информационных символов x1C, x2C, x3C, y1C, y2C, y3C, поступающих на входы выходного блока кодирования и полученных при считывании информации с информационных выходов узла памяти в соответствии с правилом: r1П=х1С⊕х2С⊕y1C⊕y2C; r2П=х2С⊕х3С⊕y2C⊕y3C, блок выявления ошибки, первый блок элементов И, элемент И, первый блок элементов ИЛИ, вход установки устройства в нулевое состояние, вход записи, вход считывания, адресные входы, информационные входы, вход синхронизации, информационные выходы, выход сигнала при возникновении ошибки, отличающиеся тем, что дополнительно содержит второй блок элементов ИЛИ, второй блок элементов, третий блок элементов И, причем вход установки в нулевое состояние, вход записи, вход считывания, адресные входы, подключены соответственно к первому, второму, третьему и четвертому входам узла памяти, информационные входы подключены к пятым входам узла памяти и к первым входам второго блока элементов ИЛИ, вторые входы которого подключены к выходам второго блока элементов И, а выходы подключены к входам блока кодирования, выходы которого подключены к шестым входам узла памяти и к первым входам блока выявления ошибки, вход синхронизации подключен к седьмому входу узла памяти и к первым входам первого блока элементов И и к первому входу элемента И, первые выходы узла памяти подключены к вторым входам первого блока элементов И и к первым входам второго блока элементов И, второй вход которого подключен к входу считывания, вторые выходы узла памяти подключены к вторым входам блока выявления ошибки, выходы которого подключены к входам первого блока элементов ИЛИ, выход которого подключен к второму входу элемента И, выходы первого блока элементов И являются информационными выходами устройства, выход элемента И является выходом сигнала при возникновении ошибки.

Недостатком устройства является низкая отказоустойчивость, так как ошибки только обнаруживаются, но не корректируются.

Наиболее близким по техническому решению является отказоустойчивое оперативное запоминающее устройство [2], содержащее исходный вычислительный канал, избыточный вычислительный канал, первое кодирующее устройство, блок вычисления синдрома, первый дешифратор, адресные входы устройства, информационные входы устройства, вход записи, вход считывания, корректор, выходы которого являются информационными выходами устройства, отличающееся тем, что дополнительно содержит второе кодирующее устройство, с первого по десятый элементы ИЛИ, с первого по четвертый элементы задержки, элемент И, блок элементов И, RS-триггер, регистр, с первого по четвертый блоки элементов неравнозначности, второй дешифратор, элемент НЕ, блок хранения поправок, блок вычисления признака поправки, вход сброс, причем адресные входы подключены к первым входам исходного вычислительного канала, информационные входы через первый и второй элементы ИЛИ подключены ко вторым входам исходного вычислительного канала и к первым входам первого кодирующего устройства, подключенного своими выходами через третий и четвертый элементы ИЛИ к первым входам избыточного вычислительного канала, вход сброс через пятый элемент ИЛИ подключен к нулевым входам регистра и RS-триггера, вход считывание подключен к входу запись регистра, через седьмой элемент ИЛИ - к третьему входу исходного вычислительного канала, к второму входу избыточного вычислительного канала и через первый элемент задержки - к единичному входу RS-триггера, вход запись через шестой элемент ИЛИ подключен к четвертому входу исходного вычислительного канала, третьему входу избыточного вычислительного канала, выходы исходного вычислительного канала подключены ко вторым входам регистра, к первым входам блока вычисления синдрома и к первым входам первого блока элементов неравнозначности, выходы избыточного вычислительного канала подключены к вторым входам блока вычисления синдрома, к третьим входам регистра и к первым входам второго блока элементов неравнозначности, выходы блока вычисления синдрома подключены к четвертым входам регистра, единичный выход RS-триггера подключен к входу считывание регистра, через второй элемент задержки - к первому входу корректора, через третий элемент задержки - к второму входу пятого элемента ИЛИ, через четвертый элемент задержки к второму входу седьмого элемента ИЛИ, первая группа выходов регистра подключена к вторым входам с первого по четвертый элементов ИЛИ, вторая группа выходов регистра подключена к вторым входам первого блока элементов неравнозначности и к вторым входам корректора, третья и четвертая группы выходов регистра подключены соответственно к вторым входам второго блока элементов неравнозначности и к первым входам третьего блока элементов неравнозначности, выход первого блока элементов неравнозначности - к входам второго кодирующего устройства, к входам элемента И, к входам девятого элемента ИЛИ, к первым входам четвертого блока элементов неравнозначности и к первым входам блока вычисления признака поправки, выходы второго блока элементов неравнозначности подключены к входам восьмого элемента ИЛИ, выходы восьмого элемента ИЛИ, девятого элемента ИЛИ и элемента И подключены к входам первого дешифратора, первый выход которого через элемент НЕ подключен к первому входу блока элементов И, а вторая группа выходов подключена к входам десятого элемента ИЛИ, выходы третьего блока элементов неравнозначности подключены к входам второго дешифратора, подключенного своими выходами ко входам блока хранения поправок, выходы которого подключены ко вторым входам блока вычисления признака поправки, соединенного своими выходами со вторыми входами четвертого блока элементов неравнозначности, выходы четвертого блока элементов неравнозначности через блок элементов И подключены к третьим входам корректора, выходы которого являются информационными выходами устройства, выход десятого элемента ИЛИ является выходом формирования сигнала ″Отказ устройства″.

Недостатком устройства является большая информационная и аппаратурная избыточность.

Целью изобретения является сокращение информационной и аппаратурной избыточности за счет использования линейного кода, обнаруживающего ошибки и требующего минимального числа контрольных разрядов.

Поставленная цель достигается тем, что устройство, содержащее исходный вычислительный канал, избыточный вычислительный канал, первый дешифратор, корректор, с первого по седьмой блоки элементов ИЛИ, с первого по третий элементы ИЛИ, с первого по четвертый элементы задержки, первый и второй блоки элементов И, RS-триггер, регистр, с первого по четвертый блоки элементов неравнозначности, второй дешифратор, элемент НЕ, блок хранения поправок, блок вычисления признака поправки, дополнительно содержит восьмой блок элементов ИЛИ, третий блок элементов И, первое кодирующее устройство, формирующее значения контрольных разрядов r1 и r2 путем сложения по модулю 2 информационных символов x1, x2, x3, y1, y2, y3, поступающих на входы первого блока кодирования, в соответствии с правилом: r1=х1⊕х2⊕y1⊕y2; r2=х2⊕х3⊕y2⊕y3, блок вычисления синдрома, формирующий значения проверочных контрольных разрядов r1П, r2П путем сложения по модулю 2 информационных символов x1С, х2С, х3С, y1C, y2C, y3C, поступающих на его входы при считывании информации с информационных выходов исходного вычислительного канала в соответствии с правилом: r1П=х1С⊕х2С⊕y1C⊕y2C; r2П=х2С⊕x3C⊕y2C⊕y3C и поразрядного сложения по модулю 2 контрольных разрядов r1⊕r1П; r2⊕r2П, второе кодирующее устройство, формирующее значения контрольных разрядов rb1 и rb2 путем сложения по модулю 2 информационных символов тестового вектора ошибки bi1, bi2, bi2 (i - номер блока информационных разрядов тестового вектора ошибок, характеризующий наличие ошибки), поступающих на его входы в соответствии с правилом: rb1=bi1⊕bi2; rb2=bi2⊕bia, причем адресные входы подключены к первым входам исходного вычислительного канала, информационные входы через первый и второй блоки элементов ИЛИ подключены ко вторым входам исходного вычислительного канала и к первым входам первого кодирующего устройства, подключенного своими выходами через третий и четвертый блоки элементов ИЛИ к первым входам избыточного вычислительного канала, вход сброс через третий элемент ИЛИ подключен к нулевым входам регистра и RS-триггера, вход считывание подключен к входу запись регистра, через второй элемент ИЛИ к третьему входу исходного вычислительного канала, к второму входу избыточного вычислительного канала и через первый элемент задержки к единичному входу RS-триггера, вход запись через первый элемент ИЛИ подключен к четвертому входу исходного вычислительного канала, третьему входу избыточного вычислительного канала, выходы исходного вычислительного канала подключены ко вторым входам регистра, к первым входам блока вычисления синдрома и к первым входам первого блока элементов неравнозначности, выходы избыточного вычислительного канала подключены к вторым входам блока вычисления синдрома, к третьим входам регистра и к первым входам второго блока элементов неравнозначности, выходы блока вычисления синдрома подключены к четвертым входам регистра, единичный выход RS-триггера подключен к входу считывание регистра, к второму входу первого элемента ИЛИ, через второй элемент задержки к первому входу корректора, через третий элемент задержки к второму входу третьего элемента ИЛИ, через четвертый элемент задержки к второму входу второго элемента ИЛИ, первая группа выходов регистра подключена к вторым входам с первого по четвертый блоков элементов ИЛИ, вторая группа выходов регистра подключена к вторым входам первого блока элементов неравнозначности и к вторым входам корректора, третья и четвертая группы выходов регистра подключены соответственно к вторым входам второго блока элементов неравнозначности и к первым входам третьего блока элементов неравнозначности, выход первого блока элементов неравнозначности подключен к входам шестого блока элементов ИЛИ, к входам седьмого блока элементов ИЛИ, к первым входам четвертого блока элементов неравнозначности, выходы второго блока элементов неравнозначности подключены к входам пятого блока элементов ИЛИ, выходы шестого блока элементов ИЛИ подключены к входам второго кодирующего устройства, к входам первого блока элементов И и к первым входам блока вычисления признака поправки, выходы второго кодирующего устройства подключены к вторым входам третьего блока элементов неравнозначности, выход пятого блока элементов ИЛИ и выходы седьмого блока элементов ИЛИ подключены к входам первого дешифратора, первый выход которого через элемент НЕ подключен к первому входу второго блока элементов И, а вторая группа выходов подключена к входам третьего блока элементов И, третья группа выходов первого дешифратора подключена к первым входам восьмого блока элементов ИЛИ, второй вход которого подключен к выходу первого блока элементов И, выходы третьего блока элементов неравнозначности подключены к входам второго дешифратора, подключенного своими выходами ко входам блока хранения поправок, выходы которого подключены ко вторым входам блока вычисления признака поправки, соединенного своими выходами со вторыми входами третьего блока элементов И, выходы которого подключены к вторым входам четвертого блока элементов неравнозначности, выходы четвертого блока элементов неравнозначности через второй блок элементов И подключены к третьим входам корректора, выходы которого являются информационными выходами устройства, выход восьмого блока элементов ИЛИ является выходом формирования сигнала ″Отказ устройства″.

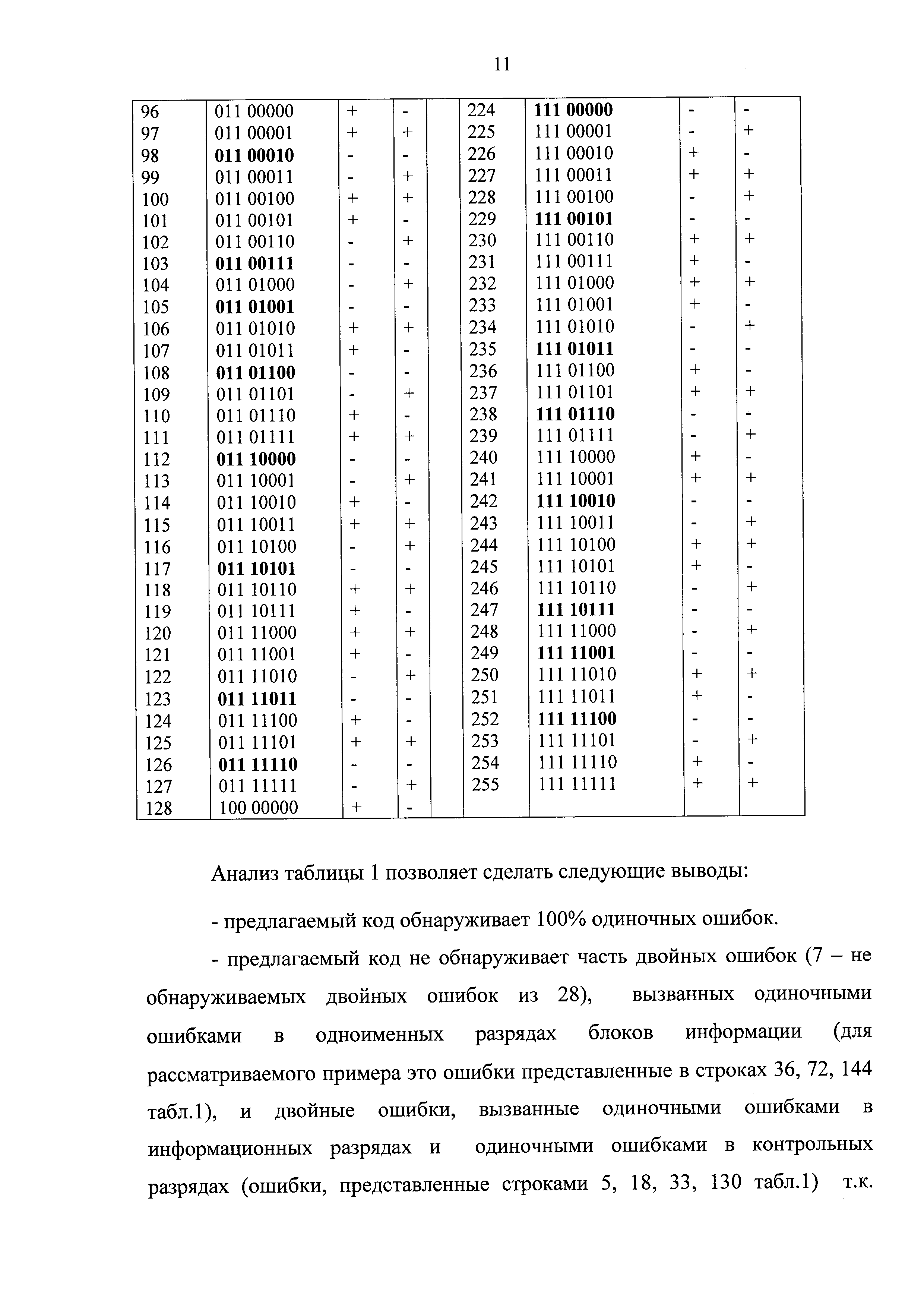

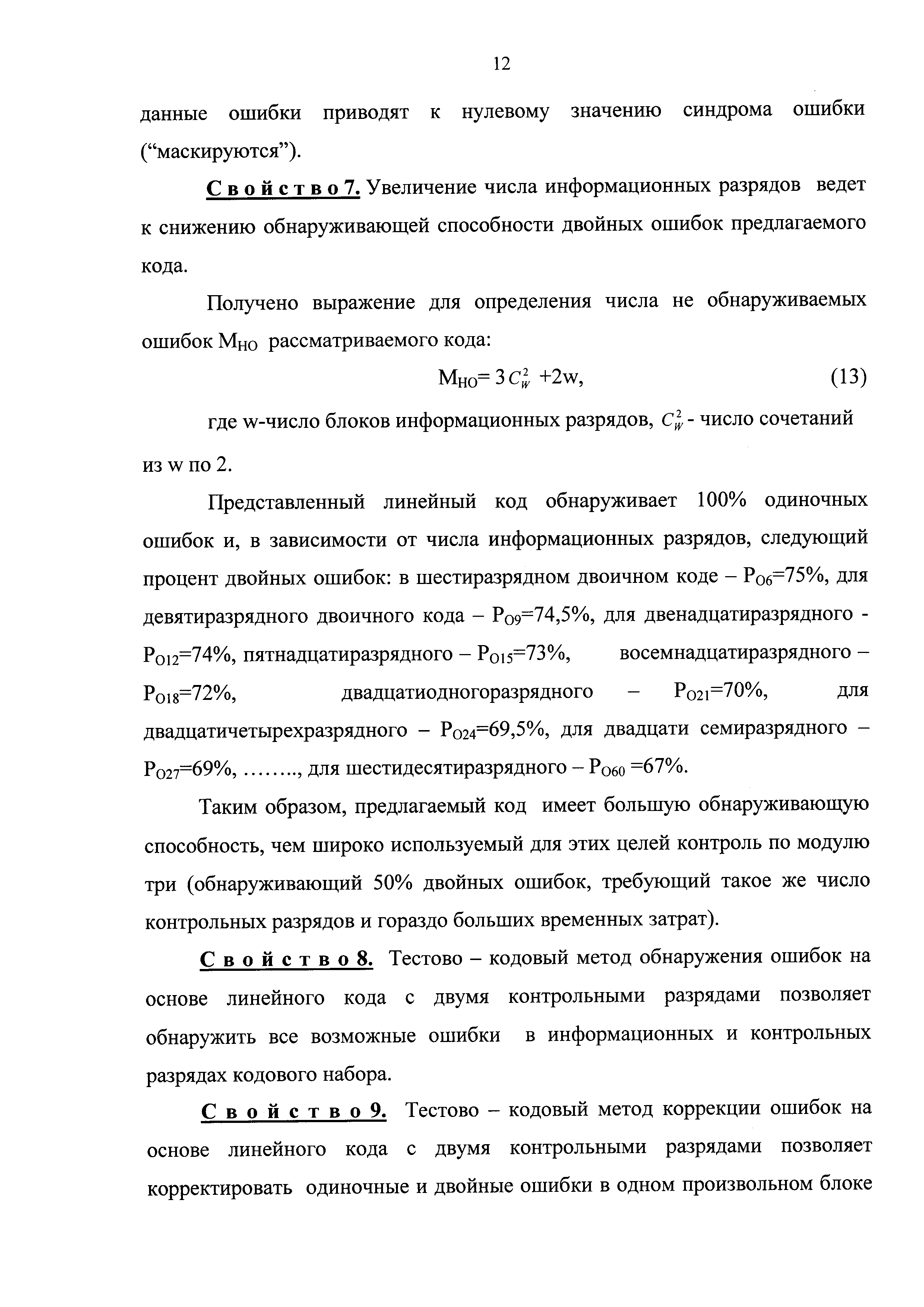

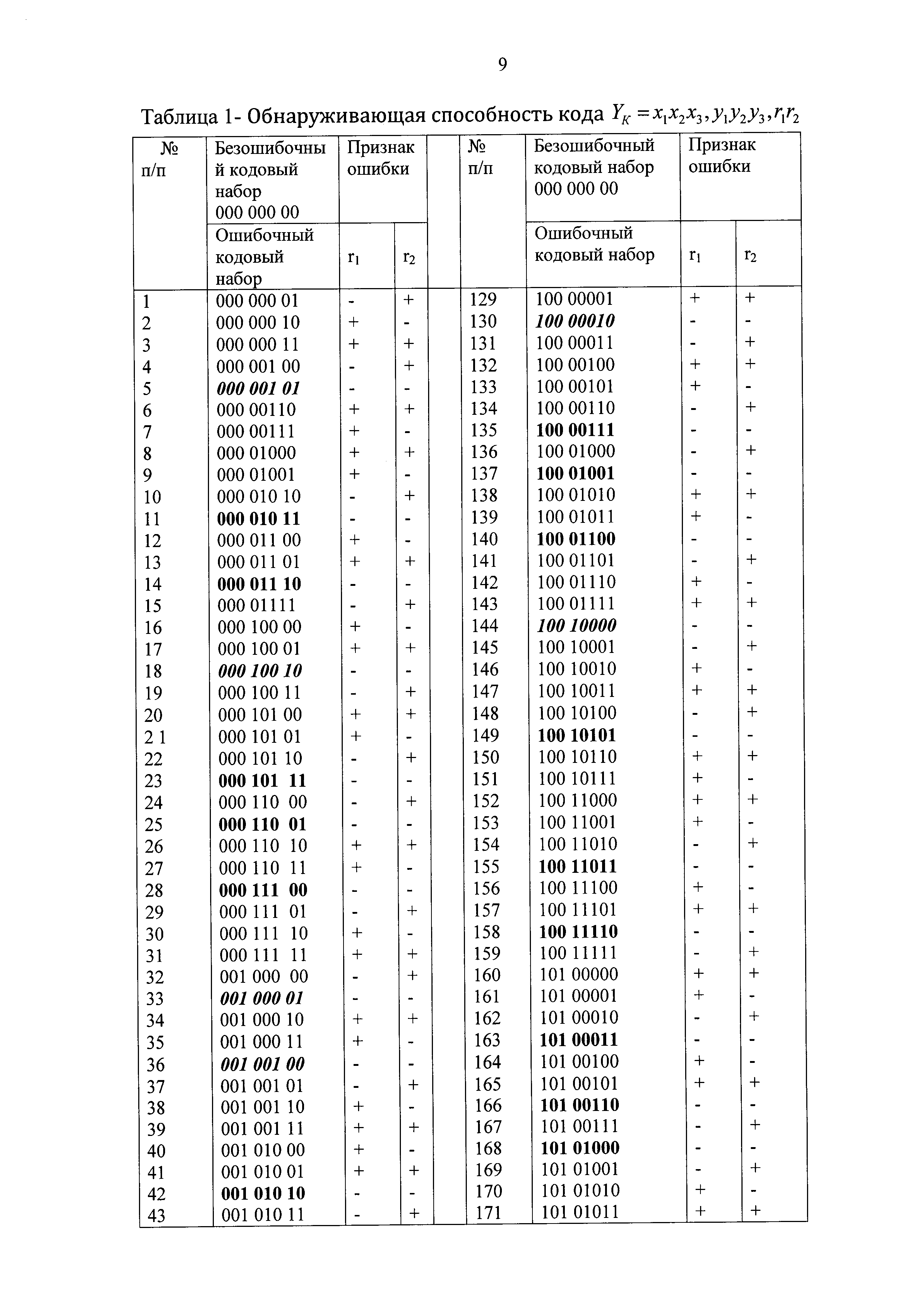

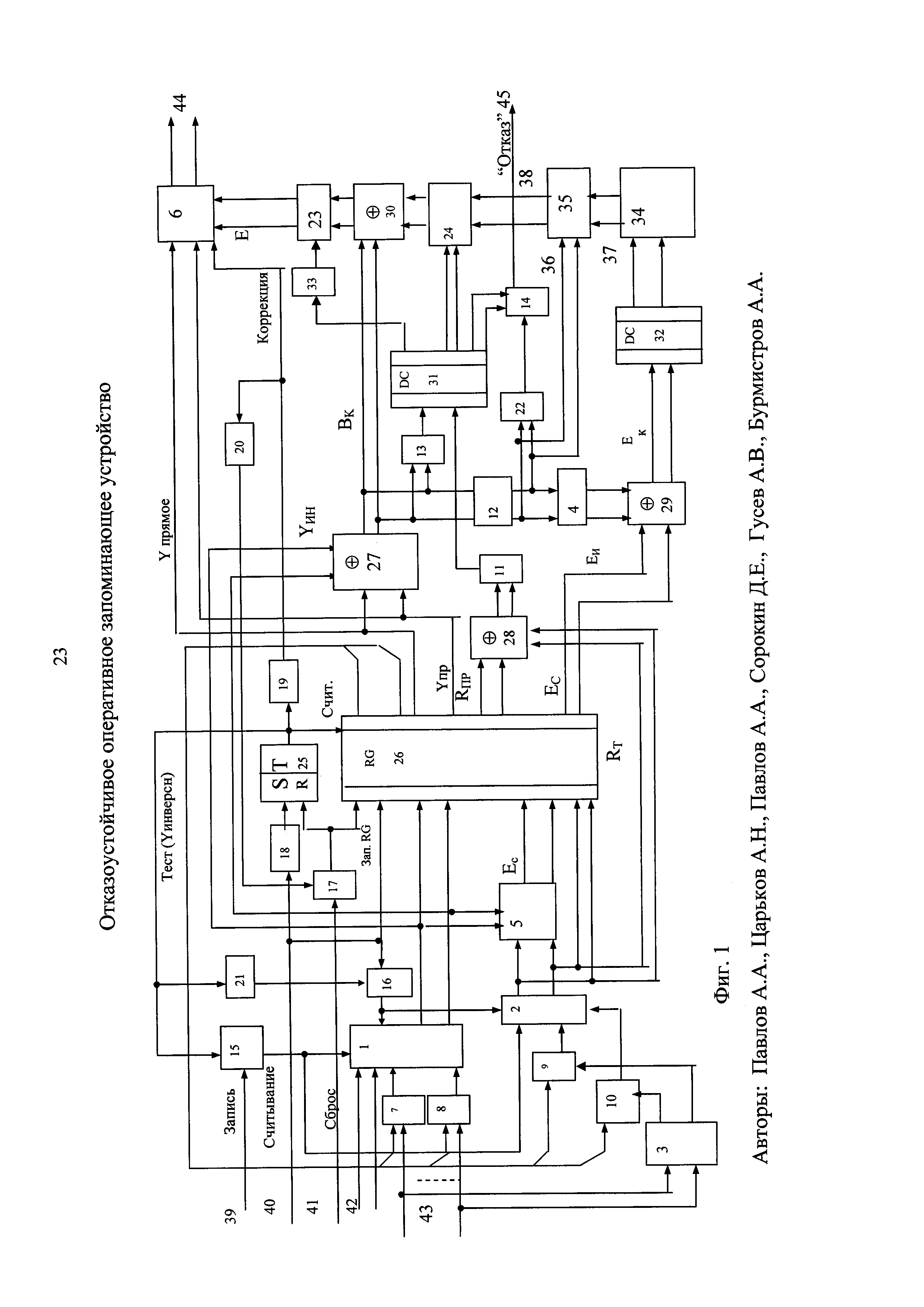

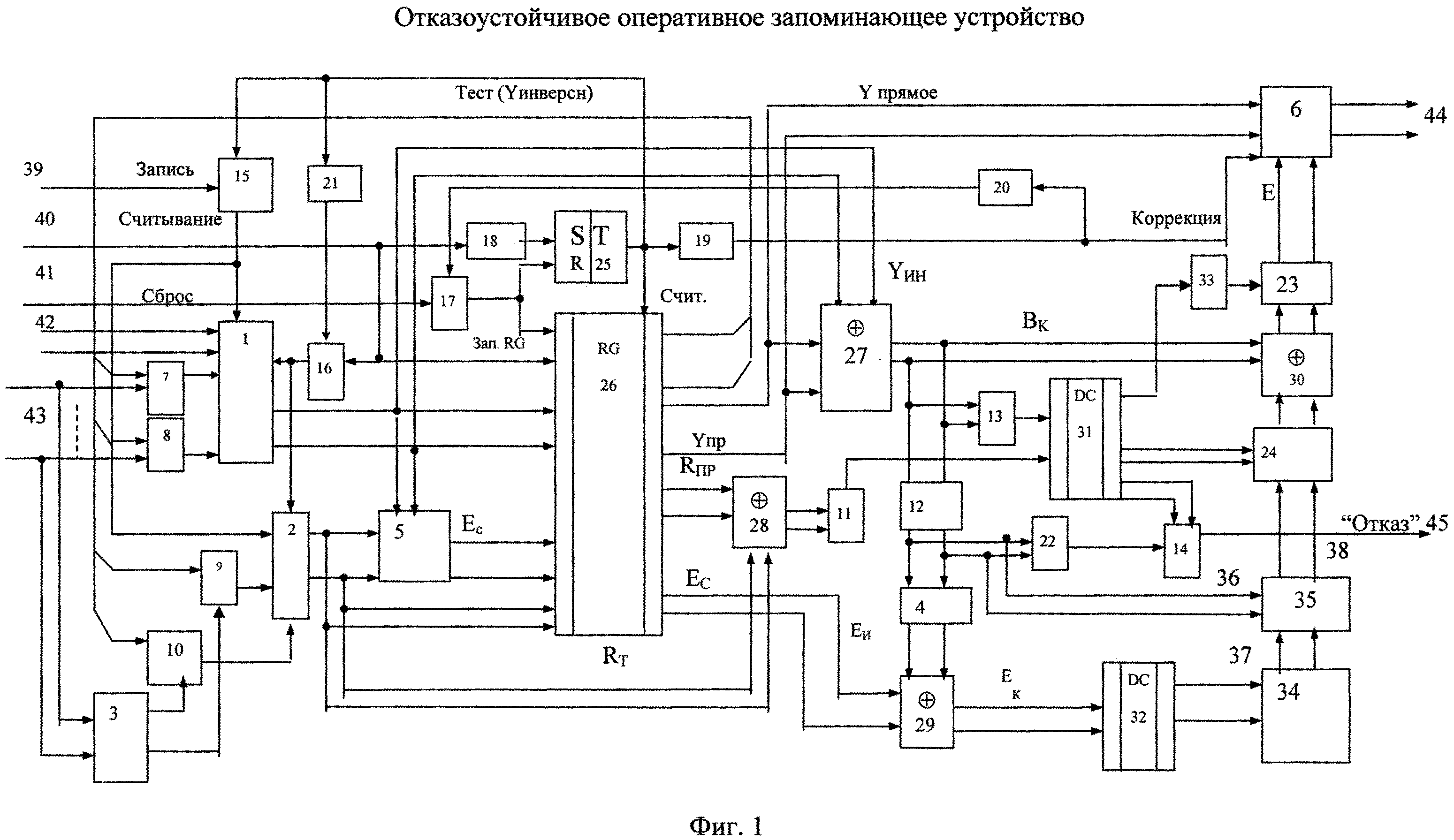

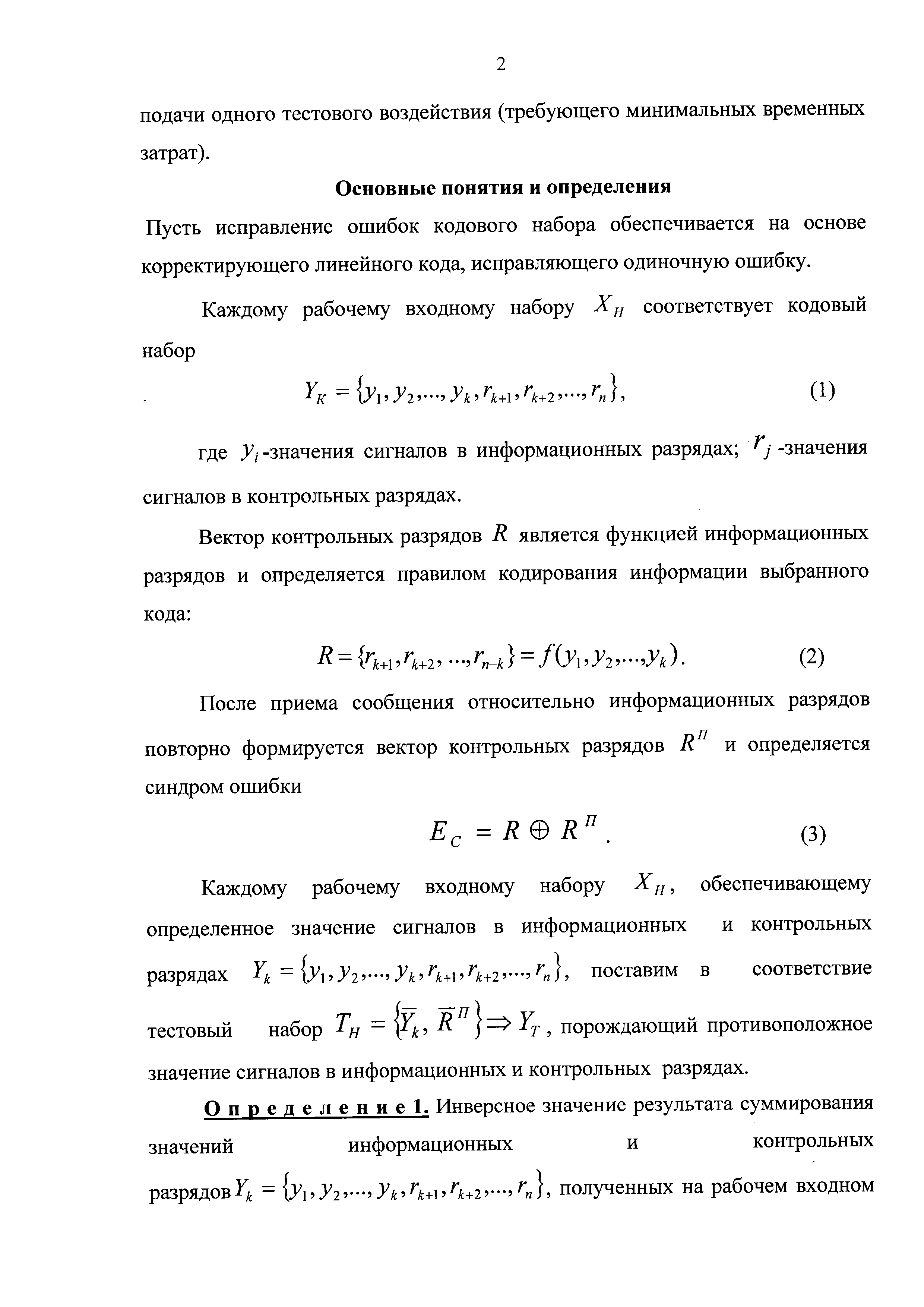

На фиг.1 представлена блок-схема отказоустойчивого оперативного запоминающего устройства. Отказоустойчивое оперативное запоминающее устройство содержит исходный вычислительный канал 1, избыточный вычислительный канал 2, первое кодирующее устройство 3, второе кодирующее устройство 4, блок вычисления синдрома 5, корректор 6, с первого по восьмой 7, 8, 9, 10, 11, 12, 13, 14 блоки элементов ИЛИ, с первого по третий 15, 16, 17 элементы ИЛИ, с первого по четвертый 18, 19, 20, 21 элементы задержки, с первого по третий 22, 23, 24 блоки элементов И, RS-триггер 25, регистр 26, с первого по четвертый 27, 28, 29, 30 блоки элементов неравнозначности, первый 31 и второй 32 дешифраторы, 33-элемент НЕ, блок 34 хранения поправок, блок 35 вычисления признака поправки, входы 36, 37 являются входами блока 35 вычисления признака поправки, выход 38 является выходом блока 35 вычисления признака поправки, вход 39 ″Запись″, вход 40 ″Считывание″, вход 41 ″Сброс″, адресные входы 42, информационные входы 43, информационные выходы 44, выход 45 восьмого блока 14 элементов ИЛИ является выходом формирования сигнала ″Отказ устройства″.

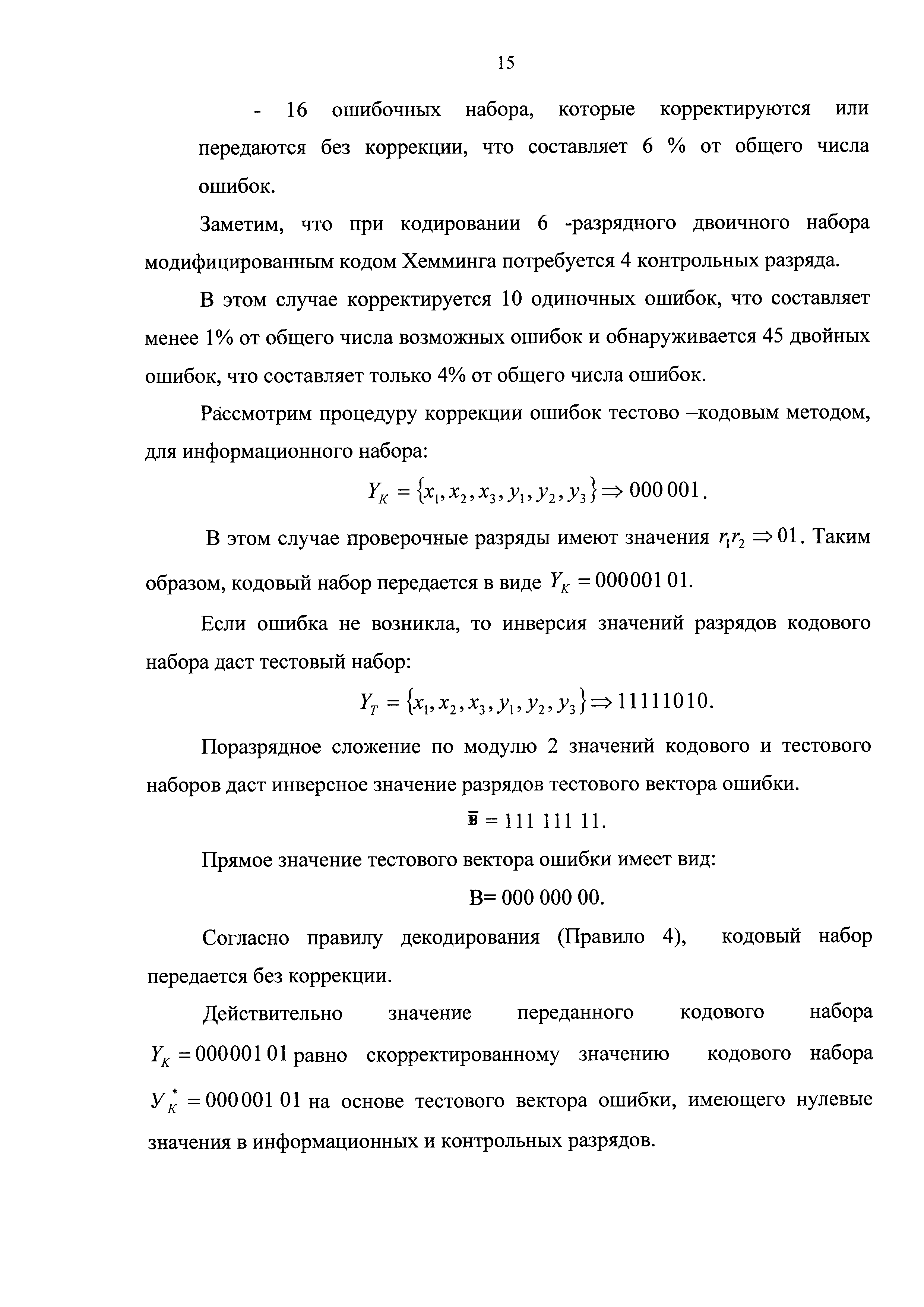

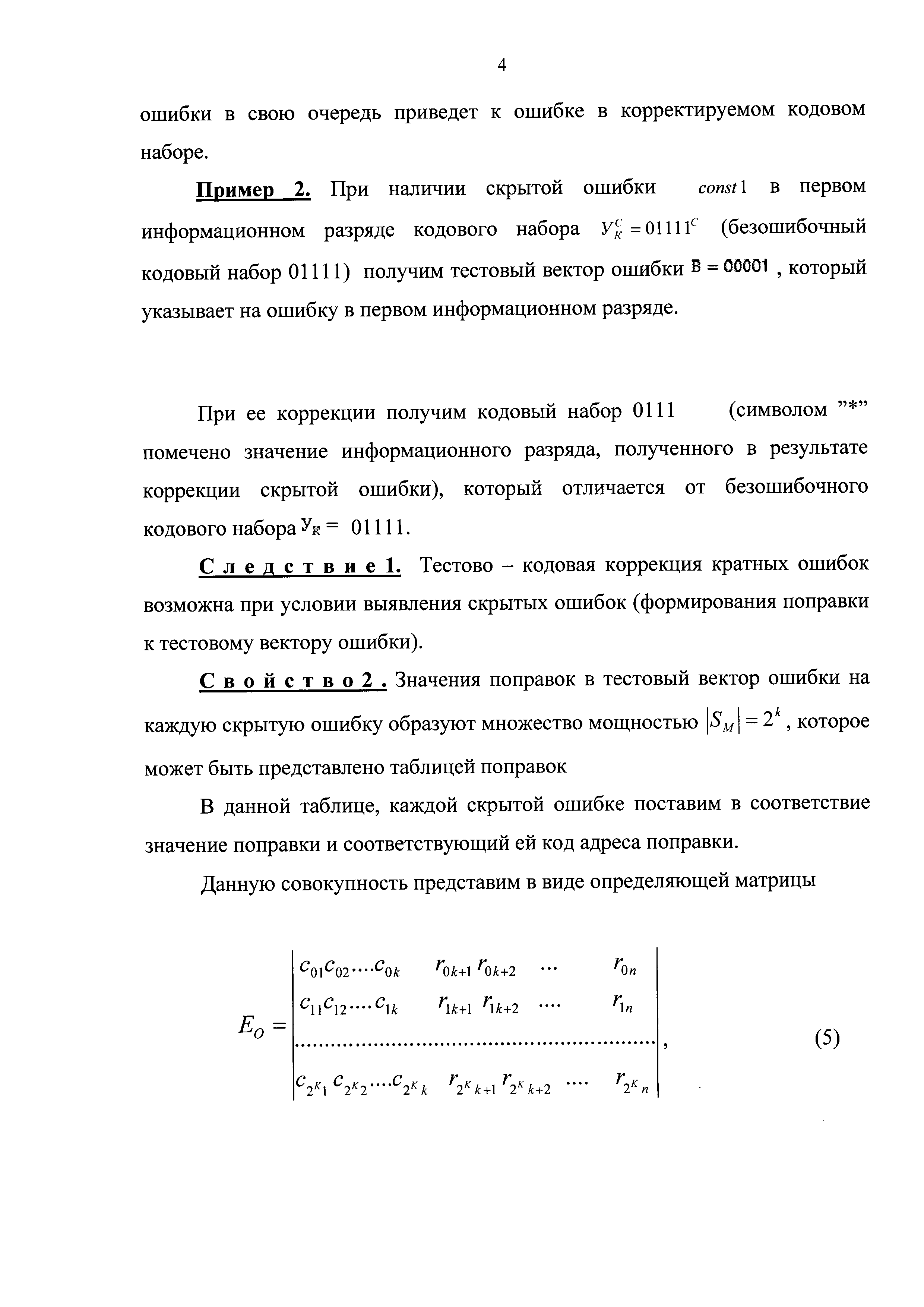

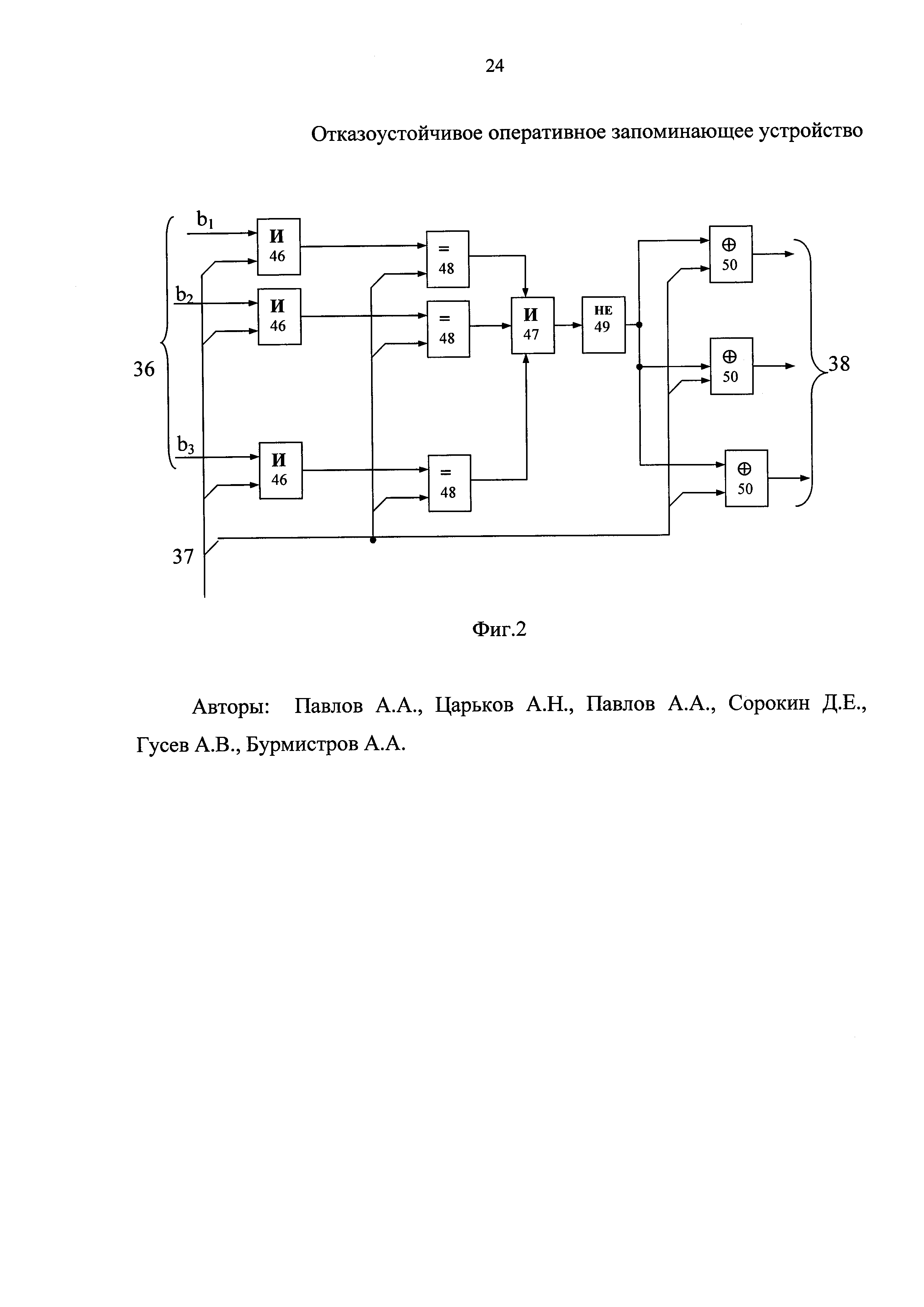

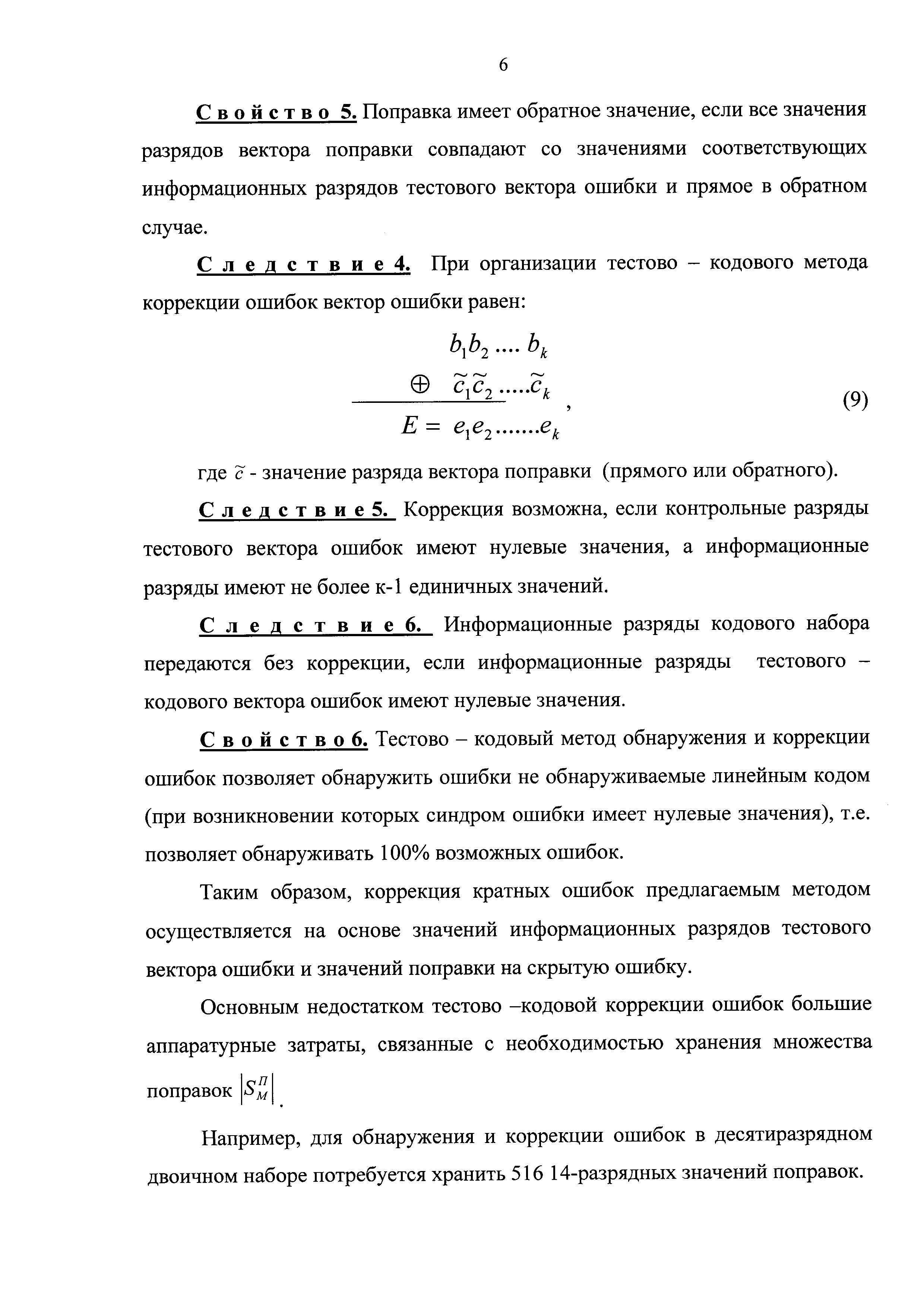

На фиг. 2 представлена схема блока 33 вычисления признака поправки. Он содержит группу 46 - элементов И, 47 - элемент И, элементы 48 равнозначности, 49 - элемент НЕ, группу элементов 50 неравнозначности.

Адресные входы 42 подключены к первым входам исходного вычислительного канала 1, информационные входы 43 через первый 7 и второй 8 блоки элементов ИЛИ подключены ко вторым входам исходного вычислительного канала 1 и к первым входам первого кодирующего устройства 3, подключенного своими выходами через третий 9 и четвертый 10 блоки элементов ИЛИ к первым входам избыточного вычислительного канала 2, вход 41 сброс через третий элемент 17 ИЛИ подключен к нулевым входам регистра и RS-триггера 25, вход 40 считывание подключен к входу запись регистра 26, через второй элемент 16 ИЛИ к третьему входу исходного вычислительного канала 1, к второму входу избыточного вычислительного канала 2 и через первый элемент 18 задержки к единичному входу RS-триггера 25, вход 39 запись через первый элемент 15 ИЛИ подключен к четвертому входу исходного вычислительного канала 1, третьему входу избыточного вычислительного канала 2, выходы исходного вычислительного канала 1 подключены к вторым входам регистра 26, к первым входам блока 5 вычисления синдрома и к первым входам первого блока 27 элементов неравнозначности, выходы избыточного вычислительного канала 2 подключены к вторым входам блока вычисления синдрома, к третьим входам регистра 26 и к первым входам второго блока элементов 28 неравнозначности, выходы блока 5 вычисления синдрома подключены к четвертым входам регистра 26, единичный выход RS-триггера 25 подключен к входу считывание регистра 26, к второму входу первого элемента 15 ИЛИ, через второй элемент 19 задержки к первому входу корректора 6, через третий элемент 20 задержки к второму входу третьего элемента 17 ИЛИ, через четвертый элемент 21 задержки к второму входу второго элемента 16 ИЛИ, первая группа выходов регистра 26 подключена к вторым входам с первого 7 по четвертый 10 блоков элементов ИЛИ, вторая группа выходов регистра 26 подключена к вторым входам первого блока 27 элементов неравнозначности и к вторым входам корректора 6, третья и четвертая группы выходов регистра 26 подключены соответственно к вторым входам второго блока 28 элементов неравнозначности и к первым входам третьего блока 29 элементов неравнозначности, выход первого блока 27 элементов неравнозначности подключен к входам шестого блока 12 элементов ИЛИ, к входам седьмого блока 13 элементов ИЛИ, к первым входам четвертого блока 30 элементов неравнозначности, выходы второго блока 28 элементов неравнозначности подключены к входам пятого блока 11 элементов ИЛИ, выходы шестого блока 12 элементов ИЛИ подключены к входам второго кодирующего устройства 4, к входам первого блока 22 элементов И и к первым входам блока 35 вычисления признака поправки, выходы второго кодирующего устройства 4 подключены к вторым входам третьего блока 29 элементов неравнозначности, выход пятого блока 11 элементов ИЛИ и выходы седьмого блока 13 элементов ИЛИ подключены к входам первого дешифратора 31, первый выход которого через элемент 33 НЕ подключен к первому входу второго блока 23 элементов И, а вторая группа выходов подключена к входам третьего блока 24 элементов И, третья группа выходов первого дешифратора 31 подключена к первым входам восьмого блока 14 элементов ИЛИ, второй вход которого подключен к выходу первого блока 22 элементов И, выходы третьего блока 29 элементов неравнозначности подключены к входам второго дешифратора 32, подключенного своими выходами ко входам блока 34 хранения поправок, выходы которого подключены ко вторым входам блока 35 вычисления признака поправки, соединенного своими выходами со вторыми входами третьего блока 24 элементов И, выходы которого подключены к вторым входам четвертого блока 30 элементов неравнозначности, выходы четвертого блока 30 элементов неравнозначности через второй блок 23 элементов И подключены к третьим входам корректора 6, выходы которого являются информационными выходами 44 устройства, выход восьмого блока 14 элементов ИЛИ является выходом формирования сигнала ″Отказ устройства″.

Исходный вычислительный канал 1 и избыточный вычислительный канал 2 представляет собой полупроводниковое оперативное ЗУ, включающее дешифраторы выбора строк и столбцов элементов памяти двух накопителей, например, трехразрядного накопителя исходного вычислительного канала 1 (каждая ячейка памяти включает три триггера) и двухразрядного накопителя избыточного вычислительного канала 2, предназначенного для хранения значений контрольных разрядов. Запись информации, поступающей в накопители с информационных входов 43, происходит по адресу, считываемому с адресных входов 42 при подаче сигнала на вход 39 ″Запись″, причем во второй накопитель информация записывается после ее кодирования первым кодирующим устройством 3. Считывание требуемого слова памяти с накопителей происходит при подаче сигнала на соответствующие адресные входы 42 и сигнала на вход 40 ″Считывание″. При возникновении ошибок в исходном вычислительном канале 1 (первом накопителе) откорректированное значение информационных разрядов считывается с информационных выходов 44.

Вход 41 ″Сброс″ предназначен для установки в нулевое состояние RS триггера 25 и регистра 26.

Первое кодирующее устройство 3 имеет два выхода r1, r2, на которых реализуются логические функции соответственно:

r1=х1⊕х2⊕y1⊕y2; r2=х2⊕х3⊕y2⊕y3

Второе кодирующее устройство 4 выполняет функции, аналогичные первому кодирующему устройству 3 относительно блока информационных разрядов тестового вектора ошибки В, имеющего ошибку:

rb1=bi1⊕bi2; rb2=bi2⊕bia.

Блок 5 вычисления синдрома выполняет операцию повторного кодирования информации, считываемой с исходного вычислительного канала 1: r1П=х1C⊕x2C⊕y1С⊕y2C; r2П=x2C⊕х3С⊕y2С⊕y3С и поразрядного сложения по модулю 2 контрольных разрядов r1⊕r1П; r2⊕r2П для вычисления синдрома ошибки ЕС:

Корректор 6 предназначен для исправления возникающих ошибок путем сложения информационных разрядов с вектором ошибки:

С первого 7 по четвертый 10 блоки элементов ИЛИ предназначены для обеспечения функциональных связей между блоками устройства.

Пятый блок 11 элементов ИЛИ обеспечивает появление единичное значения сигнала на своем выходе, при наличии ошибки в контрольных разрядах.

Шестой блок 12 элементов ИЛИ обеспечивает группирование одноименных разрядов информационных блоков тестового вектора ошибки.

Седьмой блок 13 обеспечивает группирование информационных разрядов тестового вектора ошибки на блоки информации (по три разряда в каждом блоке).

Восьмой блок 14 элементов ИЛИ обеспечивает единичное значение сигнала при наличии трех единичных значений в одном из блоков тестового вектора ошибки (при наличии сигнала на выходе первого блока 22 элементов И), при наличии ошибок одновременно в контрольных разрядах и наличии единичных значений сигналов хотя бы в одном из информационных блоках тестового вектора ошибки (одновременного появления сигналов на выходе пятого 11 и седьмого 13 блоков элементов ИЛИ) или одновременного наличия единичных значений сигналов в двух и более информационных блоках тестового вектора ошибки (одновременного наличия сигналов на двух и более выходах седьмого блока 13 элементов ИЛИ).

С первого 15 по третий 17 элементы ИЛИ предназначены для обеспечения функциональных связей между блоками устройства.

С первого 18 по четвертый 21 элементы неравнозначности предназначены для обеспечения синхронизации работы блоков устройства.

Первый блок 22 элементов И обеспечивает появление единичного значения сигнала на своем выходе при одновременно наличии трех единичных значений, поступающих с выходов шестого блока 12 элементов ИЛИ (наличии трех единичных значений сигналов в одном из информационных блоков тестового вектора ошибки).

Второй блок 23 элементов И разрешает (запрещает подачу сигналов вектора ошибки на вход корректора 6.

Третий блок 24 элементов И по сигналам, поступающим с второй группы выходов первого дешифратора 31, разрешает подачу поправки на соответствующие разряды тестового вектора ошибки.

Триггер 25 предназначены для обеспечения функциональных связей между блоками устройства.

Регистр 26 предназначен для хранения прямых и обратных значений кодового набора.

Первый блок 27 элементов неравнозначности предназначен для формирования тестового вектора ошибки (сложения по модулю 2 прямых и инверсных значений кодового набора и инвертирования результата суммы).

Второй блок 28 элементов неравнозначности предназначен для обнаружения ошибок в контрольных разрядах кодового набора (сложения по модулю 2 прямых и инверсных значений контрольных разрядов и инвертирования результата суммы).

Третий блок 29 элементов неравнозначности предназначен для формировании адреса поправки Eк путем сложения по модулю 2 одноименных разрядов синдрома ошибки EC и кода блока информационных разрядов тестового вектора ошибки, имеющего ошибку.

Четвертый блок 30 элементов неравнозначности предназначен для формировании вектора ошибки путем сложения по модулю 2 разрядов информационного блока тестового вектора ошибки, имеющего скрытую ошибку с значениями поправки C на скрытую ошибку.

Первый дешифратор 31 обеспечивает появление сигнала на первом выходе (кодовый набор передается без коррекции) при отсутствии ошибки в кодовом наборе (отсутствии сигнала на выходах седьмого блока 13 элементов ИЛИ) или наличии сигнала, поступающего с выхода пятого блока 11 элементов ИЛИ (при наличии ошибки в контрольных разрядах. В зависимости от значения сигналов на выходах седьмого 13 блока элементов ИЛИ определяет блок информационных разрядов, имеющий ошибку (открывает соответствующую группу элементов И третьего блока 24 элементов И).

Формирует сигнал ″Отказ устройства″ при одновременном появлении сигналов на двух и более выходах седьмого блока 13 элементов ИЛИ, или одновременном появлении сигналов на выходах пятого 11 и седьмого 13 блоков элементов ИЛИ.

Второй дешифратор 32 предназначен для организации считывания информации с блока 34 хранения поправок по коду адреса поправки Eк.

Элемент 33 НЕ запрещает коррекцию кодового набора при подаче на его вход единичного значения сигнала.

Блок 34 хранения поправок предназначен для хранения значений поправок в соответствии с матрицей поправок используемого кода.

Блоком 35 вычисления признака поправки (см. Фиг 2) в зависимости от информации, поступающей с выходов второго кодирующего устройства 4, выбирается прямое или обратное значение поправки.

Блок 35 вычисления признака поправки работает следующим образом. По значению кода адреса поправки Ек с блока 34 хранения поправок считывается обратное значение поправки (содержащее для данной ошибки максимальное количество единиц), которое поступает на вход 35 блока вычисления признака поправки и соответственно на входы группы элементов 46 И, группы элементов 48 равнозначности и группы элементов 50 неравнозначности. Значения информационных разрядов тестового вектора ошибки поступают на входы 36 блока 35 вычисления признака поправки.

В этом случае открываются элементы И группы элементов 46 И, имеющие на своих входах единичные значения сигналов поправки и информационных разрядов тестового вектора ошибки. Если значение сигналов, поступающих с выходов элементов И, совпадают с значением поправки, то на выходах всех элементов группы элементов 48 равнозначности появляются единичные значения сигналов (открывается элемент 47 И). В этом случае сигнал на выходе элемента 49 имеет нулевое значение, поэтому с выходов элементов 50 неравнозначности снимается обратное значение поправки. Если значение поправки не совпадает с значениями сигналов тестового вектора ошибки (сигнал на выходе элемента 47 И имеет нулевое значение), то сигнал, поступающий с выхода элемента 49 НЕ на входы элементов 50 неравнозначности, обеспечивает инвертирование значений сигналов поправки (формируется прямое значение поправки).

Устройство работает следующим образом. Перед началом работы на вход 41 подается сигнал ″Сброс″, который через третий элемент 17 ИЛИ устанавливает в нулевое состояние триггер 25 и регистр 26. При поступлении сигнала ″Запись″ на вход 39 и адреса ячейки памяти на входы 42 в выбранную ячейку записывается информация, поступающая вход 43. Одновременно подаваемая информация кодируется первым кодирующим устройством 3, и значения контрольных разрядов записываются в избыточный вычислительный канал 2.

При поступлении сигнала ″Считывание″ по выбранному адресу сигнал со входа 40 через второй элемент 16 ИЛИ поступает на вход считывания исходного вычислительного канала 1 и избыточного вычислительного канала 2.

Информация, считываемая с исходного вычислительного канала 1 и избыточного вычислительного канала 2, поступает на блок 5 вычисления синдрома, где она повторно кодируется и сравнивается с значениями контрольных разрядов, т.е. вычисляется синдром ошибки. Кроме этого сигналом, поступающим со входа 40, разрешается запись информационных разрядов и значения синдрома ошибки в регистр 26.

Через время, определяемое первым элементом 18 задержки, RS-триггер 25 переводится в единичное состояние и его единичный сигнал разрешает считывание информации с регистра 26.

Информация, считываемая с инверсных выходов регистра 26 (тестовое воздействие) через первый 7, второй 8, третий 9 и четвертый 10 блоки элементов ИЛИ, поступает на входы исходного вычислительного канала 1 и избыточного вычислительного канала 2.

Через время, определяемое четвертым элементом 21 задержки, сигнал с выхода RS-триггера 25 через второй элемент 16 ИЛИ разрешает повторное считывание информации (результатов тестового воздействия) с исходного вычислительного канала 1 и избыточного вычислительного канала 2.

Полученная ответная информация (YT, RT) сравнивается с исходной информацией (Yпр, Rпр) соответственно первым блоком 27 элементов неравнозначности и вторым блоком 28 элементов неравнозначности, т.е. формируется тестовый вектор ошибки В.

Полученное значение информационных разрядов тестового вектора ошибки В группируется на блоки информации (по три разряда в каждом блоке) шестым блоком 12 элементов ИЛИ и кодируется вторым кодирующим устройством 4 (формируется код ошибки тестовых разрядов ЕИ) и затем сравнивается с значением синдрома ошибки ЕС на третьем блоке 29 элементов неравнозначности (формируется значение кода адреса поправки Ек).

Если ошибок нет, то на первом выходе первого дешифратора 31 появляется единичное значение сигнала, которое через элемент 33 НЕ закрывает второй блок 23 элементов И, кодовый набор передается без коррекции.

При возникновении ошибки во всех информационных разрядах блока информации тестового вектора ошибки (появлении сигнала на выходе первого блока 22 элементов И) или одновременном возникновении ошибок в информационных и контрольных разрядах (появлении сигналов на двух и более выходах седьмого блока 13 элементов ИЛИ) на третьей группе выходов первого дешифратора 31 появятся единичные значения сигналов, поступающие на вход восьмого блока 14 элементов ИЛИ, формируется сигнал ″Отказ устройства″.

При возникновении ошибки только в контрольных разрядах (наличие единичного значения сигнала на выходе пятого блока 11 элементов ИЛИ) и отсутствии ошибок в информационных разрядах (наличие нулевого значения сигнала на выходе седьмого блока 13 элементов ИЛИ) на выходе первого дешифратора 31 появляется сигнал, который через элемент 33 НЕ, второй блок 23 элементов И запрещает подачу сигналов вектора ошибки Ε на корректор 6.

При возникновении скрытой ошибки третьим блоком 29 неравнозначности формируется код адреса поправки Ек, по которому вторым дешифратором 32 выбирается обратное значение поправки из блока 34 хранения поправок. В результате сравнения значения выбранной поправки с значениями информационных разрядов тестового вектора ошибки блоком 35 вычисления признака поправки выбирается прямое или обратное значение поправки. В результате сложения значений информационных разрядов тестового вектора ошибки с выбранным значениям поправки, четвертым блоком 30 элементов неравнозначности, формируется вектор ошибки Е.

Исправление ошибки корректором 6 осуществляется путем сложения информационных разрядов Υпр, содержащих ошибку, с вектором ошибки Е.

Предлагаемое устройство позволяет обеспечить: - минимальную информационную избыточность (два контрольных разряда);

- высокую достоверность функционирования (обнаруживать 100% возможных ошибок, включая ошибки, трансформируемые в разрешенные (безошибочные) кодовые наборы);

- обнаруживать скрытые ошибки;

- минимизировать аппаратурные затраты на построение декодирующего устройства (не требует хранения таблицы синдромов ошибок и использует минимальную таблицу поправок);

- исключает методическую ошибку декодирования (характерную для большинства декодирующих устройств, реализующих метод ″максимума правдоподобия″, когда ошибки различной кратности, имеющие одинаковый синдром и принадлежащие одному смежному классу, корректируются исходя из кодового расстояния выбранного линейного кода);

- минимизировать временные затраты на коррекцию ошибок (требуется подача одного тестового воздействия).

ИСТОЧНИКИ ИНФОРМАЦИИ

1. Патент на изобретение №2403615 ″Устройство хранения и передачи информации с обнаружением двойных ошибок″ / Павлов А.А., Царьков А.Н. и др. от 27.01.2009 г.

2. Патент на изобретение №2211492 /Отказоустойчивое оперативное запоминающее устройство. Павлов А.А., Шандриков А.В. от 27.08.2003 г. А.С. СССР №1716521, кл. G06F 11/18, 1989 г.

Отказоустойчивое оперативное запоминающее устройство, использующее линейный код, содержащий минимальное количество разрядов, для обнаружения одиночных и двойных ошибок, а также для определение конфигурации ошибочных разрядов и их коррекции по значению синдрома ошибки и результатам анализа ответной реакции, полученной на основе подачи тестового воздействия, содержащее исходный вычислительный канал, избыточный вычислительный канал, первый дешифратор, корректор, с первого по седьмой блоки элементов ИЛИ, с первого по третий элементы ИЛИ, с первого по четвертый элементы задержки, первый и второй блоки элементов И, RS-триггер, регистр, с первого по четвертый блоки элементов неравнозначности, второй дешифратор, элемент НЕ, блок хранения поправок, блок вычисления признака поправки, отличающееся тем, что дополнительно содержит восьмой блок элементов ИЛИ, третий блок элементов И, первое кодирующее устройство, формирующие значения контрольных разрядов r1 и r2 путем сложения по модулю 2 информационных символов x1, x2, x3, y1, y2, y3, поступающих на входы первого блока кодирования, в соответствии с правилом: r1=x1⊕x2⊕y1⊕y2; r2=x2⊕x3⊕y2⊕y3, блок вычисления синдрома, формирующий значения проверочных контрольных разрядов r1, r2 путем сложения по модулю 2 информационных символов x1, x2, x3, y1, y2, y3, поступающих на его входы при считывании информации с информационных выходов исходного вычислительного канала в соответствии с правилом: r1=x1⊕x2⊕y1⊕y2; r2=x2⊕x3⊕y2⊕y3 и поразрядного сложения по модулю 2 контрольных разрядов r1⊕r1; r2⊕r2, регистр, осуществляющий хранение прямых и инверсных значений кодового набора, первый блок элементов неравнозначности, формирующий тестовый вектор ошибки путем сложения по модулю 2 прямых и инверсных значений кодового набора и инвертирования результата суммы, второй блок элементов неравнозначности, обнаруживающий ошибки в контрольных разрядах кодового набора путем сложения по модулю 2 прямых и инверсных значений контрольных разрядов и инвертирования результата суммы, второе кодирующее устройство, формирующее значения контрольных разрядов r и r, определяющих код ошибки тестовых разрядов, путем сложения по модулю 2 информационных символов тестового вектора ошибки b, b, b для i-го блока информационных разрядов тестового вектора ошибок, свидетельствующего о наличии ошибки, поступающих на его входы в соответствии с правилом: rb=b⊕b: r=b⊕b, третий блок элементов неравнозначности, формирующий адрес поправки путем сложения по модулю 2 одноименных разрядов синдрома ошибки и кода ошибки тестовых разрядов, четвертый блок элементов неравнозначности, формирующий вектор ошибки путем сложения по модулю 2 разрядов информационного блока тестового вектора ошибки, имеющего скрытую ошибку с значениями поправки на скрытую ошибку, первый дешифратор, обеспечивающий появление сигнала на первом выходе, при котором кодовый набор передается без коррекции, при отсутствии ошибки в кодовом наборе, то есть отсутствии сигнала на выходах седьмого блока элементов ИЛИ или наличии сигнала, поступающего с выхода пятого блока элементов ИЛИ при наличии ошибки в контрольных разрядах, в зависимости от значения сигналов на выходах седьмого блока элементов ИЛИ определяется блок информационных разрядов, имеющий ошибку, в этом случае открывается соответствующая группа элементов И третьего блока элементов И, формирующая сигнал "Отказ устройства" при одновременном появлении сигналов на двух и более выходах седьмого блока элементов ИЛИ, или одновременном появлении сигналов на выходах пятого и седьмого блоков элементов ИЛИ, второй дешифратор, обеспечивающий считывание информации с блока хранения поправок по коду адреса поправки, элемент НЕ, запрещающий коррекцию кодового набора при подаче на его вход единичного значения сигнала, блок хранения поправок, обеспечивающий хранение значений поправок в соответствии с матрицей поправок используемого кода, блок вычисления признака поправки, обеспечивающий в зависимости от информации, поступающей с выходов второго кодирующего устройства, выбор прямого или обратного значения поправки, корректор, осуществляющий исправление возникающих ошибок путем сложения по модулю 2 значений информационных разрядов с значениями вектором ошибки, причем адресные входы подключены к первым входам исходного вычислительного канала, информационные входы через первый и второй блоки элементов ИЛИ подключены ко вторым входам исходного вычислительного канала и к первым входам первого кодирующего устройства, подключенного своими выходами через третий и четвертый блоки элементов ИЛИ к первым входам избыточного вычислительного канала, вход сброс через третий элемент ИЛИ подключен к нулевым входам регистра и RS-триггера, вход считывание подключен к входу запись регистра, через второй элемент ИЛИ к третьему входу исходного вычислительного канала, к второму входу избыточного вычислительного канала и через первый элемент задержки к единичному входу RS-триггера, вход запись через первый элемент ИЛИ подключен к четвертому входу исходного вычислительного канала, третьему входу избыточного вычислительного канала, выходы исходного вычислительного канала подключены ко вторым входам регистра, к первым входам блока вычисления синдрома и к первым входам первого блока элементов неравнозначности, выходы избыточного вычислительного канала подключены к вторым входам блока вычисления синдрома, к третьим входам регистра и к первым входам второго блока элементов неравнозначности, выходы блока вычисления синдрома подключены к четвертым входам регистра, единичный выход RS-триггера подключен к входу считывание регистра, к второму входу первого элемента ИЛИ, через второй элемент задержки к первому входу корректора, через третий элемент задержки к второму входу третьего элемента ИЛИ, через четвертый элемент задержки к второму входу второго элемента ИЛИ, первая группа выходов регистра подключена к вторым входам с первого по четвертый блоков элементов ИЛИ, вторая группа выходов регистра подключена к вторым входам первого блока элементов неравнозначности и к вторым входам корректора, третья и четвертая группы выходов регистра подключены соответственно к вторым входам второго блока элементов неравнозначности и к первым входам третьего блока элементов неравнозначности, выход первого блока элементов неравнозначности подключен к входам шестого блока элементов ИЛИ, к входам седьмого блока элементов ИЛИ, к первым входам четвертого блока элементов неравнозначности, выходы второго блока элементов неравнозначности подключены к входам пятого блока элементов ИЛИ, выходы шестого блока элементов ИЛИ подключены к входам второго кодирующего устройства, к входам первого блока элементов И и к первым входам блока вычисления признака поправки, выходы второго кодирующего устройства 4 подключены к вторым входам третьего блока 29 элементов неравнозначности, выход пятого блока элементов ИЛИ и выходы седьмого блока элементов ИЛИ подключены к входам первого дешифратора, первый выход которого через элемент НЕ подключен к первому входу второго блока элементов И, а вторая группа выходов подключена к входам третьего блока элементов И, третья группа выходов первого дешифратора подключена к первым входам восьмого блока элементов ИЛИ, второй вход которого подключен к выходу первого блока элементов И, выходы третьего блока элементов неравнозначности подключены к входам второго дешифратора, подключенного своими выходами ко входам блока хранения поправок, выходы которого подключены ко вторым входам блока вычисления признака поправки, соединенного своими выходами со вторыми входами третьего блока элементов И, выходы которого подключены к вторым входам четвертого блока элементов неравнозначности, выходы четвертого блока элементов неравнозначности через второй блок элементов И подключены к третьим входам корректора, выходы которого являются информационными выходами устройства, выход восьмого блока элементов ИЛИ является выходом формирования сигнала "Отказ устройства".