Результат интеллектуальной деятельности: УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ МОДУЛЯ РАЗНОСТИ ДВУХ ВХОДНЫХ ТОКОВ

Вид РИД

Изобретение

Предполагаемое изобретение относится к области вычислительной техники, автоматики и может использоваться в различных цифровых структурах и системах автоматического управления, передачи информации и т.п.

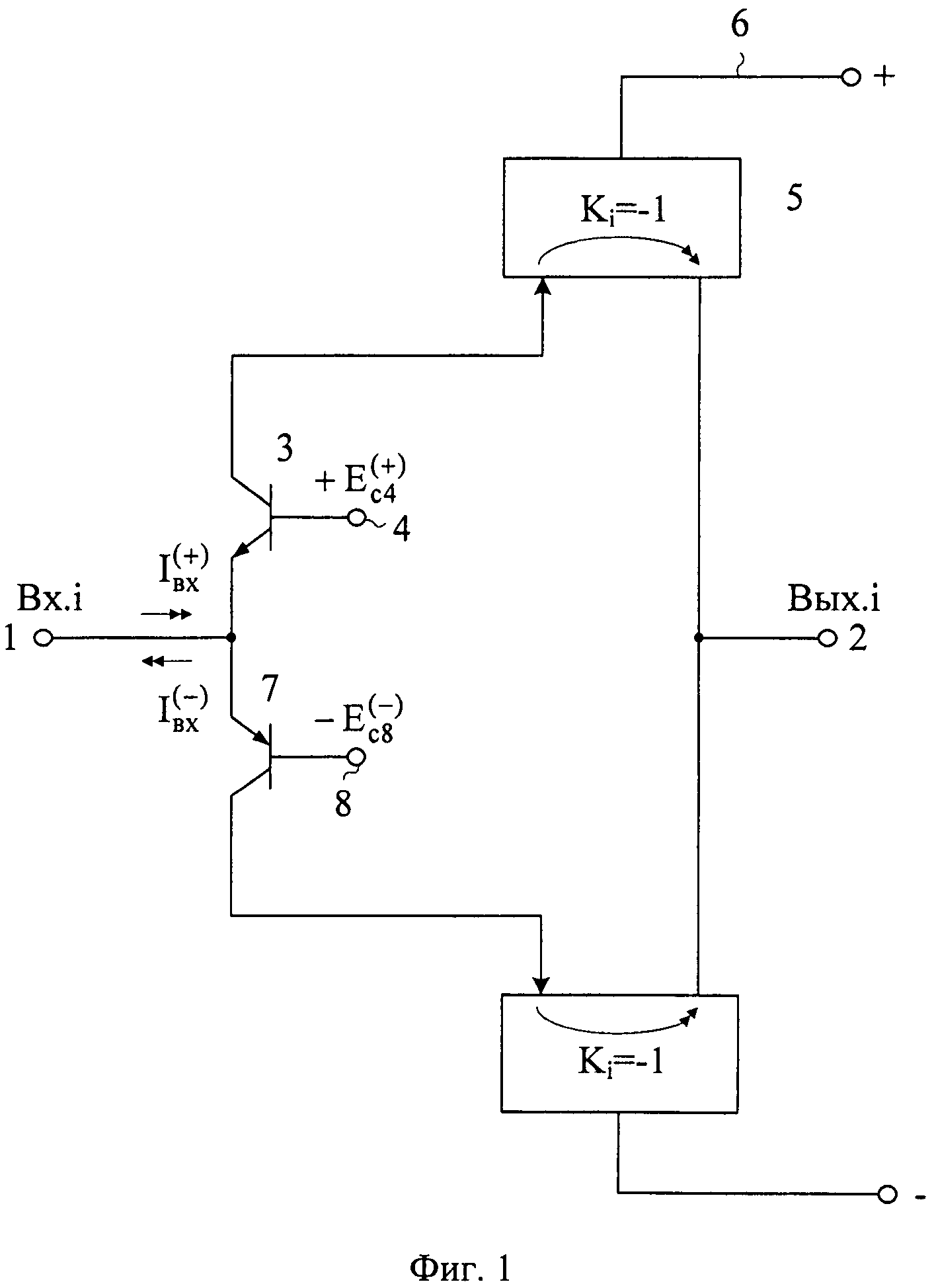

В современной аналого-цифровой микросхемотехнике широкое применение получила структура преобразователя входных токовых сигналов с токовым выходом (фиг.1), которая является базовой для так называемых усилителей с «токовой» обратной связью [1-8].

Ближайшим прототипом предлагаемого устройства является каскад преобразования двух входных токов, представленный в патенте US 5.791.414 fig.2. Данная структура присутствует также в других патентах [2-7] и статьях [8].

Существенный недостаток известного устройства состоит в том, что оно не выполняет логическую функцию выделения модуля разности двух входных логических токов, что не позволяет реализовывать на его основе различные логические элементы средств вычислительной техники в элементном базисе линейной алгебры [9, 10].

Основная задача предлагаемого изобретения состоит в реализации логической операции выделения модуля разности двух входных токов, соответствующих многозначным логическим уравнениям.

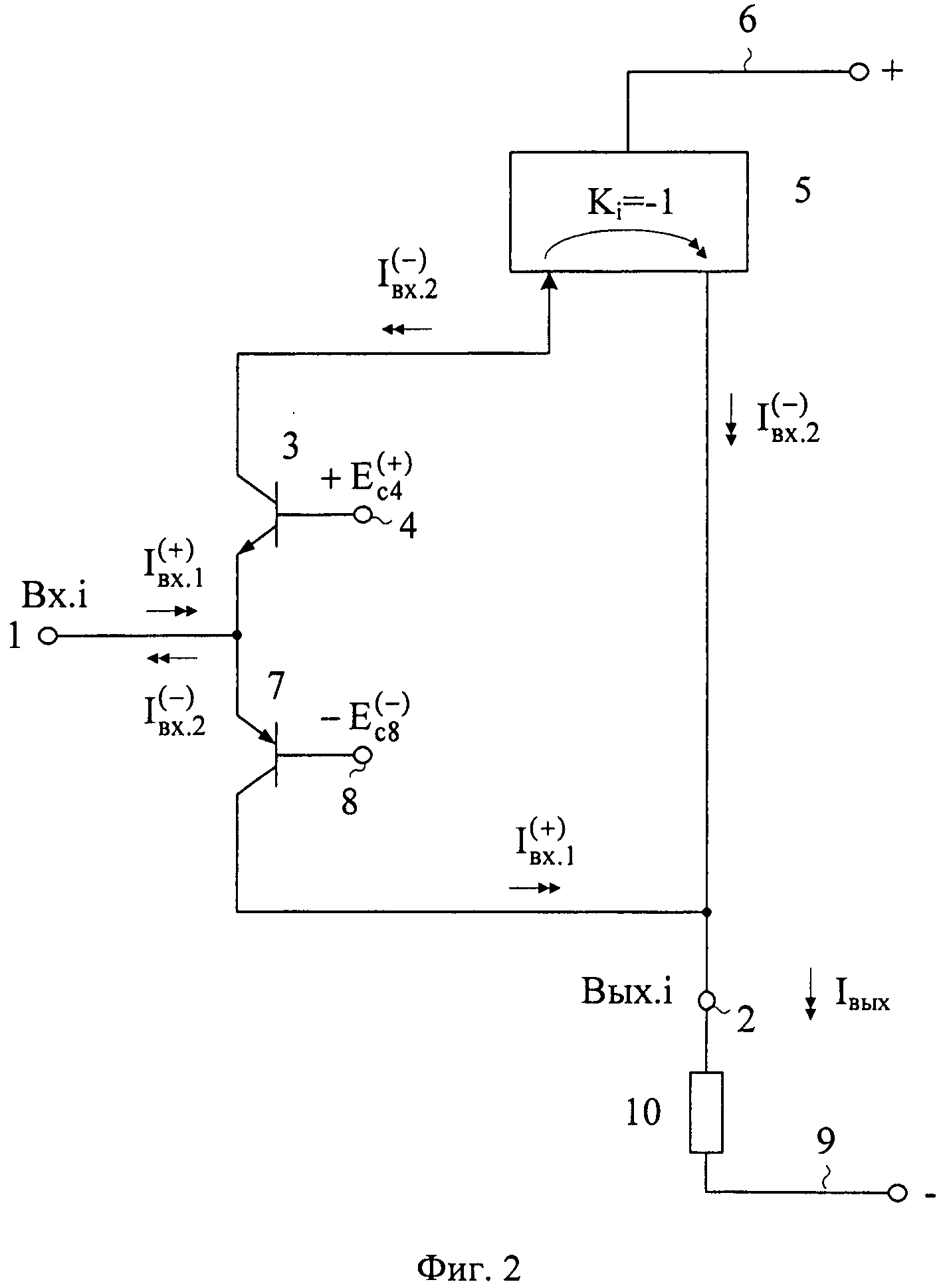

Поставленная задача решается тем, что в устройстве для преобразования входных токов (фиг.1), содержащем токовый вход 1 и токовый выход 2, первый 3 входной транзистор, эмиттер которого соединен с токовым входом устройства 1, база подключена к первому 4 источнику вспомогательного напряжения, а коллектор соединен со входом токового зеркала 5, согласованного с первой 6 шиной источника питания, второй 7 входной транзистор, эмиттер которого соединен с токовым входом 1 устройства, а база подключена ко второму 8 источнику вспомогательного напряжения, предусмотрены новые связи - коллектор второго 7 входного транзистора соединен с токовым выходом 2 устройства, причем токовый выход 2 устройства согласован со второй 9 шиной источника питания.

Схема устройства-прототипа показана на фиг.1. На фиг.2 представлена схема заявляемого устройства в соответствии с п.1 и п.2 формулы изобретения.

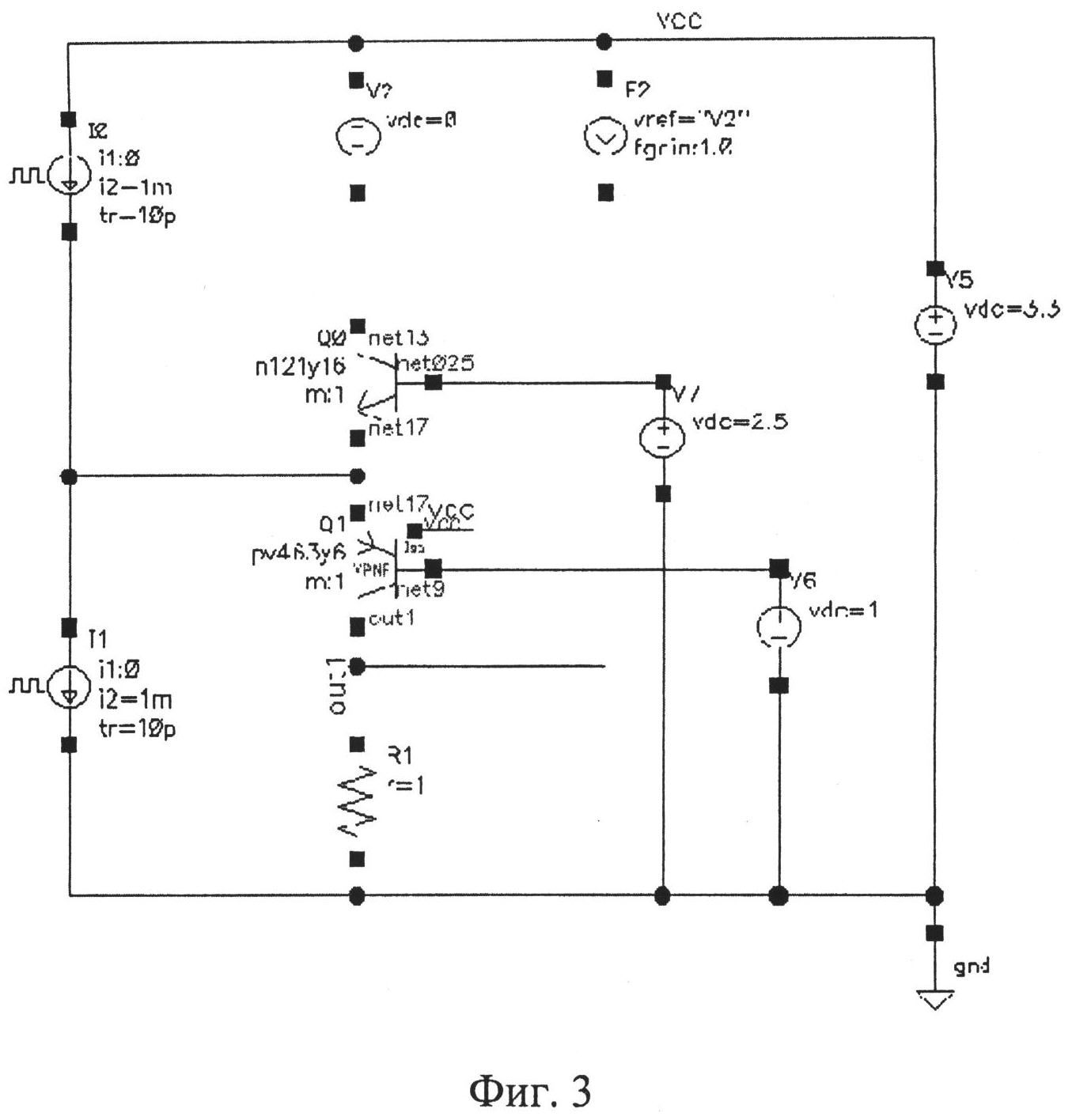

На фиг.3 показана схема заявляемого устройства фиг.2 в среде компьютерного моделирования Cadence на моделях SiGe интегральных транзисторов при неодинаковых напряжениях вспомогательных источников 4 и 8.

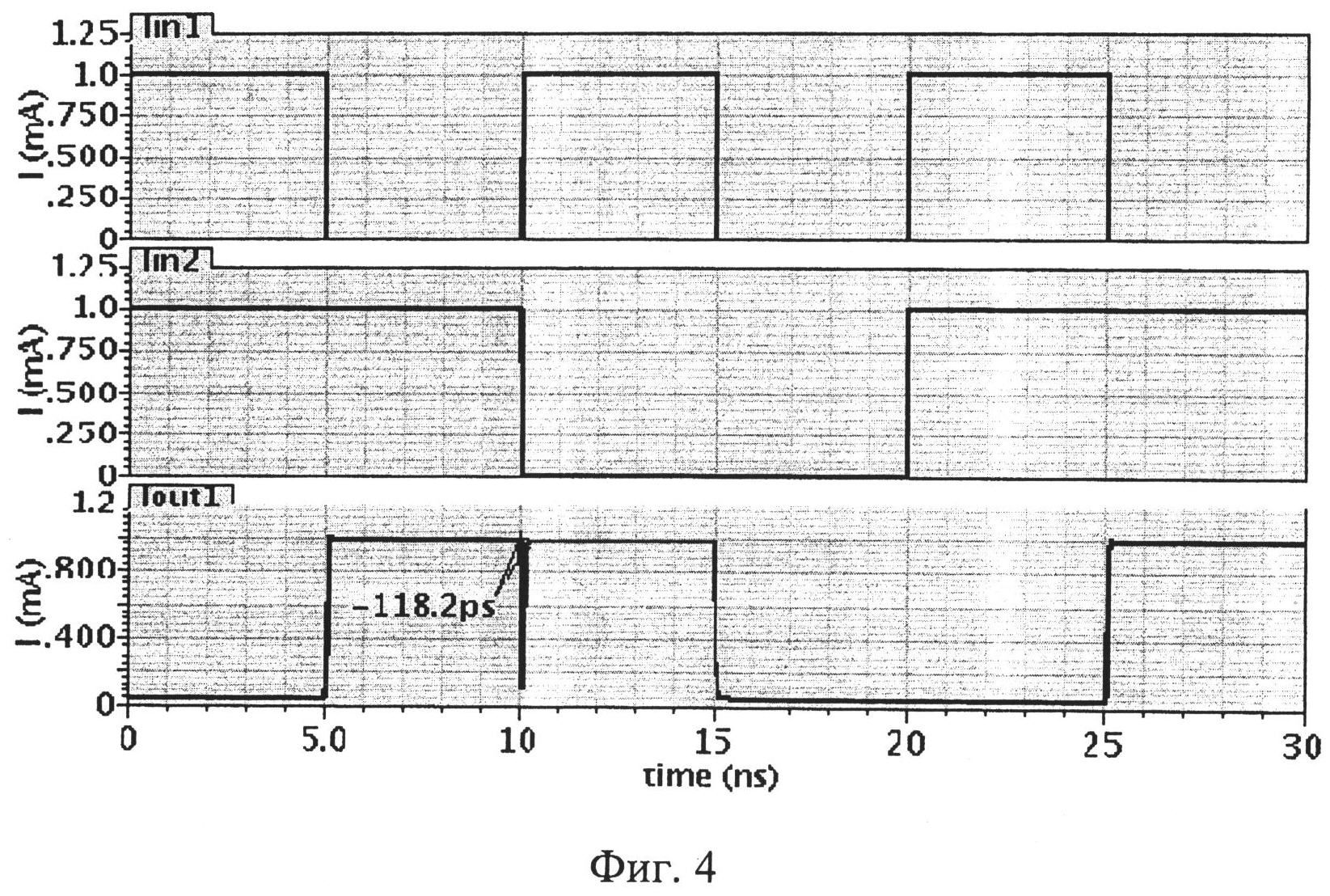

На фиг.4 приведена осциллограмма входных (I(in2), I(Iin2)) и выходных (Iout) токов устройства фиг.3.

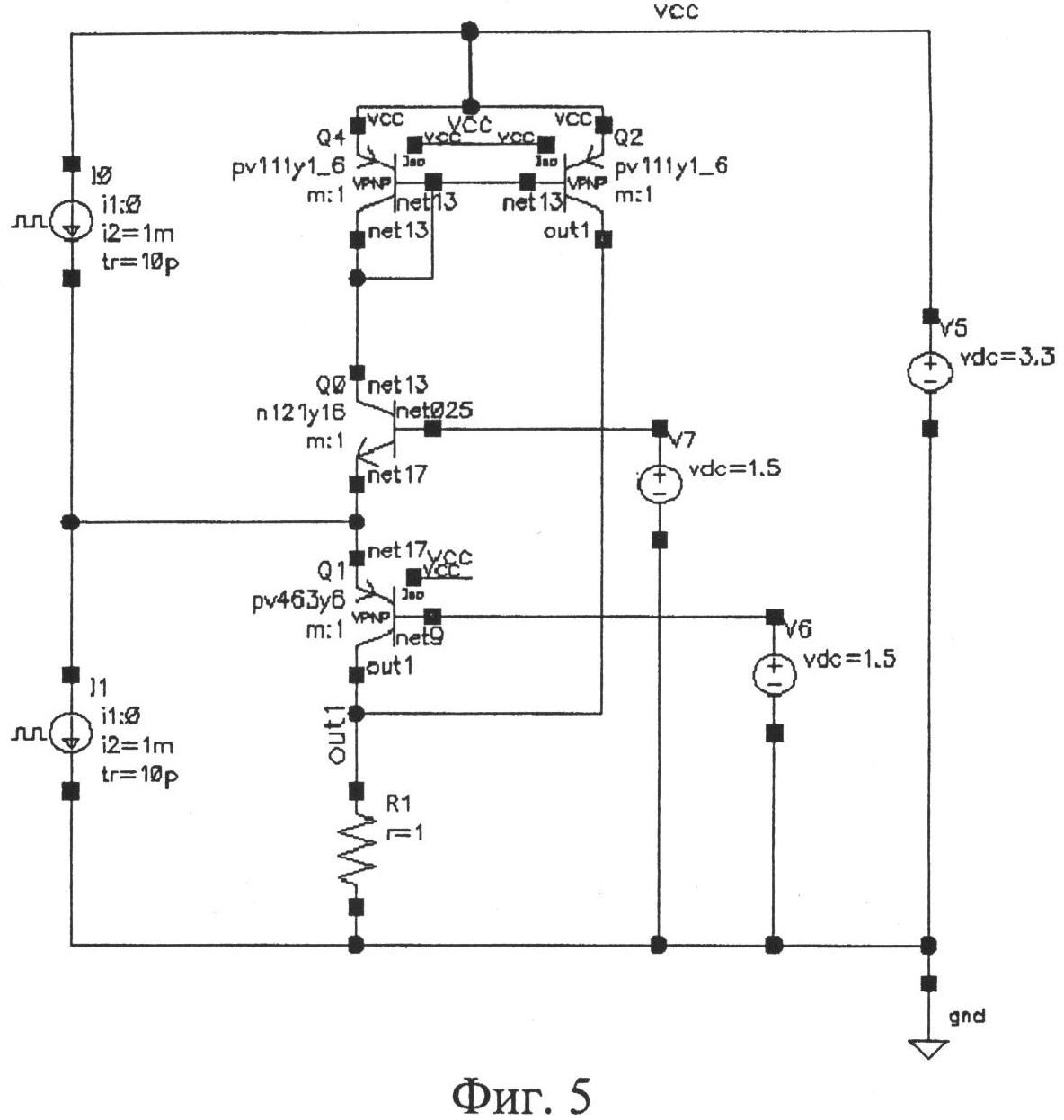

На фиг.5 приведена схема устройства фиг.3 для случая, когда напряжения вспомогательных источников 4 и 8 одинаковы, а токовое зеркало 5 реализовано на биполярных р-n-р транзисторах Q2, Q4.

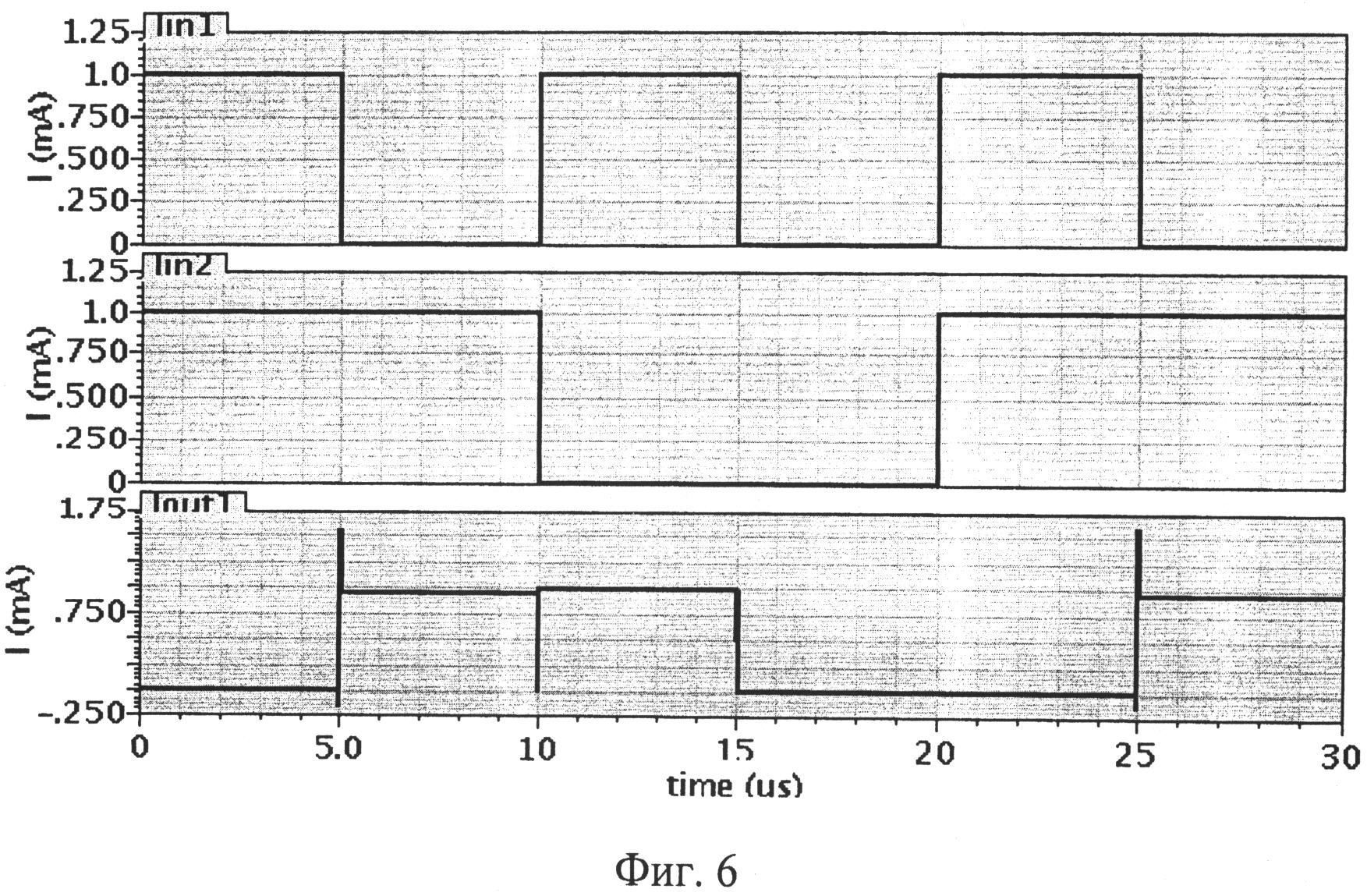

На фиг.6 показана осциллограмма входных (I(in2), I(Iin2)) и выходных (Iout) сигналов устройства фиг.5.

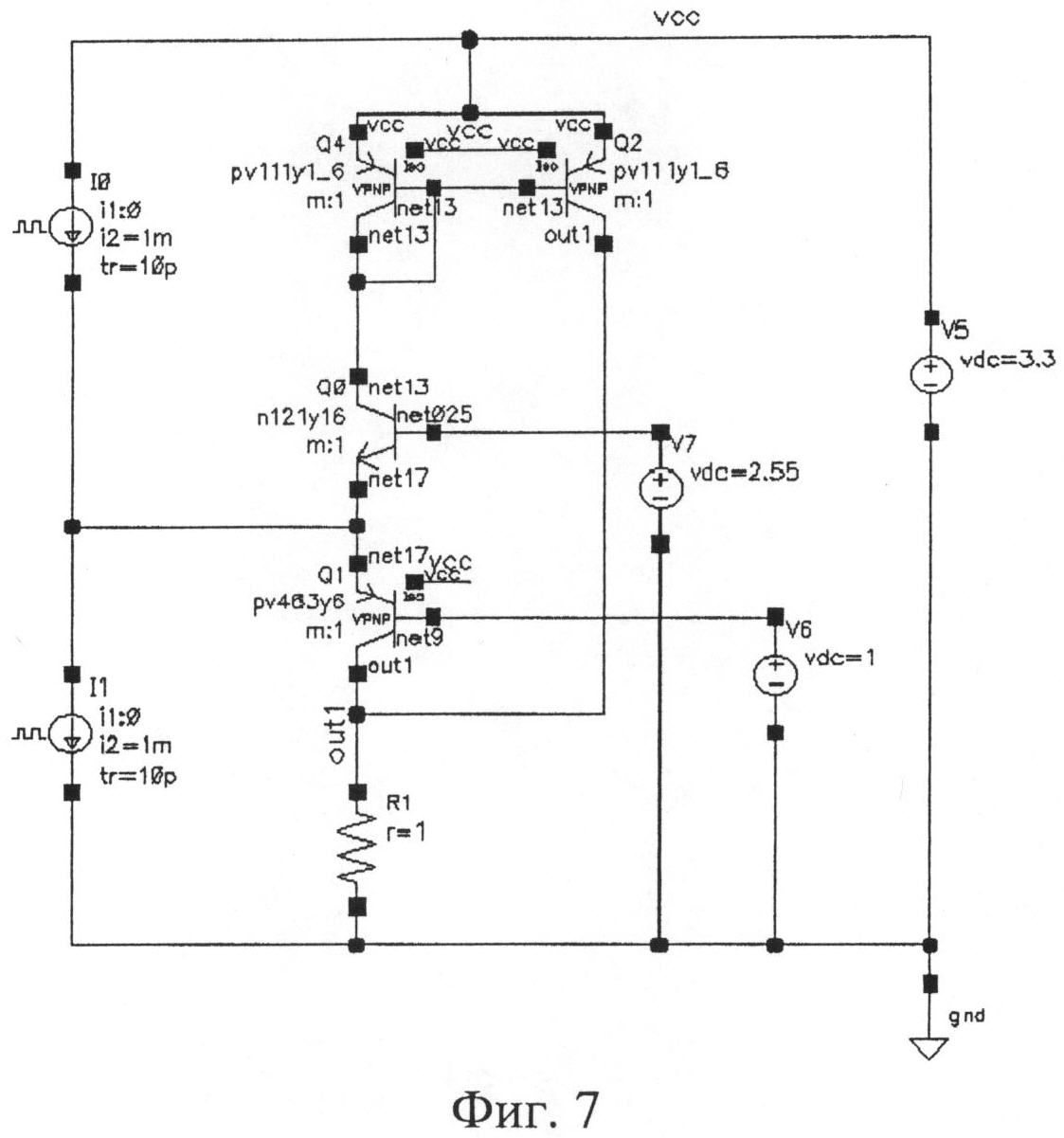

На фиг.7 представлена схема заявляемого устройства фиг.2 для случая, когда токовое зеркало 5 выполнено на транзисторах Q4 и Q2, а напряжения вспомогательных источников 4 и 8 неодинаковы.

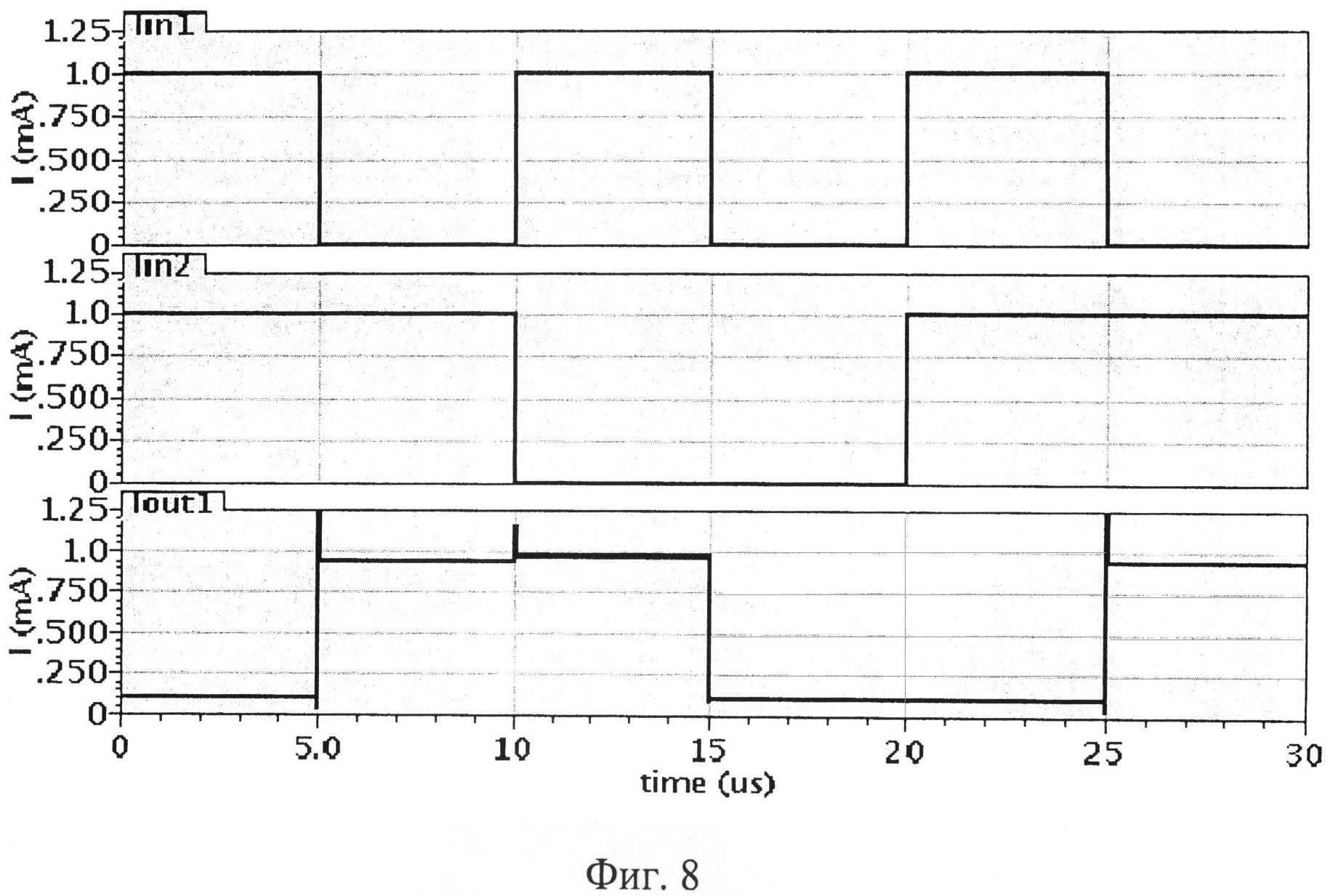

На фиг.8 приведена осциллограмма входных (I(in2), I(Iin2)) и выходных (Iout) сигналов устройства фиг.7.

Устройство для выделения модуля разности двух входных токов фиг.2 содержит токовый вход 1 и токовый выход 2, первый 3 входной транзистор, эмиттер которого соединен с токовым входом устройства 1, база подключена к первому 4 источнику вспомогательного напряжения, а коллектор соединен со входом токового зеркала 5, согласованного с первой 6 шиной источника питания, второй 7 входной транзистор, эмиттер которого соединен с токовым входом 1 устройства, а база подключена ко второму 8 источнику вспомогательного напряжения. Коллектор второго 7 входного транзистора соединен с токовым выходом 2 устройства, причем токовый выход 2 устройства согласован со второй 9 шиной источника питания. В цепь выхода 2 включается нагрузка устройства 10, например, следующий логический элемент.

На фиг.2, в соответствии с п.2 формулы изобретения, напряжения первого 4 и второго 8 источников вспомогательных напряжений незначительно отличаются друг от друга (фиг.3, фиг.7), а также могут принимать одинаковые значения (фиг.5), что сказывается на паразитных «всплесках» и «провалах» выходных токовых координат.

Рассмотрим работу предлагаемой схемы для выделения модуля разности двух входных токов фиг.2.

В отсутствие входного разностного тока  на входе 1 (Bx.i) транзисторы 3 и 7 заперты потенциалами источников вспомогательных напряжений 4 и 8 соответственно. Выходные токи коллекторов этих транзисторов отсутствуют, выходной ток токового зеркала 5 также равен нулю. В результате этого на токовом выходе 2 ток также отсутствует.

на входе 1 (Bx.i) транзисторы 3 и 7 заперты потенциалами источников вспомогательных напряжений 4 и 8 соответственно. Выходные токи коллекторов этих транзисторов отсутствуют, выходной ток токового зеркала 5 также равен нулю. В результате этого на токовом выходе 2 ток также отсутствует.

При разных по величине и противоположных по направлению токах  на токовом входе Bx.i (1) присутствует разностный ток. В зависимости от направления этого тока открывается либо транзистор 3, либо транзистор 7. При этом коллекторный ток транзистора 3 преобразуется токовым зеркалом 5 в «вытекающий» ток, который поступает на токовый выход 2. Аналогично, коллекторный ток транзистора 7 также поступает на токовый выход 2. Таким образом, на выходе схемы фиг.2 формируется ток, равный разности входных токов

на токовом входе Bx.i (1) присутствует разностный ток. В зависимости от направления этого тока открывается либо транзистор 3, либо транзистор 7. При этом коллекторный ток транзистора 3 преобразуется токовым зеркалом 5 в «вытекающий» ток, который поступает на токовый выход 2. Аналогично, коллекторный ток транзистора 7 также поступает на токовый выход 2. Таким образом, на выходе схемы фиг.2 формируется ток, равный разности входных токов  ,

,  по величине и вытекающим по направлению - независимо от направления разности этих входных токов.

по величине и вытекающим по направлению - независимо от направления разности этих входных токов.

Как видно из приведенного описания реализация модуля разности двух входных токов здесь производится формированием алгебраической суммы квантов тока и выделением определенных значений этой суммы токов. Все элементы приведенной схемы работают в режиме, предполагающем отсутствие насыщения в процессе переключений, что повышает общее быстродействие схемы. Кроме того, использование многозначного внутреннего представления сигналов повышает информативность линий связи, что уменьшает их количество. Использование стабильных значений входных квантов тока, а также определение выходного сигнала разностью этих токов обеспечивает малую зависимость параметров схемы от внешних дестабилизирующих факторов (изменение питающего напряжения, радиационное и температурное воздействия, синфазная помеха и др.).

Заявляемая схема может стать основой различных логических элементов, функционирующих в системе токовых преобразований, теория которых разработана в [9, 10].

Показанные на фиг.4, фиг.6, фиг.8 результаты моделирования подтверждают указанные свойства заявляемых схем.

Таким образом, рассмотренные схемотехнические решения устройства для выделения модуля разности двух входных токов, характеризующиеся многозначным состоянием внутренних сигналов и двоичным представлением сигнала на его токовом выходе, могут быть положены в основу вычислительных и управляющих устройств, использующих многозначную линейную алгебру, частным случаем которой является булева алгебра [9, 10].

Источники информации

1. Патент US №7.791.414

2. Патент US №6.624.701

3. Патент US №4.446.443 fig.1

4. Патент US №5.557.220 fig.3

5. Патент US №5.140.282 fig.6

6. Патент US №5.742.154 fig.1

7. Патент SU №1739476

8. Maximum rating of Voltage Feedback and Current Feedback Operational Amplifiers in Linear and Nonlinear Modes / Prokopenko N.N., Budyakov A.S., Savchenko J.M., Korneev S.V. // Proceeding of the Third International Conference on Circuits and Systems for Communications - ICCSC'06 / - Politehnica University, Bucharest, Romania: July 6-7, 2006. - pp.149-154.

9. Чернов Н.И. Основы теории логического синтеза цифровых структур над полем вещественных чисел // Монография. - Таганрог: ТРТУ, 2001. - 147 с.

10. Чернов Н.И. Линейный синтез цифровых структур АСОИУ» // Учебное пособие Таганрог. - ТРТУ, 2004 г., 118 с.