Результат интеллектуальной деятельности: СПОСОБ ИЗГОТОВЛЕНИЯ ТРАНЗИСТОРНОЙ СВЧ LDMOS СТРУКТУРЫ

Вид РИД

Изобретение

Изобретение относится к электронной полупроводниковой технике, в частности к методам изготовления мощных кремниевых СВЧ LDMOS (Lateral Diffused Metal Oxide Semiconductor) транзисторных структур и приборов в целом, и может быть использовано для создания на их основе радиоэлектронной аппаратуры нового поколения.

Известен способ изготовления фирмой «Philips Semiconductors» мощного кремниевого СВЧ LDMOS транзистора 4-го поколения типа BLF 2022-90 с диапазоном рабочих частот до 2,0…2,2 ГГц и уровнем отдаваемых в нагрузку мощностей до 90 Вт [1], выбранный в качестве аналога, включающий: создание сквозных истоковых р+-перемычек в высокоомном эпитаксиальном p--слое исходной кремниевой p-p+-подложки; выращивание подзатворного диэлектрика толщиной 480 Å на лицевой поверхности р--слоя подложки, нанесение на подзатворный диэлектрик слоя поликремния и легирование его фосфором; формирование из слоя поликремния методом фотолитографии электродов затвора элементарных ячеек в виде узких (0,82 мкм) продольных зубцов прямоугольного сечения протяженностью 330 мкм; создание в высокоомном р--слое подложки р-карманов, трехступенчатых слаболегированных n--областей стока и высоколегированных n+-областей стока и истока элементарных ячеек посредством внедрения в подложку соответственно ионов бора, фосфора и мышьяка при использовании в качестве защитной маски поликремниевых электродов затвора и слоев фоторезиста и последующего диффузионного перераспределения внедренных в подложку примесей; осаждение толстого (0,8…1,0 мкм) межслойного диэлектрика на лицевую поверхность подложки и вскрытие в нем методом фотолитографии контактных окон над поликремниевыми затворными зубцами, истоковыми p+-перемычками и высоколегированными n+-областями стока и истока элементарных ячеек; формирование металлических экранов, электродов стока, истока и шунтирующих прослоек поликремниевых затворных зубцов элементарных ячеек методом фотолитографии из трехслойного покрытия Ti(0,08 MKM)/TiW(0,14 мкм)/ Au(1,24 мкм) на лицевой поверхности подложки и общего металлического электрода истока транзисторной структуры на ее тыльной стороне.

Реализация способа-аналога в промышленном производстве из-за необходимости вскрытия узких (~0,25…0,3 мкм) протяженных (330 мкм) контактных окон в толстом одноуровневом межслойном диэлектрике над поликремниевыми затворными зубцами элементарных ячеек и последующего их шунтирования золотым покрытием (Ti/TiW/Au) требует наличия прецизионного технологического оборудования и эксклюзивных технологических процессов с субмикронными проектными нормами, которые отсутствуют у большинства возможных потенциальных разработчиков и изготовителей приборов данного класса. Это основной недостаток способа-аналога.

В качестве прототипа выбран усовершенствованный фирмой NXP способ изготовления мощных кремниевых СВЧ LDMOS транзисторов шестого и последующих поколений [2] с диапазоном рабочих частот до 3,6 ГГц, уровнем отдаваемых в нагрузку мощностей до 150 Вт, коэффициентом усиления по мощности Кур=10…14 дБ, коэффициентом полезного действия стоковой цепи ηс=48…55%, достигнутых за счет снижения минимального топологического размера транзисторной структуры по сравнению с аналогом с 0,35 мкм до 0,14 мкм, уменьшения шага элементарной транзисторной ячейки с 32,6 до 25 мкм, уменьшения величины выходной емкости, приходящейся на единицу протяженности затвора (ширины канала) в 1,6…2,0 раза и внесения в технологический маршрут аналога следующих изменений: уменьшения толщины подзатворного диэлектрика с 480 Å до 250 Å; затворных зубцов ячеек с 0,82 мкм до 0,3…0,4 мкм; шунтирования поликремниевых затворных зубцов элементарных ячеек силицидом кобальта (CoSi2) вместо золотого покрытия Ti/TiW/Au; создания экранирующих электродов транзисторных ячеек из вольфрама, а не из золотого покрытия Ti/TiW/Au;

заменой остродефицитной и дорогостоящей двухуровневой золотой металлизации на более доступную и менее дорогостоящую пятиуровневую металлизацию алюминий-медь при формировании электродов стока и истока транзисторных ячеек и общих шин стока и затвора транзисторной структуры; формирования вместо одноуровневого более толстого четырех-пятиуровневого межслойного диэлектрика на лицевой поверхности подложки.

Выполнение перечисленных выше нововведений предъявляет еще более жесткие требования по сравнению с аналогом к прецизионности используемого технологического оборудования и минимальным топологическим размерам разрабатываемой транзисторной структуры, поэтому реализация способа-прототипа в промышленном производстве для многих возможных потенциальных производителей мощных кремниевых СВЧ LDMOS транзисторов с диапазоном рабочих частот до 3,0…3,6 ГГц становится крайне проблематичной. Это основной недостаток способа-прототипа. Кроме того, выполнение в транзисторной структуре прототипа вместо многоступенчатых одноступенчатых слаболегированных n--областей стока элементарных ячеек приводит к повышенной напряженности электрического поля в стоковой части структуры и по этой причине не позволяет реализовать пробивные напряжения стокового p-n перехода свыше 65…70 В, а следовательно обеспечить возможность работы прибора при напряжениях питания по стоку свыше 28…32 В и повысить таким образом величину отдаваемой им в нагрузку мощности. Это второй серьезный недостаток способа-прототипа.

Технический результат настоящего изобретения - создание базового процесса изготовления СВЧ LDMOS структур и на их основе мощных кремниевых СВЧ LDMOS транзисторов с диапазоном рабочих частот до 3,0…3,6 ГГц на более доступном и менее дорогостоящем технологическом оборудовании, сопоставимых с современными зарубежными аналогами по основным параметрам, но способных работать по сравнению с ними при более высоких напряжениях питания по стоку.

Технический результат достигается тем, что:

в известном способе изготовления транзисторной СВЧ LDMOS структуры, включающем создание сквозных истоковых p+-перемычек элементарных транзисторных ячеек в высокоомном эпитаксиальном p--слое исходной кремниевой р-p++-подложки, выращивание подзатворного диэлектрика на лицевой поверхности подложки, нанесение на подзатворный диэлектрик слоя поликремния и легирование его фосфором, формирование из слоя поликремния методом фотолитографии электродов затвора элементарных ячеек в виде узких продольных зубцов прямоугольного сечения, создание в высокоомном р--слое подложки р-карманов, многоступенчатых слаболегированных n--областей стока и высоколегированных n+-областей стока и истока элементарных ячеек посредством внедрения в подложку ионов бора, фосфора и мышьяка при использовании в качестве защитной маски поликремниевых электродов затвора и слоев фоторезиста и последующего диффузионного перераспределения внедренных в подложку примесей, поэтапное осаждение многоуровневого межслойного диэлектрика на лицевую поверхность подложки и поэтапное вскрытие в нем методом фотолитографии контактных окон над высоколегированными p+-перемычками и истоковыми n+-областями, поликремниевыми электродами затвора и высоколегированными n+-областями стока элементарных ячеек, образование силицидов и полицидов тугоплавких металлов на кремнии и поликремнии во вскрытых окнах, формирование металлических многоуровневых электродов стока и истока, заземленных на исток экранирующих электродов и металлических шин, шунтирующих полицидные затворные зубцы транзисторных ячеек на лицевой поверхности подложки и общего металлического электрода истока транзисторной структуры на ее тыльной стороне, нанесенный на подзатворный диэлектрик поликремний покрывают тугоплавким металлом, высокотемпературным отжигом кремниевой подложки в вакууме, водороде, азоте или какой-либо другой среде формируют полицид тугоплавкого металла на поверхности поликремния, наносят на лицевую сторону подложки защитный слои фоторезиста, методом фотолитографии вскрывают окна в защитном слое фоторезиста, полициде тугоплавкого металла, поликремнии и подзатворном диэлектрике над истоковыми р+-перемычками и прилегающими к ним участками высокоомного p--слоя подложки и формируют таким образом вначале только истоковые боковые грани полицидных электродов затвора транзисторных ячеек, затем через вскрытые окна внедряют в подложку ионы бора, удаляют фоторезист с лицевой поверхности подложки и последующей диффузионной разгонкой внедренной в подложку примеси создают р-карманы элементарных ячеек, далее методом фотолитографии удаляют полицид тугоплавкого металла и поликремний с лицевой поверхности подложки в промежутке между р--карманами транзисторных ячеек и формируют стоковые боковые грани полицидных затворных зубцов и полицидные электроды затвора элементарных ячеек в целом, потом в высокоомном эпитаксиальном р--слое подложки у истоковых и в промежутке между стоковыми боковыми гранями полицидных электродов затвора создают высоколегированные истоковые n+-области и соответственно высоколегированные и многоступенчатые слаболегированные n-области стока элементарных ячеек, после этого в межслойном диэлектрике формируют металлические экранирующие электроды транзисторных ячеек, а полицидные затворные зубцы ячеек точечно шунтируют общими металлическими шинами затвора, сформированными на верхней поверхности многоуровневого межслойного диэлектрика над истоковыми р+-перемычками элементарных ячеек.

Сопоставительный анализ с прототипом показывает, что заявляемый способ отличается: принципиально новым подходом к созданию самосовмещенного затворного узла транзисторной LDMOS структуры посредством замены традиционного совместного последовательным раздельным формированием истоковых и стоковых боковых граней полицидных электродов затвора элементарных транзисторных ячеек; созданием р-карманов после формирования только истоковых боковых граней полицидных электродов затвора транзисторных ячеек, а не электродов затвора в целом; формирование полицида тугоплавкого металла посредством нанесения тугоплавкого металла на легированный фосфором поликремний и последующего высокотемпературного отжига кремниевой подложки с тугоплавким металлом в определенной среде на регламентированном формулой изобретения этапе изготовления транзисторной структуры; формированием затворных зубцов элементарных ячеек методом фотолитографии непосредственно из поликремния, прошунтированного полицидом тугоплавкого металла, а не отдельно из поликремния и последующего шунтирования уже сформированных затворных зубцов элементарных ячеек полицидом тугоплавкого металла, как это имеет место в способе-прототипе; точечным шунтированием продольных полицидных затворных зубцов элементарных ячеек общими металлическими шинами затвора, сформированными в определенном месте транзисторной структуры; формированием многоступенчатых слаболегированных n--областей стока элементарных ячеек вместо одноступенчатых в способе-прототипе. Таким образом, заявляемый способ изготовления транзисторной СВЧ LDMOS структуры отвечает критерию изобретения «новизна».

Создание в заявляемом способе затворного узла транзисторной СВЧ LDMOS структуры последовательным раздельным формированием истоковых и стоковых боковых граней полицидных электродов затвора элементарных транзисторных ячеек вместо традиционного совместного в прототипе и аналоге, позволяет:

- использовать одни и те же окна, вскрытые в защитном слое фоторезиста, полициде тугоплавкого металла, поликремнии и подзатворном диэлектрике над истоковыми p+-перемычками и прилегающими к ним участками высокоомного эпитаксиального р--слоя подложки для формирования истоковых боковых граней полицидных затворных зубцов элементарных ячеек и одновременного внедрения через них в подложку ионов бора для создания р-карманов элементарных ячеек;

- исключить дополнительную фоторезистивную защитную маску при формировании р-карманов элементарных транзисторных ячеек, как это имеет место в прототипе и аналоге;

- обычным диффузионным перераспределением примеси бора в р-карманах при повышенной температуре реализовать полностью идентичную прототипу малую (0,3…0,4 мкм) длину индуцированного n-канала элементарных ячеек, необходимую для создания мощных кремниевых СВЧ LDMOS транзисторов с диапазоном рабочих частот до 3,0…3,6 ГГц;

посредством вытравливания методом фотолитографии полицида тугоплавкого металла и поликремния в промежутке между р-карманами элементарных транзисторных ячеек сформировать стоковые боковые грани и полицидные затворные зубцы ячеек в целом, ширина которых лишь незначительно (на величину погрешности совмещения) превышает длину индуцированного n-канала транзисторных ячеек;

- изготовить практически идентичную прототипу транзисторную СВЧ LDMOS структуру с самосовмещенным затворным узлом на более доступном и менее дорогостоящем технологическом оборудовании при в 5,0…6,0 раз большем по сравнению с прототипом минимальном топологическом размере транзисторной структуры.

Формирование в заявляемом способе полицидных электродов затвора элементарных ячеек посредством нанесения тугоплавкого металла и последующего высокотемпературного отжига кремниевой подложки с тугоплавким металлом в вакууме, водороде, азоте или какой-либо другой среде, позволяет:

- образовать слой полицида тугоплавкого металла на всей поверхности легированного фосфором поликремния до создания затворных зубцов элементарных ячеек;

- сформировать затворные зубцы элементарных транзисторных ячеек методом фотолитографии непосредственно из поликремния, покрытого полицидом тугоплавкого металла;

- избежать необходимость во вскрытии контактных окон в межслойном диэлектрике над узкими поликремниевыми затворными зубцами транзисторных ячеек, как это имеет место в прототипе и аналоге при шунтировании поликремниевых электродов затвора полицидами тугоплавких металлов.

Точечное шунтирование полицидных продольных затворных зубцов элементарных ячеек в заявляемом способе общей металлической шиной затвора, размещенной на верхней поверхности многоуровнего межслойного диэлектрика над истоковыми p+-перемычками элементарных ячеек, позволяет в зависимости от конкретного значения толщины подзатворного диэлектрика, удельного поверхностного сопротивления затворных зубцов и максимальной рабочей частоты разрабатываемой транзисторной структуры уменьшить шаг элементарной ячейки, уменьшить количество шунтирующих проводников, соединяющих продольные отрезки затвора с общей металлической шиной затвора в каждом затворном зубце и увеличить при этом общую протяженность затворных зубцов до 340…500 мкм и, как результат, реализовать более плотноупакованную транзисторную LDMOS структуру с меньшей площадью и улучшенными энергетическими параметрами.

Формирование в заявляемом способе многоступенчатых слаболегированных n--областей стока элементарных ячеек вместо одноступенчатых в способе-прототипе, позволяет:

- обеспечить более однородное по сравнению с прототипом распределение электрического поля в многоступенчатых слаболегированных n--областях стока элементарных ячеек с пониженной величиной его напряженности на краях n--ступеней, непосредственно примыкающих к высоколегированной n+-области стока и р-карману ячеек;

- минимизировать вероятность инжекции горячих носителей в подзатворный диэлектрик и повысить тем самым стабильность параметров и эксплуатационную надежность прибора;

- реализовать пробивные напряжения стокового p-n перехода на уровне 75…80 В и обеспечить таким образом возможность работы транзистора при напряжениях питания по стоку свыше 28…32 В, а следовательно при прочих равных условиях повысить величину отдаваемой им в нагрузку мощности.

В предлагаемом изобретении новая совокупность, предназначенность и последовательность выполнения технологических операций позволяет в отличие от способа-прототипа создать на более доступном и менее дорогостоящем технологическом оборудовании мощные кремниевые СВЧ LDMOS транзисторы с диапазоном рабочих частот до 3,0…3,6 ГГц, работающие при напряжениях питания по стоку свыше 28…32 В с улучшенными энергетическими параметрами, то-есть проявляет новое техническое свойство. Следовательно, заявляемый способ соответствует критерию «изобретательский уровень».

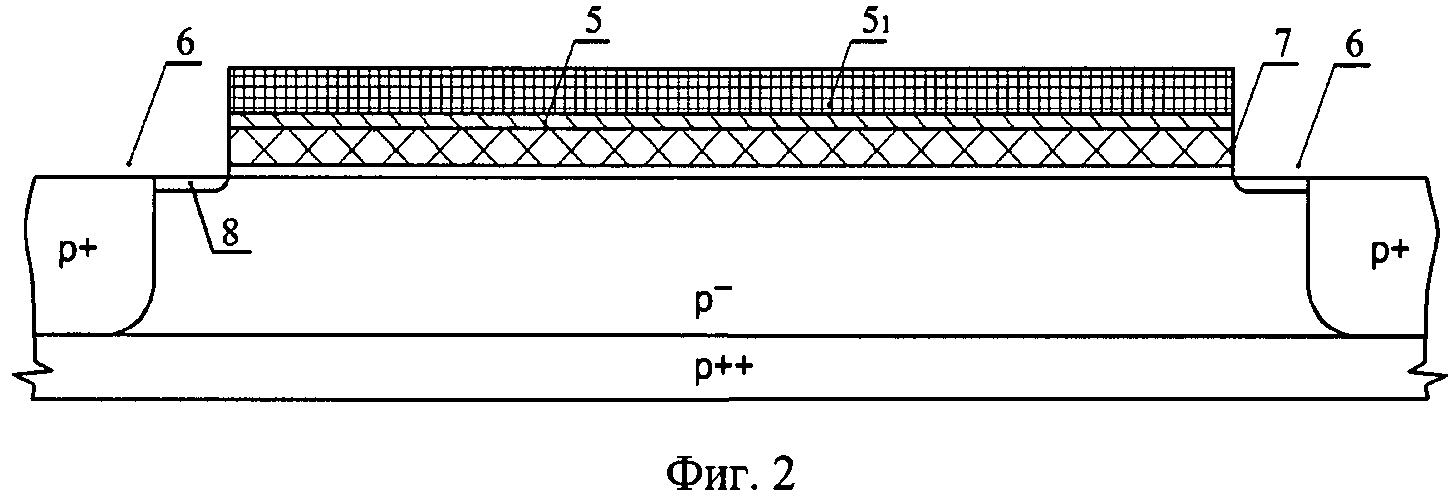

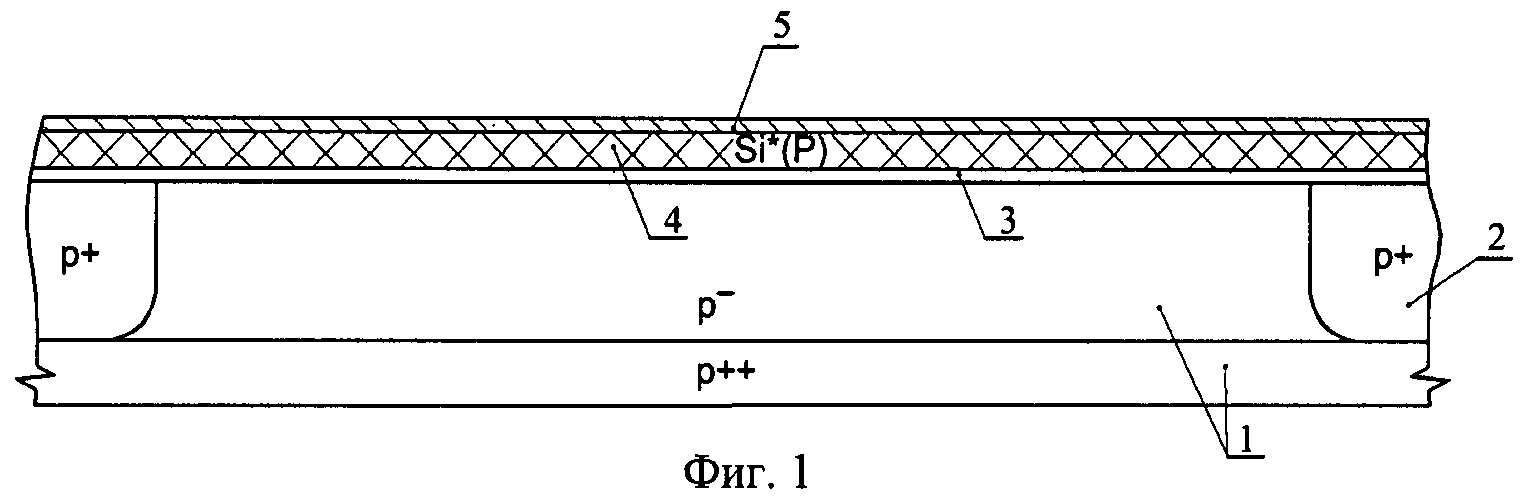

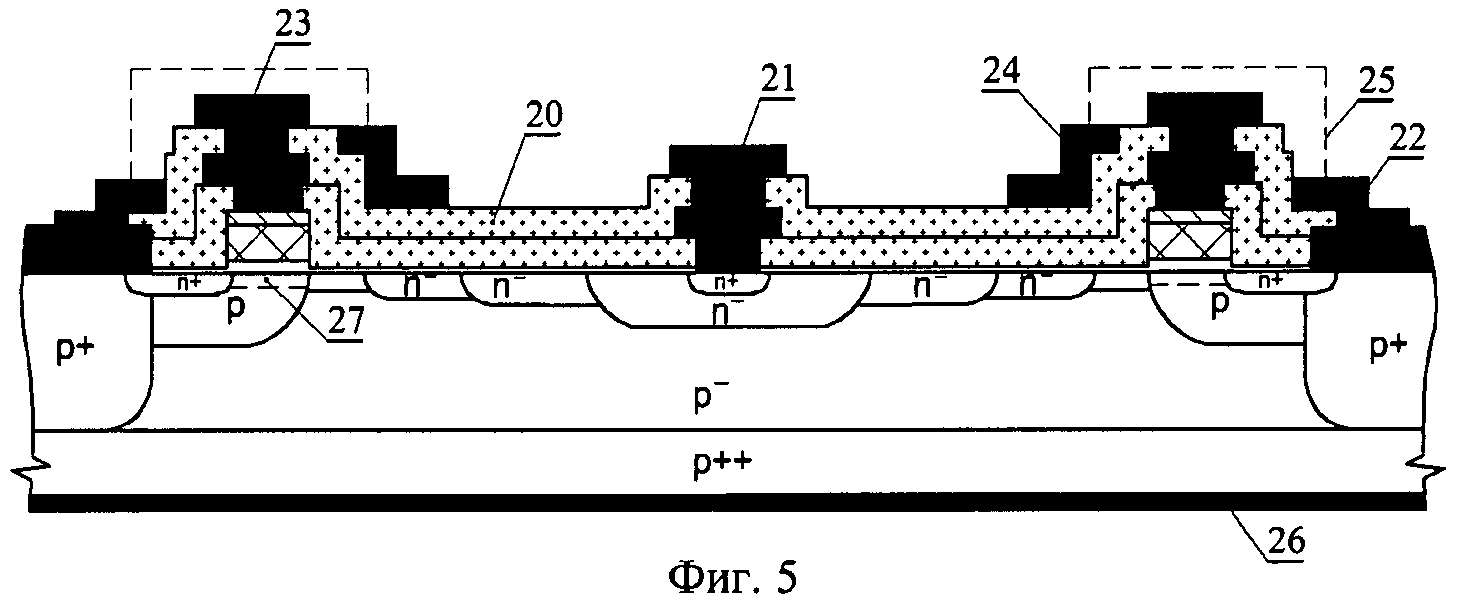

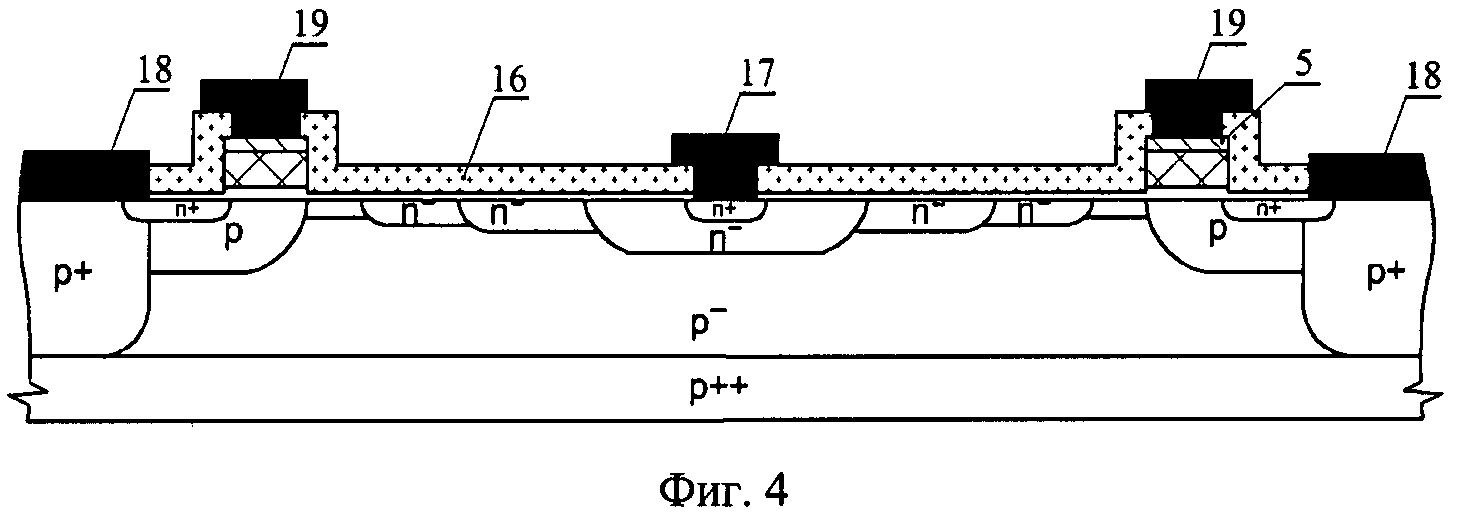

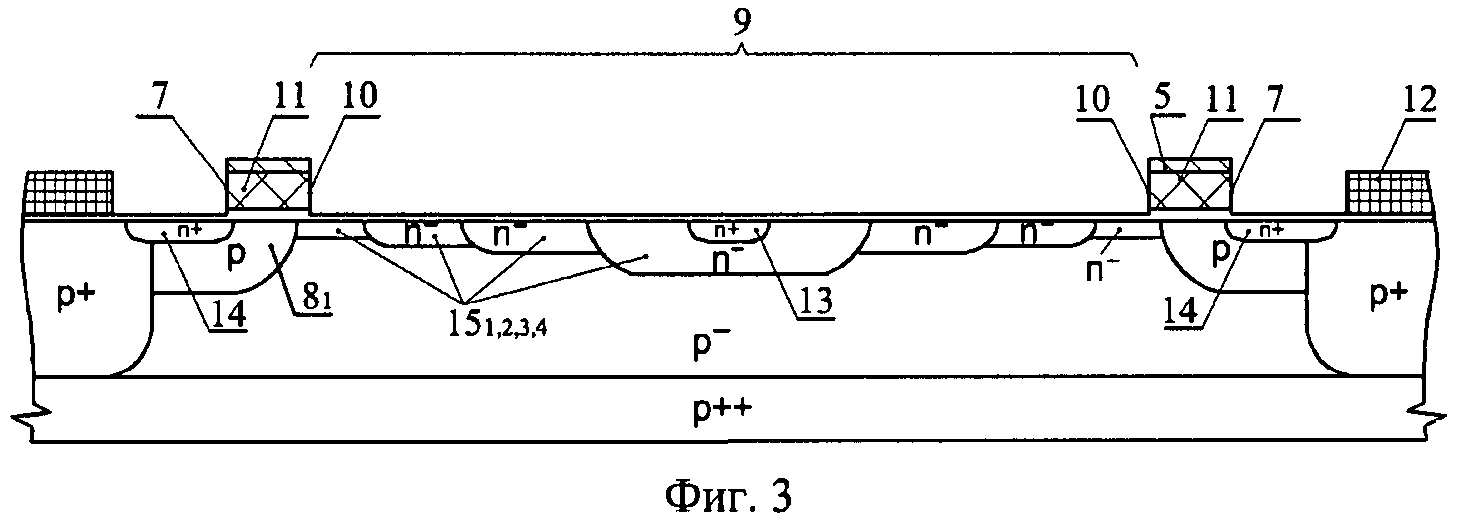

На фигурах 1…5 изображены основные этапы изготовления транзисторной СВЧ LDMOS структуры согласно заявляемому способу, где введены следующие обозначения:

1 - исходная кремниевая p-p++-подложка с высокоомным эпитаксиальным и высоколегированным слоями р-типа проводимости;

2 - сквозные истоковые р+-перемычки элементарных транзисторных ячеек в высокоомном эпитаксиальном р--слое подложки;

3 - подзатворный диэлектрик;

4 - слой поликремния, легированного фосфором на поверхности подзатворного диэлектрика;

5 - полицид тугоплавкого металла, сформированный на поверхности порликремния;

51 - защитный слой фоторезиста;

6 - окна, вскрытые в защитном слое фоторезиста, полициде тугоплавкого металла, поликремнии и подзатворном диэлектрике над истоковыми p+-перемычками и прилегающими к ним участками высокоомного р--слоя подложки элементарных транзисторных ячеек;

7 - истоковые боковые грани полицидных электродов затвора элементарных транзисторных ячеек;

8 - ионы бора, внедренные в подложку через окна (6);

81 - р-карманы элементарных транзисторных ячеек;

9 - удаляемые методом фотолитографии участки полицида тугоплавкого металла и поликремния в промежутке между р-карманами элементарных транзисторных ячеек;

10 - стоковые боковые грани полицидных электродов затвора элементарных транзисторных ячеек;

11 - полицидные затворные зубцы элементарных транзисторных ячеек;

12 - защитный слой фоторезиста;

13 - высоколегированные n+-области стока элементарных транзисторных ячеек;

14 - высоколегированные n+-области истока элементарных транзисторных ячеек;

151,2,3,4 - многоступенчаые слаболегированные n--области стока элементарных транзисторных ячеек;

16 - первый уровень межслойного диэлектрика;

17, 18 - первый уровень металлических электродов стока и истока элементарных транзисторных ячеек;

19 - первый уровень шунтирующих металлических прослоек (шин) полицидных затворных зубцов элементарных транзисторных ячеек;

20 - второй уровень межслойного диэлектрика;

21, 22 - второй уровень металлических электродов стока и истока элементарных транзисторных ячеек;

23 - второй уровень шунтирующих металлических прослоек (шин) полицидных затворных зубцов элементарных транзисторных ячеек;

24 - металлические экранирующие электроды элементарных транзисторных ячеек;

25 - металлические проводники, соединяющие экранирующие электроды с электродами истока (22) элементарных транзисторных ячеек;

26 - общий металлический электрод истока транзисторной структуры;

27 - индуцированный n-канал, формируемый на прилегающих к подзатворному диэлектрику торцах p-карманов элементарных ячеек при приложении положительного потенциала к электроду затвора транзисторной структуры.

Пример.

На основе заявляемого способа были изготовлены образцы мощных кремниевых n-канальных транзисторных СВЧ LDMOS структур (кристаллов) размером 4,2 мм х 1,0 мм с длиной и суммарной протяженностью (шириной) индуцированного n-канала элементарных ячеек соответственно Lk=0,35…0,38 мкм и Wk=97 мм, с четырехступенчатой слаболегированной n--областью стока ячеек и шагом структуры 26 мкм (в данном случае под шагом структуры подразумевается расстояние между центрами высоколегированных n+-областей стока или истока транзисторных ячеек), рассчитанных на работу в диапазоне частот до 3,0…3,6 ГГц при напряжениях питания по стоку более 28…32 В. Исходным материалом для изготовления транзисторных структур служили кремниевые p-p++-подложки (1), ориентированные по плоскости (100), с верхним высокоомным эпитаксиальным p--слоем толщиной 7,0…7,5 мкм и удельным сопротивлением 10…12 Ом·см и нижним высоколегированным р++-слоем с удельным сопротивлением 0,005 Ом·см.

Способ осуществляют следующим образом.

1. Внедрением ионов бора в подложку с энергией 80 кэВ и дозой 500 мкКл/см2 и последующим диффузионным перераспределением внедренной примеси при температуре Т=1100°С в среде азота формируют сквозные истоковые p+-перемычки (2) элементарных ячеек в высокоомном эпитаксиальным р--слое подложки (1) - фиг.1.

2. Пирогенным окислением кремния при Т=850°С выращивают на поверхности высокоомного эпитаксиального р--слоя подложки подзатворный диэлектрик (3) толщиной 800 Å, наносят на подзатворный диэлектрик слой поликремния (4) толщиной 0,35…0,4 мкм, легируют поликремний фосфором, последовательно осаждают на поликремний слой титана и нитрида титана толщиной 0,25…0,3 мкм каждый, высокотемпературным (Т=900°С) отжигом кремниевой подложки в среде азота и водорода формируют полицид титана (5) на поверхности поликремния (4) - фиг.1.

3. Наносят на лицевую сторону подложки (1) защитный слой фоторезиста (51), методом фотолитографии вскрывают в защитном слое фоторезиста (51), полициде титана (5), поликремнии (4) и подзатворном диэлектрике (3) окна (6) над истоковыми p+-перемычками (2) и прилегающими к ним участками высокоомного эпитаксиального р--слоя подложки (1) и формируют таким образом истоковые боковые грани (7) полицидных электродов затвора элементарных транзисторных ячеек - фиг.2.

4. Внедряют в высокоомный p--слой подложки (1) через окна (6) ионы бора (8) с энергией 40 кэВ и дозой 3,0…5,0 мкКл/см2, удаляют защитный слой фоторезиста (51) с лицевой поверхности подложки и последующим диффузионным перераспределением внедренной в подложку примеси бора при Т=1000°С в среде азота формируют р-карманы (81) элементарных транзисторных ячеек - фиг.2, 3.

5. Методом фотолитографии удаляют полицид титана (5), поликремний (4) и частично (до толщины 100…300 Å) подзатворный диэлектрик (3) в промежутке (9) между р-карманами (81) элементарных ячеек и формируют таким образом стоковые боковые грани (10) и, как результат, полицидные затворные зубцы (11) транзисторных ячеек в целом шириной 0,4…0,45 мкм и протяженностью 340 мкм с расстоянием между соседними затворными зубцами 6,4 мкм (шаг структуры при этом составлял приблизительно 26 мкм) - фиг.3.

6. Последовательным нанесением на лицевую сторону подложки нескольких защитных слоев фоторезиста, вскрытием методом фотолитографии в каждом из них стоковых и истоковых окон, внедрением в подложку через вскрытые окна ионов мышьяка и фосфора с определенными энергиями и дозами и последующей совместной диффузионной разгонкой внедренных в подложку примесей при повышенной (900…1000°С) температуре в среде азота создают в высокоомном р--слое подложки высоколегированные n+-области стока (13), истока (14) и 4-ступенчатые слаболегированные n--области стока (151,2,3,4) элементарных транзисторных ячеек - фиг.3 (на чертеже показан защитный слой фоторезиста (12), используемый при внедрении ионов мышьяка в высоколегированные n+-области стока и истока элементарных ячеек).

7. Формируют первый уровень межслойного диэлектрика (16) из предварительно нанесенного на лицевую сторону подложки слоя борофосфорносиликатного стекла, в котором методом фотолитографии вскрывают контактные окна над высоколегированными n+-областями стока и истока, истоковыми p+-перемычками и полицидными затворными зубцами элементарных ячеек, наносят на межслойный диэлектрик слой алюминия с добавками меди и кремния толщиной 1,5…2,5 мкм и создают из него методом фотолитографии первый уровень металлических электродов стока (17), истока (18) и шунтирующих прослоек (шин) полицидных затворных зубцов (19) элементарных транзисторных ячеек - фиг.4.

8. Наносят на лицевую сторону подложки второй слой борофосфорно-силикатного стекла (20), в котором методом фотолитографии вскрывают контактные окна над первым уровнем металлических электродов стока, истока и шунтирующих шин полицидных затворных зубцов элементарных ячеек, наносят на лицевую сторону подложки второй слой алюминия с добавками меди и кремния толщиной 1,5…3,0 мкм и создают из него методом фотолитографии второй уровень металлических электродов стока (21), истока (22) и шунтирующих шин полицидных затворных зубцов (23) транзисторных ячеек, а также экранирующие электроды ячеек (24), соединенными с электродами истока (22) металлическими проводниками (25). Общий металлический электрод истока транзисторной структуры (26) на тыльной стороне подложки создавался при напайке кристалла на теплоотводящую поверхность корпуса с помощью золотой прокладки, а индуцированный n-канал (27) образовывался на торцах p-карманов (81), прилегающих к подзатворному диэлектрику (3) при приложении положительного напряжения к электроду затвора транзисторной структуры - фиг.5.

В изготовленных по заявляемому способу транзисторных структурах (кристаллах) усредненное расстояние между истоковыми и стоковыми боковыми гранями затворных зубцов соседних ячеек и усредненная длина индуцированного n-канала элементарных ячеек составили соответственно 7,15 мкм, 6,4 мкм и 0,38 мкм. Кристаллы изготавливались на обычном фотолитографическом оборудовании с минимальными проектными нормами 0,8…1,0 мкм, вместо 0,14 мкм в прототипе. Выход годных кристаллов на пластине составил около 50%. Годные кристаллы, смонтированные в металлокерамическом корпусе типа КТ-25 без бериллиевой керамики имели пробивное напряжение стокового p-n перехода Uс.проб=75…78 В и при напряжении питания по стоку Uс.проб=36 В в режиме класса АВ, длительности импульса tp=300 мкс, скважности Q=10, на частоте 3,1 ГГц отдавали в нагрузку мощность Pвых=40…43 Вт при коэффициенте усиления по мощности Кур=10…13 дБ и коэффициенте полезного действия стоковой цепи ηс=40…45%.

Сопоставляя приведенные параметры с аналогичными параметрами прототипа и других известных зарубежных мощных кремниевых СВЧ LDMOS транзисторов, имеющих приблизительно такие же конструктивные и электрофизические параметры базового кристалла и рассчитанных на тот же диапазон рабочих частот (3,0…3,6 ГГц) и отдаваемых в нагрузку импульсных мощностей (10…120 Вт), можно сделать следующие выводы:

1. Заявляемый способ позволяет создавать мощные кремниевые СВЧ LDMOS транзисторы, сопоставимые с современными зарубежными аналогами по основным электрическим параметрам (Pвых, Кур, ηс), но с более высокими (75…78 В) по сравнению с ними пробивными напряжениями стокового p-n перехода и по этой причине способными работать при напряжениях питания по стоку Uс.пит≥36 В вместо Uс.пит=28…32 В у прототипа и аналогов (BLF6G38-10, BLF6G3135-20, BLF6G38-25, BLS6G3135-120 фирмы NXP, MRF7S35015HSR3, MRF7S35120HSR3 фирмы Freescale Semiconductors, ILD3135M30, ILD3135EL20 фирмы Integra Technologies и других).

2. Заявляемый способ позволяет существенно упростить технологический процесс изготовления мощных кремниевых СВЧ LDMOS транзисторов и на более доступном и менее дорогостоящем технологическом оборудовании. обеспечить высокий процент выхода годных структур на пластине, увеличить номенклатуру выпускаемых изделий и снизить себестоимость их изготовления.

Технико-экономическая эффективность предполагаемого способа состоит в возможности создания и организации устойчивого рентабельного промышленного выпуска мощных кремниевых СВЧ LDMOS транзисторов S-диапазона с повышенным напряжением питания по стоку, сопоставимых с современными зарубежными аналогами по энергетическим параметрам и конструирования на их основе радиоэлектронной аппаратуры, отвечающей современным и перспективным требованиями по тактико-техническим характеристикам, энергопотреблению, массогабаритным показателям, надежности и сроку службы.

Источникии информации

1. «Philips BLF2022-90 power MOSFET structural analysis». 3685 Richmond Road, Suite 500, Ottawa, ONK2H587, Canada, June 17, 2004 (аналог).

2. S.J.C.H.Theeuwen, H.Mollee «LDMOS Transistors in Power Microwave Applications», NXP Semiconductors, Gerstweg, 2,6534AE, The Netherlands steven, theeuwen@nxp.com, hans.mollee@nxp.com (прототип).

Способ изготовления транзисторной СВЧ LDMOS структуры, включающий создание сквозных истоковых р-перемычек элементарных транзисторных ячеек в высокоомном эпитаксиальном p-слое исходной кремниевой pp-подложки, выращивание подзатворного диэлектрика на лицевой поверхности подложки, нанесение на подзатворный диэлектрик слоя поликремния и легирование его фосфором, формирование из слоя поликремния методом фотолитографии электродов затвора элементарных ячеек в виде узких продольных зубцов прямоугольного сечения, создание в высокоомном p-слое подложки р-карманов, многоступенчатых слаболегированных n-областей стока и высоколегированных n-областей стока и истока элементарных ячеек посредством внедрения в подложку ионов бора, фосфора и мышьяка при использовании в качестве защитной маски поликремниевых электродов затвора и слоев фоторезиста и последующего диффузионного перераспределения внедренных в подложку примесей, поэтапное осаждение многоуровневого межслойного диэлектрика на лицевую поверхность подложки и поэтапное вскрытие в нем методом фотолитографии контактных окон над высоколегированными p-перемычками и истоковыми n-областями, поликремниевыми электродами затвора и высоколегированными n-областями стока элементарных ячеек, образование силицидов и полицидов тугоплавких металлов на кремнии и поликремнии во вскрытых окнах, формирование металлических многоуровневых электродов стока и истока, заземленных на исток экранирующих электродов и металлических шин, шунтирующих полицидные затворные зубцы транзисторных ячеек на лицевой поверхности подложки и общего металлического электрода истока транзисторной структуры на ее тыльной стороне, отличающийся тем, что нанесенный на подзатворный диэлектрик поликремний покрывают тугоплавким металлом, высокотемпературным отжигом кремниевой подложки формируют полицид тугоплавкого металла на поверхности поликремния, наносят на лицевую сторону подложки защитный слой фоторезиста, методом фотолитографии вскрывают окна в защитном слое фоторезиста, полициде тугоплавкого металла, поликремнии и подзатворном диэлектрике над истоковыми р-перемычками и прилегающими к ним участками высокоомного р-слоя подложки и формируют таким образом вначале только истоковые боковые грани полицидных электродов затвора транзисторных ячеек, затем через вскрытые окна внедряют в подложку ионы бора, удаляют фоторезист с лицевой поверхности подложки и последующей диффузионной разгонкой внедренной в подложку примеси создают р-карманы элементарных ячеек, далее методом фотолитографии удаляют полицид тугоплавкого металла и поликремний с лицевой поверхности подложки в промежутке между р-карманами транзисторных ячеек и формируют стоковые боковые грани полицидных затворных зубцов и полицидные электроды затвора элементарных ячеек в целом, потом в высокоомном эпитаксиальном p-слое подложки у истоковых и в промежутке между стоковыми боковыми гранями полицидных электродов затвора создают высоколегированные истоковые n-области и соответственно высоколегированные и многоступенчатые слаболегированные n-области стока элементарных ячеек, после этого в межслойном диэлектрике формируют металлические экранирующие электроды транзисторных ячеек, а полицидные затворные зубцы ячеек точечно шунтируют общими металлическими шинами затвора, сформированными на верхней поверхности многоуровневого межслойного диэлектрика над истоковыми p-перемычками элементарных ячеек.