Результат интеллектуальной деятельности: Способ сравнения данных в ячейке ассоциативного запоминающего устройства и модуль сравнения данных в ячейке ассоциативного запоминающего устройства

Вид РИД

Изобретение

Изобретение относится к области вычислительной цифровой техники, а именно к вычислительным системам на основе микропроцессоров с ассоциативным запоминающим устройством (АЗУ).

Известен способ сравнения данных, хранящихся в ячейке АЗУ, с внешними данными, включающий разряд линии совпадения до низкого логического уровня через один р-канальный МОП транзистор, который обеспечивает протекание тока между линией совпадения и шиной земли АЗУ. Данный способ осуществляется устройством сравнения, содержащим два n-канальных МОП транзистора, стоки которых подключены к затвору указанного транзистора, затворы - к узлам хранения прямого и инверсного бита данных в ячейке памяти, а истоки - к парафазной шине внешних данных (патент US №6,181,591 кл. G11C 15/00, опублик. 2001 г.). Также общеизвестен способ, рассматриваемый в упомянутом патенте в качестве предшествующего, в котором разряд линии совпадения осуществляется через n-канальный МОП транзистор.

Недостатком первого описанного способа является то, что линия совпадения разряжается не в точности до напряжения шины земли, принимаемого обычно за низкий логический уровень, а до некоторого потенциала выше этого напряжения приблизительно на величину порогового напряжения р-канального МОП-транзистора. За высокий логический уровень при этом принимается потенциал шины питания АЗУ. Недостаток второго указанного способа состоит в том, что отпирающее напряжение на затворе n-канального МОП-транзистор, через который обеспечивается протекание тока между линией совпадения и шиной земли, будет меньше напряжения логической единицы приблизительно на величину порогового напряжения n-канального МОП-транзистора из-за потерь в одном из двух n-канальных транзисторах в устройстве сравнения. Это приводит к падению помехоустойчивости АЗУ.

Наиболее близким по технической сути и достигаемому результату является способ сравнения данных в ячейке ассоциативного запоминающего устройства (АЗУ), включающий разряд потенциала линии совпадения до низкого логического уровня во время цикла сравнения хранящихся в ячейке памяти данных с внешними данными при несовпадении хранящихся в ячейке памяти данных с внешними данными и модуль сравнения данных в ячейке ассоциативного запоминающего устройства (АЗУ), включающий две параллельно подключенные между шиной земли и линией совпадения пар последовательно включенных n-канальных МОП (патентная заявка US №2004/0213027 кл. G11C 15/00, опублик. 2004 г.). Ток, разряжающий линию совпадения, протекает в случае несовпадения данных, хранящихся в ячейке АЗУ, с данными на парафазной внешней шине данных через одну из двух указанных пар.

Недостатком описанных выше способа и модуля является наличие четырех транзисторов в устройстве сравнения, что приводит к росту площади на кристалле, занимаемой ячейками АЗУ, а следовательно, АЗУ в целом.

Техническим результатом, ожидаемым от использования изобретения, является уменьшение площади АЗУ и повышение его помехоустойчивости за счет использования меньшего количества транзисторов в устройстве сравнения и использования полного логического перепада сигналов в нем без потерь уровней напряжения.

Указанный технический результат достигается тем, что в способе сравнения данных в ячейке АЗУ, включающем разряд потенциала линии совпадения до низкого логического уровня во время цикла сравнения хранящихся в ячейке памяти данных с внешними данными при несовпадении хранящихся в ячейке памяти данных с внешними данными, согласно изобретению указанный разряд потенциала линии совпадения осуществляют путем протекания тока между одним из двух парафазных выходов усилителя сигналов сравнения данных и предварительно заряженной до высокого логического уровня линией совпадения после установления одного из парафазных сигналов сравнения данных в низкий логический уровень на истоке одного из двух транзисторов одинакового типа проводимости, параллельно установленных между линией совпадения и парафазными шинами сравнения данных и при подаче на затвор указанного транзистора высокого логического уровня с одного из двух узлов хранения данных ячейки памяти.

Для осуществления способа предназначен модуль сравнения данных в ячейке ассоциативного запоминающего устройства (АЗУ), включающий два транзистора с одинаковым типом проводимости, к затвору одного из которых подключен узел хранения прямого бита данных ячейки памяти, а к затвору другого - узел хранения инверсного бита данных ячейки памяти, отличающийся тем, что согласно изобретению стоки указанных транзисторов подключены к линии совпадения АЗУ, при этом, прямой выход усилителя сравнения данных АЗУ подключен к истоку транзистора, затвор которого соединен с узлом хранения прямого бита данных ячейки памяти, а инверсный выход усилителя сравнения данных АЗУ подключен к истоку транзистора, затвор которого соединен с узлом хранения инверсного бита данных ячейки памяти.

Для использования выходов усилителя, как для цикла сравнения, так и для цикла записи в указанном модуле прямая битовая шина соединена с прямым выходом усилителя сравнения данных АЗУ, а инверсная битовая шина соединена с инверсным выходом указанного усилителя сравнения данных.

В результате при несовпадении данных, хранящихся в ячейке памяти, с данными на парафазной шине сравнения данных на затворе того из двух указанных транзисторов, на исток которого подается высокий логический уровень, оказывается низкий логический уровень, и протекание тока через него невозможно. А на исток другого транзистора в это же время подается низкий логический уровень при высоком логическом уровне на затворе, что делает возможным протекание тока и разряду линии совпадения до низкого логического уровня. При совпадении данных на парафазной шине сравнения с данными, хранящимися в ячейке памяти, на исток открытого транзистора подается высокий логический уровень идентичный потенциалу стока этого транзистора, подключенного к линии совпадения, и разряда линии совпадения не происходит. Использование двух транзисторов в устройстве, реализующем способ, приводит к сокращению площади, занимаемой устройством, а использование в устройстве логических уровней без потерь в величине напряжения между ними увеличивает помехоустойчивость.

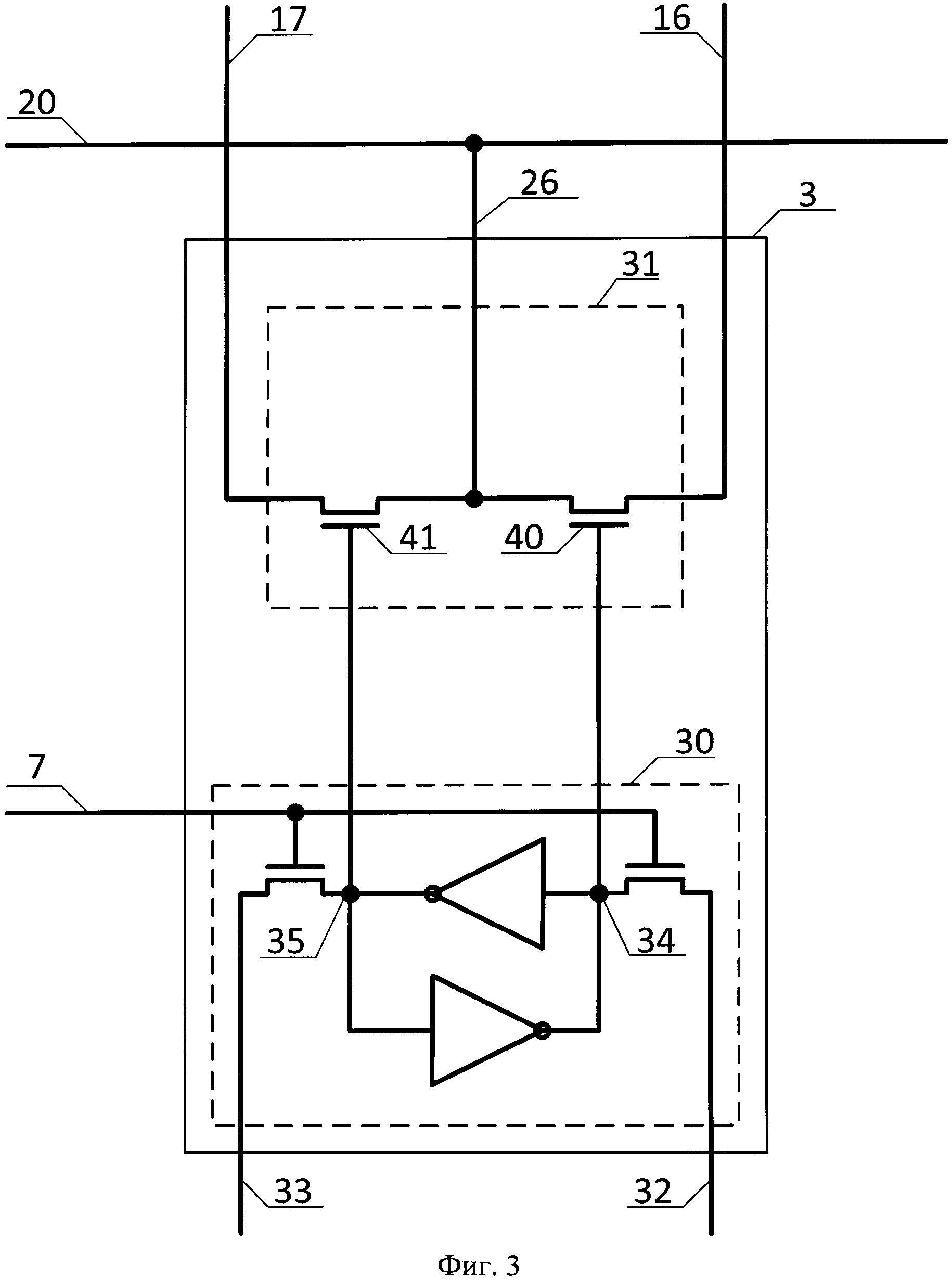

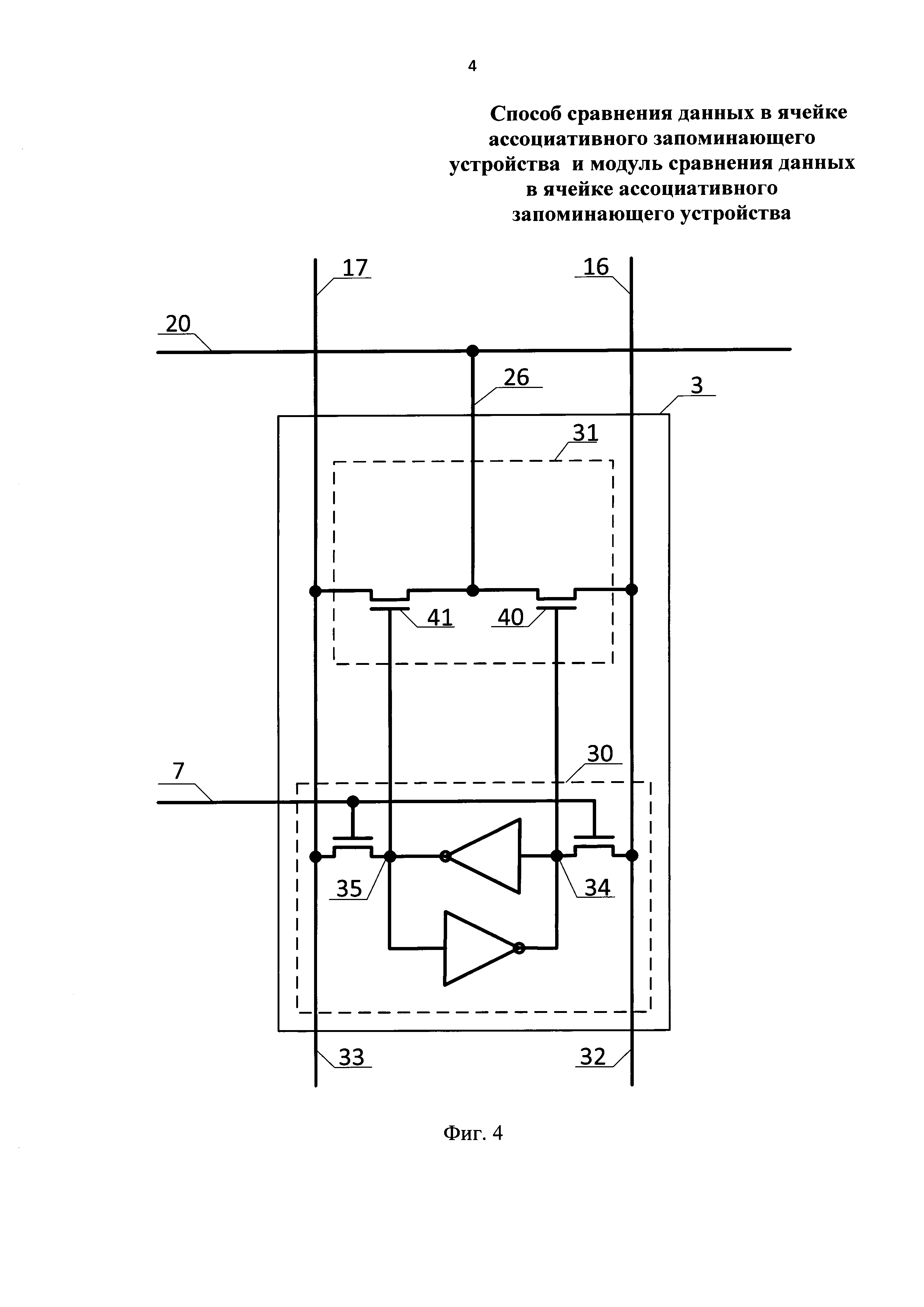

Изобретение поясняется чертежами, где на

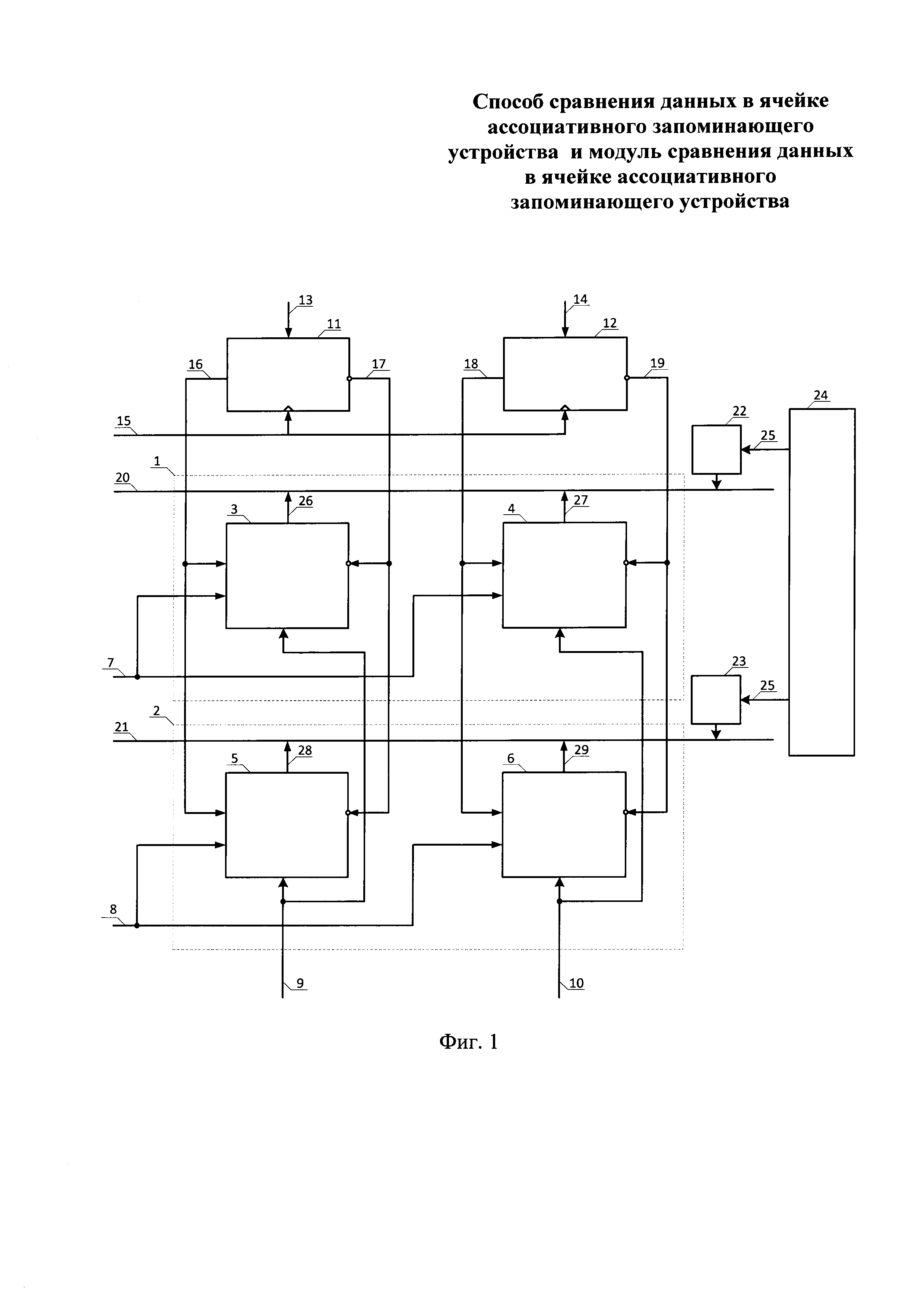

фиг. 1 представлен неограничивающий пример схемы массива АЗУ,

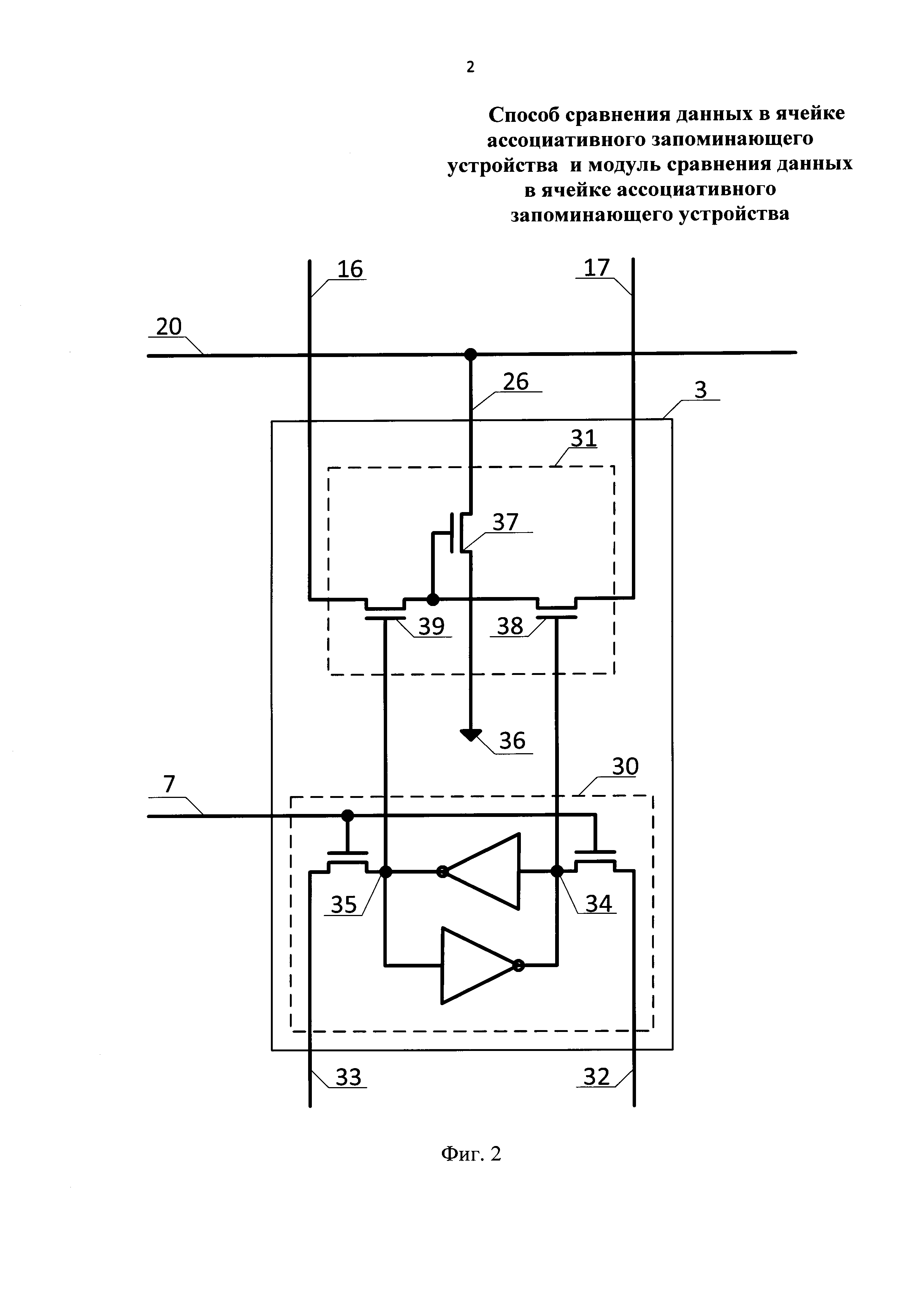

фиг. 2 - общеизвестный способ и устройство сравнения данных в ячейке АЗУ по прототипу,

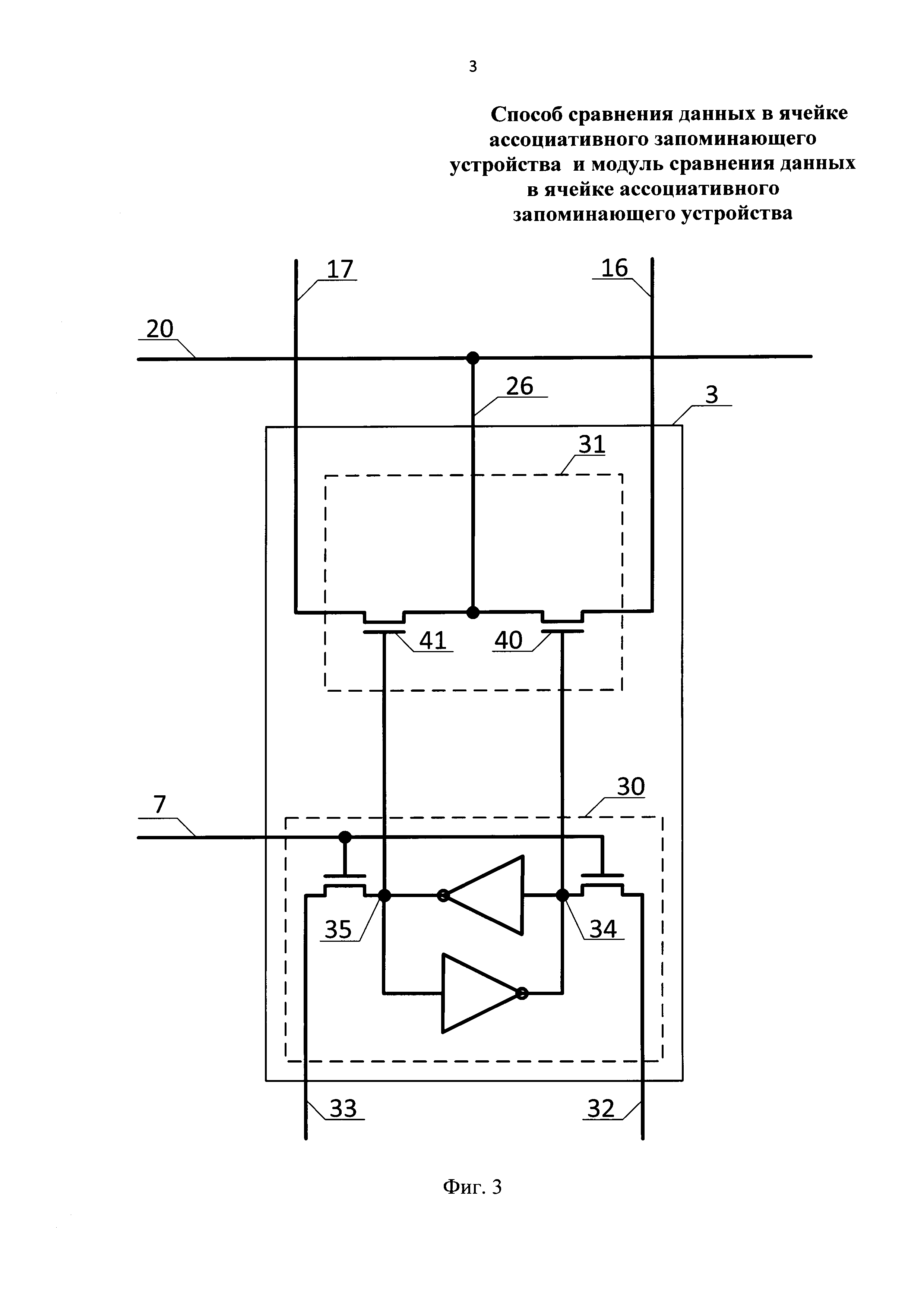

фиг. 3 - модуль сравнения данных в ячейке ассоциативного запоминающего устройства (АЗУ) в соответствии с изобретением,

фиг. 4 - модуль сравнения данных в ячейке ассоциативного запоминающего устройства (АЗУ) с расширенной функцией,

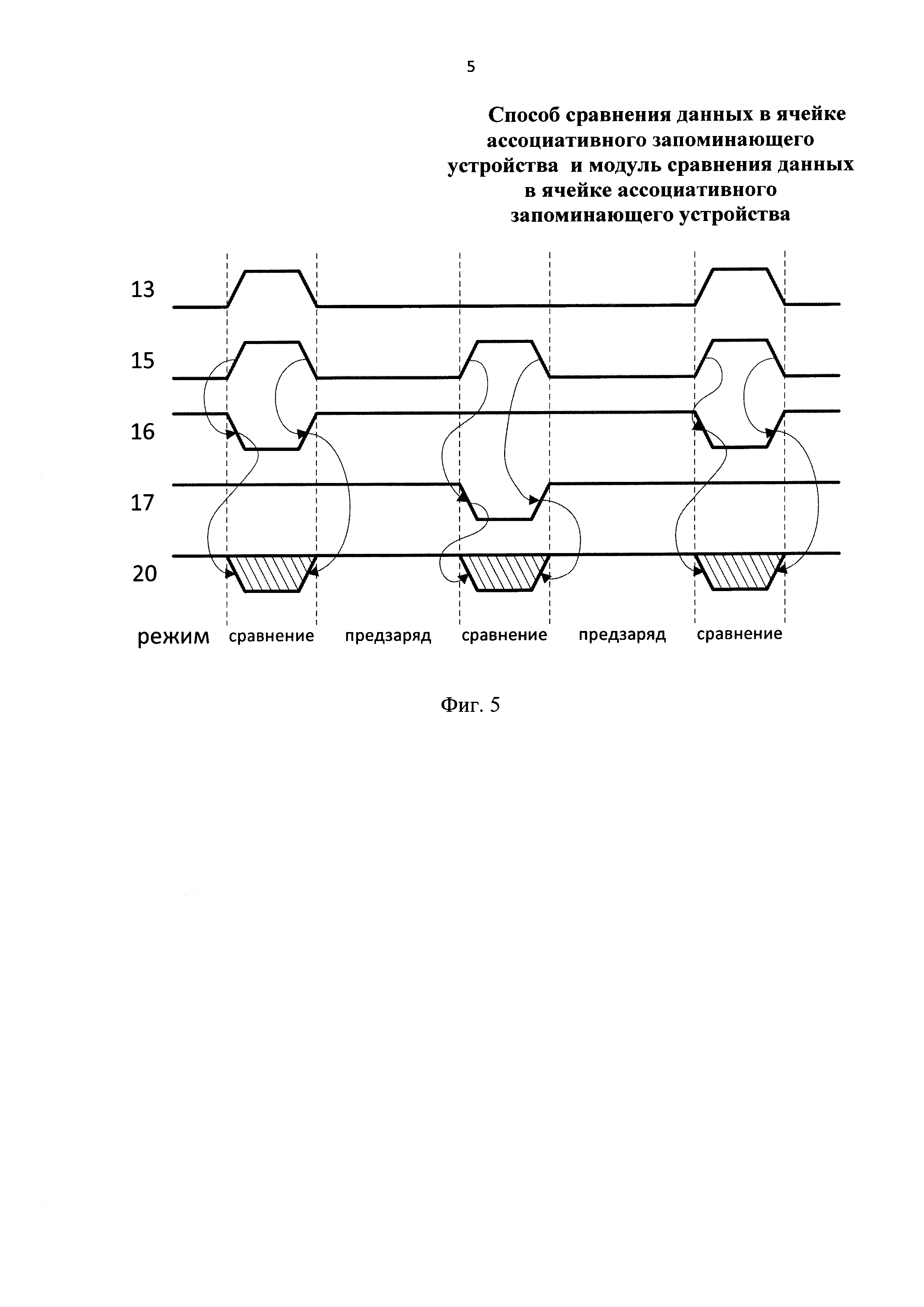

фиг. 5 - временная диаграмма работы АЗУ на основе данного способа.

Массив памяти АЗУ содержит несколько регистров с определенным количеством бит в каждом. Неограничивающий пример, известный из уровня техники и приведенный на фиг. 1, содержит, например, два регистра: верхний 1 и нижний 2. Верхний регистр 1 в данном примере содержит две ячейки АЗУ: левая 3 и правая 4. Нижний регистр 2 в данном примере содержит также две ячейки АЗУ: левая 5 и правая 6. Ячейки АЗУ 3, 4, 5, 6 могут иметь как идентичные, так и разные схемы. Через верхний регистр 1 проходят одна или несколько сквозных словарных шин 7, управляющих чтением и записью данных в ячейки АЗУ 3 и 4. Через нижний регистр 2 проходят одна или несколько сквозных словарных шин 8, управляющих чтением и записью данных в ячейки АЗУ 5 и 6. Записываемые и считываемые данные по одной или нескольким битовым шинам 9 подаются к ячейкам АЗУ 3 и 5, а по одной или нескольким битовым шинам 10 - к ячейкам АЗУ 4 и 6. Над ячейками АЗУ 3 и 5 находится усилитель 11. А над ячейками АЗУ 4 и 6 находится усилитель 12. Бит внешних данных для сравнения с данными, записанными в ячейках АЗУ 3 и 5, подается на вход 13 усилителя 11. Бит внешних данных для сравнения с данными, записанными в ячейках АЗУ 4 и 6, подается на вход 14 усилителя 12. Все усилители управляются синхросигналом 15. Усилитель 11 имеет парафазные выходы - прямой 16 и инверсный 17 - подключенные к парафазным входам сравнения в ячейках АЗУ 3 и 5. Усилитель 12 имеет парафазные выходы - прямой 18 и инверсный 19 - подключенные к парафазным входам сравнения в ячейках АЗУ 4 и 6. Через регистр 1 проходит сквозная линия совпадения 20, а через регистр 2 - линия совпадения 21. К линии совпадения 20 подключена схема предзаряда 22, а к линии совпадения 21 подключена схема предзаряда 23. Устройство управления предзарядом 24 генерирует один или несколько сигналов 25, запускающих схемы предзаряда 22 и 23. Также к линии совпадения 20 подключен выход сравнения 26 ячейки АЗУ 3 и выход сравнения 27 ячейки АЗУ 4. А к линии совпадения 21 подключен выход сравнения 28 ячейки АЗУ 5 и выход сравнения 29 ячейки АЗУ 6.

На фиг. 2 представлена схема реализации способа сравнения данных в ячейке АЗУ, известная из уровня техники (по прототипу). Ячейка АЗУ 3 состоит из триггера 30 и компаратора 31. Данные поступают в триггер 30 ячейки АЗУ 3 по прямой 32 и инверсной 33 битовым шинам и записываются по сигналу на словарной шине 7, соответственно, в узел хранения прямого бита данных 34 и узел хранения инверсного бита данных 35. Компаратор 31 обеспечивает подключение предварительно заряженной схемой 22 до высокого логического уровня линии совпадения 20 к шине земли 36 в случае несовпадения данных, хранящихся в узлах 34 и 35 ячейки АЗУ 3 с внешними данными, подаваемым с выходов 16 и 17 усилителя 11. Для этого к шине земли 36 подключен исток n-канального транзистора 37, сток которого подключен линии совпадения 20. На затвор транзистора 37 приходит сигнал со стоков транзисторов 38 и 39. На затвор транзистора 39 приходит сигнал с узла хранения инверсного бита данных 35, а на затвор транзистора 38 - сигнал с узла хранения прямого бита данных 34. Исток транзистора 39 подключен к прямому выходу 16 усилителя 11, а исток транзистора 38 - к инверсному выходу 17 усилителя 11.

Если узел хранения прямого бита данных 34 находится в высоком логическом уровне, то n-канальный транзистор 38 открыт и передает на затвор транзистора 37 сигнал с инверсного выхода 17 усилителя 11. Если выход 17 находится в низком логическом уровне, то он без потерь передается на затвор транзистора 37, запирая его, и протекание тока от линии совпадения 20 к шине земли 36 невозможно. Это соответствует ситуации совпадения данных. Если же выход 17 находится в высоком логическом уровне, то этот уровень с потерями, определяемыми величиной порогового напряжения транзистора 38, передается на затвор транзистора 37, отпирая его, и ток протекает от линии совпадения 20 к шине земли 36, разряжая потенциал линии совпадения 20 до низкого логического уровня. Эта соответствует ситуации несовпадения данных. Аналогичные рассуждения справедливы для транзистора 39, выхода 16 усилителя 11 и узла хранения инверсного бита данных 35.

Компаратор 31 (см. фиг. 3) обеспечивает подключение предварительно заряженной схемой 22 до высокого логического уровня линии совпадения 20 к одному из двух выходов 16 и 17 усилителя 11 таким образом, что в случае совпадения данных, линия совпадения 20 подключается к тому выходу усилителя 11, на котором находится высокий логический уровень, что не приводит к снижению потенциала линии совпадения 20, а в случае несовпадения данных, линия совпадения 20 подключается к тому выходу усилителя 11, на котором находится низкий логический уровень, что приводит к протеканию тока через компаратор 31 от линии совпадения 20 к указанному выходу усилителя 11 и к разряду потенциала линии совпадения 20 до низкого логического уровня.

Усовершенствованный модуль представлен на фиг. 4.

Компаратор 31 состоит из двух n-канальных транзисторов 40 и 41, затворы которых подключены к узлам хранения прямого и инверсного бита данных 34 и 35, соответственно. Стоки транзисторов 40 и 41 подключены к линии совпадения 20, а истоки к прямому 16 и инверсному 17 выходам усилителя 11, соответственно. Прямая битовая шина 32 соединена с прямым выходом 16 усилителя сравнения данных 11 АЗУ, а инверсная битовая шина 33 соединена с инверсным выходом 17 указанного усилителя сравнения данных 11. Устройство работает следующим образом. Если узел хранения прямого бита данных 34 находится в высоком логическом уровне, то транзистор 40 открыт, а транзистор 41 закрыт.Если при этом на прямом выходе 16 усилителя 11 находится высокий логический уровень, то ток через транзистор 40 не протекает, так как разности потенциалов между его стоком и истоком нет. Это соответствует ситуации совпадения данных. Если на прямом выходе 16 усилителя 11 находится низкий логический уровень, то через открытый транзистор 40 протекает ток от линии совпадения 20 к выходу усилителя 16, разряжая тем самым потенциал линии совпадения 20 до низкого логического уровня. Аналогичные рассуждения справедливы для узла хранения инверсного бита данных 35, транзистора 41 и инверсного выхода 17 усилителя 11. Вне цикла сравнения внешних данных 13 с данными, хранящимися в ячейке АЗУ 3, потенциалы обоих выходов 16 и 17 усилителя 11 должны устанавливаться в высокий логический уровень для предотвращения непреднамеренного разряда линии совпадения 20.

Выходы 16 и 17 усилителя 11 для уменьшения количества проводников могут быть использованы не только в цикле сравнения, но и в цикле записи, если прямой 16 и инверсный 17 выходы усилителя 11 объединить с прямой 32 и инверсной 33 битовыми шинами, соответственно. При этом во время цикла записи в силу совпадения данных, записанных в триггер 30 ячейки 3, с данными на шинах 16 и 17, подаваемых на вход компаратора 31 разряда линии совпадения не происходит, то есть правильность работы всего устройства не нарушается.

Временная диаграмма работы АЗУ, представленная на фиг. 5, изображена для случая, при котором бит данных, поступивший на вход 13, передается на выходы 16 и 17 по высокому уровню синхросигнала разрешения 15, а по низкому уровню синхросигнала 15 напряжение на выходах 16 и 17 устанавливается в высокий уровень. Когда один из сигналов на выходах 16 или 17 переключается в высокий логический уровень, модули предзаряда 22 и 23 отключаются, в ячейках АЗУ происходит сравнение данных, хранящихся в ячейках, с данными, поступившими с выходов 16 и 17 усилителя 11, что или разряжает линию совпадения до низкого логического уровня в случае несовпадения, или не изменяет ее потенциал в случае совпадения.

Изобретение позволяет уменьшить площадь, занимаемое АЗУ на кристалле, а также повысить помехоустойчивость АЗУ за счет использования двух транзисторов с одинаковым типом проводимости в модуле сравнения данных в ячейке АЗУ в соответствии с изобретением и использования полного логического перепада сигналов в нем без потерь уровней напряжения.