Результат интеллектуальной деятельности: УСТРОЙСТВО ИМИТОЗАЩИТЫ КОНТРОЛИРУЕМЫХ ОБЪЕКТОВ С ПОВЫШЕННОЙ СТРУКТУРНОЙ СКРЫТНОСТЬЮ СИГНАЛОВ-ПЕРЕНОСЧИКОВ

Вид РИД

Изобретение

Область техники

Изобретение относится к технике охранно-пожарной сигнализации, в частности к устройствам имитозащиты контролируемых объектов, и может быть использовано для охраны объектов.

Уровень техники

Известно устройство имитозащиты контролируемых объектов (Патент РФ №2310236 «УСТРОЙСТВО ДЛЯ ИМИТОЗАЩИТЫ КОНТРОЛИРУЕМЫХ ОБЪЕКТОВ», опубл. 10.11.2007), состоящее из датчика, содержащего блок памяти стартовой последовательности, блок сравнения, генератор второй псевдослучайной последовательности (генератор ПСП-2), блок преобразования n-разрядной параллельной комбинации в последовательную, блок памяти, блок преобразования последовательной комбинации в n-разрядную параллельную, демодулятор, модулятор, согласующее устройство, блока обработки информации, содержащего блок памяти стартовой последовательности, блок преобразования n-разрядной параллельной комбинации в последовательную, модулятор, согласующее устройство, генератор ключа, генератор первой псевдослучайной последовательности (генератор ПСП-1), блок памяти контрольного значения, генератор второй псевдослучайной последовательности (генератор ПСП-2), блок первого запоминающего устройства, блок сравнения, блок второго запоминающего устройства, блок преобразования последовательной комбинации в n-разрядную параллельную, демодулятор, блока избирания сигналов, входящего в состав блока передачи, линии связи, блока избирания сигналов, входящего в состав транслятора, блока управления, входящего в состав блока приема информации.

Главным недостатком данного устройства является то обстоятельство, что передаваемые по линии связи последовательности не защищены от перехвата, просмотра и подмены злоумышленником. Следовательно, достаточно перехватывать поступающие на вход контролируемого объекта значения, направленные от блока обработки информации к генератору ПСП-2 объекта, и осуществлять подмену выходных значений, исходя из полученных в результате наблюдения данных.

Возможным решением проблемы защиты передаваемых по открытым линиям связи псевдослучайных последовательностей от перехвата и внедрения в систему имитозащиты контролируемых объектов может быть следующее устройство (Патент РФ №2326500 «КОГЕРЕНТНАЯ СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ ХАОТИЧЕСКИМИ СИГНАЛАМИ», опубл. 10.06.2008), состоящее из источника информации, передающей стороны, включающей в себя накопитель хаотического сигнала, модулятор-передатчик, линии связи, приемной стороны, включающей в себя полосовой фильтр, усилитель, первый умножитель, второй умножитель, инвертор, накопитель копии хаотического сигнала, первый интегратор, второй интегратор, вычитающее устройство, решающее устройство, получателя информации.

Раскрытие изобретения

Задачами предлагаемого изобретения является разработка устройства имитозащиты контролируемых объектов, способного не только обеспечить имитозащищенность датчика, но также позволяющего производить структурно скрытый обмен псевдослучайными последовательностями между передающей и получающей сторонами, обеспечивая таким образом увеличение защищенности линии связи от встраивания и перехвата информации и уменьшение вероятности перехвата и подмены псевдослучайных последовательностей, циркулирующих между датчиком и блоком контроля за счет использования накопителей хаотических сигналов. Для этого в состав блока контроля и в датчик введены блок передатчика, состоящий из накопителя хаотического сигнала, модулятора-передатчика, и блок приемника, состоящий из полосового фильтра, усилителя, первого умножителя, второго умножителя, инвертора, накопителя копии хаотического сигнала, первого интегратора, второго интегратора, вычитающего устройства, решающего устройства. Внедрение данных блоков в устройство в качестве подсистем предназначено для структурно скрытого обмена псевдослучайными последовательностями между передающей и получающей сторонами за счет использования накопителей хаотических сигналов.

Технический результат, который может быть получен с помощью предлагаемого изобретения, сводится к увеличению защищенности линии связи от встраивания и перехвата информации и уменьшению вероятности перехвата и подмены псевдослучайных последовательностей, циркулирующих между датчиком и блоком контроля за счет использования накопителей хаотических сигналов.

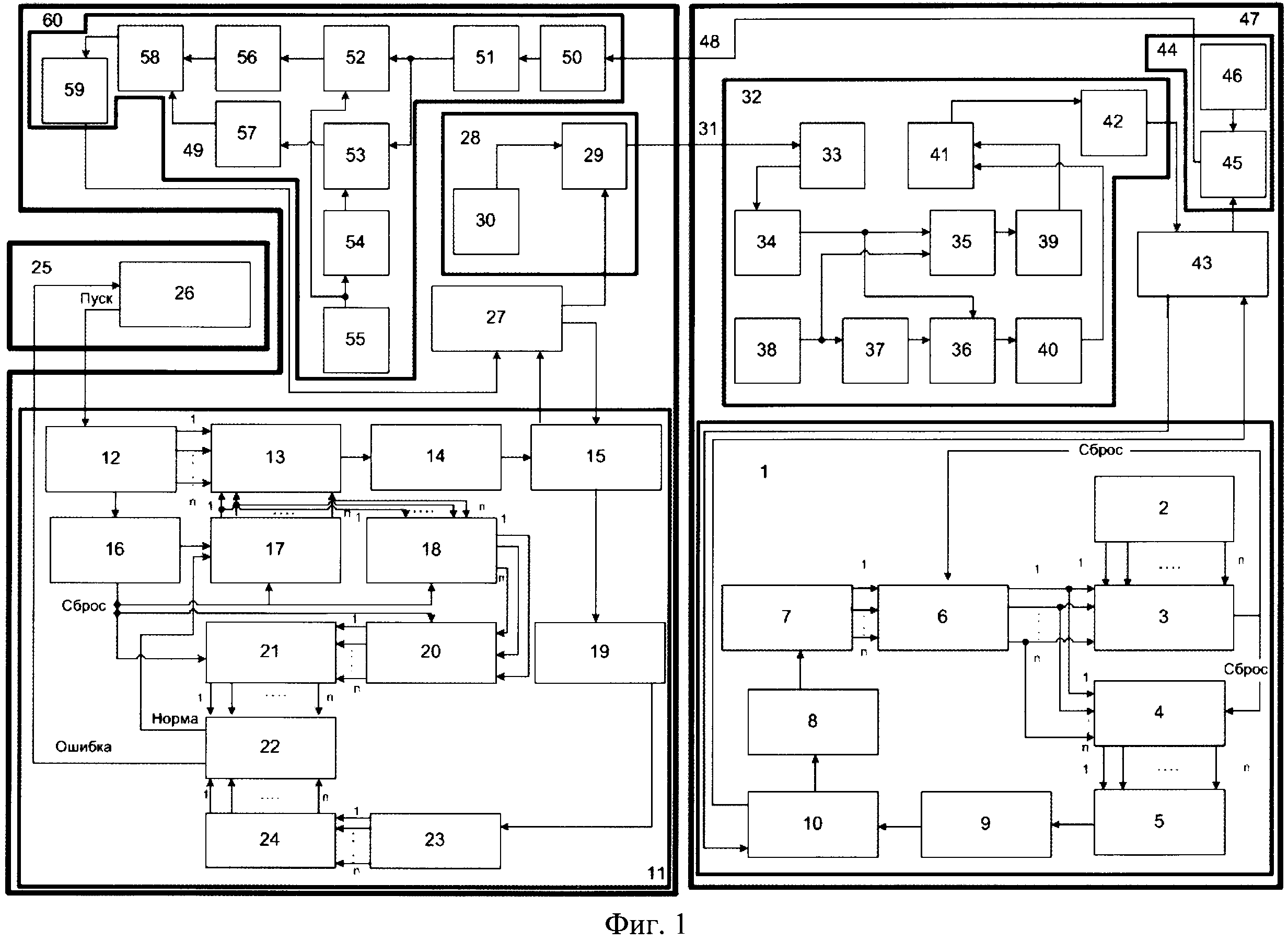

Технический результат достигается с помощью устройства имитозащиты контролируемых объектов с повышенной структурной скрытностью сигналов-переносчиков, состоящего из датчика 1, содержащего в себе: блок памяти стартовой последовательности 2, блок сравнения 3, генератор 4 ПСП-2, блок 5 преобразования n-разрядной параллельной комбинации в последовательную, блок 6 памяти, блок 7 преобразования последовательной комбинации в n-разрядную параллельную, демодулятор 8, модулятор 9, согласующее устройство 10, блока 11 обработки информации, содержащего в себе: блок памяти 12 стартовой последовательности, блок 13 преобразования n-разрядной параллельной комбинации в последовательную, модулятор 14, согласующее устройство 15, генератор 16 ключа, генератор 17 первой псевдослучайной последовательности (генератор 17 ПСП-1), блок памяти 18 контрольного значения, демодулятор 19, генератор 20 второй псевдослучайной последовательности (генератор 20 ПСП-2), блок первого запоминающего устройства 21, блок 22 сравнения, блок 23 преобразования последовательной комбинации в n-разрядную параллельную, блок второго запоминающего устройства 24, блока 25 приема информации, содержащего в себе блок управления 26, блока 27 избирания сигналов, блока 28 передатчика, содержащего в себе: модулятор-передатчик 29, накопитель хаотического сигнала 30, линии связи 31, блока 32 приемника, содержащего в себе: полосовой фильтр 33, усилитель 34, первый умножитель 35, второй умножитель 36, инвертор 37, накопитель копии хаотического сигнала 38, первый интегратор 39, второй интегратор 40, вычитающее устройство 41, решающее устройство 42, блока 43 избирания сигналов, блока 44 передатчика, содержащего в себе: модулятор-передатчик 45, накопитель хаотического сигнала 46, входящих в состав блока 47 передачи информации, линии связи 48, блока 49 приемника, содержащего в себе: полосовой фильтр 50, усилитель 51, первый умножитель 52, второй умножитель 53, инвертор 54, накопитель копии хаотического сигнала 55, первый интегратор 56, второй интегратор 57, вычитающее устройство 58, решающее устройство 59, входящих в состав транслятора 60,

причем выход блока памяти 2 стартовой последовательности, входящего в состав датчика 1, подключен к первому входу блока сравнения 3,

выход блока сравнения 3 подключен к входу сброса в исходное состояние блока памяти 6 и входу сброса в исходное состояние генератора 4 ПСП-2,

выход генератора 4 ПСП-2 подключен к входу блока 5 преобразования n-разрядной параллельной комбинации в последовательную,

выход блока 5 преобразования n-разрядной параллельной комбинации в последовательную подключен к входу модулятора 9,

выход блока памяти 6 подключен к входу блока сравнения 3 и к входу запуска генератора 4 ПСП-2,

выход блока 7 преобразования последовательной комбинации в n-разрядную параллельную подключен к входу блока памяти 6,

выход демодулятора 8 подключен к входу блока 7 преобразования последовательной комбинации в n-разрядную параллельную,

выход модулятора 9 подключен к первому входу согласующего устройства 10,

первый выход согласующего устройства 10 подключен к входу демодулятора 8, второй выход согласующего устройства 10 подключен к первому входу блока избирания сигналов 43, входящего в состав блока передачи информации 47,

первый выход блока памяти 12 стартовой последовательности, входящего в состав блока 11 обработки информации, подключен к первому входу блока 13 преобразования n-разрядной параллельной комбинации в последовательную, второй выход блока памяти 12 стартовой последовательности подключен к входу генератора 16 ключа,

выход блока 13 преобразования n-разрядной параллельной комбинации в последовательную подключен к входу модулятора 14,

выход модулятора 14 подключен к первому входу согласующего устройства 15,

первый выход согласующего устройства 15 подключен к входу демодулятора 19, второй выход согласующего устройства 15 подключен к первому входу блока избирания сигналов 27, входящего в состав транслятора 60,

первый выход генератора 16 ключа подключен к входу запуска генератора 17 ПСП-1, второй выход генератора 16 ключа подключен к входу сброса в исходное состояние генератора 17 ПСП-1, входу сброса в исходное состояние блока памяти 18 контрольного значения, входу сброса в исходное состояние генератора 20 ПСП-2, входу сброса в исходное состояние блока первого запоминающего устройства 21,

выход генератора 17 ПСП-1 подключен к входу блока памяти 18 контрольного значения и ко второму входу блока 13 преобразования n-разрядной параллельной комбинации в последовательную,

выход блока памяти 18 контрольного значения подключен к входу запуска генератора 20 ПСП-2,

выход демодулятора 19 подключен к входу блока 23 преобразования последовательной комбинации в n-разрядную параллельную,

выход генератора 20 ПСП-2 подключен к входу первого запоминающего устройства 21,

выход первого запоминающего устройства 21 подключен к первому входу блока 22 сравнения,

первый выход блока 22 сравнения подключен ко второму входу генератора 17 ПСП-1, второй выход блока 22 сравнения подключен к входу блока управления 26, входящего в состав блока 25 приема информации,

выход блока 23 преобразования последовательной комбинации в n-разрядную параллельную подключен к входу второго запоминающего устройства 24,

выход второго запоминающего устройства 24 подключен ко второму входу блока 22 сравнения,

выход блока управления 26 подключен к входу блока памяти 12 стартовой последовательности,

первый выход блока избирания сигналов 27 подключен к первому входу модулятора-передатчика 29, входящего в состав блока 28 передатчика, второй выход блока избирания сигналов 27 подключен к первому входу согласующего устройства 15,

выход модулятора-передатчика 29 через линию связи 31 подключен к полосовому фильтру 33, входящему в состав блока 32 приемника,

выход накопителя хаотического сигнала 30 подключен ко второму входу модулятора-передатчика 29,

выход полосового фильтра 33 подключен к входу усилителя 34,

выход усилителя 34 подключен к первому входу первого умножителя 35 и к первому входу второго умножителя 36,

выход первого умножителя 35 подключен к входу первого интегратора 39,

выход второго умножителя 36 подключен к входу второго интегратора 40,

выход инвертора 37 подключен ко второму входу второго умножителя 36,

выход накопителя копии хаотического сигнала 38 подключен к входу инвертора 37 и ко второму входу первого умножителя 35,

выход первого интегратора 39 подключен к первому входу вычитающего устройства 41,

выход второго интегратора 40 подключен ко второму входу вычитающего устройства 41,

выход вычитающего устройства 41 подключен к входу решающего устройства 42,

выход решающего устройства 42 подключен ко второму входу блока 43 избирания сигналов,

первый выход блока 43 избирания сигналов, входящего в состав блока 47 передачи информации, подключен к первому входу модулятора-передатчика 45, второй выход блока 43 избирания сигналов подключен ко второму входу согласующего устройства 10,

выход модулятора-передатчика 45, входящего в состав блока 44 передатчика, через линию связи 48 подключен к входу полосового фильтра 50,

выход накопителя хаотического сигнала 46 подключен ко второму входу модулятора-передатчика 45,

выход полосового фильтра 50, входящего в состав блока 49 приемника, подключен к входу усилителя 51,

выход усилителя 51 подключен к первому входу первого умножителя 52 и к первому входу второго умножителя 53,

выход первого умножителя 52 подключен к входу первого интегратора 56,

выход второго умножителя 53 подключен к входу второго интегратора 57,

выход инвертора 54 подключен ко второму входу второго умножителя 53,

выход накопителя копии хаотического сигнала 55 подключен к входу инвертора 54 и ко второму входу первого умножителя 52,

выход первого интегратора 56 подключен к первому входу вычитающего устройства 58,

выход второго интегратора 57 подключен ко второму входу вычитающего устройства 58,

выход вычитающего устройства 58 подключен к входу решающего устройства 59,

выход решающего устройства 59 подключен ко второму входу блока 27 избирания сигналов.

Краткое описание чертежей

На фиг. 1 изображена блок-схема устройства имитозащиты контролируемых объектов с повышенной структурной скрытностью сигналов-переносчиков.

Устройство имитозащиты контролируемых объектов с повышенной структурной скрытностью сигналов-переносчиков состоит из датчика 1, содержащего в себе: блок памяти стартовой последовательности 2, блок сравнения 3, генератор 4 ПСП-2, блок 5 преобразования n-разрядной параллельной комбинации в последовательную, блок 6 памяти, блок 7 преобразования последовательной комбинации в n-разрядную параллельную, демодулятор 8, модулятор 9, согласующее устройство 10, блока 11 обработки информации, содержащего в себе: блок памяти 12 стартовой последовательности, блок 13 преобразования n-разрядной параллельной комбинации в последовательную, модулятор 14, согласующее устройство 15, генератор 16 ключа, генератор 17 первой псевдослучайной последовательности (генератор 17 ПСП-1), блок памяти 18 контрольного значения, демодулятор 19, генератор 20 второй псевдослучайной последовательности (генератор 20 ПСП-2), блок первого запоминающего устройства 21, блок 22 сравнения, блок 23 преобразования последовательной комбинации в n-разрядную параллельную, блок второго запоминающего устройства 24, блока 25 приема информации, содержащего в себе блок управления 26, блока 27 избирания сигналов, блока 28 передатчика, содержащего в себе: модулятор-передатчик 29, накопитель хаотического сигнала 30, линии связи 31, блока 32 приемника, содержащего в себе: полосовой фильтр 33, усилитель 34, первый умножитель 35, второй умножитель 36, инвертор 37, накопитель копии хаотического сигнала 38, первый интегратор 39, второй интегратор 40, вычитающее устройство 41, решающее устройство 42, блока 43 избирания сигналов, блока 44 передатчика, содержащего в себе: модулятор-передатчик 45, накопитель хаотического сигнала 46, входящих в состав блока 47 передачи информации, линии связи 48, блока 49 приемника, содержащего в себе: полосовой фильтр 50, усилитель 51, первый умножитель 52, второй умножитель 53, инвертор 54, накопитель копии хаотического сигнала 55, первый интегратор 56, второй интегратор 57, вычитающее устройство 58, решающее устройство 59, входящих в состав транслятора 60.

Осуществление изобретения

Устройство имитозащиты контролируемых объектов с повышенной структурной скрытностью сигналов-переносчиков состоит из датчика 1, содержащего в себе: блок памяти стартовой последовательности 2, блок сравнения 3, генератор 4 ПСП-2, блок 5 преобразования n-разрядной параллельной комбинации в последовательную, блок 6 памяти, блок 7 преобразования последовательной комбинации в n-разрядную параллельную, демодулятор 8, модулятор 9, согласующее устройство 10, блока 11 обработки информации, содержащего в себе: блок памяти 12 стартовой последовательности, блок 13 преобразования n-разрядной параллельной комбинации в последовательную, модулятор 14, согласующее устройство 15, генератор 16 ключа, генератор 17 первой псевдослучайной последовательности (генератор 17 ПСП-1), блок памяти 18 контрольного значения, демодулятор 19, генератор 20 второй псевдослучайной последовательности (генератор 20 ПСП-2), блок первого запоминающего устройства 21, блок 22 сравнения, блок 23 преобразования последовательной комбинации в n-разрядную параллельную, блок второго запоминающего устройства 24, блока 25 приема информации, содержащего в себе блок управления 26, блока 27 избирания сигналов, блока 28 передатчика, содержащего в себе: модулятор-передатчик 29, накопитель хаотического сигнала 30, линии связи 31, блока 32 приемника, содержащего в себе: полосовой фильтр 33, усилитель 34, первый умножитель 35, второй умножитель 36, инвертор 37, накопитель копии хаотического сигнала 38, первый интегратор 39, второй интегратор 40, вычитающее устройство 41, решающее устройство 42, блока 43 избирания сигналов, блока 44 передатчика, содержащего в себе: модулятор-передатчик 45, накопитель хаотического сигнала 46, входящих в состав блока 47 передачи информации, линии связи 48, блока 49 приемника, содержащего в себе: полосовой фильтр 50, усилитель 51, первый умножитель 52, второй умножитель 53, инвертор 54, накопитель копии хаотического сигнала 55, первый интегратор 56, второй интегратор 57, вычитающее устройство 58, решающее устройство 59, входящих в состав транслятора 60,

причем выход блока памяти 2 стартовой последовательности, входящего в состав датчика 1, подключен к первому входу блока сравнения 3,

выход блока сравнения 3 подключен к входу сброса в исходное состояние блока памяти 6 и входу сброса в исходное состояние генератора 4 ПСП-2,

выход генератора 4 ПСП-2 подключен к входу блока 5 преобразования n-разрядной параллельной комбинации в последовательную,

выход блока 5 преобразования n-разрядной параллельной комбинации в последовательную подключен к входу модулятора 9,

выход блока памяти 6 подключен к входу блока сравнения 3 и к входу запуска генератора 4 ПСП-2,

выход блока 7 преобразования последовательной комбинации в n-разрядную параллельную подключен к входу блока памяти 6,

выход демодулятора 8 подключен к входу блока 7 преобразования последовательной комбинации в n-разрядную параллельную,

выход модулятора 9 подключен к первому входу согласующего устройства 10,

первый выход согласующего устройства 10 подключен к входу демодулятора 8, второй выход согласующего устройства 10 подключен к первому входу блока избирания сигналов 43, входящего в состав блока передачи информации 47,

первый выход блока памяти 12 стартовой последовательности, входящего в состав блока 11 обработки информации, подключен к первому входу блока 13 преобразования n-разрядной параллельной комбинации в последовательную, второй выход блока памяти 12 стартовой последовательности подключен к входу генератора 16 ключа,

выход блока 13 преобразования n-разрядной параллельной комбинации в последовательную подключен к входу модулятора 14,

выход модулятора 14 подключен к первому входу согласующего устройства 15,

первый выход согласующего устройства 15 подключен к входу демодулятора 19, второй выход согласующего устройства 15 подключен к первому входу блока избирания сигналов 27, входящего в состав транслятора 60,

первый выход генератора 16 ключа подключен к входу запуска генератора 17 ПСП-1, второй выход генератора 16 ключа подключен к входу сброса в исходное состояние генератора 17 ПСП-1, входу сброса в исходное состояние блока памяти 18 контрольного значения, входу сброса в исходное состояние генератора 20 ПСП-2, входу сброса в исходное состояние блока первого запоминающего устройства 21,

выход генератора 17 ПСП-1 подключен к входу блока памяти 18 контрольного значения и ко второму входу блока 13 преобразования n-разрядной параллельной комбинации в последовательную,

выход блока памяти 18 контрольного значения подключен к входу запуска генератора 20 ПСП-2,

выход демодулятора 19 подключен к входу блока 23 преобразования последовательной комбинации в n-разрядную параллельную,

выход генератора 20 ПСП-2 подключен к входу первого запоминающего устройства 21,

выход первого запоминающего устройства 21 подключен к первому входу блока 22 сравнения,

первый выход блока 22 сравнения подключен ко второму входу генератора 17 ПСП-1, второй выход блока 22 сравнения подключен к входу блока управления 26, входящего в состав блока 25 приема информации,

выход блока 23 преобразования последовательной комбинации в n-разрядную параллельную подключен к входу второго запоминающего устройства 24,

выход второго запоминающего устройства 24 подключен ко второму входу блока 22 сравнения,

выход блока управления 26 подключен к входу блока памяти 12 стартовой последовательности,

первый выход блока избирания сигналов 27 подключен к первому входу модулятора-передатчика 29, входящего в состав блока 28 передатчика, второй выход блока избирания сигналов 27 подключен к первому входу согласующего устройства 15,

выход модулятора-передатчика 29 через линию связи 31 подключен к полосовому фильтру 33, входящему в состав блока 32 приемника,

выход накопителя хаотического сигнала 30 подключен ко второму входу модулятора-передатчика 29,

выход полосового фильтра 33 подключен к входу усилителя 34,

выход усилителя 34 подключен к первому входу первого умножителя 35 и к первому входу второго умножителя 36,

выход первого умножителя 35 подключен к входу первого интегратора 39,

выход второго умножителя 36 подключен к входу второго интегратора 40,

выход инвертора 37 подключен ко второму входу второго умножителя 36,

выход накопителя копии хаотического сигнала 38 подключен к входу инвертора 37 и ко второму входу первого умножителя 35,

выход первого интегратора 39 подключен к первому входу вычитающего устройства 41,

выход второго интегратора 40 подключен ко второму входу вычитающего устройства 41,

выход вычитающего устройства 41 подключен к входу решающего устройства 42,

выход решающего устройства 42 подключен ко второму входу блока 43 избирания сигналов,

первый выход блока 43 избирания сигналов, входящего в состав блока 47 передачи информации, подключен к первому входу модулятора-передатчика 45, второй выход блока 43 избирания сигналов подключен ко второму входу согласующего устройства 10,

выход модулятора-передатчика 45, входящего в состав блока 44 передатчика, через линию связи 48 подключен к входу полосового фильтра 50,

выход накопителя хаотического сигнала 46 подключен ко второму входу модулятора-передатчика 45,

выход полосового фильтра 50, входящего в состав блока 49 приемника, подключен к входу усилителя 51,

выход усилителя 51 подключен к первому входу первого умножителя 52 и к первому входу второго умножителя 53,

выход первого умножителя 52 подключен к входу первого интегратора 56,

выход второго умножителя 53 подключен к входу второго интегратора 57,

выход инвертора 54 подключен ко второму входу второго умножителя 53,

выход накопителя копии хаотического сигнала 55 подключен к входу инвертора 54 и ко второму входу первого умножителя 52,

выход первого интегратора 56 подключен к первому входу вычитающего устройства 58,

выход второго интегратора 57 подключен ко второму входу вычитающего устройства 58,

выход вычитающего устройства 58 подключен к входу решающего устройства 59,

выход решающего устройства 59 подключен ко второму входу блока 27 избирания сигналов.

Устройство имитозащиты контролируемых объектов с повышенной структурной скрытностью сигналов-переносчиков работает следующим образом.

При подаче сигнала запуска с блока управления 26, входящего в состав блока 25 приема информации, на вход блока памяти 12 стартовой последовательности, со второго выхода блока памяти 12 стартовой последовательности поступает команда приведения в исходное состояние блока обработки информации 11, для этого через генератор 16 ключа на входы сброса в исходное состояние генератора 17 ПСП-1, блока памяти 18 контрольного значения, генератора 20 ПСП-2, блока первого запоминающего устройства 21 подается команда «сброс», одновременно с первого выхода блока памяти 12 стартовой последовательности поступает хранящаяся в блоке двоичная стартовая последовательность на первый вход блока 13 преобразования n-разрядной параллельной комбинации в последовательную. При прохождении стартовой последовательности через блок 13 преобразования n-разрядной параллельной комбинации в последовательную, модулятор 14, согласующее устройство 15, блок избирания сигналов 27, модулятор-передатчик 29, ко второму входу модулятора-передатчика 29 одновременно с этим поступает хаотический сигнал с накопителя хаотического сигнала 30, входящих в состав блока 28 передатчика, в модуляторе-передатчике 29 осуществляется перемножение последовательности с хаотическим переносчиком. Сформированный таким образом сигнал через линию связи 31 поступает на вход полосового фильтра 33 и через усилитель 34 поступает на первые входы умножителей 35 и 36, входящих в состав блока 32 приемника. На вторые входы умножителей 35 и 36 поступают копии хаотического сигнала с накопителя копии хаотического сигнала 38, идентичному накопителю хаотического сигнала 30, причем на второй умножитель 36 копия хаотического сигнала поступает через инвертор 37. Далее с выходов умножителей 35 и 36 сигналы через интеграторы 39 и 40 подаются на вычитающее устройство 41. С выхода вычитающего устройства 41 сигнал поступает на решающее устройство 42, где происходит сравнение принятых уровней с пороговым значением напряжения и извлекается последовательность. Полученная последовательность с выхода решающего устройства 42 поступает на блок избирания сигналов 43, входящего в состав блока 47 передачи информации, и через согласующее устройство 10, демодулятор 8, блок 7 преобразования последовательной комбинации в n-разрядную параллельную стартовая последовательность записывается в блок памяти 6.

Из блока памяти 6 стартовая последовательность поступает в блок сравнения 3, где сравнивается с последовательностью, хранящейся в блоке памяти 2 стартовой последовательности (блоки памяти стартовой последовательности 2, 12 содержат одну и ту же стартовую последовательность) и, в случае совпадения последовательностей, блок сравнения 3 вырабатывает сигнал на установку в исходное состояние блока памяти 6 и генератора 4 ПСП-2, тем самым подготавливая генератор 4 ПСП-2 к приему посылки от генератора 17 ПСП-1. Одновременно с этим стартовая последовательность, поступившая из блока памяти 12 стартовой последовательности, запускает генератор 16 ключа, который вырабатывает комбинацию запуска генератора 17 ПСП-1. Сформированное в генераторе 17 ПСП-1 первое значение первой псевдослучайной последовательности (ПСП-1) сохраняется в блоке памяти 18 контрольного значения. Сохраненное в блоке памяти 18 контрольного значения первое значение ПСП-1 запускает генератор 20 ПСП-2 (функции генерации второй псевдослучайной последовательности генераторов 4, 20 ПСП-2 идентичны) выработанное генератором 20 ПСП-2 первое значение второй псевдослучайной последовательности (ПСП-2), сохраняется в блоке первого запоминающего устройства 21.

Одновременно с этим сформированное в генераторе 17 ПСП-1 первое значение ПСП-1 поступает на второй вход блока 13 преобразования n-разрядной параллельной комбинации в последовательную и через модулятор 14, согласующее устройство 15, блок избирания сигналов 27, модулятор-передатчик 29, ко второму входу модулятора-передатчика 29 одновременно с этим поступает хаотический сигнал с накопителя хаотического сигнала 30, в модуляторе-передатчике 29 осуществляется перемножение последовательности с хаотическим переносчиком. Сформированный таким образом сигнал через линию связи 31 поступает на вход полосового фильтра 33 и через усилитель 34 поступает на первые входы умножителей 35 и 36, входящие в состав блока 32 приемника. На вторые входы умножителей 35 и 36 поступают копии хаотического сигнала с накопителя копии хаотического сигнала 38, идентичному накопителю хаотического сигнала 30, причем на второй умножитель 36 копия хаотического сигнала поступает через инвертор 37. Далее с выходов умножителей 35 и 36 сигналы через интеграторы 39 и 40 подаются на вычитающее устройство 41. С выхода вычитающего устройства 41 сигнал поступает на решающее устройство 42, где происходит сравнение принятых уровней с пороговым значением напряжения и извлекается последовательность. Полученная последовательность с выхода решающего устройства 42 поступает на блок избирания сигналов 43, входящего в состав блока 47 передачи информации, согласующее устройство 10, демодулятор 8 поступает на вход блока 7 преобразования последовательной комбинации в n-разрядную параллельную. С выхода блока 7 преобразования последовательной комбинации в n-разрядную параллельную первое значение ПСП-1 поступает на вход блока памяти 6, где сохраняется. Хранящееся в блоке памяти 6 первое значение ПСП-1, сравнивается в блоке сравнения 3 с последовательностью, постоянно хранящейся в блоке памяти 2 стартовой последовательности. В случае несовпадения последовательностей, команда на установку датчика 1 в исходное состояние не вырабатывается, и первое значение ПСП-1, хранящееся в блоке памяти 6, дает команду генератору 4 ПСП-2 на формирование псевдослучайной последовательности. Сформированное в генераторе 4 ПСП-2 первое значение ПСП-2 поступает на вход блока 5 преобразования n-разрядной параллельной комбинации в последовательную и через модулятор 9, согласующее устройство 10, блок избирания сигналов 43, модулятор-передатчик 45, ко второму входу модулятора-передатчика 45 одновременно с этим поступает хаотический сигнал с накопителя хаотического сигнала 46, входящих в состав блока 44 передатчика, в модуляторе-передатчике 45 осуществляется перемножение последовательности с хаотическим переносчиком. Сформированный таким образом сигнал через линию связи 48 поступает на вход полосового фильтра 50 и через усилитель 51 поступает на первые входы умножителей 52 и 53, входящих в состав блока 49 приемника. На вторые входы умножителей 52 и 53 поступают копии хаотического сигнала с накопителя копии хаотического сигнала 55, идентичному накопителю хаотического сигнала 46, причем на второй умножитель 53 копия хаотического сигнала поступает через инвертор 54. Далее с выходов умножителей 52 и 53 сигналы через интеграторы 56 и 57 подаются на вычитающее устройство 58. С выхода вычитающего устройства 58 сигнал поступает на решающее устройство 59, где происходит сравнение принятых уровней с пороговым значением напряжения и извлекается последовательность. Полученная последовательность с выхода решающего устройства 59 поступает на блок избирания сигналов 27, входящего в состав транслятора 60, и через согласующее устройство 15, демодулятор 19 поступает на вход блока 23 преобразования последовательной комбинации в n-разрядную параллельную, преобразованное в блоке 23 преобразования последовательной комбинации в n-разрядную параллельную первое значение ПСП-2 записывается в блок второго запоминающего устройства 24.

Таким образом, в блоке первого запоминающего устройства 21 хранится первое значение ПСП-2, выработанное генератором 20 ПСП-2, входящим в состав блока обработки информации 11, а в блоке второго запоминающего устройства 24 хранится первое значение ПСП-2, выработанное генератором 4 ПСП-2, входящим в состав датчика 1. Исходя из того, что для генерации псевдослучайных последовательностей генераторами 4, 20 ПСП-2 используется одна и та же функция генерации псевдослучайной последовательности, выработанная генератором 17 ПСП-1, значения, находящиеся в блоках 21 и 24, должны быть одинаковы. Для проверки имитозащищенности линии связи 31, 48 и блока передачи 47 информации значения, хранящиеся в блоках 21, 24, сравниваются в блоке 22 сравнения. В случае совпадения значений блок 22 сравнения вырабатывает команду «Норма», запускающую генератор 17 ПСП-1 на выработку очередного значения ПСП-1. В случае несовпадения значений (нарушение режима имитозащиты), блок 22 сравнения выдает сигнал «Ошибка» на вход блока 26 управления, входящего в состав блока 25 приема информации.

Предлагаемое изобретение по сравнению с прототипом и другими техническими решениями имеет следующие преимущества:

- увеличение защищенности линии связи от встраивания и перехвата информации за счет использования накопителей хаотических сигналов;

- уменьшение вероятности перехвата и подмены псевдослучайных последовательностей, циркулирующих между датчиком и блоком контроля за счет использования накопителей хаотических сигналов.

Устройство имитозащиты контролируемых объектов с повышенной структурной скрытностью сигналов-переносчиков состоит из датчика, содержащего в себе: блок памяти стартовой последовательности, блок сравнения, генератор второй псевдослучайной последовательности (генератор ПСП-2), блок преобразования n-разрядной параллельной комбинации в последовательную, блок памяти, блок преобразования последовательной комбинации в n-разрядную параллельную, демодулятор, модулятор, согласующее устройство, блока обработки информации, содержащего в себе: блок памяти стартовой последовательности, блок преобразования n-разрядной параллельной комбинации в последовательную, модулятор, согласующее устройство, генератор ключа, генератор первой псевдослучайной последовательности (генератор ПСП-1), блок памяти контрольного значения, демодулятор, генератор второй псевдослучайной последовательности (генератор ПСП-2), блок первого запоминающего устройства, блок сравнения, блок преобразования последовательной комбинации в n-разрядную параллельную, блок второго запоминающего устройства, блока приема информации, содержащего в себе блок управления, блока избирания сигналов, блока передатчика, содержащего в себе: модулятор-передатчик, накопитель хаотического сигнала, линии связи, блока приемника, содержащего в себе: полосовой фильтр, усилитель, первый умножитель, второй умножитель, инвертор, накопитель копии хаотического сигнала, первый интегратор, второй интегратор, вычитающее устройство, решающее устройство, блока избирания сигналов, блока передатчика, содержащего в себе: модулятор-передатчик, накопитель хаотического сигнала, входящих в состав блока передачи информации, линии связи, блока приемника, содержащего в себе: полосовой фильтр, усилитель, первый умножитель, второй умножитель, инвертор, накопитель копии хаотического сигнала, первый интегратор, второй интегратор, вычитающее устройство, решающее устройство, входящих в состав транслятора, причем выход блока памяти стартовой последовательности, входящего в состав датчика, подключен к первому входу блока сравнения, выход блока сравнения подключен к входу сброса в исходное состояние блока памяти и входу сброса в исходное состояние генератора ПСП-2, выход генератора ПСП-2 подключен к входу блока преобразования n-разрядной параллельной комбинации в последовательную, выход блока преобразования n-разрядной параллельной комбинации в последовательную подключен к входу модулятора, выход блока памяти подключен к входу блока сравнения и к входу запуска генератора ПСП-2, выход блока преобразования последовательной комбинации в n-разрядную параллельную подключен к входу блока памяти, выход демодулятора подключен к входу блока преобразования последовательной комбинации в n-разрядную параллельную, выход модулятора подключен к первому входу согласующего устройства, первый выход согласующего устройства подключен к входу демодулятора, второй выход согласующего устройства подключен к первому входу блока избирания сигналов, входящего в состав блока передачи информации, первый выход блока памяти стартовой последовательности, входящего в состав блока обработки информации, подключен к первому входу блока преобразования n-разрядной параллельной комбинации в последовательную, второй выход блока памяти стартовой последовательности подключен к входу генератора ключа, выход блока преобразования n-разрядной параллельной комбинации в последовательную подключен к входу модулятора, выход модулятора подключен к первому входу согласующего устройства, первый выход согласующего устройства подключен к входу демодулятора, второй выход согласующего устройства подключен к первому входу блока избирания сигналов, входящего в состав транслятора, первый выход генератора ключа подключен к входу запуска генератора ПСП-1, второй выход генератора ключа подключен к входу сброса в исходное состояние генератора ПСП-1, входу сброса в исходное состояние блока памяти контрольного значения, входу сброса в исходное состояние генератора ПСП-2, входу сброса в исходное состояние блока первого запоминающего устройства, выход генератора ПСП-1 подключен к входу блока памяти контрольного значения и ко второму входу блока преобразования n-разрядной параллельной комбинации в последовательную, выход блока памяти контрольного значения подключен к входу запуска генератора ПСП-2, выход демодулятора подключен к входу блока преобразования последовательной комбинации в n-разрядную параллельную, выход генератора ПСП-2 подключен к входу первого запоминающего устройства, выход первого запоминающего устройства подключен к первому входу блока сравнения, первый выход блока сравнения подключен ко второму входу генератора ПСП-1, второй выход блока сравнения подключен к входу блока управления, входящего в состав блока приема информации, выход блока преобразования последовательной комбинации в n-разрядную параллельную подключен к входу второго запоминающего устройства, выход второго запоминающего устройства подключен ко второму входу блока сравнения, выход блока управления подключен к входу блока памяти стартовой последовательности, первый выход блока избирания сигналов подключен к первому входу модулятора-передатчика, входящего в состав блока передатчика, второй выход блока избирания сигналов подключен к первому входу согласующего устройства, выход модулятора-передатчика через линию связи подключен к полосовому фильтру, входящему в состав блока приемника, выход накопителя хаотического сигнала подключен ко второму входу модулятора-передатчика, выход полосового фильтра подключен к входу усилителя, выход усилителя подключен к первому входу первого умножителя и к первому входу второго умножителя, выход первого умножителя подключен к входу первого интегратора, выход второго умножителя подключен к входу второго интегратора, выход инвертора подключен ко второму входу второго умножителя, выход накопителя копии хаотического сигнала подключен к входу инвертора и ко второму входу первого умножителя, выход первого интегратора подключен к первому входу вычитающего устройства, выход второго интегратора подключен ко второму входу вычитающего устройства, выход вычитающего устройства подключен к входу решающего устройства, выход решающего устройства подключен ко второму входу блока избирания сигналов, первый выход блока избирания сигналов, входящего в состав блока передачи информации, подключен к первому входу модулятора-передатчика, второй выход блока избирания сигналов подключен ко второму входу согласующего устройства, выход модулятора-передатчика, входящего в состав блока передатчика, через линию связи подключен к входу полосового фильтра, выход накопителя хаотического сигнала подключен ко второму входу модулятора-передатчика, выход полосового фильтра, входящего в состав блока приемника, подключен к входу усилителя, выход усилителя подключен к первому входу первого умножителя и к первому входу второго умножителя, выход первого умножителя подключен к входу первого интегратора, выход второго умножителя подключен к входу второго интегратора, выход инвертора подключен ко второму входу второго умножителя, выход накопителя копии хаотического сигнала подключен к входу инвертора и ко второму входу первого умножителя, выход первого интегратора подключен к первому входу вычитающего устройства, выход второго интегратора подключен ко второму входу вычитающего устройства, выход вычитающего устройства подключен к входу решающего устройства, выход решающего устройства подключен ко второму входу блока избирания сигналов.