Результат интеллектуальной деятельности: БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИРУЮЩИМИ ЦЕПЯМИ КОРРЕКЦИИ В МОСТОВОМ ВХОДНОМ ДИФФЕРЕНЦИАЛЬНОМ КАСКАДЕ

Вид РИД

Изобретение

Изобретение относится к области радиотехники и может быть использовано в различных аналоговых и аналого-цифровых интерфейсах для обработки сигналов датчиков физических величин.

В современной радиоэлектронной аппаратуре, приборостроении и измерительной технике находят широкое применение быстродействующие операционные усилители (ОУ), которые определяют динамические параметры многих аналого-цифровых преобразователей (АЦП), драйверов линий связи, устройств частотной селекции и т.п. Методам повышения максимальной скорости нарастания выходного напряжения ОУ (SR) посвящено значительное количество патентов, монографий и статей, в т.ч. [1-18].

Сегодня широкое распространение в микроэлектронике получили операционные усилители с двухкаскадной архитектурой, которая включает мостовой входной дифференциальный каскад (ДК), два токовых зеркала и буферный усилитель [1-18]. Предполагаемое изобретение относится к данному классу устройств.

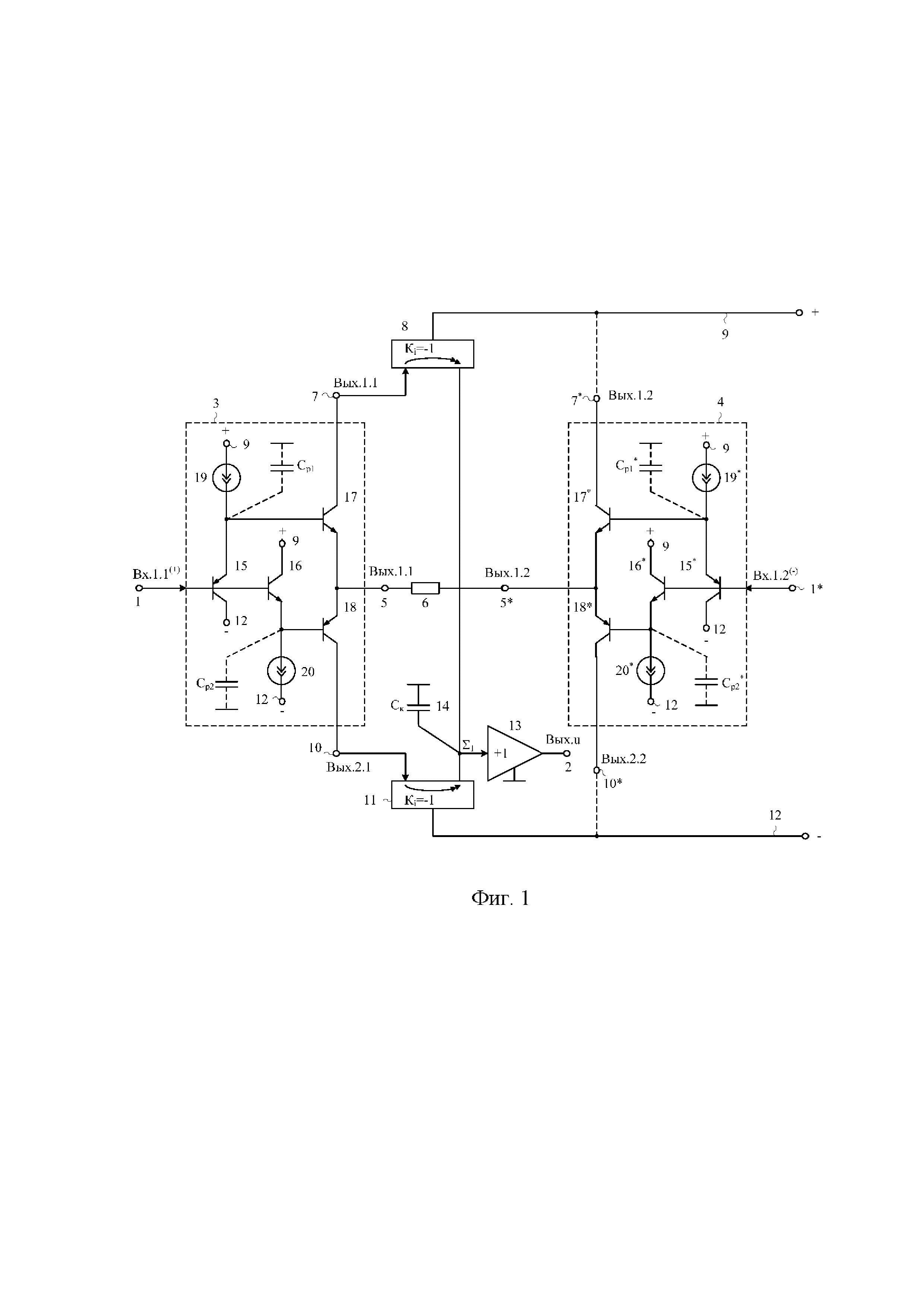

Ближайшим прототипом (фиг. 1) заявляемого устройства является ОУ по патенту US 5.374.897, fig. 2, 1994 г. Кроме этого данная схема представлена в US 6.542.032, fig.2, 2003 г., US 5.512.859, fig.4, 1996 г. ОУ-прототип (фиг. 1) содержит неинвертирующий 1 и инвертирующий 1* входы устройства, потенциальный выход устройства 2, первый 3 и второй 4 идентичные буферные усилители, входящие в структуру входного мостового дифференциального каскада, входы которых связаны с соответствующими неинвертирующим 1 и инвертирующим 1* входами устройства, а соответствующие потенциальные выходы 5 и 5* соединены друг с другом через токоограничивающий резистор 6, первый 7 токовый выход первого 3 буферного усилителя соединен со входом первого 8 токового зеркала, согласованного с первой 9 шиной источника питания, второй 10 токовый выход первого 3 буферного усилителя соединен со входом второго 11 токового зеркала, согласованного со второй 12 шиной источника питания, выходы первого 8 и второго 11 токовых зеркал соединены друг с другом и подключены к выходу устройства 2 через выходной усилитель 13 и связаны с интегрирующим корректирующим конденсатором 14, причем первый 3 буферный усилитель включает первый 15 и второй 16 входные транзисторы, базы которых подключены к неинвертирующему 1 входу устройства, коллектор первого 15 входного транзистора соединен со второй 12 шиной источника питания, коллектор второго 16 входного транзистора соединен с первой 9 шиной источника питания, первый 17 и второй 18 выходные транзисторы, объединенные эмиттеры которых подключены к потенциальному выходу 5 первого 3 буферного усилителя, база первого 17 выходного транзистора соединена с эмиттером первого 15 входного транзистора и через первый источник опорного тока 19 связана с первой 9 шиной источника питания, база второго 18 выходного транзистора соединена с эмиттером второго 16 входного транзистора и через второй 20 источник опорного тока связана со второй 12 шиной источника питания, коллектор первого 17 выходного транзистора соединен с первым 7 токовым выходом первого 3 буферного усилителя, коллектор второго 18 выходного транзистора соединен со вторым 10 токовым выходом первого 3 буферного усилителя, кроме этого, второй 4 буферный усилитель идентичен первому 3 буферному усилителю и включает третий 15* и четвертый 16* входные транзисторы, базы которых подключены к инвертирующему 1* входу устройства, коллектор третьего 15* входного транзистора соединен со второй 12 шиной источника питания, коллектор четвертого 16* входного транзистора соединен с первой 9 шиной источника питания, третий 17* и четвертый 18* выходные транзисторы, объединенные эмиттеры которых подключены к потенциальному выходу 5* второго 4 буферного усилителя, база третьего 17* выходного транзистора соединена с эмиттером третьего 15* входного транзистора и через третий 19* источник опорного тока связана с первой 9 шиной источника питания, база четвертого 18* выходного транзистора соединена с эмиттером четвертого 16* входного транзистора и через четвертый 20* источник опорного тока связана со второй 12 шиной источника питания, коллектор третьего 17* выходного транзистора соединен с первым 7* токовым выходом второго 4 буферного усилителя, коллектор четвертого 18* выходного транзистора соединен со вторым 10* токовым выходом второго 4 буферного усилителя, причем первый 7* токовый выход второго 4 буферного усилителя согласован с первой 9 шиной источника питания, а второй 10* токовый выход второго 4 буферного усилителя согласован со второй 12 шиной источника питания.

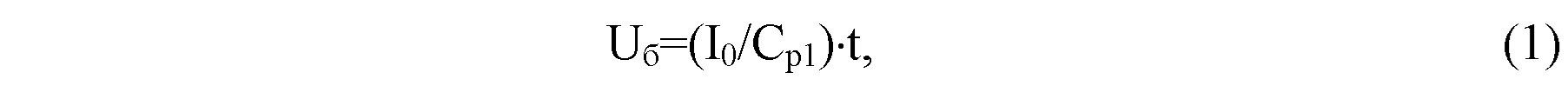

Следует отметить, что архитектура ОУ на чертеже фиг. 1 с мостовым входным дифференциальным каскадом, включающем четыре эмиттерных повторителя на транзисторах 15 и 16, 15* и 16*, является основой многих серийных аналоговых микросхем [1-18]. Однако из-за наличия паразитных емкостей Cp1, Cp2, Cp1*, Cp2* в цепи эмиттеров вышеназванных входных эмиттерных повторителей известные схемы ОУ не реализуют предельные параметры по максимальной скорости нарастания выходного напряжения (SR). Действительно, входной положительный импульсный сигнал большой амплитуды на базах первого 15 и второго 16 входных транзисторов в ОУ со 100% отрицательной обратной связью передается на базу первого 17 выходного транзистора как «пилообразное» напряжение:

где  – статический ток первого 19 источника опорного тока; Ср1 – суммарная паразитная емкость в эмиттере первого 15 входного транзистора, зависящая от паразитной емкости первого 19 источника опорного тока

– статический ток первого 19 источника опорного тока; Ср1 – суммарная паразитная емкость в эмиттере первого 15 входного транзистора, зависящая от паразитной емкости первого 19 источника опорного тока  и емкости коллектор-база первого 17 выходного транзистора. Как следствие, это ограничивает производную тока коллектора первого 17 выходного транзистора (см. уравнение (1)), далее – производную выходного тока первого 8 токового зеркала и тока перезаряда интегрирующего корректирующего конденсатора ОУ 14. Эти эффекты ограничивают предельные значения SR ОУ. Данный недостаток присущ всем известным архитектурам ОУ рассматриваемого класса [1-18]. На практике он минимизируется за счет увеличения численных значений

и емкости коллектор-база первого 17 выходного транзистора. Как следствие, это ограничивает производную тока коллектора первого 17 выходного транзистора (см. уравнение (1)), далее – производную выходного тока первого 8 токового зеркала и тока перезаряда интегрирующего корректирующего конденсатора ОУ 14. Эти эффекты ограничивают предельные значения SR ОУ. Данный недостаток присущ всем известным архитектурам ОУ рассматриваемого класса [1-18]. На практике он минимизируется за счет увеличения численных значений  =I19, что увеличивает входные токи ОУ и его общее энергопотребление. Возможно также применение более высокочастотных и, как следствие более дорогих технологий, уменьшающих паразитные емкости Cp1, Cp2, Cp1*, Cp2*.

=I19, что увеличивает входные токи ОУ и его общее энергопотребление. Возможно также применение более высокочастотных и, как следствие более дорогих технологий, уменьшающих паразитные емкости Cp1, Cp2, Cp1*, Cp2*.

Таким образом, существенный недостаток известного ОУ фиг. 1 состоит в том, что при его инвертирующем (или неинвертирующем) включении с традиционными резисторами общей отрицательной обратной связи, он имеет невысокую скорость нарастания выходного напряжения в режиме большого сигнала. Это обусловлено малыми значениями токов перезаряда его интегрирующего корректирующего конденсатора 14. По многим причинам этот ток не может выбираться большим. Кроме этого, ОУ-прототип фиг. 1 характеризуется разными значениями SR при положительной (SR(+)) и отрицательной (SR(-)) полярностях входного импульсного сигнала, что обусловлено неодинаковыми значениями емкостей паразитных конденсаторов Cp1 Cp2, Cp1*

Cp2, Cp1* Cp2*, которые определяются неидентичностью топологий n-p-n и p-n-p транзисторов.

Cp2*, которые определяются неидентичностью топологий n-p-n и p-n-p транзисторов.

Основная задача предполагаемого изобретения состоит в повышении предельных значений SR без ухудшения энергетических параметров ОУ в статическом режиме, а также без использования дорогостоящих СВЧ технологических процессов его изготовления, уменьшающих паразитные емкости Cp1, Cp2, Cp1*, Cp2*.

Поставленная задача достигается тем, что в операционном усилителе фиг.1, содержащем неинвертирующий 1 и инвертирующий 1* входы устройства, потенциальный выход устройства 2, первый 3 и второй 4 идентичные буферные усилители, входящие в структуру входного мостового дифференциального каскада, входы которых связаны с соответствующими неинвертирующим 1 и инвертирующим 1* входами устройства, а соответствующие потенциальные выходы 5 и 5* соединены друг с другом через токоограничивающий резистор 6, первый 7 токовый выход первого 3 буферного усилителя соединен со входом первого 8 токового зеркала, согласованного с первой 9 шиной источника питания, второй 10 токовый выход первого 3 буферного усилителя соединен со входом второго 11 токового зеркала, согласованного со второй 12 шиной источника питания, выходы первого 8 и второго 11 токовых зеркал соединены друг с другом и подключены к выходу устройства 2 через выходной усилитель 13 и связаны с интегрирующим корректирующим конденсатором 14, причем первый 3 буферный усилитель включает первый 15 и второй 16 входные транзисторы, базы которых подключены к неинвертирующему 1 входу устройства, коллектор первого 15 входного транзистора соединен со второй 12 шиной источника питания, коллектор второго 16 входного транзистора соединен с первой 9 шиной источника питания, первый 17 и второй 18 выходные транзисторы, объединенные эмиттеры которых подключены к потенциальному выходу 5 первого 3 буферного усилителя, база первого 17 выходного транзистора соединена с эмиттером первого 15 входного транзистора и через первый источник опорного тока 19 связана с первой 9 шиной источника питания, база второго 18 выходного транзистора соединена с эмиттером второго 16 входного транзистора и через второй 20 источник опорного тока связана со второй 12 шиной источника питания, коллектор первого 17 выходного транзистора соединен с первым 7 токовым выходом первого 3 буферного усилителя, коллектор второго 18 выходного транзистора соединен со вторым 10 токовым выходом первого 3 буферного усилителя, кроме этого, второй 4 буферный усилитель идентичен первому 3 буферному усилителю и включает третий 15* и четвертый 16* входные транзисторы, базы которых подключены к инвертирующему 1* входу устройства, коллектор третьего 15* входного транзистора соединен со второй 12 шиной источника питания, коллектор четвертого 16* входного транзистора соединен с первой 9 шиной источника питания, третий 17* и четвертый 18* выходные транзисторы, объединенные эмиттеры которых подключены к потенциальному выходу 5* второго 4 буферного усилителя, база третьего 17* выходного транзистора соединена с эмиттером третьего 15* входного транзистора и через третий 19* источник опорного тока связана с первой 9 шиной источника питания, база четвертого 18* выходного транзистора соединена с эмиттером четвертого 16* входного транзистора и через четвертый 20* источник опорного тока связана со второй 12 шиной источника питания, коллектор третьего 17* выходного транзистора соединен с первым 7* токовым выходом второго 4 буферного усилителя, коллектор четвертого 18* выходного транзистора соединен со вторым 10* токовым выходом второго 4 буферного усилителя, причем первый 7* токовый выход второго 4 буферного усилителя согласован с первой 9 шиной источника питания, а второй 10* токовый выход второго 4 буферного усилителя согласован со второй 12 шиной источника питания, предусмотрены новые элементы и связи – в схеме первого 3 буферного усилителя между эмиттером и базой первого 15 входного транзистора включены последовательно соединенные первый 21 дополнительный корректирующий конденсатор и первый 22 дополнительный корректирующий резистор, а между эмиттером и базой второго 16 входного транзистора включены последовательно соединенные второй 23 дополнительный корректирующий конденсатор и второй 24 дополнительный корректирующий резистор, кроме этого, в схему второго 4 буферного усилителя между эмиттером и базой третьего 15* входного транзистора включены последовательно соединенные третий 21* дополнительный корректирующий конденсатор и третий 22* дополнительный корректирующий резистор, а между эмиттером и базой четвертого 16* входного транзистора включены последовательно соединенные четвертый 23* дополнительный корректирующий конденсатор и четвертый 24* дополнительный корректирующий резистор.

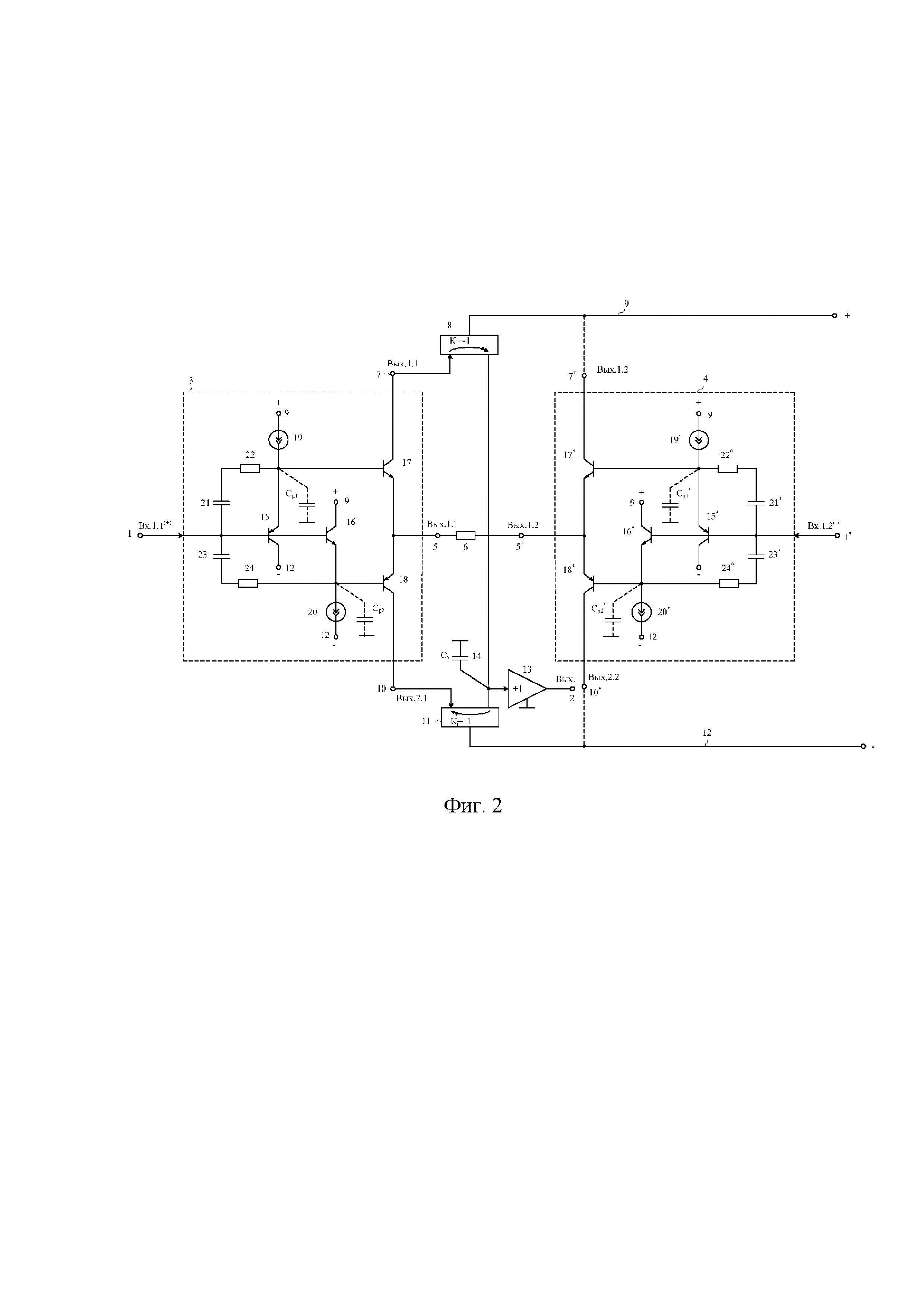

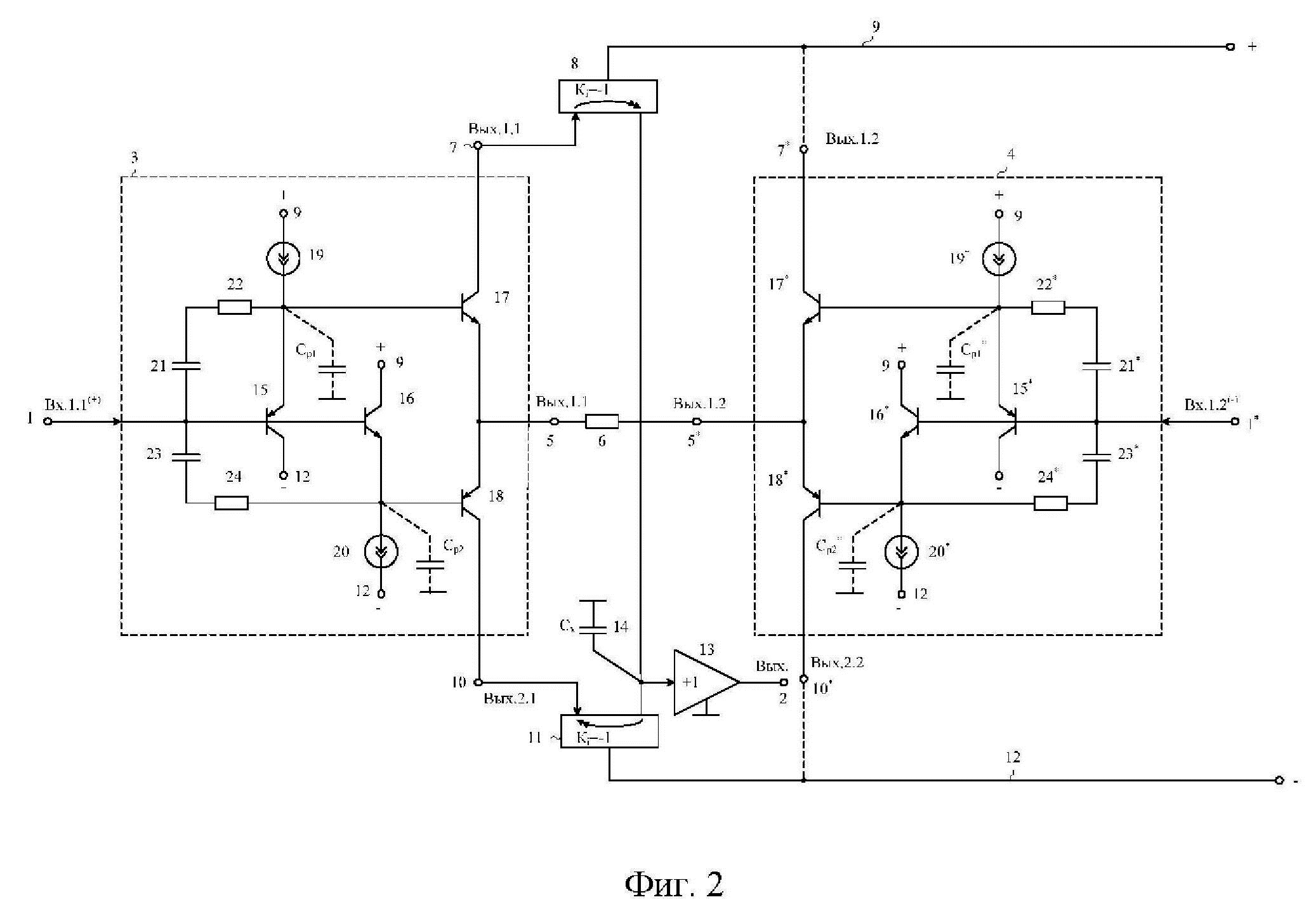

На чертеже фиг. 1 показана схема ОУ-прототипа, а на чертеже фиг. 2 – схема заявляемого быстродействующего операционного усилителя в соответствии с формулой изобретения.

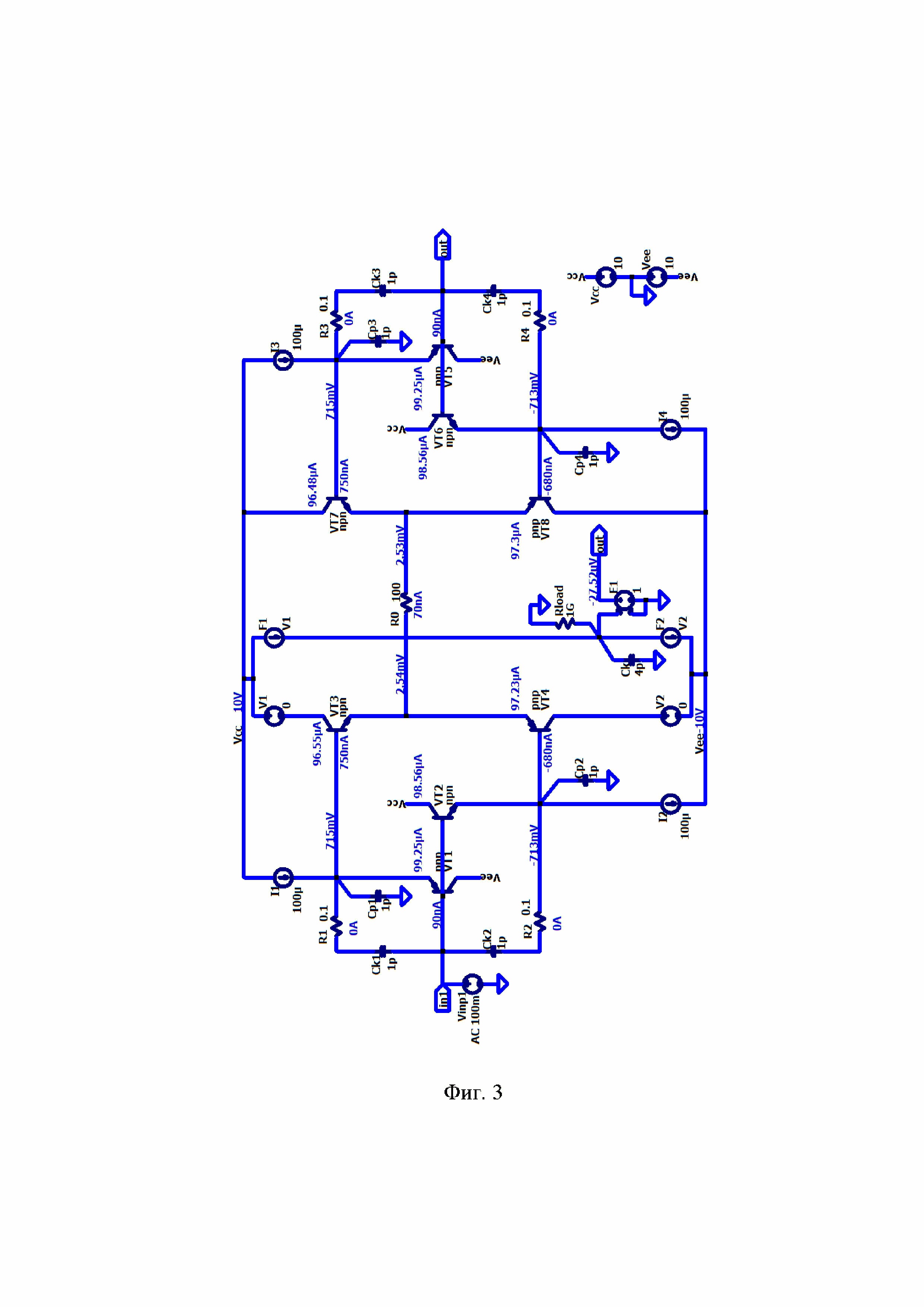

На чертеже фиг. 3 приведена схема для моделирования быстродействующего ОУ фиг. 2 в среде LTspice при t=27oC, +Vcc=-Vee=10 В, Сk=4 пФ, Сp1÷Сp4=1 пФ, R0=100 Ом, Rload=1 ГОм, Сk1÷Сk4=1 пФ, R1÷R4=0,1 Ом, I1÷I4=100 мкА на моделях транзисторов базового матричного кристалла MH2XA031 (ОАО «Интеграл», г. Минск).

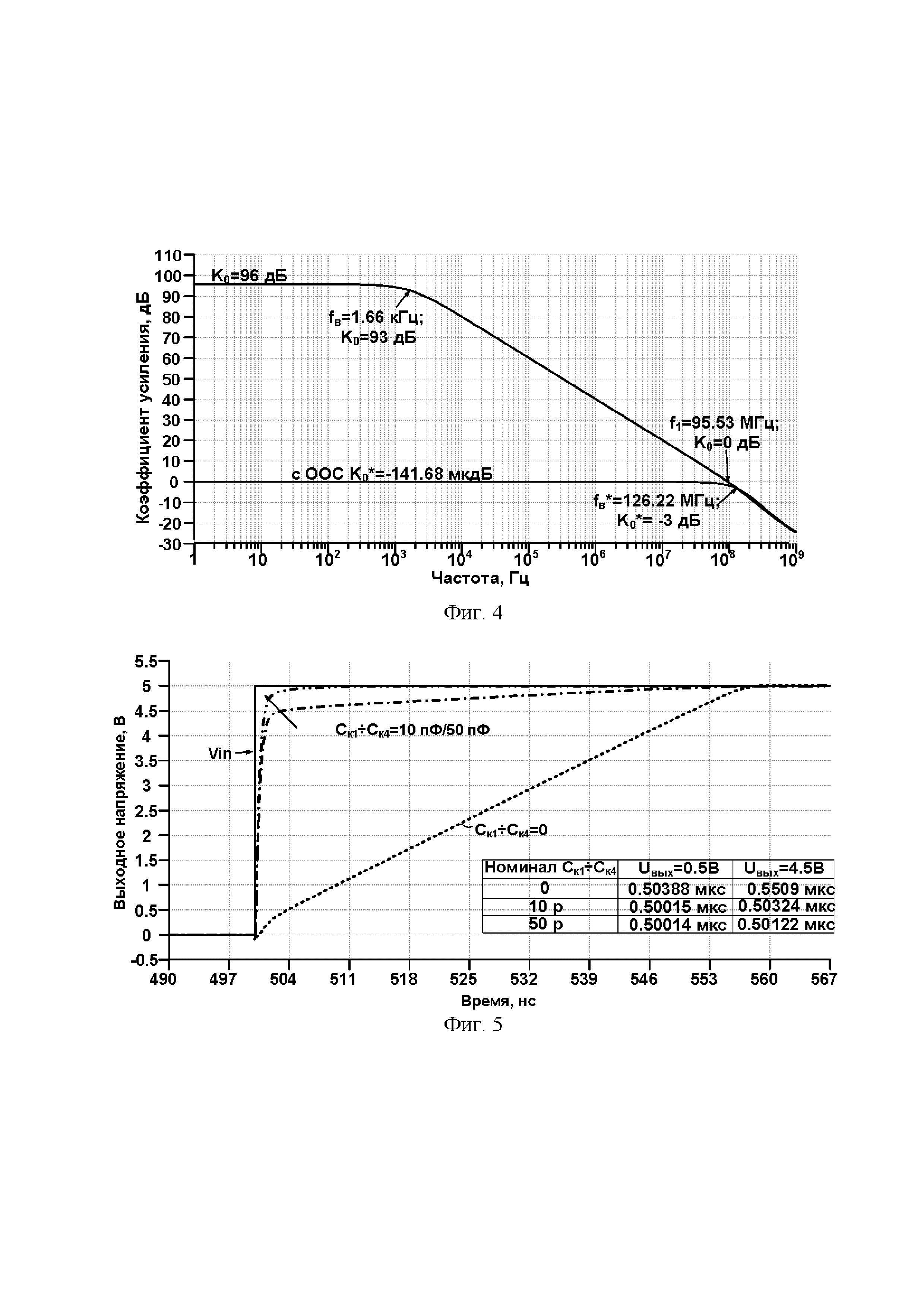

На чертеже фиг. 4 представлена логарифмическая амплитудно-частотная характеристика (ЛАЧХ) быстродействующего ОУ фиг. 3 в среде LTspice.

На чертеже фиг. 5 показана переходная характеристика переднего фронта быстродействующего ОУ фиг. 3 при разных значениях емкостей дополнительных корректирующих конденсаторов Сk1÷Сk4=0/10 пФ/50 пФ.

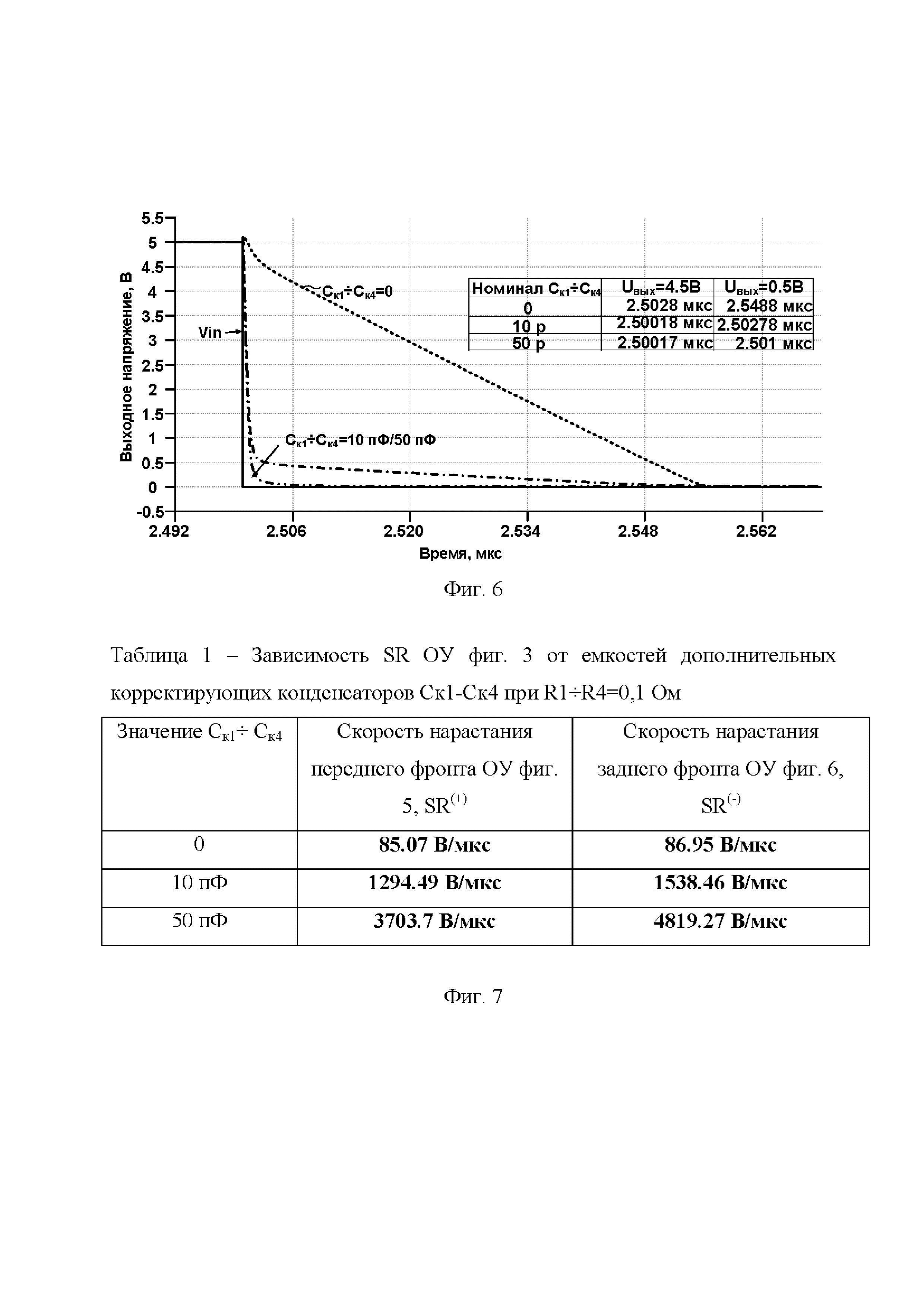

На чертеже фиг. 6 представлена переходная характеристика заднего фронта быстродействующего ОУ фиг. 3 при разных значениях емкостей дополнительных корректирующих конденсаторов Сk1÷Сk4=0/10 пФ/50 пФ.

На чертеже фиг.7 приведена таблица зависимости SR ОУ фиг. 3 от емкостей дополнительных корректирующих конденсаторов Сk1÷Сk4.

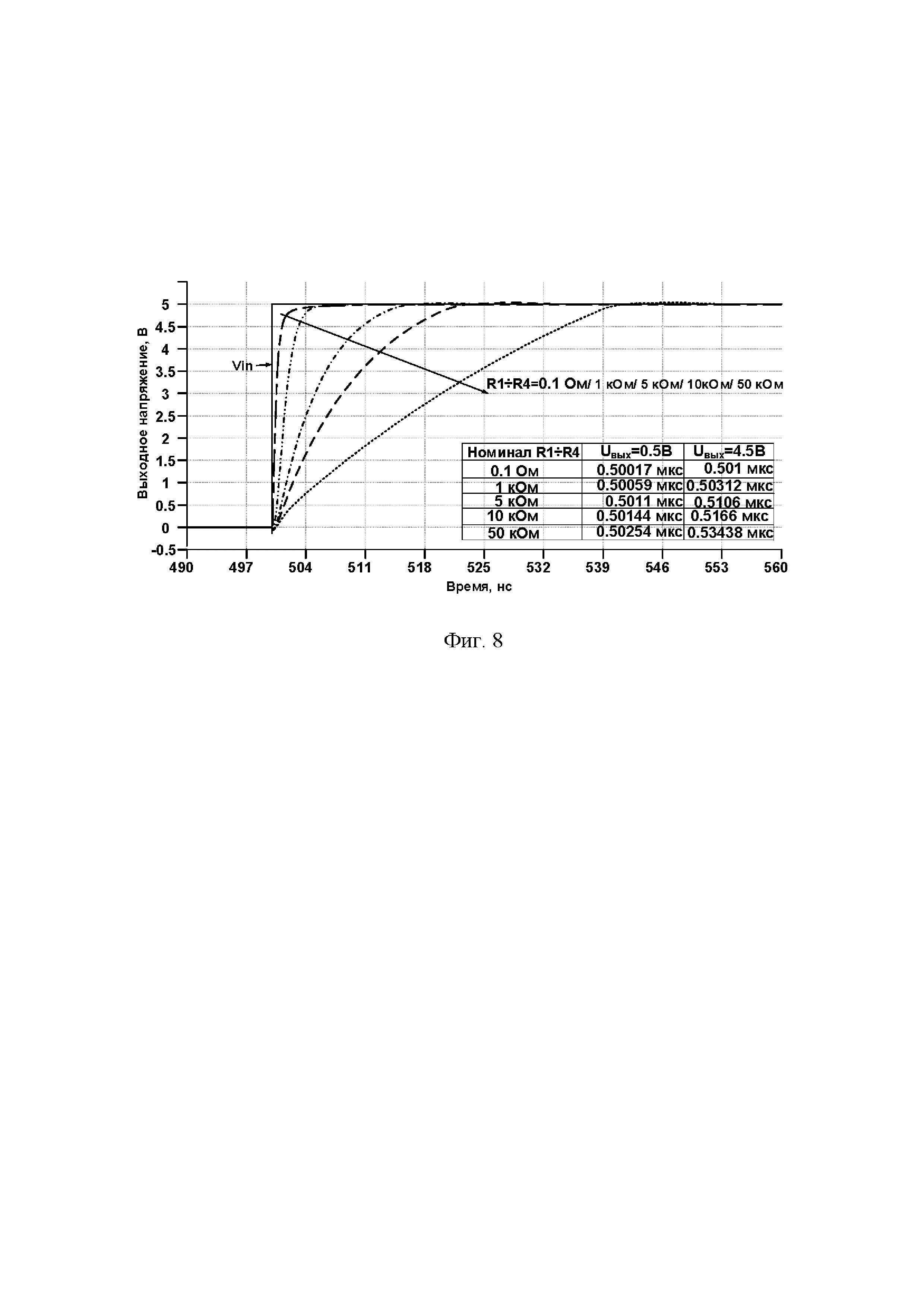

На чертеже фиг. 8 показана переходная характеристика переднего фронта быстродействующего ОУ фиг. 3 при t=27oC, +Vcc=-Vee=10 В, Сk=4 пФ, Сp1÷Сp4=1 пФ, R0=100 Ом, Rload=1 ГОм, Сk1÷Сk4=50 пФ для разных сопротивлений дополнительных корректирующих резисторов R1÷R4=0.1 Ом/ 1кОм/ 5кОм/ 10кОм/ 50кОм.

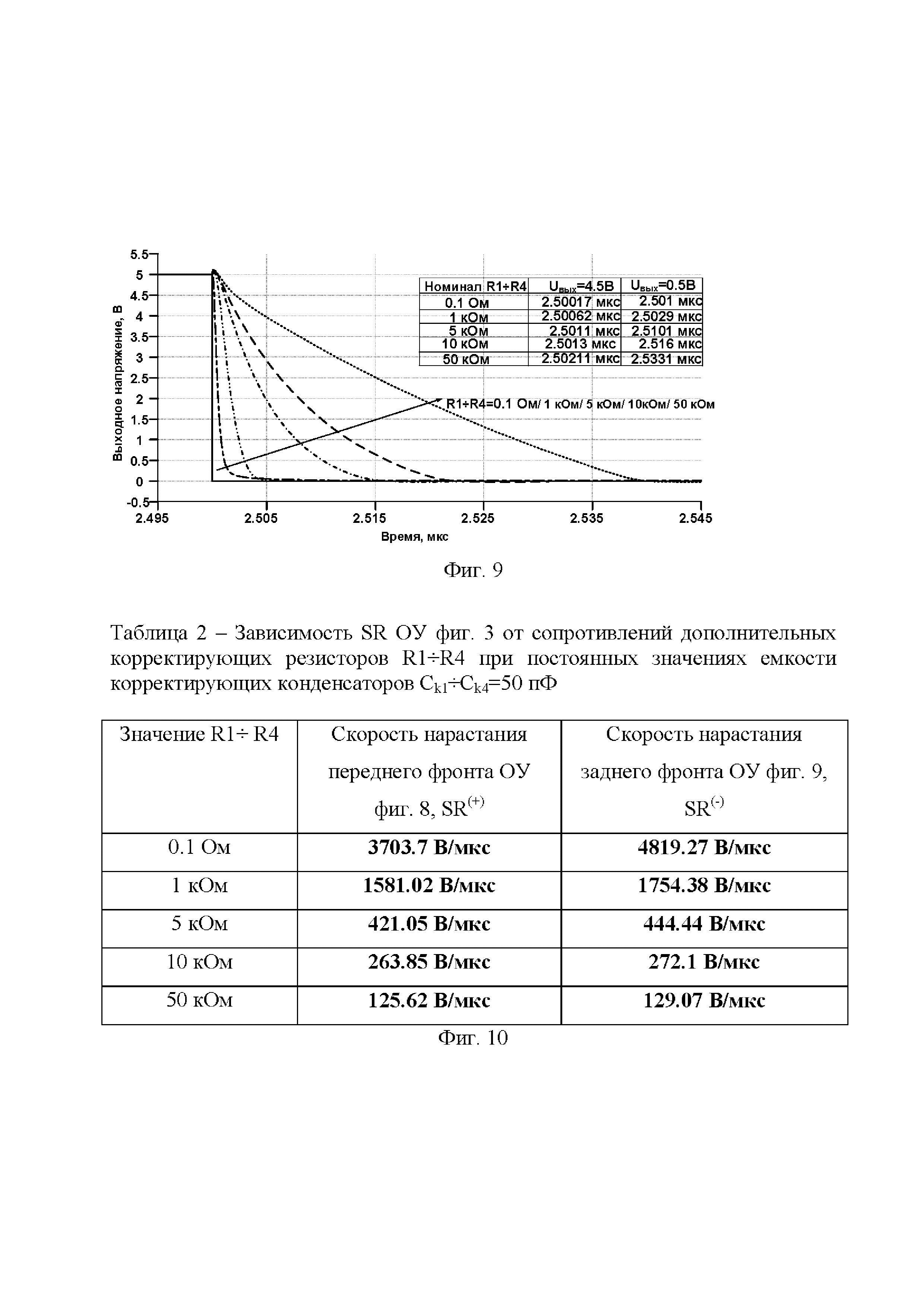

На чертеже фиг. 9 представлена переходная характеристика заднего фронта быстродействующего ОУ фиг. 4 при Сk1÷Сk4=50 пФ и разных сопротивлениях дополнительных корректирующих резисторов R1÷R4=0.1 Ом/ 1кОм/ 5кОм/ 10кОм/ 50кОм.

На чертеже фиг. 10 приведена таблица зависимости SR ОУ фиг. 3 от сопротивлений дополнительных корректирующих резисторов R1÷R4 при постоянных значениях емкости дополнительных корректирующих конденсаторов Сk1÷Сk4=50 пФ.

Быстродействующий операционный усилитель с дифференцирующими цепями коррекции в мостовом входном дифференциальном каскаде фиг. 2 содержит неинвертирующий 1 и инвертирующий 1* входы устройства, потенциальный выход устройства 2, первый 3 и второй 4 идентичные буферные усилители, входящие в структуру входного мостового дифференциального каскада, входы которых связаны с соответствующими неинвертирующим 1 и инвертирующим 1* входами устройства, а соответствующие потенциальные выходы 5 и 5* соединены друг с другом через токоограничивающий резистор 6, первый 7 токовый выход первого 3 буферного усилителя соединен со входом первого 8 токового зеркала, согласованного с первой 9 шиной источника питания, второй 10 токовый выход первого 3 буферного усилителя соединен со входом второго 11 токового зеркала, согласованного со второй 12 шиной источника питания, выходы первого 8 и второго 11 токовых зеркал соединены друг с другом и подключены к выходу устройства 2 через выходной усилитель 13 и связаны с интегрирующим корректирующим конденсатором 14, причем первый 3 буферный усилитель включает первый 15 и второй 16 входные транзисторы, базы которых подключены к неинвертирующему 1 входу устройства, коллектор первого 15 входного транзистора соединен со второй 12 шиной источника питания, коллектор второго 16 входного транзистора соединен с первой 9 шиной источника питания, первый 17 и второй 18 выходные транзисторы, объединенные эмиттеры которых подключены к потенциальному выходу 5 первого 3 буферного усилителя, база первого 17 выходного транзистора соединена с эмиттером первого 15 входного транзистора и через первый источник опорного тока 19 связана с первой 9 шиной источника питания, база второго 18 выходного транзистора соединена с эмиттером второго 16 входного транзистора и через второй 20 источник опорного тока связана со второй 12 шиной источника питания, коллектор первого 17 выходного транзистора соединен с первым 7 токовым выходом первого 3 буферного усилителя, коллектор второго 18 выходного транзистора соединен со вторым 10 токовым выходом первого 3 буферного усилителя, кроме этого, второй 4 буферный усилитель идентичен первому 3 буферному усилителю и включает третий 15* и четвертый 16* входные транзисторы, базы которых подключены к инвертирующему 1* входу устройства, коллектор третьего 15* входного транзистора соединен со второй 12 шиной источника питания, коллектор четвертого 16* входного транзистора соединен с первой 9 шиной источника питания, третий 17* и четвертый 18* выходные транзисторы, объединенные эмиттеры которых подключены к потенциальному выходу 5* второго 4 буферного усилителя, база третьего 17* выходного транзистора соединена с эмиттером третьего 15* входного транзистора и через третий 19* источник опорного тока связана с первой 9 шиной источника питания, база четвертого 18* выходного транзистора соединена с эмиттером четвертого 16* входного транзистора и через четвертый 20* источник опорного тока связана со второй 12 шиной источника питания, коллектор третьего 17* выходного транзистора соединен с первым 7* токовым выходом второго 4 буферного усилителя, коллектор четвертого 18* выходного транзистора соединен со вторым 10* токовым выходом второго 4 буферного усилителя, причем первый 7* токовый выход второго 4 буферного усилителя согласован с первой 9 шиной источника питания, а второй 10* токовый выход второго 4 буферного усилителя согласован со второй 12 шиной источника питания. В схеме первого 3 буферного усилителя между эмиттером и базой первого 15 входного транзистора включены последовательно соединенные первый 21 дополнительный корректирующий конденсатор и первый 22 дополнительный корректирующий резистор, а между эмиттером и базой второго 16 входного транзистора включены последовательно соединенные второй 23 дополнительный корректирующий конденсатор и второй 24 дополнительный корректирующий резистор, кроме этого, в схему второго 4 буферного усилителя между эмиттером и базой третьего 15* входного транзистора включены последовательно соединенные третий 21* дополнительный корректирующий конденсатор и третий 22* дополнительный корректирующий резистор, а между эмиттером и базой четвертого 16* входного транзистора включены последовательно соединенные четвертый 23* дополнительный корректирующий конденсатор и четвертый 24* дополнительный корректирующий резистор.

Рассмотрим работу предлагаемого быстродействующего ОУ на чертеже фиг. 2.

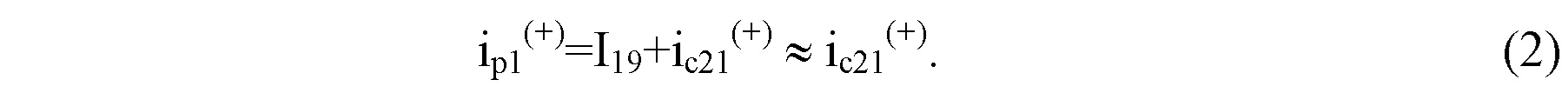

При большом импульсном сигнале на неинвертирующем входе 1 ОУ в схеме со 100% отрицательной обратной связью первый 15 входной транзистор запирается, а паразитный конденсатор Ср1 заряжается током первого 19 источника опорного тока, к которому добавляется значительный импульсный ток ic21(+)>>I19 через первый 21 дополнительный корректирующий конденсатор:

Как следствие, потенциал на базе первого 17 выходного транзистора uA имеет «более прямоугольную форму», что приводит к быстрому изменению его тока эмиттера через токоограничивающий резистор 6 и, как следствие, входного и выходного токов iвых.8(+) первого 8 токового зеркала. В результате интегрирующий корректирующий конденсатор 14 перезаряжается относительно большим импульсным током iвых.8(+), что повышает максимальную скорость нарастания выходного напряжения ОУ.

Предлагаемая схема ОУ фиг. 2 допускает независимую регулировку SR при разных полярностях входного импульсного сигнала, что обеспечивается соответствующим выбором емкостей первого 21 и второго 23 дополнительных корректирующих конденсаторов, а также первого 22 и второго 24 дополнительных корректирующих резисторов, которые в этом случае должны быть не одинаковы.

О высоком быстродействии заявляемого ОУ свидетельствуют графики переходных процессов на чертежах фиг. 5, фиг. 6 и данные таблицы фиг. 7, из которых можно определить, что максимальная скорость нарастания выходного напряжения предлагаемого ОУ увеличивается с 85-86 В/мкс до 3700-4800 В/мкс. При этом за счет изменения сопротивлений первого 22 и второго 24 дополнительных корректирующих резисторов можно управлять величиной SR в широком диапазоне (см. табл. 2, фиг. 10).

Таким образом, в сравнении с ОУ-прототипом, предлагаемый ОУ обладает существенными преимуществами по динамическим параметрам в режиме большого сигнала. Данный положительный эффект обеспечивается за счет введения дополнительных корректирующих конденсаторов сравнительно небольшой емкости (21, 23, 21*, 23*) и не требует увеличения тока потребления ОУ в статическом режиме.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 5.399.991, fig. 2, 1995 г.

2. Патент US 6.492.870, fig. 2, 2002 г.

3. Патент US 6.278.326, fig.11, 2001 г.

4. Патент US 6.294.958, 2001 г.

5. Патентная заявка US 2004/0232968, fig. 12, 2004 г.

6. Патент US 6.429.744, 2002 г.

7. Патент US 5.510.754, fig. 2, 1996 г.

8. Патентная заявка US 2004/0212430, fig. 2, 2004 г.

9. Патентная заявка US 2002/0011875, fig. 1, 2002 г.

10. Патент US 6.542.032, fig.2, fig.3, 2003 г.

11. Патент US 5.150.074, fig. 1, 1992 г.

12. Патент US 5.374.897, fig. 4, 1994 г.

13. Патент US 5.512.859, fig. 4, 1996 г.

14. Патент US 6.459.338, fig. 2, 2002 г.

15. Патент US 6.262.633, fig. 2a, 2001 г.

16. Патентная заявка US 2005/0128000, fig. 2, 2005 г.

17. Патент US 6.710.655, fig. 3, 2004 г.

18. Патентная заявка US 2010/0225393, fig. 1B, 2010 г.

Быстродействующий операционный усилитель с дифференцирующими цепями коррекции в мостовом входном дифференциальном каскаде, содержащий неинвертирующий (1) и инвертирующий (1*) входы устройства, потенциальный выход устройства (2), первый (3) и второй (4) идентичные буферные усилители, входящие в структуру входного мостового дифференциального каскада, входы которых связаны с соответствующими неинвертирующим (1) и инвертирующим (1*) входами устройства, а соответствующие потенциальные выходы (5) и (5*) соединены друг с другом через токоограничивающий резистор (6), первый (7) токовый выход первого (3) буферного усилителя соединен со входом первого (8) токового зеркала, согласованного с первой (9) шиной источника питания, второй (10) токовый выход первого (3) буферного усилителя соединен со входом второго (11) токового зеркала, согласованного со второй (12) шиной источника питания, выходы первого (8) и второго (11) токовых зеркал соединены друг с другом и подключены к выходу устройства (2) через выходной усилитель (13) и связаны с интегрирующим корректирующим конденсатором (14), причем первый (3) буферный усилитель включает первый (15) и второй (16) входные транзисторы, базы которых подключены к неинвертирующему (1) входу устройства, коллектор первого (15) входного транзистора соединен со второй (12) шиной источника питания, коллектор второго (16) входного транзистора соединен с первой (9) шиной источника питания, первый (17) и второй (18) выходные транзисторы, объединенные эмиттеры которых подключены к потенциальному выходу (5) первого (3) буферного усилителя, база первого (17) выходного транзистора соединена с эмиттером первого (15) входного транзистора и через первый источник опорного тока (19) связана с первой (9) шиной источника питания, база второго (18) выходного транзистора соединена с эмиттером второго (16) входного транзистора и через второй (20) источник опорного тока связана со второй (12) шиной источника питания, коллектор первого (17) выходного транзистора соединен с первым (7) токовым выходом первого (3) буферного усилителя, коллектор второго (18) выходного транзистора соединен со вторым (10) токовым выходом первого (3) буферного усилителя, кроме этого, второй (4) буферный усилитель идентичен первому (3) буферному усилителю и включает третий (15*) и четвертый (16*) входные транзисторы, базы которых подключены к инвертирующему (1*) входу устройства, коллектор третьего (15*) входного транзистора соединен со второй (12) шиной источника питания, коллектор четвертого (16*) входного транзистора соединен с первой (9) шиной источника питания, третий (17*) и четвертый (18*) выходные транзисторы, объединенные эмиттеры которых подключены к потенциальному выходу (5*) второго (4) буферного усилителя, база третьего (17*) выходного транзистора соединена с эмиттером третьего (15*) входного транзистора и через третий (19*) источник опорного тока связана с первой (9) шиной источника питания, база четвертого (18*) выходного транзистора соединена с эмиттером четвертого (16*) входного транзистора и через четвертый (20*) источник опорного тока связана со второй (12) шиной источника питания, коллектор третьего (17*) выходного транзистора соединен с первым (7*) токовым выходом второго (4) буферного усилителя, коллектор четвертого (18*) выходного транзистора соединен со вторым (10*) токовым выходом второго (4) буферного усилителя, причем первый (7*) токовый выход второго (4) буферного усилителя согласован с первой (9) шиной источника питания, а второй (10*) токовый выход второго (4) буферного усилителя согласован со второй (12) шиной источника питания, отличающийся тем, что в схеме первого (3) буферного усилителя между эмиттером и базой первого (15) входного транзистора включены последовательно соединенные первый (21) дополнительный корректирующий конденсатор и первый (22) дополнительный корректирующий резистор, а между эмиттером и базой второго (16) входного транзистора включены последовательно соединенные второй (23) дополнительный корректирующий конденсатор и второй (24) дополнительный корректирующий резистор, кроме этого, в схему второго (4) буферного усилителя между эмиттером и базой третьего (15*) входного транзистора включены последовательно соединенные третий (21*) дополнительный корректирующий конденсатор и третий (22*) дополнительный корректирующий резистор, а между эмиттером и базой четвертого (16*) входного транзистора включены последовательно соединенные четвертый (23*) дополнительный корректирующий конденсатор и четвертый (24*) дополнительный корректирующий резистор.