Результат интеллектуальной деятельности: Триггерный двухступенчатый D триггер

Вид РИД

Изобретение

Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Оно, в частности, может быть применено в блоках вычислительной технике, выполненных с использованием D триггеров.

Известен двухтактный D триггер [1 Гольбенберг Л.М. Импульсные устройства. − М.: Радио и связь, 1981, с. 98, рис. 4.12, б], содержащий пять логических элемента и два R-S триггера.

Недостаток его заключается в том, что у него малая нагрузочная способность. Внешняя нагрузка подключается к выходу R-S триггера второй ступени двухступенчатого D триггера. В частности, при выполнении этого R-S триггера на логических элементах И-НЕ [1, c. 90, рис. 4.9, в] транзисторно-транзисторного (ТТЛ) варианта [1, c. 41, рис. 2.20] электрический ток внешней нагрузки формирует только один из имеющихся транзисторов. Если бы в формировании электрического тока внешней нагрузки участвовало больше транзисторов, то это повысило бы силу электрического тока в нагрузке и соответственно повысило бы нагрузочную способность триггера.

Наиболее близким по достигаемому результату является выбранный в качестве прототипа триггер с дополнительной симметрией [Гольденберг Л.М., Импульсные и цифровые устройства. − М.: Связь, 1973, стр. 275, рис. 4.18, в], содержащий два транзистора, четыре резистора и источники постоянных питающих напряжений.

Недостаток его заключается в том, что у него малая нагрузочная способность, т.к. относительно небольшая часть электрического тока, потребляемого от источника постоянного питающего напряжения, образует электрический ток внешней нагрузки. Это объясняется тем, что одну внешнюю нагрузку в рассматриваемой схеме можно подключать к коллектору или к эмиттеру только одного из двух имеющихся транзисторов. Если бы в формировании электрического тока внешней нагрузки участвовали оба имеющихся транзистора, то это повысило бы нагрузочную способность триггера.

Задача, на решение которой направлено изобретение, состоит в повышении нагрузочной способности триггерного двухступенчатого D триггера.

Это достигается тем, что в триггерный двухступенчатый D триггер, содержащий источник питающего постоянного напряжения, общая (минусовая) шина которого заземлена, в первой ступени двухступенчатого триггера последовательно включённые первый резистор, первый (n-p-n) транзистор и второй резистор, свободный вывод первого резистора подключён к выходу (плюсовой вывод) питающего постоянного напряжения, также в первой ступени двухступенчатого триггера последовательно включенные третий резистор, второй (p-n-p) транзистор и четвёртый резистор, свободный вывод третьего резистора подключен к общему выводу первого резистора и выхода источника питающего постоянного напряжения, база второго транзистора соединена с общим выводом первого резистора и коллектора первого транзистора, общий вывод коллектора этого второго транзистора и четвёртого резистора подсоединён к базе первого транзистора, а свободный вывод четвёртого резистора соединён со свободным выводом второго резистора, приведённые выше резисторы и транзисторы также имеются и во второй ступени двухступенчатого триггера, и они имеют такое же включение, как и в первой ступени, а именно последовательно между собой включены пятый резистор, третий (n-p-n) транзистор и шестой резистор, свободный вывод пятого резистора подключён к общему выводу первого, третьего резисторов и выхода источника питающего постоянного напряжения, также последовательно между собой включены седьмой резистор, четвёртый (p-n-p) транзистор и восьмой резистор, свободный вывод седьмого резистора подключён к общему выводу первого, третьего, пятого резисторов и выхода источника питающего постоянного напряжения, база четвёртого транзистора соединена с общим выводом пятого резистора и коллектора третьего транзистора, общий вывод коллектора четвёртого транзистора и восьмого резистора подсоединён к базе третьего транзистора, свободный вывод восьмого резистора соединён со свободным выводом шестого резистора, введены двенадцать дополнительных транзисторов и одиннадцать дополнительных резисторов, последовательно между собой включены первый дополнительный резистор и первый дополнительный (p-n-p) транзистор, свободный вывод первого дополнительного резистора подключен к выходу источника питающего постоянного напряжения, база первого дополнительного транзистора соединена с базой второго дополнительного (n-p-n) транзистора, вывод эмиттера которого образует относительно «земли» вход D двухступенчатого триггера, последовательно между собой включены третий дополнительный (n-p-n) транзистор, второй дополнительный резистор, четвёртый дополнительный (n-p-n) транзистор и третий дополнительный резистор, коллектор третьего дополнительного транзистора подключён к общему выводу первого резистора, коллектора первого транзистора и базы второго транзистора, база третьего дополнительного транзистора подсоединена к коллектору второго дополнительного транзистора, вывод базы четвёртого дополнительного транзистора образует относительно «земли» вход синхронизации (вход С) двухступенчатого триггера, свободный вывод третьего дополнительного резистора заземлён, последовательно между собой включены пятый дополнительный (n-p-n) транзистор и четвёртый дополнительный резистор, коллектор пятого дополнительного транзистора подключён к общему выводу первого резистора, базы второго транзистора и коллекторов первого и дополнительного третьего транзисторов, свободный вывод четвёртого дополнительного резистора заземлён, вывод базы пятого дополнительного транзистора образует относительно «земли» вход «Сброс 1» несинхронизированной установки двухступенчатого триггера в исходное начальное состояние 1, где уровень выходного напряжения триггера соответствует логической 1, последовательно включены шестой дополнительный (n-p-n) транзистор и пятый дополнительный резистор, коллектор шестого дополнительного транзистора подключён к общему выводу третьего резистора и эмиттера второго транзистора, база шестого дополнительного транзистора подсоединена к коллектору первого дополнительного транзистора, свободный вывод пятого дополнительного резистора соединён с общим выводом второго дополнительного резистора и коллектора четвёртого дополнительного транзистора, последовательно включены седьмой дополнительный (n-p-n) транзистор и шестой дополнительный резистор, коллектор седьмого дополнительного транзистора подключён к общему выводу третьего резистора, коллектора шестого дополнительного транзистора и эмиттера второго транзистора вывод базы седьмого дополнительного транзистора образует относительно «земли» вход «Сброс 0» несинхронизированной установки двухступенчатого триггера в исходное начальное состояние 0, где уровень выходного напряжения триггера соответствует логическому 0, свободный вывод шестого дополнительного резистора заземлён, седьмой дополнительный резистор включён между «землёй» и общим выводом второго и четвёртого резисторов, последовательно включены восьмой дополнительный резистор и восьмой дополнительный (n-p-n) транзистор, свободный вывод восьмого дополнительного резистора подключён к выходу источника питающего постоянного напряжения, эмиттер восьмого дополнительного транзистора заземлён, а его база соединена с общим выводом третьего дополнительного резистора и эмиттера четвёртого дополнительного транзистора, последовательно включены девятый дополнительный резистор и девятый дополнительный (p-n-p) транзистор, свободный вывод девятого дополнительного резистора подключен к выходу источника питающего постоянного напряжения, база девятого дополнительного транзистора соединена с общим выводом второго, четвёртого и дополнительного седьмого резисторов, последовательно включены десятый дополнительный (n-p-n) транзистор, десятый дополнительный резистор и одиннадцатый дополнительный (n-p-n) транзистор, коллектор десятого дополнительного транзистора подключён к общему выводу пятого резистора, коллектора третьего транзистора и базы четвёртого транзистора, база десятого дополнительного транзистора соединена с общим выводом второго, четвёртого, дополнительного седьмого резисторов и базы девятого дополнительного транзистора, эмиттер одиннадцатого дополнительного транзистора заземлён, а его база подсоединена к общему выводу восьмого дополнительного резистора и коллектора восьмого дополнительного транзистора, последовательно включены двенадцатый дополнительный (n-p-n) транзистор и одиннадцатый дополнительный резистор, коллектор двенадцатого дополнительного транзистора подсоединён к общему выводу седьмого резистора и эмиттера четвёртого транзистора, база двенадцатого дополнительного транзистора соединёна с коллектором девятого дополнительного транзистора, свободный вывод одиннадцатого дополнительного резистора подключён к общему выводу десятого дополнительного резистора и коллектора одиннадцатого дополнительного транзистора, выход ( ) двухступенчатого триггера относительно «земли» образует общий вывод шестого и восьмого резисторов.

) двухступенчатого триггера относительно «земли» образует общий вывод шестого и восьмого резисторов.

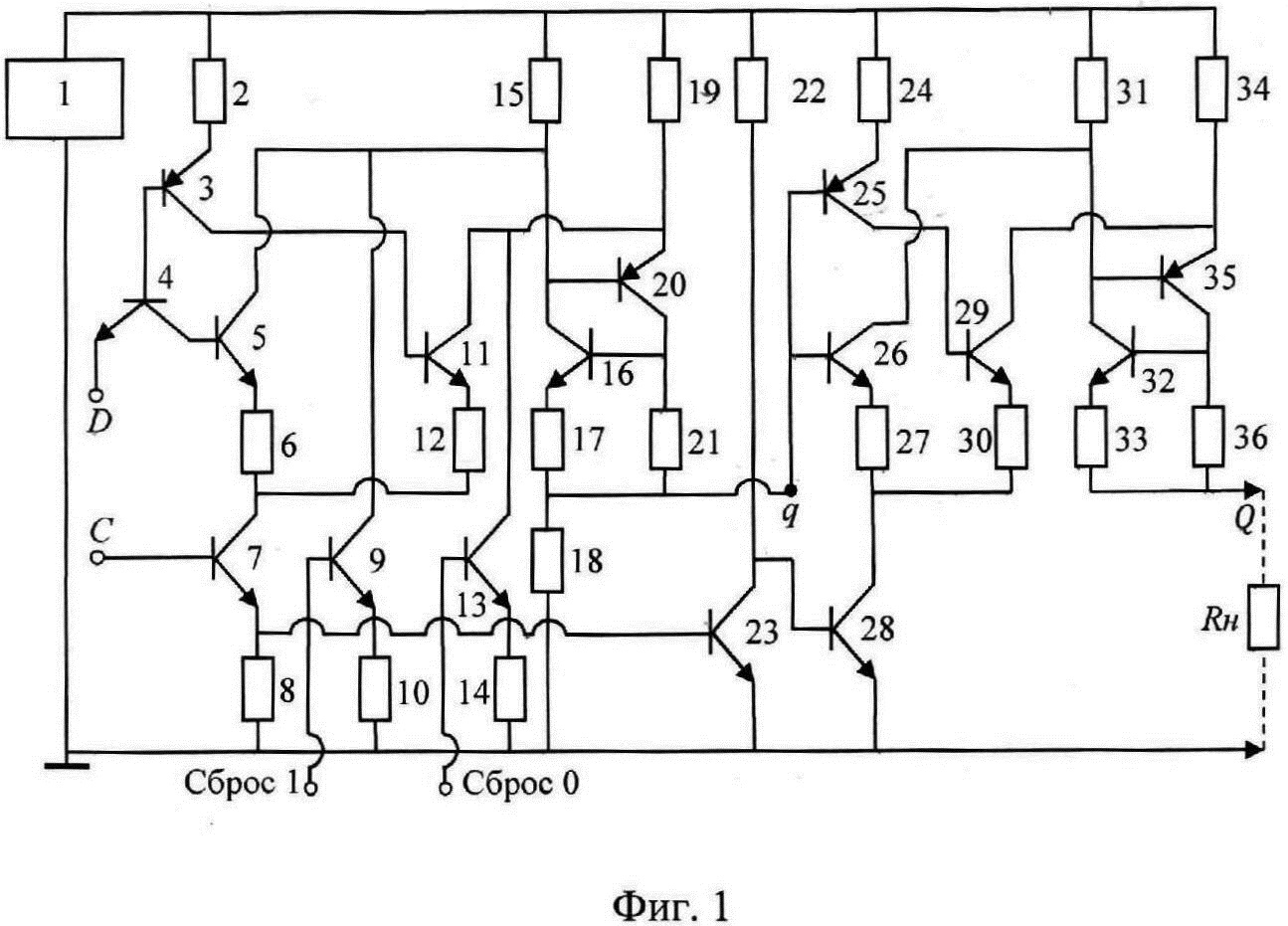

Сущность изобретения поясняется чертежом (фиг. 1) и таблицей (фиг. 2).

В триггерном двухступенчатом D триггере общая шина (минусовой вывод) источника 1 питающего постоянного напряжения заземлена. Последовательно между собой включены резистор 2 и p-n-p транзистор 3. Свободный вывод резистора 2 подключен к выходу (плюсовой вывод) источника 1. База транзистора 3 подсоединена к базе n-p-n транзистора 4, вывод эмиттера которого образует относительно «земли» вход D двухступенчатого триггера. Последовательно между собой включены n-p-n транзистор 5, резистор 6, n-p-n транзистор 7 и резистор 8. База транзистора 5 подключена к коллектору транзистора 4. Вывод базы транзистора 7 образует относительно «земли» вход синхронизации (вход С) двухступенчатого триггера. Свободный вывод резистора 8 заземлен. Последовательно включены n-p-n транзистор 9 и резистор 10. Коллектор транзистора 9 подключен к коллектору транзистора 5. Свободный вывод резистора 10 заземлен. Вывод базы транзистора 9 образует относительно «земли» вход «Сброс 1» несинхронизированной установки двухступенчатого триггера в исходное (начальное) состояние 1 (уровень выходного напряжения соответствует логической 1). Последовательно соединены n-p-n транзистор 11 и резистор 12. База транзистора 11 подключена к коллектору транзистора 3, а свободный вывод резистора 12 – к общему выводу резистора 6 и коллектора транзистора 7. Последовательно включены n-p-n транзистор 13 и резистор 14. Коллектор транзистора 13 подключен к коллектору транзистора 11. Вывод базы транзистора 13 образует относительно «земли» вход «Сброс 0» несинхронизированной установки двухступенчатого триггера в исходное (начальное) состояние 0 (уровень выходного напряжения соответствует уровню логического 0). Свободный вывод резистора 14 заземлён.

Последовательно включены резистор 15, n-p-n транзистор 16, резисторы 17 и 18. Свободный вывод резистора 15 подключен к выходу источника 1. Общий вывод этого резистора и коллектора транзистора 16 соединен с общим выводом коллекторов транзисторов 5 и 9. Свободный вывод резистора 18 заземлен. Последовательно включены резистор 19, p-n-p транзистор 20 и резистор 21. Свободный вывод резистора 19 подключен к выходу источника 1. Общий вывод этого резистора и эмиттеры транзистора 20 подключен к коллекторам транзисторов 11 и 13. База транзистора 20 подключена к общему выводу резистора 15, коллекторов транзисторов 16, 5 и 9. Общий вывод резистора 21 и коллектора транзистора 20 соединен с базой транзистора 16, а свободный вывод этого резистора 21 – с общим выводом резисторов 17 и 18. Схема на транзисторах 16, 20 и резисторах 15, 17, 19, 21 является триггером на транзисторах противоположного типа проводимости. Выход этого триггера на фиг.1 обозначен q.

Последовательно включены резистор 22 и p-n-p транзистор 23. Свободный выход резистора 22 подключен к выходу источника 1, а эмиттер транзистора 23 заземлен. База этого транзистора 23 соединена с общим выводом резистора 8 и эмиттера транзистора 7. Последовательно включены резистор 24 и p-n-p транзистор 25. Свободный вывод резистора 24 подключен к выходу источника 1, а база транзистора 25 – к общему выводу резисторов 17, 18 и 21. Последовательно включены n-p-n транзистор 26, резистор 27 и n-p-n транзистор 28. Вывод базы транзистора 26 подключен к общему выводу резисторов 17, 18, 21 и базы транзистора 25. Эмиттер транзистора 28 заземлен, а его база соединена с общим выводом резистора 22 и коллектора транзистора 23. Последовательно включены n-p-n транзистор 29 и резистор 30. База транзистора 29 подключена к коллектору транзистора 25, а свободный вывод резистора 30 - к общему выводу резистора 27 и коллектора транзистора 28.

Последовательно включены резистор 31, n-p-n транзистор 32 и резистор 33. Свободный вывод резистора 31 подключен к выходу источника 1. Общий вывод последнего резистора и коллектора транзистора 32 соединен коллектором транзистора 26. И наконец, последовательно включены резистор 34, p-n-p транзистор 35 и резистор 36. Свободный вывод резистора 34 подключен к выходу источника 1. Общий вывод резистора 34 и эмиттера транзистора 35 подключен к коллектору транзистора 29. База транзистора 35 подсоединена к общему выводу резистора 31 и коллекторов транзисторов 32 и 26. Общий вывод коллектора транзистора 35 и резистора 36 соединен с базой транзистора 32. Свободный вывод последнего резистора 36 соединен со свободным выводом резистора 33 и их общий вывод образует относительно «земли» выход  двухступенчатого триггера. Схема на транзисторах 32, 35 и резисторах 31, 33, 34 и 36 представляет собой еще один триггер на транзисторах противоположного типа проводимости. На фиг.1 также приведен пунктирными линиями резистор Rн, условно отображающий внешнюю нагрузку двухступенчатого триггера.

двухступенчатого триггера. Схема на транзисторах 32, 35 и резисторах 31, 33, 34 и 36 представляет собой еще один триггер на транзисторах противоположного типа проводимости. На фиг.1 также приведен пунктирными линиями резистор Rн, условно отображающий внешнюю нагрузку двухступенчатого триггера.

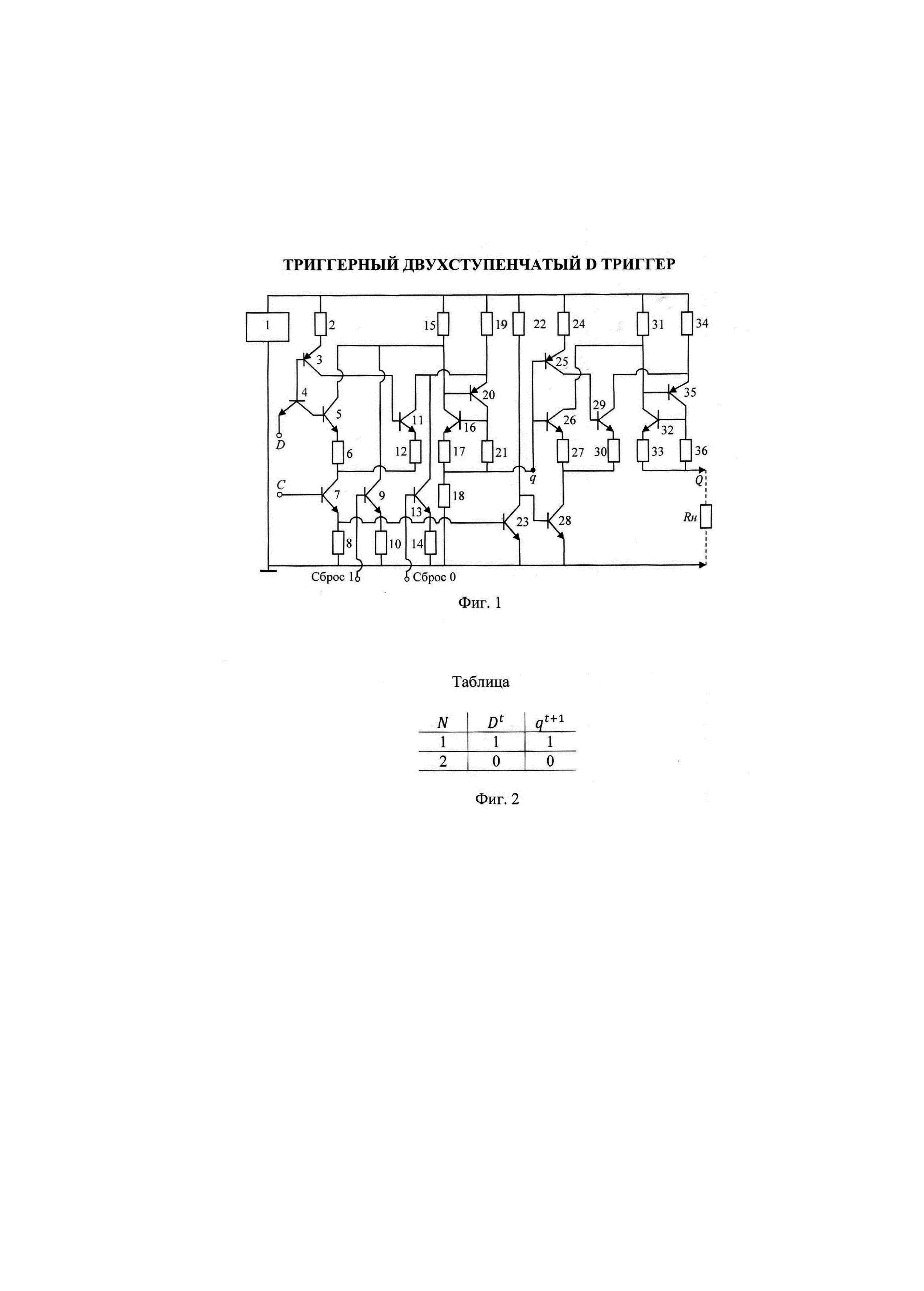

Триггерный двухступенчатый D триггер работает следующим образом. В цифровой электронике используются входные и выходные электрические сигналы низкого и высокого уровней. Низкий уровень − уровень логического нуля соответствует значениям напряжения в районе нуля или в районе ближе к нулю, высокий уровень − уровень логической единицы соответствует значениям напряжения в районе единиц вольт (нередко в районе четырёх вольт). Работа асинхронного D триггера отображается известной табл. на фиг. 2, где − номер строки по порядку,

− номер строки по порядку,  − условное отображение входного сигнала в данный момент времени t и

− условное отображение входного сигнала в данный момент времени t и  − условное отображения выходного сигнала триггера в последующее время (состояние на выходе).

− условное отображения выходного сигнала триггера в последующее время (состояние на выходе).

Приведённая табл. на фиг. 2 справедлива только при наличии сигнала синхронизации С-1 (импульса синхронизации). При его отсутствии табл. не справедлива, состояние D триггера не изменяется, оно останется неизменным вне зависимости от сигнала на входе D (0 или 1), кратко говоря, триггер в этом случае не работает, а в нём хранится имевшаяся ранее информация (0 или 1 на выходе q).

Триггер на транзисторах 16, 20 противоположного типа проводимости имеет два состояния равновесия. В первом (условно) состоянии оба транзистора закрыты и не проводят электрический ток. Тогда в том числе на резисторах 15 и 21 нулевые значения напряжения. Они прикладываются к базам транзисторов 16, 20 меньше пороговых напряжений этих транзисторов по абсолютной величине и в итоге поддерживают эти транзисторы в закрытом состоянии. Во втором (условно) состоянии транзисторы 16 и 20 открыты, их электрические токи создают напряжения в том числе на резисторах 15 и 21 больше по абсолютной величине и по значениям пороговых напряжений транзисторов и поддерживают транзисторы 16, 20 в открытом состоянии. Триггер на транзисторах противоположного типа проводимости, как и другие распространённые триггеры, переходит из первого состояния во второе и наоборот, когда управляющие входные напряжения по своим значениям превышают значения напряжений соответствующих порогов срабатывания триггера. Точно так же работает второй триггер на транзисторах 32 и 35 противоположного типа проводимости.

После несинхронизированной установки двухступенчатого триггера в исходное (начальное) состояние на входы его подаются следующие сигналы: на входы «Сброс 1» и «Сброс 0» − уровень логического нуля, на входе синхронизации С − уровень напряжения логического единицы. При таких сигналах состояния транзисторов 9 и 13 в районе порогового напряжения и возможные незначительные значения силы токов этих транзисторов не оказывает влияние на работу двухступенчатого триггера. Транзистор 7 открыт и проводит электрический ток. В соответствии с первой строкой табл. на фиг. 2 высокий уровень напряжения на входе D предопределяет пониженные значения и напряжения, и силы электрического тока базы транзистора 3. Последнее вызывает пониженные значения силы электрических токов коллектора транзистора 3, базы и коллектора транзистора 11. Ток транзистора 11 создает на резисторе 19 соответственно пониженное значение напряжения, которое меньше по абсолютной величине напряжения порога срабатывания триггера на транзисторах 16, 20 противоположного типа проводимости и не влияет на его состояние. Электрический ток транзистора 11 замыкается на «землю» через открытый транзистор 7. Базо-коллекторный p-n переход транзистора 4 открыт и через него на базу транзистора 5 поступает высокий уровень напряжения со входа D. Это определяет повышенные значения силы электрических токов базы и коллектора транзистора 5, что вызывает повышенное значение напряжения на резисторе 15. Последнее больше по абсолютной величине значения порогового напряжения срабатывания триггера на транзисторах 16, 20 и обеспечивает его второе состояние. Тогда электрические токи транзисторов 16 и 20 создают на выходе q повышенное значение напряжения - уровень логической единицы. Электрический ток транзистора 5 замыкается на «землю» через открытый транзистор 7.

В соответствии со второй строкой табл. на фиг. 2 низкий уровень напряжения на входе D предопределяет низкий уровень напряжения на базе транзистора 4 относительно «земли», т.к. базо-эмиттерный p-n переход транзистора 4 открыт. Это вызывает высокий уровень напряжения между выходом источника 1 и базами транзисторов 3 и 4, а также низкий уровень напряжения между базой и «землей» транзистора 5. Последнее приводит к пониженным значениям силы тока транзистора 5 и напряжения на резисторе 15. Значение напряжения по абсолютной величине на резисторе 15 меньше значения порогового напряжения срабатывания триггера на транзисторах 16, 20 противоположного типа проводимости и не влияет на его состояние. Повышенное значение напряжения между выходом источника 1 и общим выводом баз транзисторов 4 и 3 определяет повышенное значение сил электрических токов базы транзистора 3, коллектора этого транзистора, базы и коллектора транзистора 11. Электрический ток транзистора 11 замыкается через открытый транзистор 7, его повышенное значение создает на резисторе 19 повышенное значение напряжения. Оно превышает по абсолютной величине значение напряжения порога срабатывания триггера на транзисторах 16, 20 и переводит его в первое состояние. Тогда нулевые (или малые) значения силы электрических токов транзисторов 16, 20 создают на выходе q триггера напряжение уровня логического нуля.

При отсутствии сигнала синхронизации С-0 транзистор 7 закрыт (или его состояние в районе порогового напряжения ) и тем самым разорвана цепь прохождения электрического тока и транзистора 5, и транзистора 11 при любых значениях сигналов на входе D. Тогда на резисторах 15, 19 не могут появиться напряжения по значениям превышающие пороговые напряжения срабатывания триггера на транзисторах 16, 20. В итоге состояние этого триггера не изменяется и соответственно не изменяется напряжение на выходе q.

При наличии сигнала синхронизации С-1 транзистор 7 открыт и напряжение на резисторе 8 поддерживает транзистор 23 в открытом состоянии и обеспечивает на коллекторе этого транзистора малое значение напряжение, а именно в районе порогового напряжения транзистора 28. Не значительное (малое) значение силы электрического тока транзистора 28 может обеспечить только соответственно малые значения силы электрических токов транзисторов 26 и 29. Эти токи создают на резисторах 31 и 34 не существенные значения напряжений, меньше порогов срабатывания триггера на транзисторах 32, 35 противоположного типа проводимости. Тогда, кратко говоря. Этот триггер не работает и на выходе  напряжение не может изменяться. При наличии сигнала синхронизации изменение состояния триггера первой ступени не вызывает изменение состояния триггера второй ступени и соответственно состояние на выходе

напряжение не может изменяться. При наличии сигнала синхронизации изменение состояния триггера первой ступени не вызывает изменение состояния триггера второй ступени и соответственно состояние на выходе  .

.

И только после окончания импульса синхронизации С-0 напряжение с резистора 8 в худшем случае поддерживает транзистор 23 в районе порогового напряжения и базовый ток, замыкающийся через резистор 22 и базо-эмиттерный переход транзистора 28 обеспечивает требующееся значение силы электрического тока открытого транзистора 28. Теперь на резисторах 31, 34 могут появиться значения напряжения, достаточные для управления триггером на транзисторах 32, 35 противоположного типа проводимости и информация на выходе  может изменяться.

может изменяться.

При отсутствии сигнала синхронизации С-0 информация с выхода q первой ступени двухступенчатого триггера перезаписывается в его вторую ступень и появляется на выходе  . При q-1 коллекторный ток транзистора 26 создает на резисторе 31 напряжение, значение которого достаточно для обеспечения открытого состояния транзисторов 32, 35 триггера на транзисторах противоположного типа проводимости (второе состояние триггера). Электрические токи этих двух транзисторов обеспечивают на внешней нагрузке повышенный уровень напряжения (тоже уровень логический 1). Разность напряжений источника 1 и на базе транзистора 25 имеет сравнительно малое значение (весьма малое значение). Малы значения силы токов транзисторов 25, 29 и не оказывают влияние на состояние триггера на транзисторах противоположного типа проводимости. При q-0 сила электрического тока транзистора 26 мала и не оказывает влияние на состояние триггера на транзисторах противоположного типа проводимости. Разность между напряжением источника 1 и напряжением на базе транзистора 25 существенно возросла по сравнению с предыдущим. Это повысило силу электрического тока транзисторов 25, 29 повысило напряжение на резисторе 34 и второй триггер на транзисторах противоположного типа проводимости переходит в первое состояние. В итоге напряжение на выходе

. При q-1 коллекторный ток транзистора 26 создает на резисторе 31 напряжение, значение которого достаточно для обеспечения открытого состояния транзисторов 32, 35 триггера на транзисторах противоположного типа проводимости (второе состояние триггера). Электрические токи этих двух транзисторов обеспечивают на внешней нагрузке повышенный уровень напряжения (тоже уровень логический 1). Разность напряжений источника 1 и на базе транзистора 25 имеет сравнительно малое значение (весьма малое значение). Малы значения силы токов транзисторов 25, 29 и не оказывают влияние на состояние триггера на транзисторах противоположного типа проводимости. При q-0 сила электрического тока транзистора 26 мала и не оказывает влияние на состояние триггера на транзисторах противоположного типа проводимости. Разность между напряжением источника 1 и напряжением на базе транзистора 25 существенно возросла по сравнению с предыдущим. Это повысило силу электрического тока транзисторов 25, 29 повысило напряжение на резисторе 34 и второй триггер на транзисторах противоположного типа проводимости переходит в первое состояние. В итоге напряжение на выходе  и внешней нагрузке соответствует уровню напряжения логического нуля. Таким образом, информация действительно перезаписывается из первой ступени двухступенчатого триггера в его вторую ступень.

и внешней нагрузке соответствует уровню напряжения логического нуля. Таким образом, информация действительно перезаписывается из первой ступени двухступенчатого триггера в его вторую ступень.

Для установки двухступенчатого триггера перед началом работы в исходное (начальное) состояние используются входы: «Сброс 1» и «Сброс 0». Это входы несинхронизированной установки триггера в определенное состояние (0 или 1). При отсутствии сигналов на входе С (С-0) и поступлении напряжения уровня логической единицы на вход «Сброс 1» транзистор 9 проводит электрический ток. Сила этого тока достаточна для получения напряжения на резистор 15 такого, которое переводит триггер на транзисторах противоположного типа проводимости во второе состояние. В итоге на выходе q напряжение уровня логической единицы. При поступлении единицы на вход «Сброс 0» транзистор 13 проводит электрический ток, который на резисторе 19 создает напряжение достаточное для перевода триггера на транзисторах 16, 20 в первое состояние. В результате на выходе q напряжение уровня логического нуля. При напряжении уровня логического нуля на выходах «Сброс 1», «Сброс 0» и С имеем уже изложенную выше ситуацию, где информация из первой ступени двухступенчатого триггера перезаписывается в его вторую ступень и появляется на выходе  . Тогда здесь отпадает необходимость в использовании дополнительных элементов для несинхронизированной установки второй ступени и в итоге всего двухступенчатого триггера в исходное начальное состояние.

. Тогда здесь отпадает необходимость в использовании дополнительных элементов для несинхронизированной установки второй ступени и в итоге всего двухступенчатого триггера в исходное начальное состояние.

Таким образом, в рассмотренном триггерном двухступенчатом D триггере сила электрического тога внешней нагрузки равна сумме силы токов двух транзисторов 32 и 35, а не одного транзистора, как в известных решениях, что повышает нагрузочную способность этого триггера. Можно обратить внимание, что приведенная схема (фиг. 1) существенно (значительно) упрощает и удешевляет двухступенчатый триггер. В ней 35 элементов (16 транзисторов и 19 резисторов), а, например, в приведенном аналоге на транзисторно-транзисторных логических элементах имеется 81 элемент (36 транзисторов, 9 диодов и 36 резисторов).

Отсутствие в схеме такого большого количества элементов значительно уменьшает число соединений этих элементов и соответственно количество технологических операций для их реализации, упрощает конструирование схемы и уменьшает ее габаритные размеры. Все это тоже удешевляет триггерный двухступенчатый D триггер. Распространено применение триггеров в регистрах. В частности, двухступенчатые D триггеры используются в буферных регистрах и регистрах общего назначения процессоров ЭВМ. И столь значительное уменьшение количества элементов в них повышает надежность этих изделий.

Триггерный двухступенчатый D триггер, содержащий источник питающего постоянного напряжения, общая (минусовая) шина которого заземлена, в первой ступени двухступенчатого триггера последовательно включённые первый резистор, первый (n-p-n) транзистор и второй резистор, свободный вывод первого резистора подключён к выходу (плюсовой вывод) питающего постоянного напряжения, также в первой ступени двухступенчатого триггера последовательно включенные третий резистор, второй (p-n-p) транзистор и четвёртый резистор, свободный вывод третьего резистора подключен к общему выводу первого резистора и выхода источника питающего постоянного напряжения, база второго транзистора соединена с общим выводом первого резистора и коллектора первого транзистора, общий вывод коллектора этого второго транзистора и четвёртого резистора подсоединён к базе первого транзистора, а свободный вывод четвёртого резистора соединён со свободным выводом второго резистора, приведённые выше резисторы и транзисторы также имеются и во второй ступени двухступенчатого триггера, и они имеют такое же включение, как и в первой ступени, а именно последовательно между собой включены пятый резистор, третий (n-p-n) транзистор и шестой резистор, свободный вывод пятого резистора подключён к общему выводу первого, третьего резисторов и выхода источника питающего постоянного напряжения, также последовательно между собой включены седьмой резистор, четвёртый (p-n-p) транзистор и восьмой резистор, свободный вывод седьмого резистора подключён к общему выводу первого, третьего, пятого резисторов и выхода источника питающего постоянного напряжения, база четвёртого транзистора соединена с общим выводом пятого резистора и коллектора третьего транзистора, общий вывод коллектора четвёртого транзистора и восьмого резистора подсоединён к базе третьего транзистора, свободный вывод восьмого резистора соединён со свободным выводом шестого резистора, отличающийся тем, что в него введены двенадцать дополнительных транзисторов и одиннадцать дополнительных резисторов, последовательно между собой включены первый дополнительный резистор и первый дополнительный (p-n-p) транзистор, свободный вывод первого дополнительного резистора подключен к выходу источника питающего постоянного напряжения, база первого дополнительного транзистора соединена с базой второго дополнительного (n-p-n) транзистора, вывод эмиттера которого образует относительно «земли» вход D двухступенчатого триггера, последовательно между собой включены третий дополнительный (n-p-n) транзистор, второй дополнительный резистор, четвёртый дополнительный (n-p-n) транзистор и третий дополнительный резистор, коллектор третьего дополнительного транзистора подключён к общему выводу первого резистора, коллектора первого транзистора и базы второго транзистора, база третьего дополнительного транзистора подсоединена к коллектору второго дополнительного транзистора, вывод базы четвёртого дополнительного транзистора образует относительно «земли» вход синхронизации (вход С) двухступенчатого триггера, свободный вывод третьего дополнительного резистора заземлён, последовательно между собой включены пятый дополнительный (n-p-n) транзистор и четвёртый дополнительный резистор, коллектор пятого дополнительного транзистора подключён к общему выводу первого резистора, базы второго транзистора и коллекторов первого и дополнительного третьего транзисторов, свободный вывод четвёртого дополнительного резистора заземлён, вывод базы пятого дополнительного транзистора образует относительно «земли» вход «Сброс 1» несинхронизированной установки двухступенчатого триггера в исходное начальное состояние 1, где уровень выходного напряжения триггера соответствует логической 1, последовательно включены шестой дополнительный (n-p-n) транзистор и пятый дополнительный резистор, коллектор шестого дополнительного транзистора подключён к общему выводу третьего резистора и эмиттера второго транзистора, база шестого дополнительного транзистора подсоединена к коллектору первого дополнительного транзистора, свободный вывод пятого дополнительного резистора соединён с общим выводом второго дополнительного резистора и коллектора четвёртого дополнительного транзистора, последовательно включены седьмой дополнительный (n-p-n) транзистор и шестой дополнительный резистор, коллектор седьмого дополнительного транзистора подключён к общему выводу третьего резистора, коллектора шестого дополнительного транзистора и эмиттера второго транзистора, вывод базы седьмого дополнительного транзистора образует относительно «земли» вход «Сброс 0» несинхронизированной установки двухступенчатого триггера в исходное начальное состояние 0, где уровень выходного напряжения триггера соответствует логическому 0, свободный вывод шестого дополнительного резистора заземлён, седьмой дополнительный резистор включён между «землёй» и общим выводом второго и четвёртого резисторов, последовательно включены восьмой дополнительный резистор и восьмой дополнительный (n-p-n) транзистор, свободный вывод восьмого дополнительного резистора подключён к выходу источника питающего постоянного напряжения, эмиттер восьмого дополнительного транзистора заземлён, а его база соединена с общим выводом третьего дополнительного резистора и эмиттера четвёртого дополнительного транзистора, последовательно включены девятый дополнительный резистор и девятый дополнительный (p-n-p) транзистор, свободный вывод девятого дополнительного резистора подключен к выходу источника питающего постоянного напряжения, база девятого дополнительного транзистора соединена с общим выводом второго, четвёртого и дополнительного седьмого резисторов, последовательно включены десятый дополнительный (n-p-n) транзистор, десятый дополнительный резистор и одиннадцатый дополнительный (n-p-n) транзистор, коллектор десятого дополнительного транзистора подключён к общему выводу пятого резистора, коллектора третьего транзистора и базы четвёртого транзистора, база десятого дополнительного транзистора соединена с общим выводом второго, четвёртого, дополнительного седьмого резисторов и базы девятого дополнительного транзистора, эмиттер одиннадцатого дополнительного транзистора заземлён, а его база подсоединена к общему выводу восьмого дополнительного резистора и коллектора восьмого дополнительного транзистора, последовательно включены двенадцатый дополнительный (n-p-n) транзистор и одиннадцатый дополнительный резистор, коллектор двенадцатого дополнительного транзистора подсоединён к общему выводу седьмого резистора и эмиттера четвёртого транзистора, база двенадцатого дополнительного транзистора соединена с коллектором девятого дополнительного транзистора, свободный вывод одиннадцатого дополнительного резистора подключён к общему выводу десятого дополнительного резистора и коллектора одиннадцатого дополнительного транзистора, выход () двухступенчатого триггера относительно «земли» образует общий вывод шестого и восьмого резисторов.