Результат интеллектуальной деятельности: ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ ДЛЯ РАБОТЫ В УСЛОВИЯХ НИЗКИХ ТЕМПЕРАТУР

Вид РИД

Изобретение

Изобретение относится к области радиотехники и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем на комплементарных полевых транзисторах с управляющим p-n переходом (JFet) различного функционального назначения, например, операционных усилителях (ОУ), компараторах и т.п., в т.ч. работающих при низких температурах и воздействии радиации [1].

Известны схемы классических дифференциальных каскадов (ДК) на комплементарных транзисторах [2-28], в т.ч. на комплементарных КМОП полевых транзисторах [3-28] и комплементарных полевых транзисторах с управляющим p-n переходом (JFet) [2], которые стали основой многих серийных аналоговых микросхем. В литературе по аналоговой микроэлектронике этот класс ДК имеет специальное обозначение – dual-input-stage [29].

Для работы при низких температурах при жестких ограничениях на уровень шумов перспективно использование JFet полевых транзисторов с управляющим p-n переходом [30-32]. ДК данного класса активно применяются в структуре малошумящих аналоговых интерфейсов для обработки сигналов датчиков [33-35].

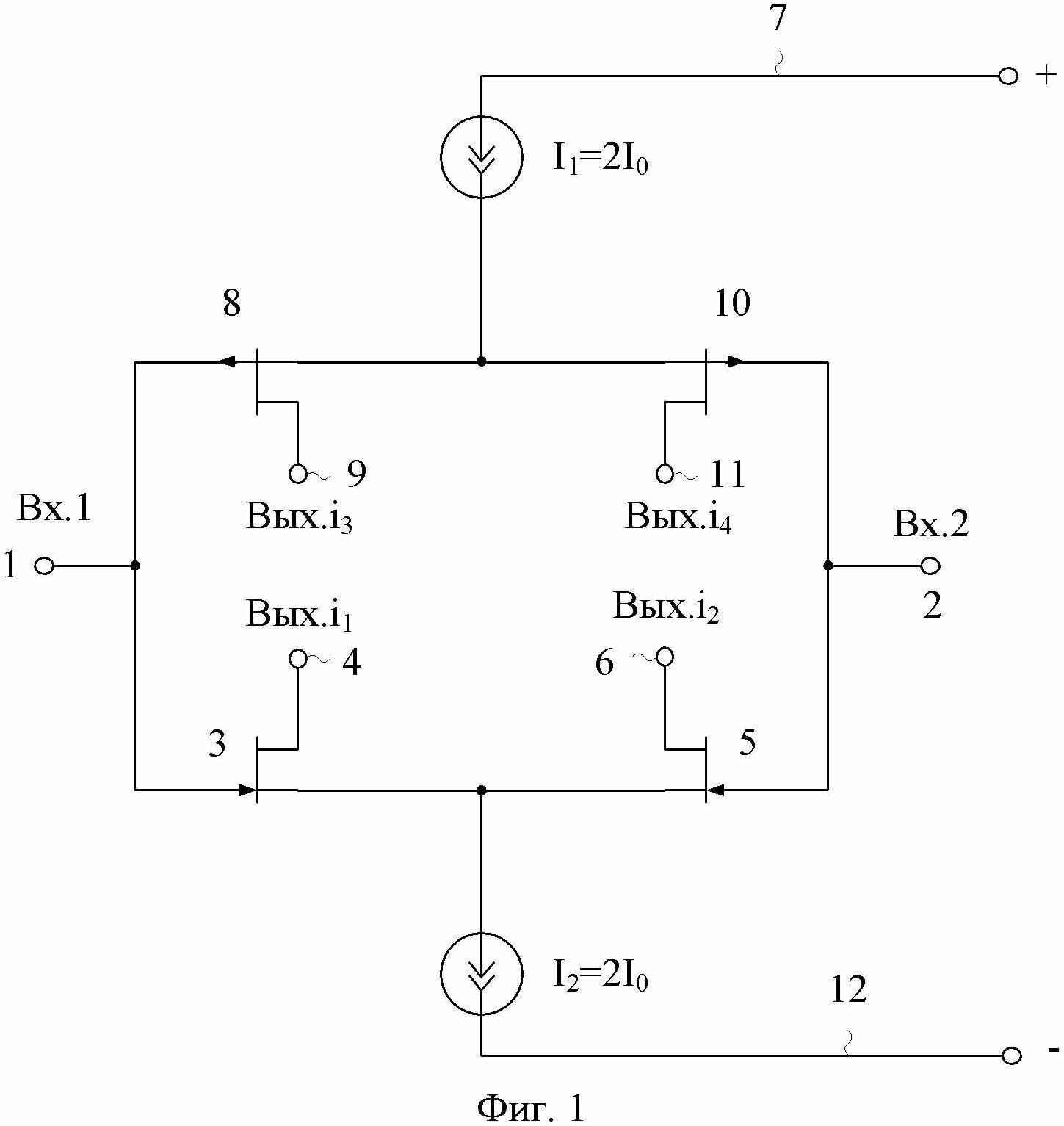

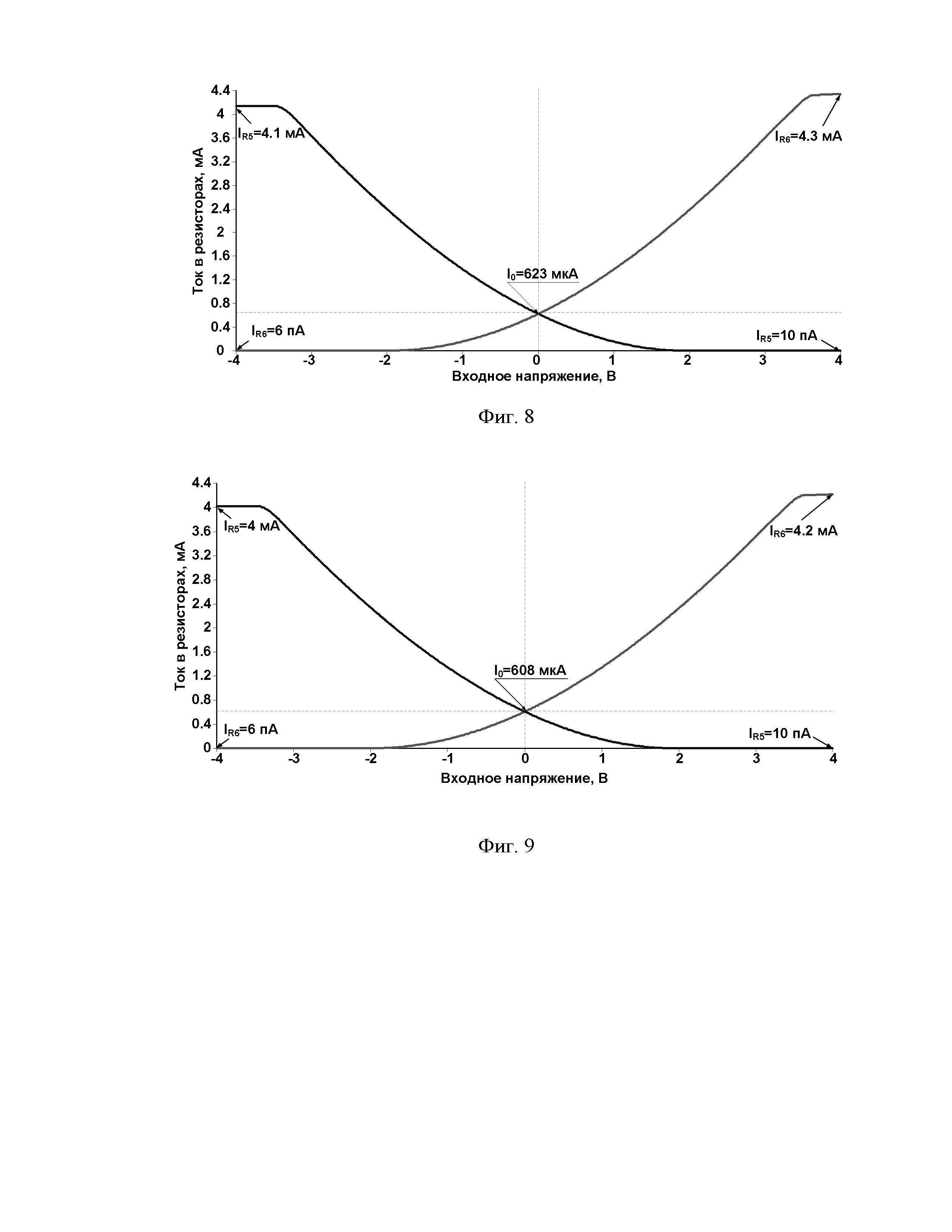

Ближайшим прототипом (фиг. 1) заявляемого устройства является дифференциальный каскад на комплементарных полевых транзисторах с управляющим p-n переходом, описанный в патенте US 5.291.149, fig.4, 1994г., который содержит первый 1 и второй 2 входы устройства, первый 3 входной полевой транзистор, затвор которого соединен с первым 1 входом устройства, сток связан с первым 4 токовым выходом, а исток подключен к истоку второго 5 входного полевого транзистора, затвор которого соединен со вторым 2 входом устройства, а сток соединен со вторым 6 токовым выходом, причем первый 4 и второй 6 токовые выходы согласованы с первой 7 шиной источника питания, третий 8 входной полевой транзистор, сток которого связан с третьим 9 токовым выходом, а исток соединен с истоком четвертого 10 входного полевого транзистора, сток которого соединен с четвертым 11 токовым выходом, причем третий 9 и четвертый 11 токовые выходы согласованы со второй 12 шиной источника питания.

Существенный недостаток ДК-прототипа фиг. 1 состоит в том, что он работает в режиме класса «А», то есть его максимальные выходные токи не превышают статические токи опорных источников I1=I2=2I0. Это не позволяет повысить быстродействие операционных усилителей (ОУ) с дифференциальным каскадом фиг. 1, так как его напряжение ограничения проходной характеристики при микроамперных I0 оказывается небольшим [36, 37].

Основная задача предполагаемого изобретения состоит в создании условий, которые позволяют ДК работать в режиме класса «АВ» при малом статическом токопотреблении. В конечном итоге, это позволяет повысить максимальную скорость нарастания выходного напряжения (SR) ОУ с предлагаемым входным ДК [36, 37].

Поставленные задачи достигаются тем, что в дифференциальном каскаде фиг. 1, содержащем первый 1 и второй 2 входы устройства, первый 3 входной полевой транзистор, затвор которого соединен с первым 1 входом устройства, сток связан с первым 4 токовым выходом, а исток подключен к истоку второго 5 входного полевого транзистора, затвор которого соединен со вторым 2 входом устройства, а сток соединен со вторым 6 токовым выходом, причем первый 4 и второй 6 токовые выходы согласованы с первой 7 шиной источника питания, третий 8 входной полевой транзистор, сток которого связан с третьим 9 токовым выходом, а исток соединен с истоком четвертого 10 входного полевого транзистора, сток которого соединен с четвертым 11 токовым выходом, причем третий 9 и четвертый 11 токовые выходы согласованы со второй 12 шиной источника питания, предусмотрены новые элементы и связи – в схему введены первый 13 и второй 14 дополнительные полевые транзисторы, стоки которых подключены к первой 7 шине источника питания, затвор первого 13 дополнительного полевого транзистора соединен с первым 1 входом устройства, затвор второго 14 дополнительного полевого транзистора соединен со вторым 2 входом устройства, исток первого 13 дополнительного полевого транзистора соединен с затвором третьего 8 входного полевого транзистора и через первый 15 источник опорного тока связан со второй 12 шиной источника питания, исток второго 14 дополнительного полевого транзистора соединен с затвором четвертого 10 входного полевого транзистора и через второй 16 источник опорного тока связан со второй 12 шиной источника питания, причем объединенные истоки первого 3 и второго 5 входных полевых транзисторов связаны с объединенными истоками третьего 8 и четвертого 10 входных полевых транзисторов.

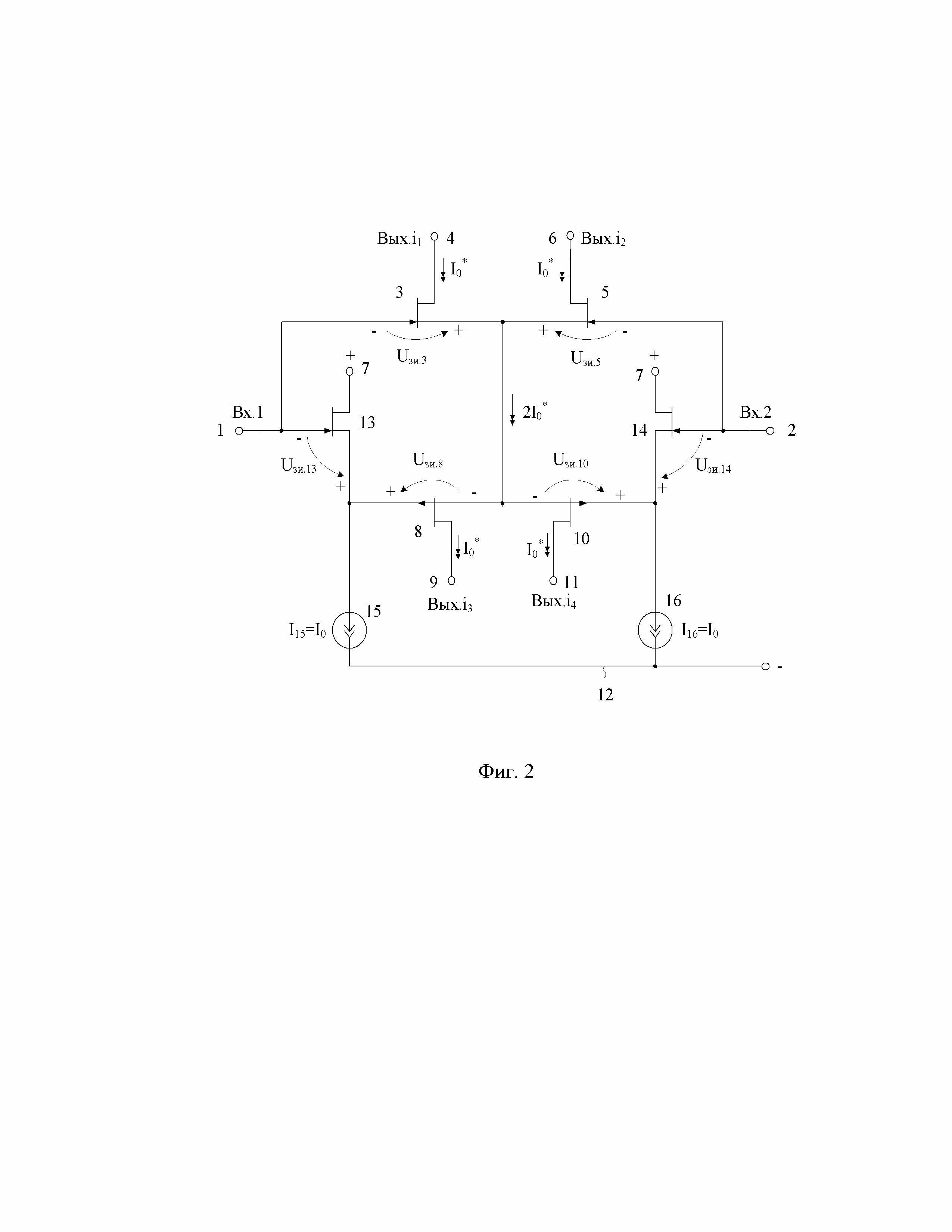

На чертеже фиг. 1 представлена схема ДК-прототипа, а на чертеже фиг. 2 – схема заявляемого дифференциального каскада на комплементарных полевых транзисторах (CJFET) в соответствии с п.1 формулы изобретения.

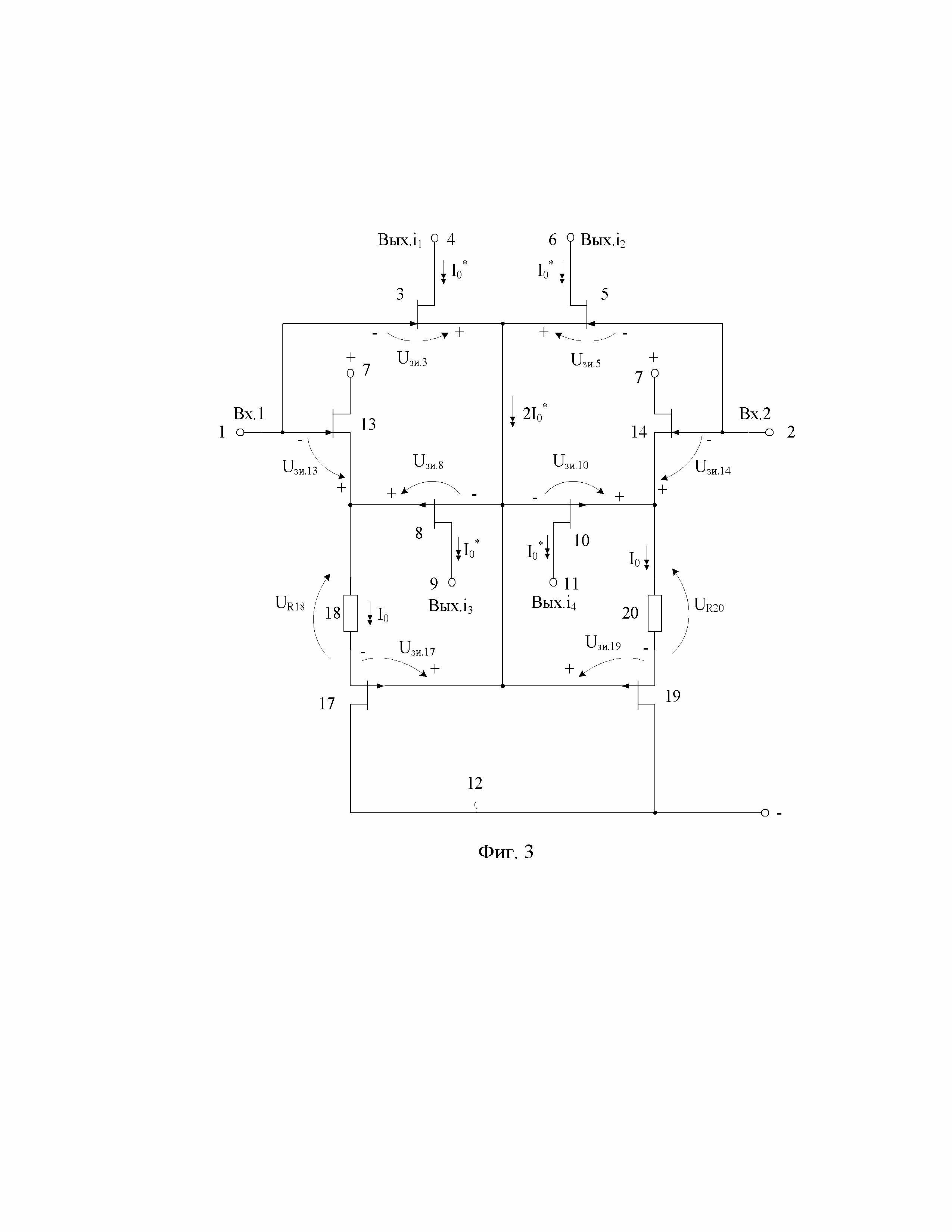

На чертеже фиг. 3 показана схема дифференциального каскада в соответствии с п. 2 формулы изобретения.

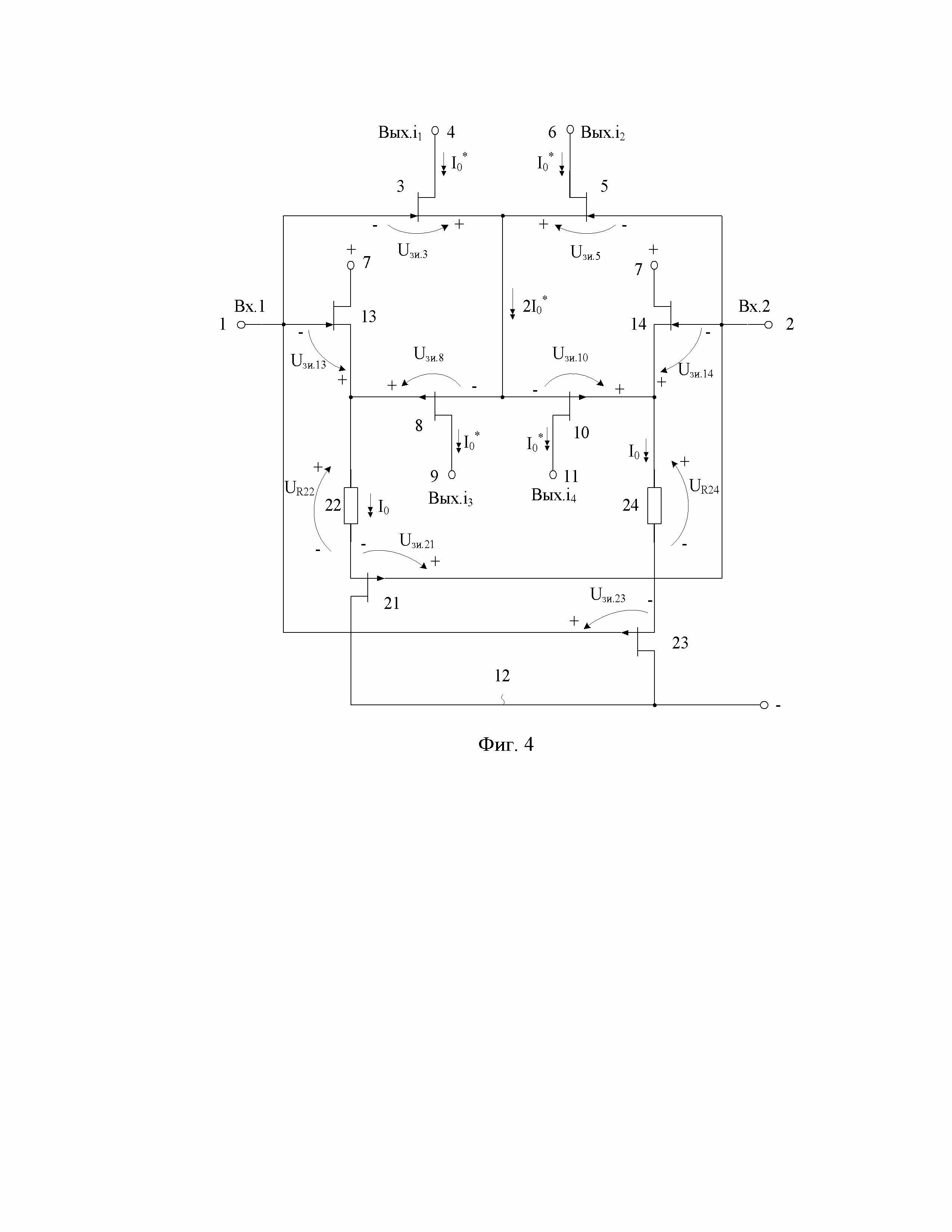

На чертеже фиг. 4 приведена схема дифференциального каскада в соответствии с п. 3 формулы изобретения.

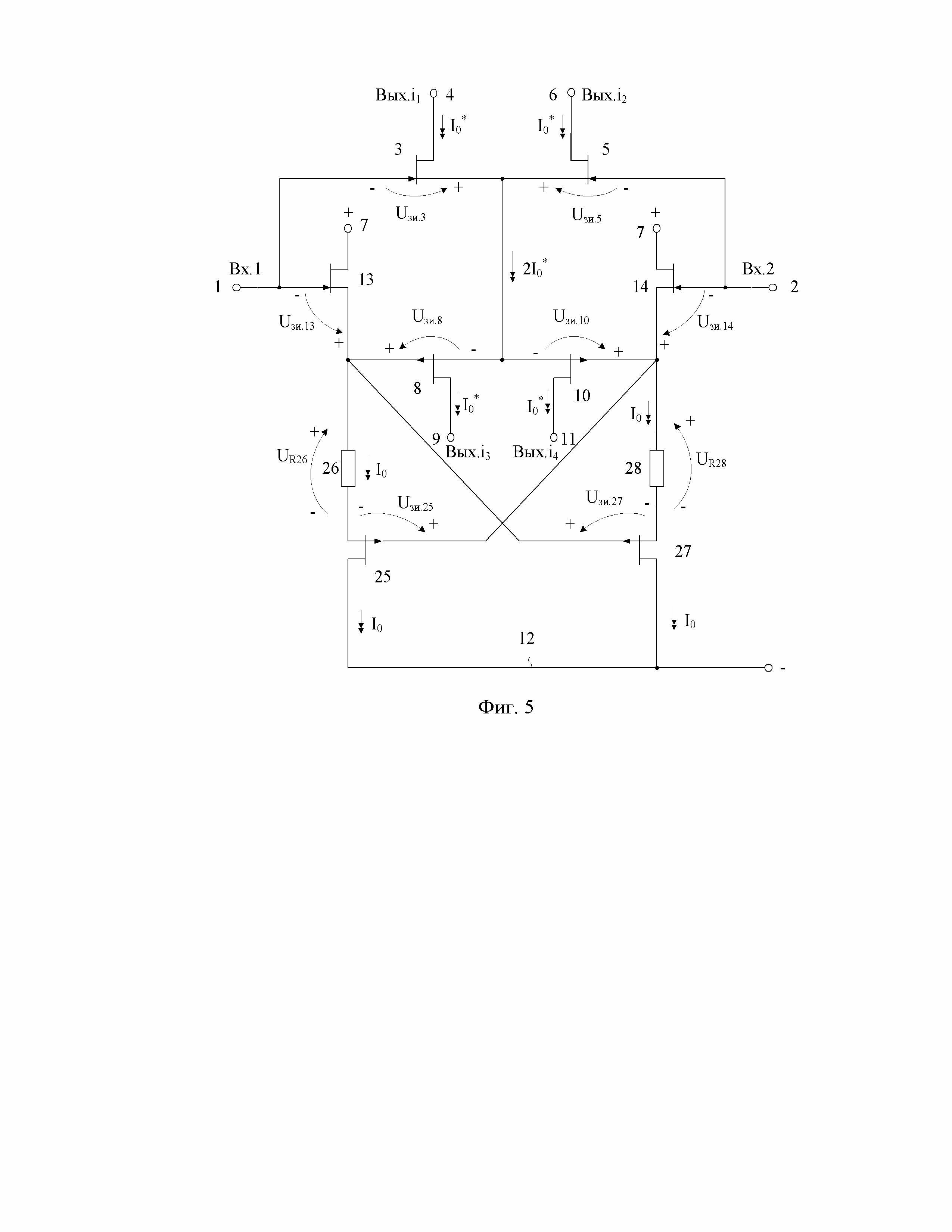

На чертеже фиг. 5 представлена схема дифференциального каскада в соответствии с п. 4 формулы изобретения.

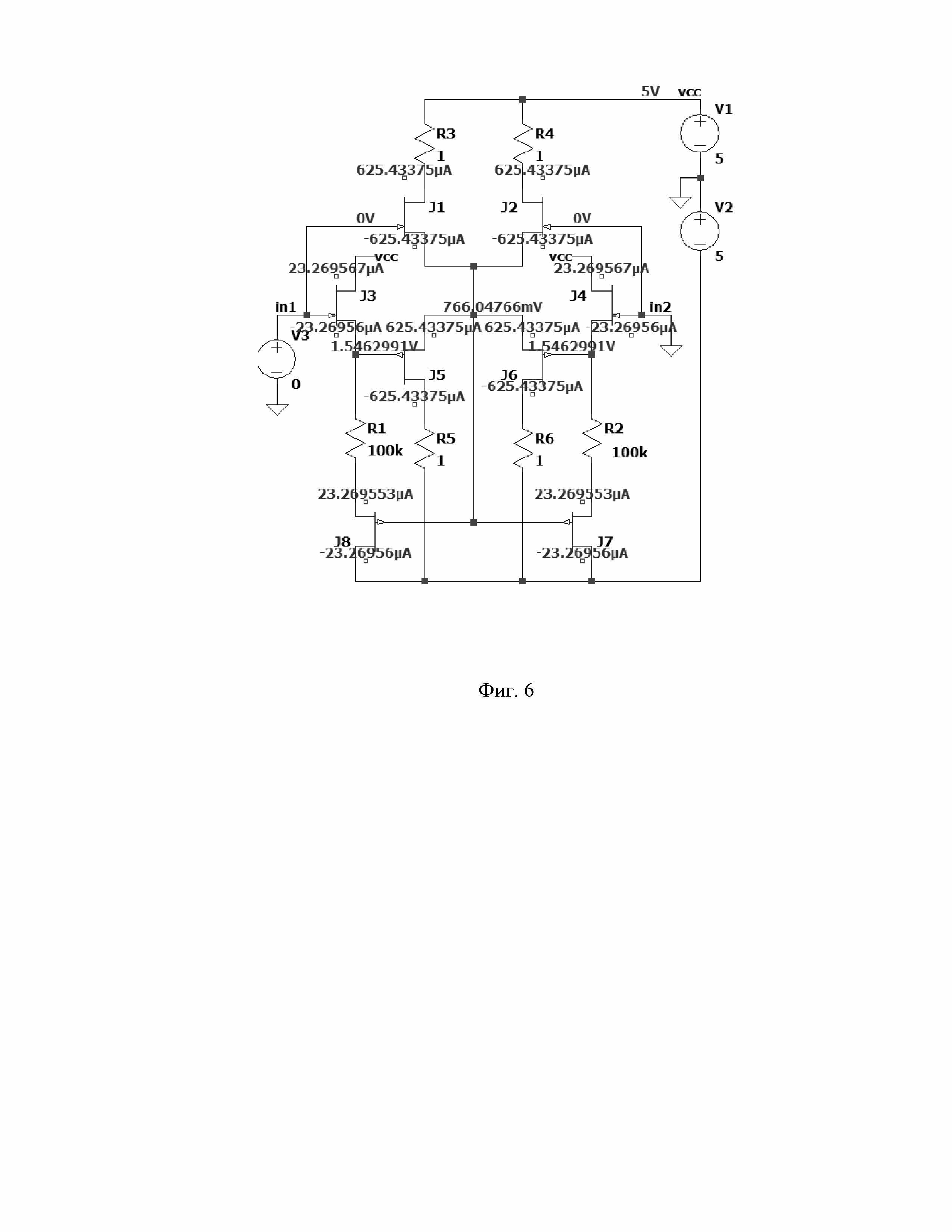

На чертеже фиг. 6 приведена схема для моделирования статического режима CJFet ДК фиг. 2 в среде САПР LTSpice XVII (Analog Devices, США) при температуре окружающей среды t=27°C. Здесь резисторы R3=R4=R5= R6=1 Ом моделируют свойства нагрузки ДК, например, входы токовых зеркал в конкретных ОУ.

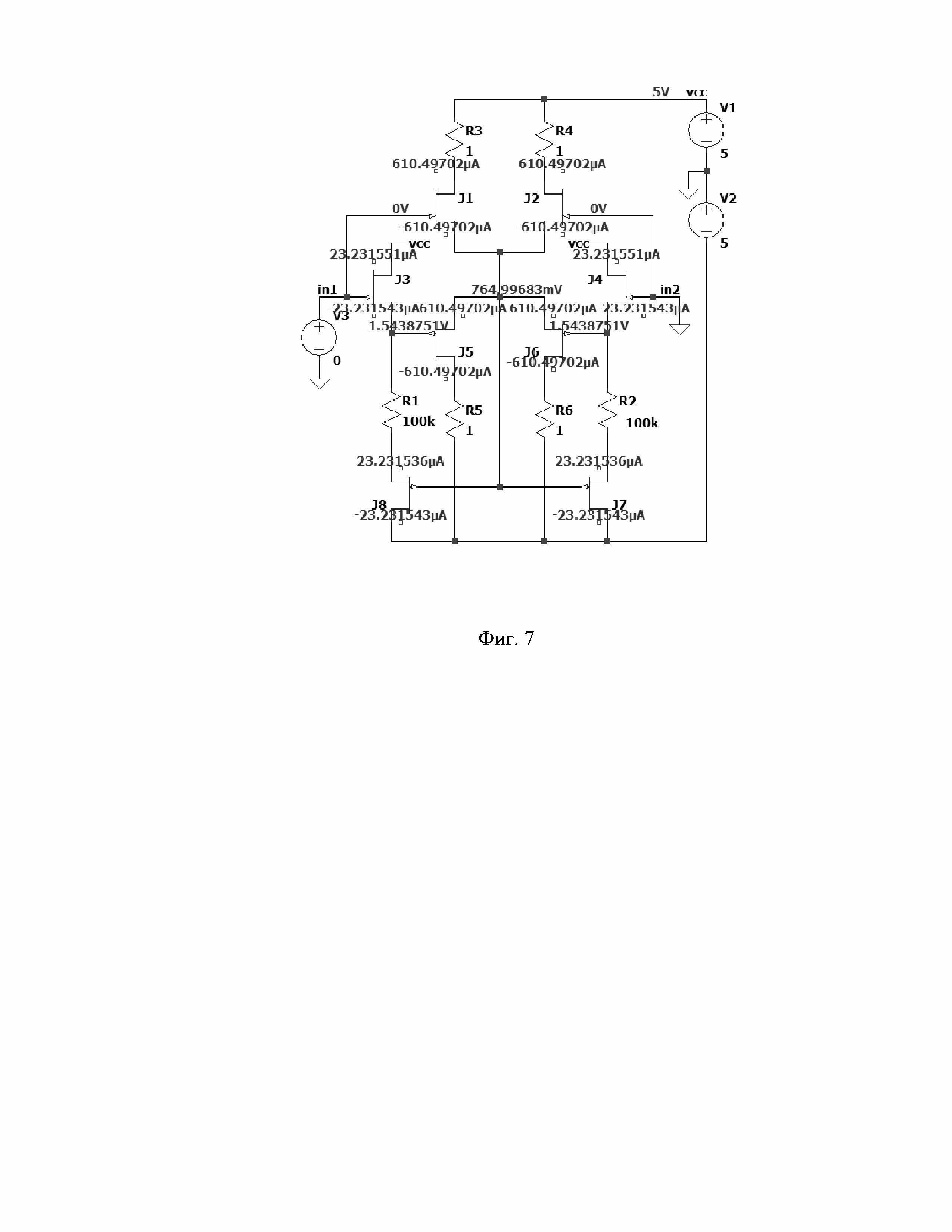

На чертеже фиг. 7 показан статический режим схемы CJFet ДК фиг. 2 в среде LTSpice XVII при низкой температуре t=-197°C.

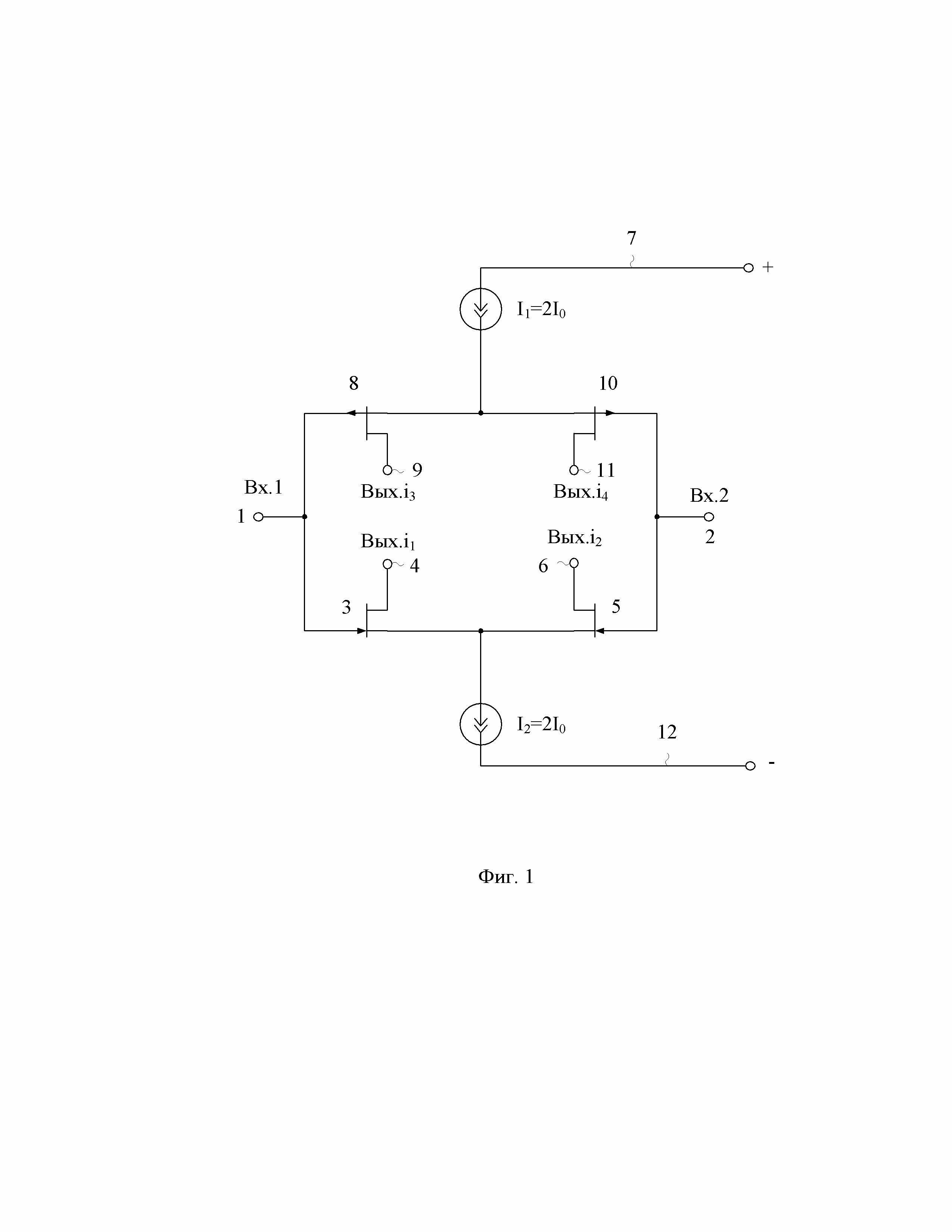

На чертеже фиг. 8 представлена проходная характеристика CJFet ДК фиг. 6 в среде LTSpice XVII при температуре окружающей среды t=27°C.

На чертеже фиг. 9 показана проходная характеристика CJFet ДК фиг. 7 в среде LTSpice XVII при низкой температуре t=-197°C.

Дифференциальный каскад класса АВ на комплементарных полевых транзисторах с управляющим p-n переходом для работы в условиях низких температур фиг. 2 содержит первый 1 и второй 2 входы устройства, первый 3 входной полевой транзистор, затвор которого соединен с первым 1 входом устройства, сток связан с первым 4 токовым выходом, а исток подключен к истоку второго 5 входного полевого транзистора, затвор которого соединен со вторым 2 входом устройства, а сток соединен со вторым 6 токовым выходом, причем первый 4 и второй 6 токовые выходы согласованы с первой 7 шиной источника питания, третий 8 входной полевой транзистор, сток которого связан с третьим 9 токовым выходом, а исток соединен с истоком четвертого 10 входного полевого транзистора, сток которого соединен с четвертым 11 токовым выходом, причем третий 9 и четвертый 11 токовые выходы согласованы со второй 12 шиной источника питания. В схему введены первый 13 и второй 14 дополнительные полевые транзисторы, стоки которых подключены к первой 7 шине источника питания, затвор первого 13 дополнительного полевого транзистора соединен с первым 1 входом устройства, затвор второго 14 дополнительного полевого транзистора соединен со вторым 2 входом устройства, исток первого 13 дополнительного полевого транзистора соединен с затвором третьего 8 входного полевого транзистора и через первый 15 источник опорного тока связан со второй 12 шиной источника питания, исток второго 14 дополнительного полевого транзистора соединен с затвором четвертого 10 входного полевого транзистора и через второй 16 источник опорного тока связан со второй 12 шиной источника питания, причем объединенные истоки первого 3 и второго 5 входных полевых транзисторов связаны с объединенными истоками третьего 8 и четвертого 10 входных полевых транзисторов.

На чертеже фиг. 3, в соответствии с п. 2 формулы изобретения, первый 15 источник опорного тока выполнен на основе первого 17 вспомогательного полевого транзистора, сток которого соединен со второй 12 шиной источника питания, исток связан с истоком первого 13 дополнительного полевого транзистора через первый 18 вспомогательный резистор, а его затвор соединен с объединенными истоками третьего 8 и четвертого 10 входных полевых транзисторов, второй 16 источник опорного тока выполнен на основе второго 19 вспомогательного полевого транзистора, сток которого соединен со второй 12 шиной источника питания, исток связан с истоком второго 14 дополнительного полевого транзистора через второй 20 вспомогательный резистор, а его затвор соединен с объединенными истоками третьего 8 и четвертого 10 входных полевых транзисторов.

На чертеже фиг. 4, в соответствии с п. 3 формулы изобретения, первый 15 источник опорного тока выполнен на основе третьего 21 вспомогательного полевого транзистора, сток которого соединен со второй 12 шиной источника питания, исток связан с истоком первого 13 дополнительного полевого транзистора через второй 22 вспомогательный резистор, а его затвор соединен со входом 2 устройства, второй 16 источник опорного тока выполнен на основе четвертого 23 вспомогательного полевого транзистора, сток которого соединен со второй 12 шиной источника питания, исток связан с истоком второго 14 дополнительного полевого транзистора через четвертый 24 вспомогательный резистор, а его затвор соединен с первым 1 входом устройства.

На чертеже фиг. 5, в соответствии с п. 4 формулы изобретения, первый 15 источник опорного тока выполнен на основе пятого 25 вспомогательного полевого транзистора, сток которого соединен со второй 12 шиной источника питания, исток связан с истоком первого 13 дополнительного полевого транзистора через пятый 26 вспомогательный резистор, а его затвор связан с истоком второго 14 дополнительного полевого транзистора, второй 16 источник опорного тока выполнен на основе шестого 27 вспомогательного полевого транзистора, сток которого соединен со второй 12 шиной источника питания, исток связан с истоком второго 14 дополнительного полевого транзистора через шестой 28 вспомогательный резистор, а его затвор соединен с истоком первого 13 дополнительного полевого транзистора.

Рассмотрим работу ДК фиг. 2. В данной схеме применяются JFet транзисторы с p- и n-каналами, которые из-за технологических и конструктивных особенностей всегда имеют неодинаковые напряжения отсечки (Uотс.) стоко-затворной характеристики. В результате, при малых токах первого 15 и второго 16 источников опорного тока (единица-десятки микроампер) статические токи первого 3, второго 5, третьего 8 и четвертого 10 входных полевых транзисторов имеют значения на уровне 300 – 600 микроампер. Причем, такой статический режим достаточно устойчив при технологических разбросах Uотс., а так же в широком диапазоне температур и в условиях проникающей радиации.

Как следует из графиков фиг. 8 и фиг. 9 предлагаемое схемотехническое решение фиг.2 работает в режиме класса «АВ», когда его максимальные выходные токи превышают статическое значение I0 в 5÷7 раз. Большие напряжения ограничения проходной характеристики ДК (Uгр.) позволяют создавать на базе схемы фиг. 2 быстродействующие CJFet операционные усилители [36, 37].

В схемах фиг. 3-фиг. 5, которые являются частным случаем построения ДК фиг. 2, введены соответственно первый 17, второй 19, третий 21, четвертый 23, пятый 25 и шестой 27 вспомогательные полевые транзисторы, которые улучшают другие параметры базовой схемы фиг. 2 – коэффициент ослабления входных синфазных сигналов, коэффициент подавления помех по шинам питания, повышают стабильность статического тока первого 3, второго 5, третьего 8 и четвертого 10 входных полевых транзисторов при внешних воздействиях.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с известным схемотехническим решением.

Библиографический список

1. O. V. Dvornikov, V. L. Dziatlau, N. N. Prokopenko, K. O. Petrosiants, N. V. Kozhukhov and V. A. Tchekhovski, "The accounting of the simultaneous exposure of the low temperatures and the penetrating radiation at the circuit simulation of the BiJFET analog interfaces of the sensors," 2017 International Siberian Conference on Control and Communications (SIBCON), Astana, 2017, pp. 1-6. DOI: 10.1109/SIBCON.2017.7998507

2. Патент US 5.291.149 fig. 4, 1994 г.

3. Патент US 4.377.789, fig. 1, 1983 г.

4. Патентная заявка US 2006/0125522, 2006 г.

5. Патент US 7.907.011, 2011

6. Патент US 2008/0024217, fig. 1, 2008 г.

7. Патент EP 0318263,1989 г.

8. Патент US 5.907.259, fig. 1, 1999 г.

9. Патент US 7.408.410, 2008 г.

10. Патент US 6.628.168, fig.2, 2003 г.

11. Патентная заявка US 2009/0302895, 2009 г.

12. Патент US 5.714.906, fig. 4, 1998 г.

13. Патент US 2005/0285677, 2005 г.

14. Патент US 5.070.306, fig. 3, 1991 г.

15. Патент US 2010/001797, 2010 г.

16. Патент US 6.972.623, fig. 4, fig. 6, 2005 г.

17. Патент US 2008/0252374, 2008 г.

18. Патент US 7.586.373, 2009 г.

19. Патент US 2006/0215787, 2006 г.

20. Патент US 7.453.319, 2008 г.

21. Патент US 2004/0174216, fig. 2, 2004 г.

22. Патент US 7.215.200, fig. 6, 2007 г.

23. Патент US № 6.433.637, fig. 2, 2002 г.

24. Патент US № 6.392.485, 2002 г.

25. Патент US 5.963.085, fig. 3, 1999 г.

26. Патент US 6.788.143, 2004 г.

27. Патент US 4.390.850, 1983 г.

28. Патент US 6.696.894, fig. 1, 2004 г.

29. N. N. Prokopenko, N. V. Butyrlagin, A. V. Bugakova and A. A. Ignashin, "Method for speeding the micropower CMOS operational amplifiers with dual-input-stages," 2017 24th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Batumi, 2017, pp. 78-81.

30. K. O. Petrosyants, M. R. Ismail-zade, L. M. Sambursky, O. V. Dvornikov, B. G. Lvov and I. A. Kharitonov, "Automation of parameter extraction procedure for Si JFET SPICE model in the −200…+110°C temperature range," 2018 Moscow Workshop on Electronic and Networking Technologies (MWENT), Moscow, 2018, pp. 1-5. DOI: 10.1109/MWENT.2018.8337212

31. Создание низкотемпературных аналоговых ИС для обработки импульсных сигналов датчиков. Часть 2 / О. Дворников, В. Чеховский, В. Дятлов, Н. Прокопенко // Современная электроника, 2015, № 5. С. 24-28

32. O. V. Dvornikov, N. N. Prokopenko, N. V. Butyrlagin and I. V. Pakhomov, "The differential and differential difference operational amplifiers of sensor systems based on bipolar-field technological process AGAMC," 2016 International Siberian Conference on Control and Communications (SIBCON), Moscow, 2016, pp. 1-6. DOI: 10.1109/SIBCON.2016.7491792

33. Дворников О.В., Чеховский В.А., Дятлов В.Л., Прокопенко Н.Н. "Малошумящий электронный модуль обработки сигналов лавинных фотодиодов" Приборы и методы измерений, no. 2 (7), 2013, pp. 42-46.

34. Дворников О. Чеховский В., Дятлов В., Прокопенко Н. Применение структурных кристаллов для создания интерфейсов датчиков //Современная электроника. – 2014. – №. 1. – С. 32-37.

35. O. V. Dvornikov, A. V. Bugakova, N. N. Prokopenko, V. L. Dziatlau and I. V. Pakhomov, "The microcircuits MH2XA010-02/03 for signal processing of optoelectronic sensors," 2017 18th International Conference of Young Specialists on Micro/Nanotechnologies and Electron Devices (EDM), Erlagol, 2017, pp. 396-402. DOI: 10.1109/EDM.2017.7981781

36. Прокопенко Н.Н. Нелинейная активная коррекция в прецизионных аналоговых микросхемах (монография) // Ростов-на-Дону: Изд-во Северо-Кавказского научного центра высшей школы, 2000. 222с.

37. Операционные усилители с непосредственной связью каскадов: монография / Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. - Л.: «Энергия», 1979. - 148 с.