Результат интеллектуальной деятельности: БЫСТРОДЕЙСТВУЮЩИЙ БУФЕРНЫЙ УСИЛИТЕЛЬ

Вид РИД

Изобретение

Изобретение относится к области радиотехники и связи и может быть использовано в качестве выходного каскада для усиления быстроизменяющихся аналоговых сигналов по мощности (буферного усилителя), в структуре аналоговых микросхем различного функционального назначения, например, операционных усилителях (ОУ).

Одним из классических вариантов построения буферных усилителей (БУ) являются схемы на основе так называемых «бриллиантовых» составных транзисторов, которые широко применяются в современных аналоговых микросхемах [1-23], в том числе в быстродействующих драйверах линий связи и видеоусилителях (OPA633, BUF600/601, BUF604, BUF634, КМ1432УЕ1, AD9630, МА5033, MAX405, М1432УЕ2, М1432УЕ3 и др.).

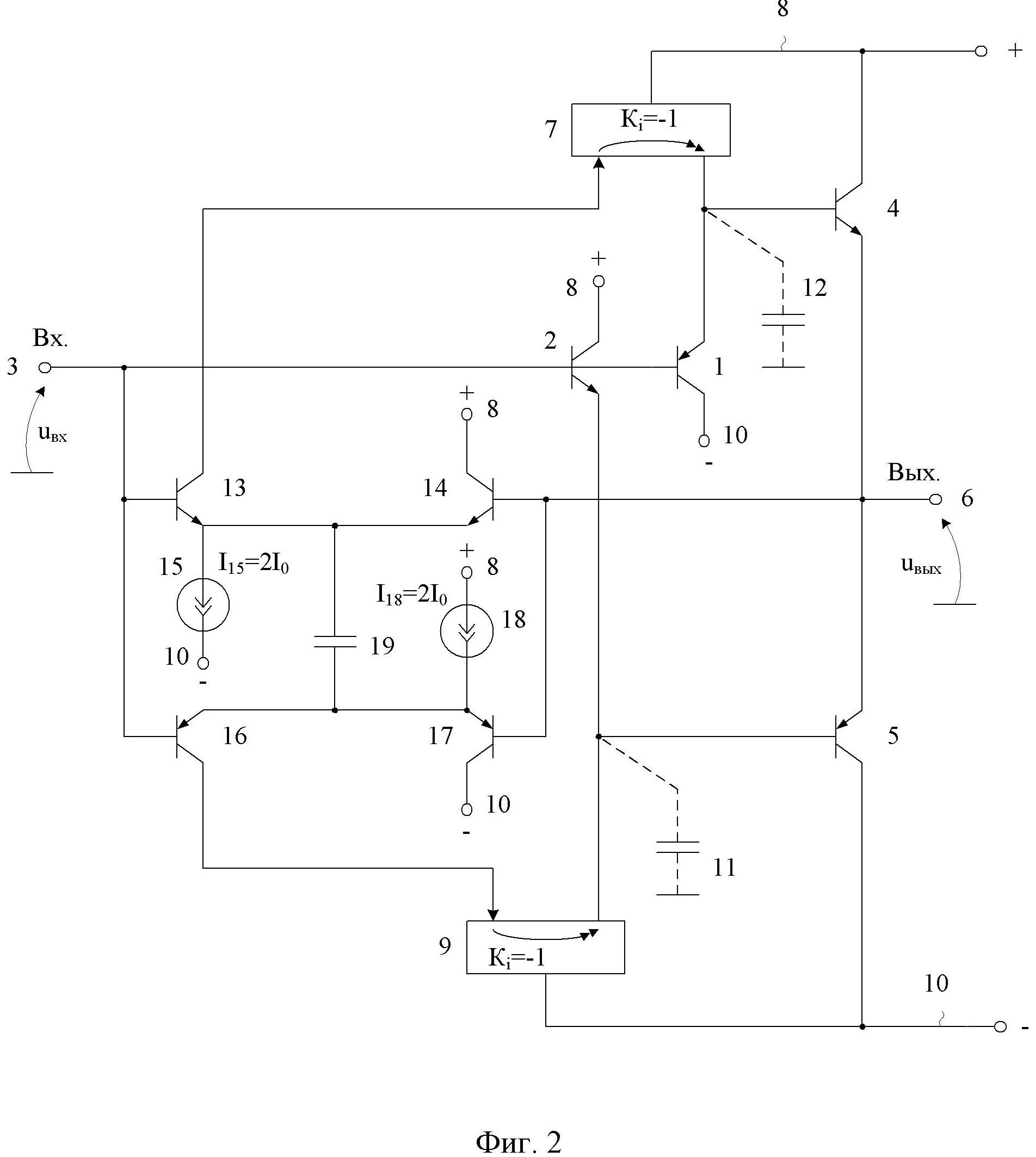

Ближайшим прототипом заявляемого устройства является БУ, представленный в патенте США № 5.512.859, fig 3. (эта архитектура БУ присутствует в большем числе других патентов [2-23]). Он содержит первый 1 и второй 2 входные транзисторы разного типа проводимости, объединенные базы которых подключены ко входу устройства 3, первый 4 и второй 5 выходные транзисторы разного типа проводимости, объединенные эмиттеры которых соединены с выходом устройства 6, первая 7 цепь управления статическим режимом первого 1 входного транзистора, согласованная с первой 8 шиной источника питания, связанная с эмиттером первого 1 входного транзистора и базой первого 4 выходного транзистора, вторая 9 цепь управления статическим режимом второго 2 входного транзистора, согласованная со второй 10 шиной источника питания, связанная с эмиттером второго 2 входного транзистора и базой второго 5 выходного транзистора, первая 11 паразитная емкость, связанная с базой второго 5 выходного транзистора, вторая 12 паразитная емкость, связанная с базой первого 4 выходного транзистора, причем коллекторы первого 4 выходного и второго 2 входного транзисторов связаны с первой 8 шиной источника питания, а коллекторы первого 1 входного и второго 5 выходного транзисторов связаны со второй 10 шиной источника питания.

Существенный недостаток известного буферного усилителя состоит в том, что он имеет относительно малую скорость нарастания выходного напряжения (SR), которая обусловлена наличием паразитных емкостей в базовой цепи первого 4 и второго 5 выходных транзисторов. Как следствие, при большом импульсном входном сигнале, из-за нелинейных режимов работы первого 1 и второго 2 входных транзисторов, время установления переходного процесса в известном БУ имеет сравнительно большие значения. Для многих быстродействующих применений БУ – это недопустимо.

Основная задача предполагаемого изобретения состоит в повышении максимальной скорости нарастания выходного напряжения и уменьшении времени установления переходного процесса в БУ при больших импульсных входных сигналах, соизмеренных с напряжением питания.

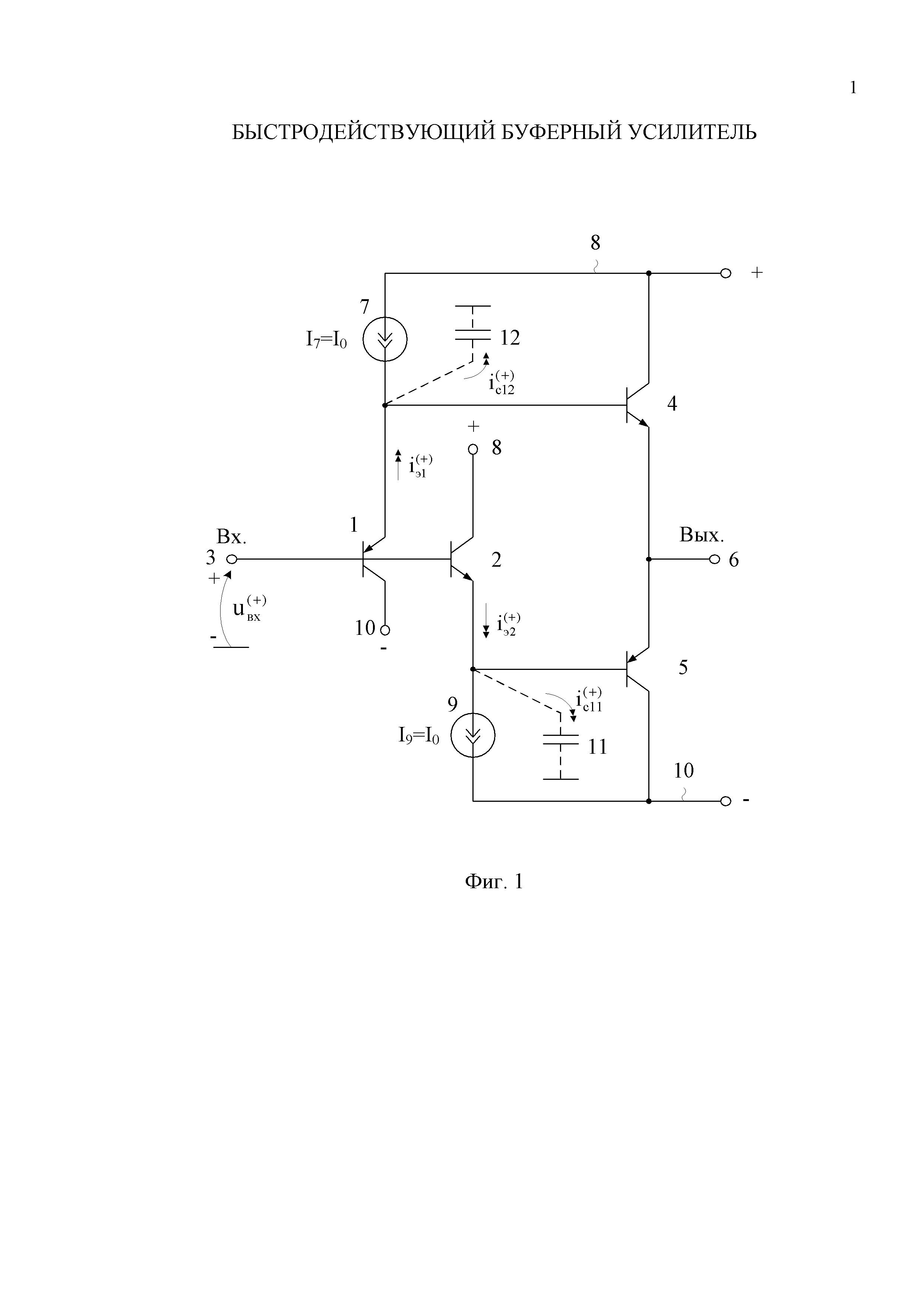

Поставленная задача достигается тем, что в буферном усилителе фиг. 1, содержащем первый 1 и второй 2 входные транзисторы разного типа проводимости, объединенные базы которых подключены ко входу устройства 3, первый 4 и второй 5 выходные транзисторы разного типа проводимости, объединенные эмиттеры которых соединены с выходом устройства 6, первая 7 цепь управления статическим режимом первого 1 входного транзистора, согласованная с первой 8 шиной источника питания, связанная с эмиттером первого 1 входного транзистора и базой первого 4 выходного транзистора, вторая 9 цепь управления статическим режимом второго 2 входного транзистора, согласованная со второй 10 шиной источника питания, связанная с эмиттером второго 2 входного транзистора и базой второго 5 выходного транзистора, первая 11 паразитная емкость, связанная с базой второго 5 выходного транзистора, вторая 12 паразитная емкость, связанная с базой первого 4 выходного транзистора, причем коллекторы первого 4 выходного и второго 2 входного транзисторов связаны с первой 8 шиной источника питания, а коллекторы первого 1 входного и второго 5 выходного транзисторов связаны со второй 10 шиной источника питания, предусмотрены новые элементы и связи – в качестве первой 7 и второй 9 цепей управления статическим режимом соответствующих первого 1 и второго 2 входных транзисторов применяются первый 7 и второй 9 инвертирующие усилители тока, база первого 13 дополнительного транзистора соединена со входом устройства 3, база второго 14 дополнительного транзистора соединена с выходом устройства 6, объединенные эмиттеры первого 13 и второго 14 дополнительных транзисторов связаны со второй 10 шиной источника питания через первый 15 дополнительный токостабилизирующий двухполюсник, коллектор второго 14 дополнительного транзистора подключен к первой 8 шине источника питания, а коллектор первого 13 дополнительного транзистора соединен со входом первого 7 инвертирующего усилителя тока, база третьего 16 дополнительного транзистора соединена со входом устройства 3, база четвертого 17 дополнительного транзистора соединена с выходом устройства 6, объединенные эмиттеры третьего 16 и четвертого 17 дополнительных транзисторов связаны с первой 8 шиной источника питания через второй 18 дополнительный токостабилизирующий двухполюсник, коллектор четвертого 17 дополнительного транзистора подключен ко второй 10 шине источника питания, а коллектор третьего 16 дополнительного транзистора соединен со входом второго 9 инвертирующего усилителя тока, причем между эмиттером первого 13 дополнительного транзистора и эмиттером третьего 16 дополнительного транзистора включен корректирующий конденсатор 19.

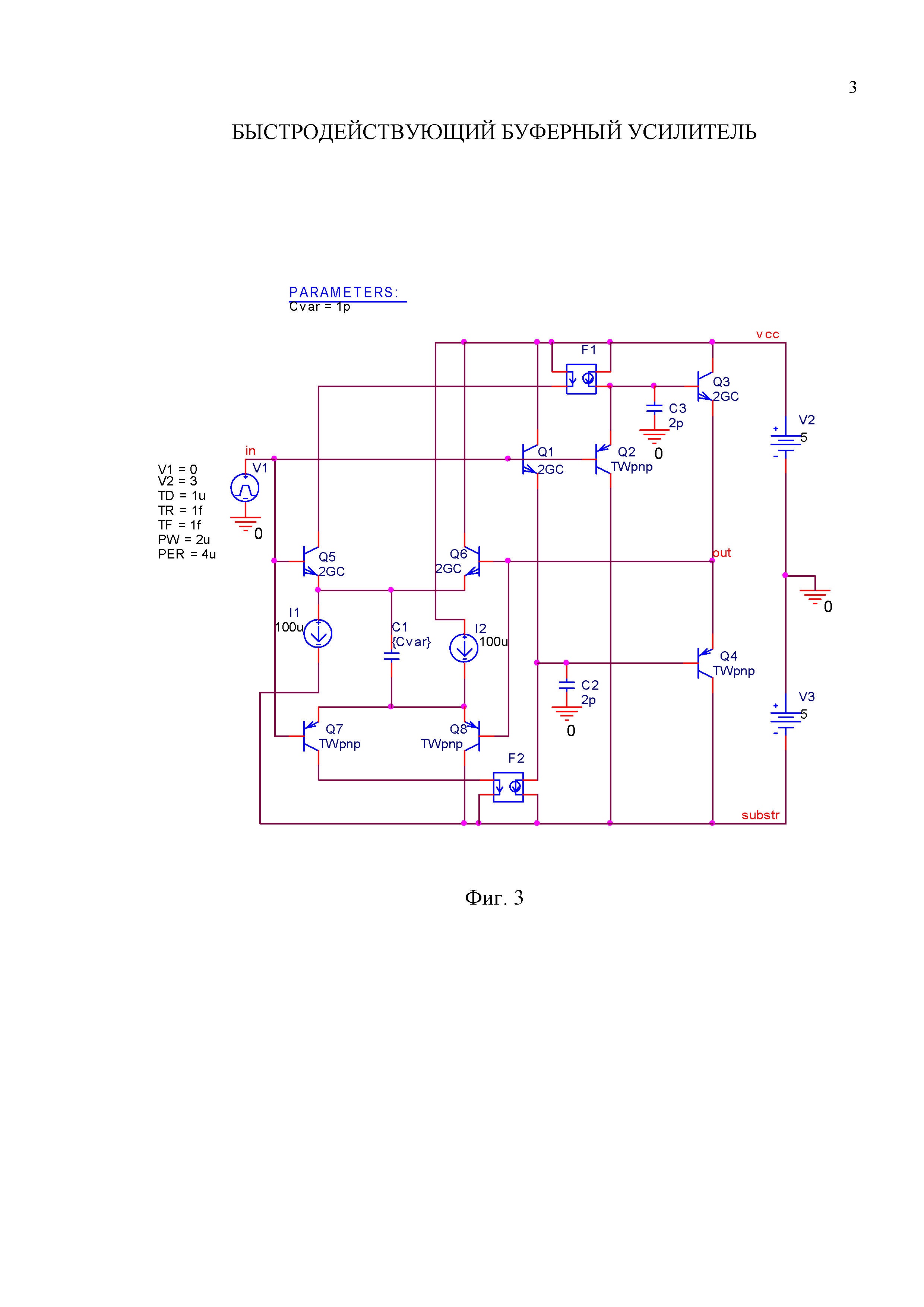

На чертеже фиг. 1 представлена схема БУ-прототип, а на чертеже фиг. 2 – схема заявляемого устройства.

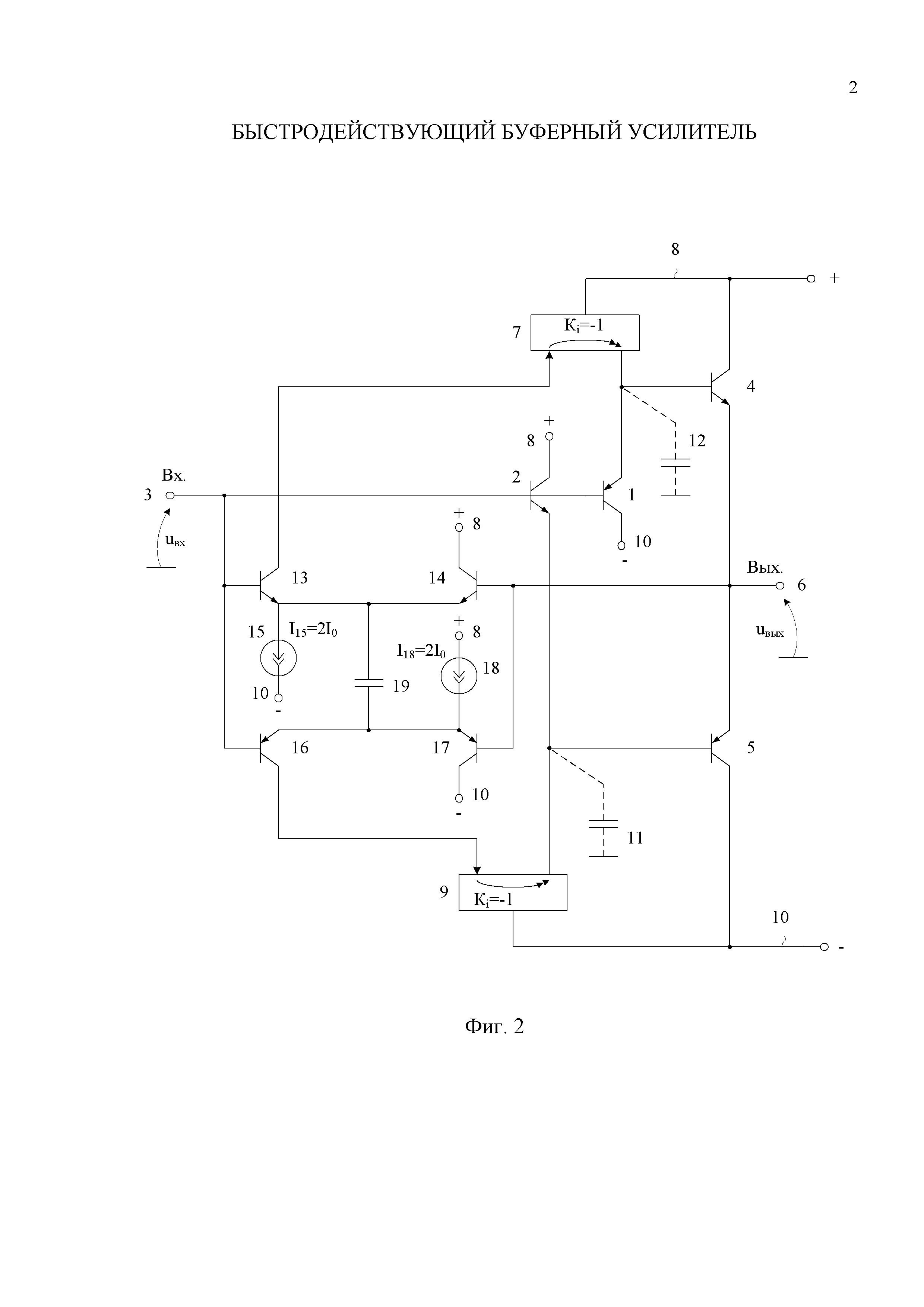

На чертеже фиг. 3 приведена схема заявляемого БУ фиг. 2 в среде PSpice на элементах радиационно-стойкого базового матричного кристалла АБМК_1.3 (ОАО «Интеграл», г. Минск).

На чертеже фиг. 4 показаны переходные процессы переднего фронта в заявляемом БУ фиг. 3 при амплитуде входного импульсного сигнала Uвх=3В и разных значениях ёмкости корректирующего конденсатора 19 С1(С19)=Сvar=0;10;50пФ.

На чертеже фиг. 5 показаны переходные процессы заднего фронта в заявляемом БУ фиг. 3 при амплитуде входного импульсного сигнала Uвх=3В и разных значениях ёмкости корректирующего конденсатора 19 С1(С19)=Сvar=0;10;50пФ.

Быстродействующий буферный усилитель фиг. 2 содержит первый 1 и второй 2 входные транзисторы разного типа проводимости, объединенные базы которых подключены ко входу устройства 3, первый 4 и второй 5 выходные транзисторы разного типа проводимости, объединенные эмиттеры которых соединены с выходом устройства 6, первая 7 цепь управления статическим режимом первого 1 входного транзистора, согласованная с первой 8 шиной источника питания, связанная с эмиттером первого 1 входного транзистора и базой первого 4 выходного транзистора, вторая 9 цепь управления статическим режимом второго 2 входного транзистора, согласованная со второй 10 шиной источника питания, связанная с эмиттером второго 2 входного транзистора и базой второго 5 выходного транзистора, первая 11 паразитная емкость, связанная с базой второго 5 выходного транзистора, вторая 12 паразитная емкость, связанная с базой первого 4 выходного транзистора, причем коллекторы первого 4 выходного и второго 2 входного транзисторов связаны с первой 8 шиной источника питания, а коллекторы первого 1 входного и второго 5 выходного транзисторов связаны со второй 10 шиной источника питания. В качестве в качестве первой 7 и второй 9 цепей управления статическим режимом соответствующих первого 1 и второго 2 входных транзисторов применяются первый 7 и второй 9 инвертирующие усилители тока, база первого 13 дополнительного транзистора соединена со входом устройства 3, база второго 14 дополнительного транзистора соединена с выходом устройства 6, объединенные эмиттеры первого 13 и второго 14 дополнительных транзисторов связаны со второй 10 шиной источника питания через первый 15 дополнительный токостабилизирующий двухполюсник, коллектор второго 14 дополнительного транзистора подключен к первой 8 шине источника питания, а коллектор первого 13 дополнительного транзистора соединен со входом первого 7 инвертирующего усилителя тока, база третьего 16 дополнительного транзистора соединена со входом устройства 3, база четвертого 17 дополнительного транзистора соединена с выходом устройства 6, объединенные эмиттеры третьего 16 и четвертого 17 дополнительных транзисторов связаны с первой 8 шиной источника питания через второй 18 дополнительный токостабилизирующий двухполюсник, коллектор четвертого 17 дополнительного транзистора подключен ко второй 10 шине источника питания, а коллектор третьего 16 дополнительного транзистора соединен со входом второго 9 инвертирующего усилителя тока, причем между эмиттером первого 13 дополнительного транзистора и эмиттером третьего 16 дополнительного транзистора включен корректирующий конденсатор 19.

Рассмотрим работу заявляемого БУ фиг. 2.

Статический режим схемы фиг. 2 устанавливается первым 15 и вторым 18 дополнительными токостабилизирующими двухполюсниками, а также зависит от разности между входным и выходным напряжениями БУ, которая в идеальном случае должна быть близка к нулю. При коэффициенте передачи по току Ki≈1 первого 7 и второго 9 инвертирующих усилителей тока статические эмиттерные токи первого 1

( ) и второго 2 (

) и второго 2 ( ) входных транзисторов будут определяться формулами

) входных транзисторов будут определяться формулами

|

При малых входных импульсных сигналах все элементы схемы БУ работают в линейном режиме, и как следствие, БУ имеет максимально возможное быстродействие. В этом режиме переменная составляющая напряжения между эмиттерами первого 13 (второго 14) и третьего 16 (четвертого 17) дополнительных транзисторов близка к нулю, так как приращения напряжений между входом 3 и выходом 6 устройства идентичны. Поэтому корректирующий конденсатор 19 не влияют на работу схемы БУ в режиме малого сигнала.

При большом положительном импульсном входном сигнале (соизмеримом с напряжением питания) второй 14 и третий 16 дополнительные транзисторы запираются, и поэтому медленный заряд второй 12 паразитной емкости обеспечивается выходным током первого 7 инвертирующего усилителя тока. В этом режиме образуется большая разность напряжений между эмиттерами первого 13 и четвертого 17 дополнительных транзисторов, которая дифференцируются корректирующим конденсатором 19. В результате через корректирующий конденсатор 19 формируется большой импульс тока, который передается через первый 13 дополнительный транзистор на вход первого 7 инвертирующего усилителя тока, а затем – в цепь базы первого 4 выходного транзистора. Как следствие скорость перезаряда второй 12 паразитной емкости существенно возрастает, что способствует быстрому увеличению напряжения на базе первого 4 выходного транзистора и, как следствие, выходного напряжения БУ.

По мере приближения уровня выходного напряжения uвых к уровню входного напряжения БУ uвх, приращение напряжения на корректирующем конденсаторе 19, и следовательно, ток через данный корректирующий конденсатор 19 уменьшаются. В конечном итоге схема БУ фиг. 2 входит в линейный режим, когда ток заряда второй 12 паразитной емкости уменьшается до уровня тока 0,5I15=I0 первого 15 дополнительного токостабилизирующего двухполюсника.

Компьютерное моделирование схемы фиг. 3, представленное на чертежах фиг. 4 и фиг. 5, показывает, что в сравнении с БУ-прототипом динамические параметры предлагаемого БУ существенно улучшаются. Так для переднего фронта скорость нарастания выходного напряжения БУ увеличивается более, чем в 310 раз (см. табл. 1).

Таблица 1 – Взаимосвязь ёмкости корректирующего конденсатора 19 С1(С19)=Сvar=0;10;50пФ и максимальной скорости нарастания выходного напряжения БУ фиг. 3 при статических токах I1=I2=100мкА

|

Замечательной особенностью схемы фиг. 2 является малое значение напряжение смещения нуля. Это обусловлено наличием в данной схеме цепи отрицательной обратной связи между входом 3 и выходом 6 устройства, которая образуется первым 13 и вторым 14 (третьим 16 и четвертым 17) дополнительными транзисторами, а также первым 7 и вторым 9 инвертирующими усилителями тока.

Таким образом, заявляемое устройство в сравнением с БУ-прототипом обладает более высокими техническими параметрами.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США № 5.512.859 fig.3

2. Патент США № 6.268.769 fig.3

3. Патент США № 6.420.933

4. Патент США № 5.223.122

5. Патентная заявка США № 2004/0196101

6. Патентная заявка США № 2005/0264358 fig.1

7. Патентная заявка США № 2002/0175759

8. Патент США № 5.049.653 fig.8

9. Патент США № 4.837.523

10. Патент США № 5.179.355

11. Патент Японии JP 10.163.763

12. Патент Японии JP 10.270.954

13. Патент США № 5.170.134 fig.6

14. Патент США № 4.540.950

15. Патент США № 4.424.493

16. Патент Японии JP 6310950

17. Патент США № 5.378.938

18. Патент США № 4.827.223

19. Патент США № 6.160.451

20. Патент США № 4.639.685

21. А.св. СССР 1506512

22. Патент США № 5.399.991

23.Патент США № 6.542.032.

Быстродействующий буферный усилитель, содержащий первый (1) и второй (2) входные транзисторы разного типа проводимости, объединенные базы которых подключены к входу устройства (3), первый (4) и второй (5) выходные транзисторы разного типа проводимости, объединенные эмиттеры которых соединены с выходом устройства (6), первую (7) цепь управления статическим режимом первого (1) входного транзистора, согласованную с первой (8) шиной источника питания, связанную с эмиттером первого (1) входного транзистора и базой первого (4) выходного транзистора, вторую (9) цепь управления статическим режимом второго (2) входного транзистора, согласованную со второй (10) шиной источника питания, связанную с эмиттером второго (2) входного транзистора и базой второго (5) выходного транзистора, первую (11) паразитную емкость, связанную с базой второго (5) выходного транзистора, вторую (12) паразитную емкость, связанную с базой первого (4) выходного транзистора, причем коллекторы первого (4) выходного и второго (2) входного транзисторов связаны с первой (8) шиной источника питания, а коллекторы первого (1) входного и второго (5) выходного транзисторов связаны со второй (10) шиной источника питания, отличающийся тем, что в качестве первой (7) и второй (9) цепей управления статическим режимом соответствующих первого (1) и второго (2) входных транзисторов применяются первый (7) и второй (9) инвертирующие усилители тока, база первого (13) дополнительного транзистора соединена с входом устройства (3), база второго (14) дополнительного транзистора соединена с выходом устройства (6), объединенные эмиттеры первого (13) и второго (14) дополнительных транзисторов связаны со второй (10) шиной источника питания через первый (15) дополнительный токостабилизирующий двухполюсник, коллектор второго (14) дополнительного транзистора подключен к первой (8) шине источника питания, а коллектор первого (13) дополнительного транзистора соединен с входом первого (7) инвертирующего усилителя тока, база третьего (16) дополнительного транзистора соединена с входом устройства (3), база четвертого (17) дополнительного транзистора соединена с выходом устройства (6), объединенные эмиттеры третьего (16) и четвертого (17) дополнительных транзисторов связаны с первой (8) шиной источника питания через второй (18) дополнительный токостабилизирующий двухполюсник, коллектор четвертого (17) дополнительного транзистора подключен ко второй (10) шине источника питания, а коллектор третьего (16) дополнительного транзистора соединен с входом второго (9) инвертирующего усилителя тока, причем между эмиттером первого (13) дополнительного транзистора и эмиттером третьего (16) дополнительного транзистора включен корректирующий конденсатор (19).