Результат интеллектуальной деятельности: ТОНКОПЛЕНОЧНЫЙ ТРАНЗИСТОР ИЗ НИЗКОТЕМПЕРАТУРНОГО ПОЛИКРИСТАЛЛИЧЕСКОГО КРЕМНИЯ И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ

Вид РИД

Изобретение

Область техники

Настоящее изобретение относится к технической области изготовления тонкопленочных транзисторов из низкотемпературного поликристаллического кремния, в частности к тонкопленочному транзистору из низкотемпературного поликристаллического кремния, обладающему определенными электрическими характеристиками и надежностью, а также к способу изготовления такого тонкопленочного транзистора.

Предпосылки для создания изобретения

Жидкокристаллический дисплей (ЖК-дисплей) в настоящее время является наиболее развитой технологией отображения на плоской панели. Например, все мобильные телефоны, цифровые фотоаппараты, видеокамеры, ноутбуки и мониторы, которые широко используются в повседневной жизни, изготовлены с использованием этой технологии.

Однако, поскольку области применения новых технологий расширяются, и требования людей к внешнему виду дисплеев повышаются, направлением и мотивацией для развития новых технологий отображения информации стал дисплей с плоской панелью, который отличается повышенным качеством изображения, высокой четкостью, высокой яркостью и низкой ценой. Тонкопленочный транзистор (ТПТ) из низкотемпературного поликристаллического кремния (НТПК) в дисплее с плоской панелью, помимо своей характеристики активного возбуждения, точно представляет собой важный технологический прорыв в достижении вышеуказанных целей.

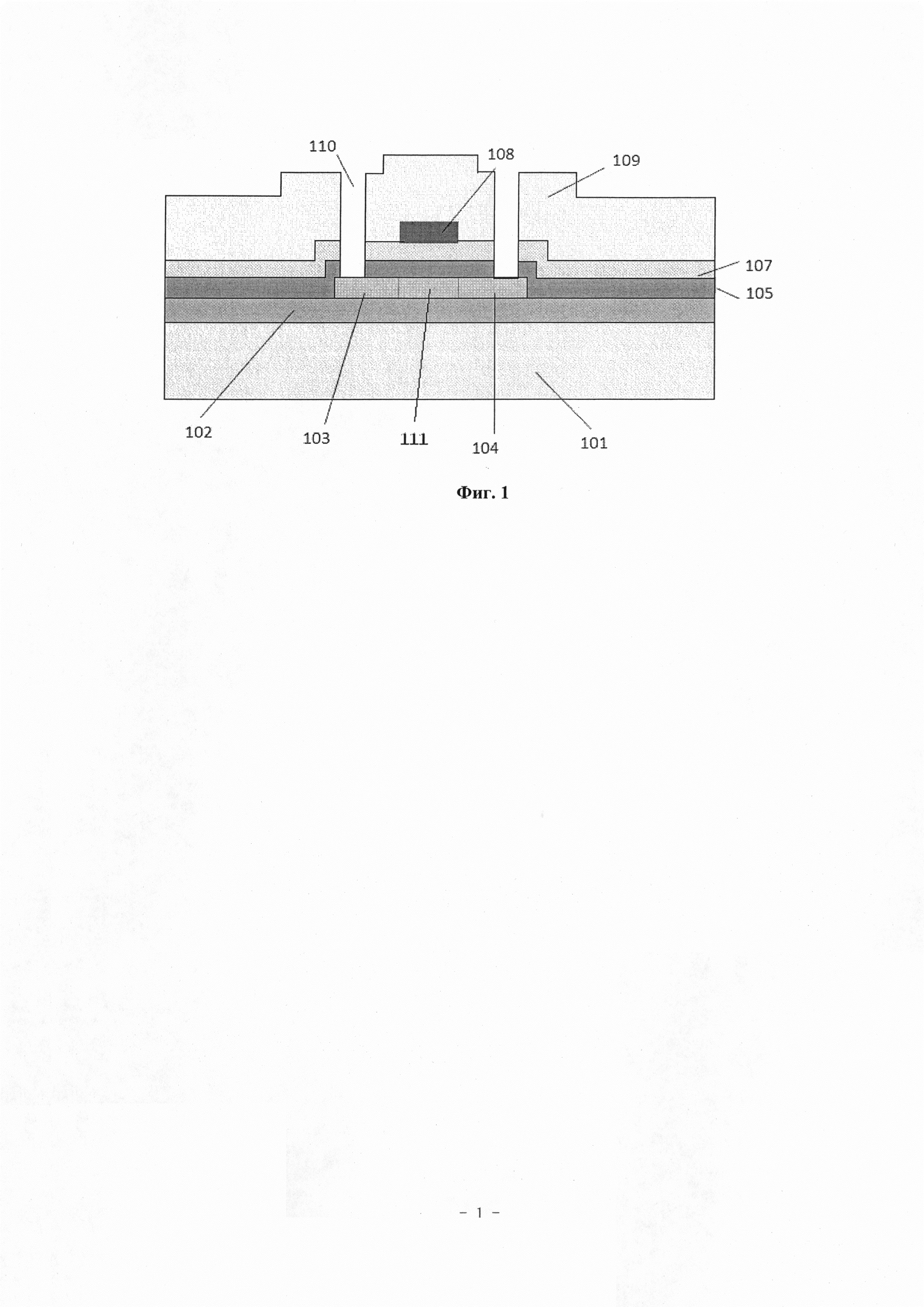

Известный ТПТ НТПК, показанный на Фиг. 1, включает стеклянную подложку 101 и буферный слой 102, расположенный на стеклянной подложке 101. На буферном слое 102 сформирован слой поликристаллического кремния, который включает электрод истока, расположенный в области истока 103, электрод стока, расположенный в области стока 104 и подзатворный слой GI, расположенный на области 111 канала. Электрод затвора 108 и пассивирующий слой 109 сформированы на подзатворном слое GI. Слой GI обычно имеет двухслойную композитную структуру, включающую диэлектрический слой 105 и диэлектрический слой 107, которые обычно выполнены из SiO2 и SiNx.

Однако подзатворный слой, сформированный из SiNx и SiO2, имеет плохие характеристики поверхности контакта и электропроводность тонкой пленки, а также подтравленные участки, когда на нем выполнены сквозные отверстия, что означает, что отверстия в SiO2 больше отверстий в SiNx из-за более высокой скорости травления SiO2 чем SiNx, что и приводит к плохим характеристикам контактов.

Поэтому для того чтобы решить вышеуказанные задачи, главная цель усилий в этой отрасли промышленности заключается в разработке способа изготовления тонкопленочного транзистора из низкотемпературного поликристаллического кремния, который имеет относительно надежную электропроводность контактов и может эффективно уменьшать паразитную емкость и, таким образом, повышать скорость срабатывания транзистора.

Раскрытие изобретения

Одна из технических задач, решаемых настоящим изобретением, заключается в том, чтобы предложить способ изготовления тонкопленочного транзистора из низкотемпературного поликристаллического кремния, который имеет относительно хорошую электропроводность контактов и может эффективно уменьшать паразитную емкость, этим повышая скорость срабатывания транзистора. Помимо этого настоящее изобретение также предлагает тонкопленочный транзистор из низкотемпературного поликристаллического кремния.

(1) Для решения вышеуказанных технических задач настоящее изобретение предлагает способ изготовления тонкопленочного транзистора из низкотемпературного поликристаллического кремния, включающий следующие этапы: предоставление изоляционной подложки; формирование на буферном слое изоляционной подложки по меньшей мере одного слоя поликристаллического кремния, на поверхности которого расположены область истока, область стока и область канала тонкопленочного транзистора из низкотемпературного поликристаллического кремния; выполнение процесса плазмохимического осаждения из паровой фазы (PECVD) по меньшей мере три раза, чтобы последовательно сформировать по меньшей мере три диэлектрических слоя на области канала, таким образом формируя композитный подзатворный слой, при этом плотность каждого диэлектрического слоя увеличивается в порядке их формирования в данном способе изготовления, и формирование электрода затвора на композитном подзатворном слое.

(2) В одном предпочтительном варианте осуществления согласно (1) настоящего изобретения композитный подзатворный слой включает первый диэлектрический слой, второй диэлектрический слой и третий диэлектрический слой, при этом первый диэлектрический слой изготовлен из SiO2, второй диэлектрический слой изготовлен из SiON и третий диэлектрический слой изготовлен из SiNx.

(3) В одном предпочтительном варианте осуществления согласно (1) или (2) настоящего изобретения толщина пленки первого диэлектрического слоя больше, чем толщина пленки второго и третьего диэлектрических слоев.

(4) В одном предпочтительном варианте осуществления согласно любому из (1)-(3) настоящего изобретения толщина пленки SiO2 первого диэлектрического слоя составляет от 1000 до 1500 ангстрем, толщина пленки SiON второго диэлектрического слоя составляет от 100 до 1000 ангстрем, и толщина пленки SiNx третьего диэлектрического слоя составляет от 100 до 500 ангстрем.

(5) В одном предпочтительном варианте осуществления согласно любому из (1)-(4) настоящего изобретения формирование слоя поликристаллического кремния включает следующие этапы: выполнение процесса напыления, чтобы сформировать слой аморфного кремния на поверхности изоляционной подложки, и выполнение процесса отжига, чтобы повторно кристаллизовать слой аморфного кремния и получить слой поликристаллического кремния, при этом процесс отжига включает операцию отжига с помощью эксимерного лазера.

(6) В одном предпочтительном варианте осуществления согласно любому из (1)-(5) настоящего изобретения, после того как будет сформирован электрод затвора, выполняют процесс ионной имплантации, используя электрод затвора в качестве маски, чтобы сформировать электрод истока и электрод стока в области истока и области стока, соответственно, на поликремниевом слое; и после процесса ионной имплантации выполняют процесс активации, чтобы активировать примеси в электроде истока и электроде стока.

(7) Согласно еще одному аспекту настоящего изобретения, также предложен тонкопленочный транзистор из низкотемпературного поликристаллического кремния, включающий по меньшей мере подзатворный слой, которым является композитный изоляционный слой, включающий по меньшей мере три диэлектрических слоя, при этом плотность каждого диэлектрического слоя последовательно увеличивается в порядке их формирования в данном способе изготовления.

(8) В одном предпочтительном варианте осуществления согласно (7) настоящему изобретению подзатворный слой включает первый диэлектрический слой, второй диэлектрический слой и третий диэлектрический слой. Первый диэлектрический слой изготовлен из SiO2, второй диэлектрический слой изготовлен из SiON и третий диэлектрический слой изготовлен из SiNx.

(9) В одном предпочтительном варианте осуществления согласно (7) или (8) настоящего изобретения толщина пленки первого диэлектрического слоя больше, чем толщина пленки второго и третьего диэлектрических слоев.

(10) В одном предпочтительном варианте осуществления согласно любому из (7)-(9) настоящего изобретения толщина пленки SiO2 первого диэлектрического слоя составляет от 1000 до 1500 ангстрем, толщина пленки SiON второго диэлектрического слоя составляет от 100 до 1000 ангстрем, и толщина пленки SiNx третьего диэлектрического слоя составляет от 100 до 500 ангстрем.

По сравнению с известным уровнем техники, один или несколько примеров настоящего изобретения имеют следующие преимущества. Поскольку согласно настоящему изобретению учитывается отношение между плотностью каждого слоя композитного изоляционного слоя и плотностью других его слоев, каждый слой в композитном изоляционном слое тонкопленочного транзистора из низкотемпературного поликристаллического кремния, полученный способом согласно настоящему изобретению, имеет улучшенные характеристики контакта поверхности и электропроводности тонкой пленки. Также учитывается толщина пленки каждого слоя в композитном изоляционном слое, так что паразитная емкость может быть эффективно уменьшена, и, таким образом, скорость срабатывания транзистора может быть повышена.

Другие признаки и преимущества настоящего изобретения будут проиллюстрированы и станут частично понятны в последующем описании, или же могут быть поняты посредством реализации настоящего изобретения. Цели и другие преимущества настоящего изобретения могут быть достигнуты и получены на основании структур, указанных в описании, формуле изобретения и на прилагаемых чертежах.

Краткое описание чертежей

Прилагаемые чертежи, которые являются частью описания, представлены для дальнейшей иллюстрации настоящего изобретения вместе с примерами. Они не должны истолковываться как ограничивающие настоящее изобретение. На прилагаемых чертежах:

Фиг. 1 - схема частичной структуры тонкопленочного транзистора из низкотемпературного поликристаллического кремния, известного из уровня техники;

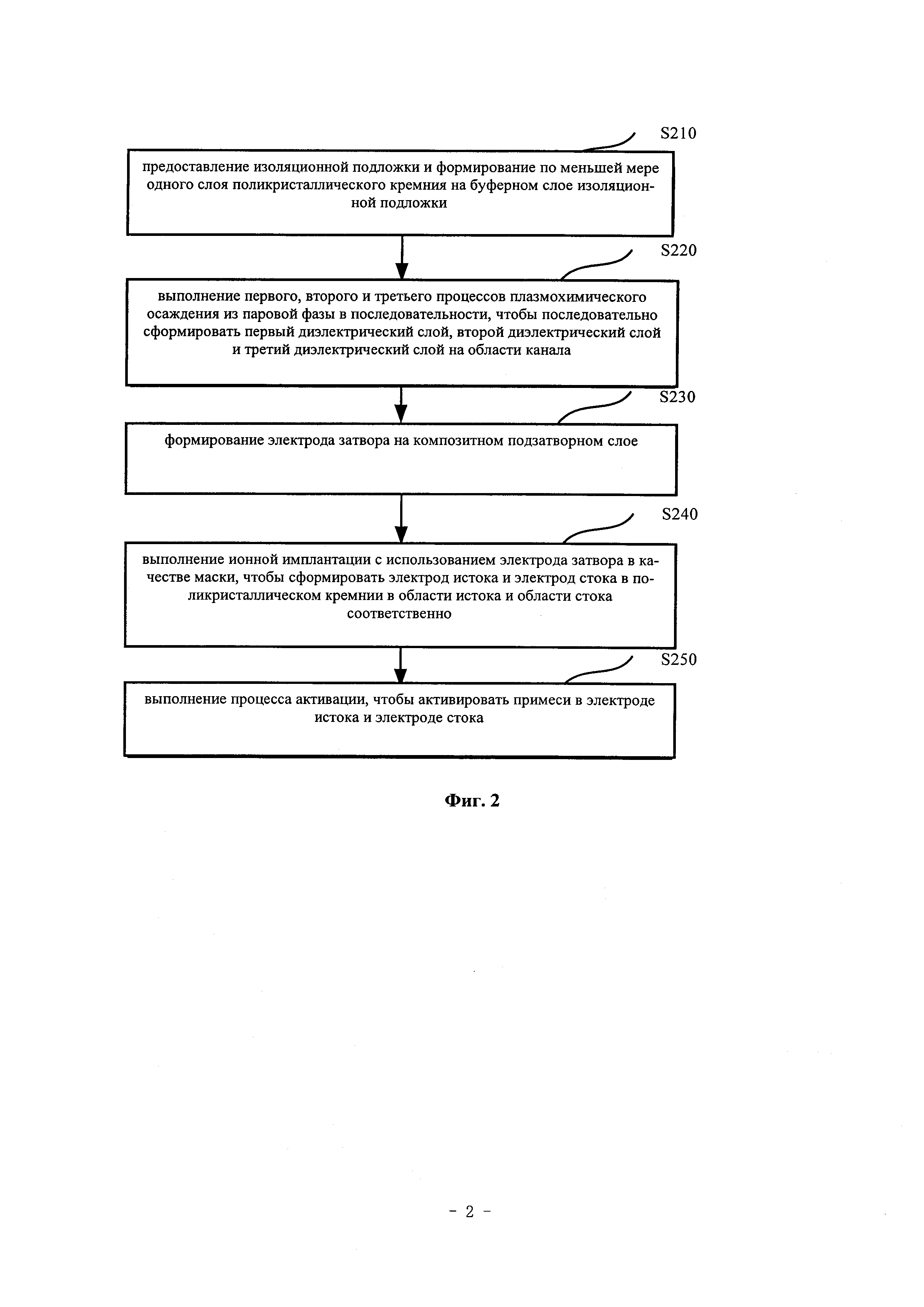

Фиг. 2 - схема технологического процесса способа изготовления тонкопленочного транзистора из низкотемпературного поликристаллического кремния согласно одному примеру настоящего изобретения;

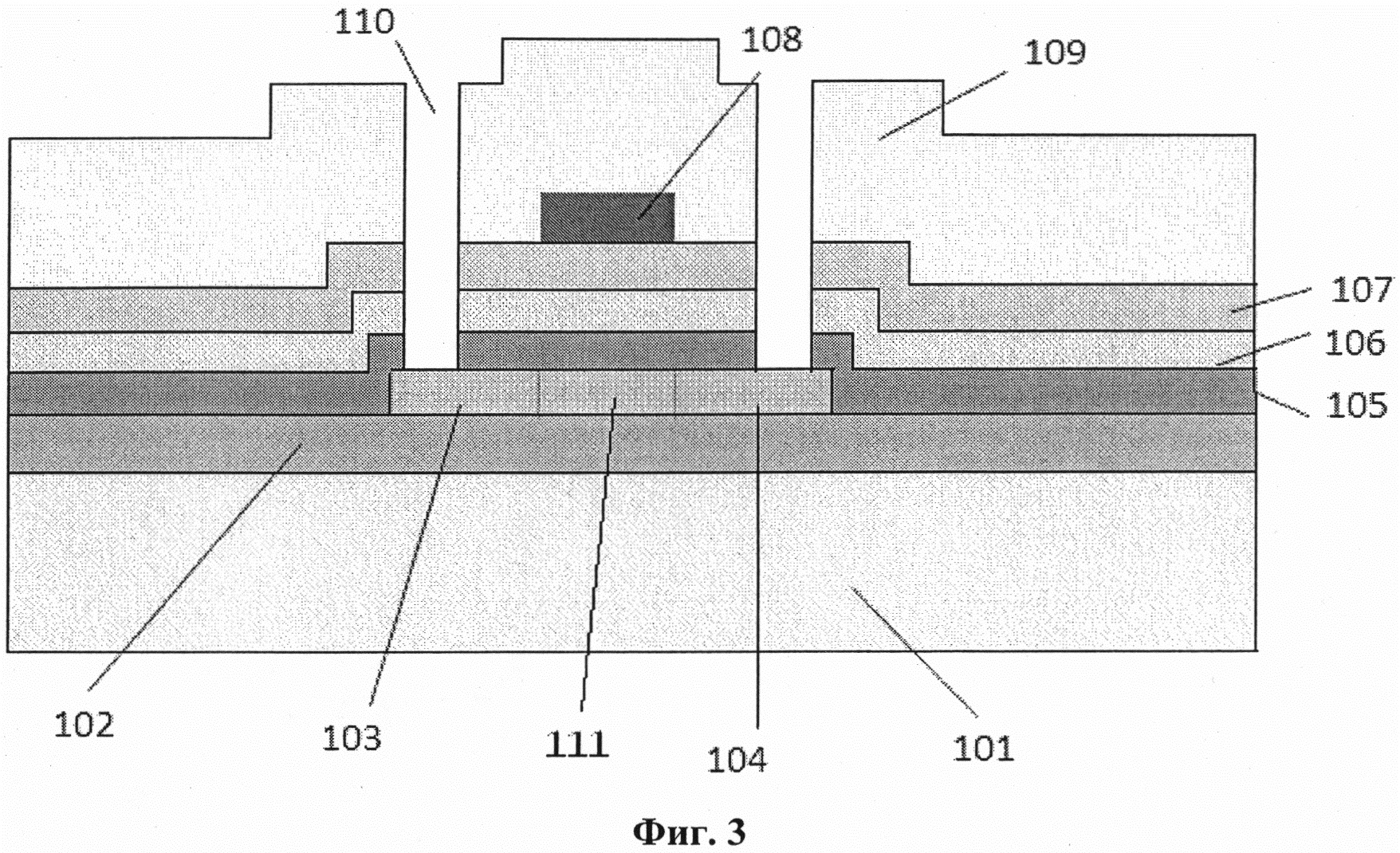

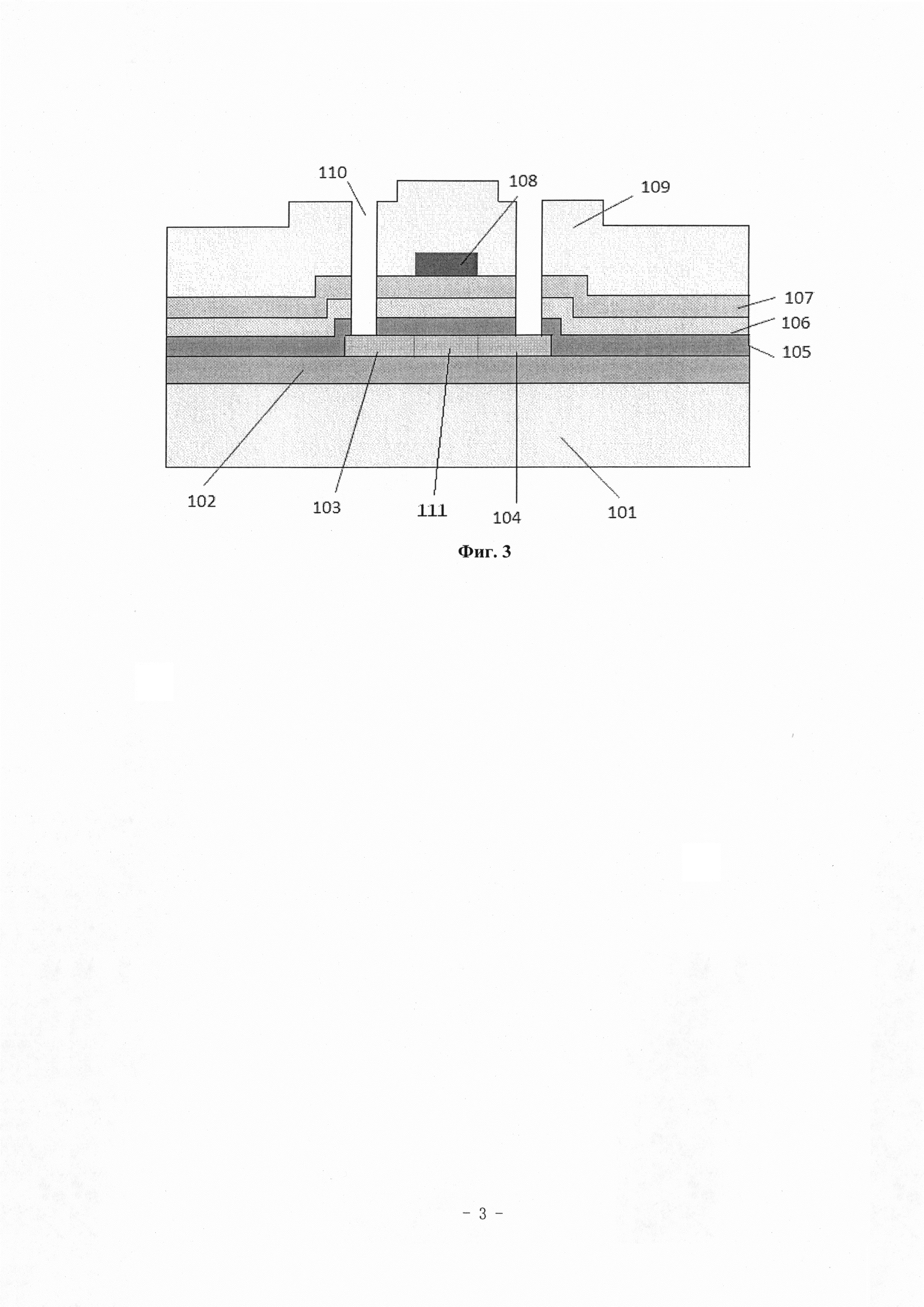

Фиг. 3 - схема частичной структуры тонкопленочного транзистора из низкотемпературного поликристаллического кремния согласно одному примеру настоящего изобретения.

Подробное описание вариантов осуществления

Для объяснения целей, технических решений и преимуществ настоящего изобретения оно будет подробно описано ниже в связи с прилагаемыми чертежами.

На Фиг. 2 показана схема технологического процесса способа изготовления тонкопленочного транзистора из низкотемпературного поликристаллического кремния согласно одному примеру настоящего изобретения. Способ изготовления НТПК ТПТ будет описан ниже со ссылками на Фиг. 2 и Фиг. 3.

На Этапе S210 получают изоляционную подложку 101 и формируют по меньшей мере один слой поликристаллического кремния (НТПК) на буферном слое 102 изоляционной подложки 101. Область истока 103, область стока 104 и область канала 111 НТПК ТПТ располагают на поверхности слоя поликристаллического кремния.

Следует сказать, что изоляционной подложкой 101 может быть стеклянная подложка или кварцевая подложка, и буферным слоем 102 является слой SiO2, сформированный на изоляционной подложке 101 посредством плазмохимического осаждения из паровой фазы.

Помимо этого, формирование слоя НТПК также включает следующие процессы: сначала выполняют процесс напыления, чтобы сформировать слой аморфного кремния (a-Si) на поверхности изоляционной подложки 101, и затем выполняют процесс отжига, чтобы повторно кристаллизовать слой a-Si и сформировать слой поликристаллического кремния. Вышеупомянутый процесс отжига включает операцию отжига с помощью эксимерного лазера.

На Этапе S220 первый, второй и третий процесса плазмохимического осаждения из паровой фазы выполняют в последовательности, чтобы последовательно сформировать первый диэлектрический слой 105, второй диэлектрический слой 106 и третий диэлектрический слой 107 на вышеупомянутой области канала 111. Эти три диэлектрических слоя совместно образуют композитный подзатворный слой (GI), при этом плотность каждого диэлектрического слоя последовательно увеличивается в порядке их формирования в данном способе изготовления, а именно плотность первого диэлектрического слоя 105 меньше чем плотность второго диэлектрического слоя 106, и плотность второго диэлектрического слоя 106 меньше чем плотность третьего диэлектрического слоя 107.

Более конкретно, первый диэлектрический слой 105 осаждают на поверхность слоя поликристаллического кремния посредством первого процесса плазмохимического осаждения из паровой фазы, затем второй диэлектрический слой 106 осаждают на первый диэлектрический слой 105 посредством второго процесса плазмохимического осаждения из паровой фазы и затем третий диэлектрический слой 107 осаждают на второй диэлектрический слой 106 посредством третьего процесса плазмохимического осаждения из паровой фазы.

Следует сказать, что процессы плазмохимического осаждения из паровой фазы слоя GI выполняют непрерывно в одном реакторе для получения кремниевых пластин.

Предпочтительно, первый диэлектрический слой 105 композитного GI слоя изготовлен из SiO2, второй диэлектрический слой 106 изготовлен из SiON и третий диэлектрический слой 107 изготовлен из SiNx. SiO2 в первом диэлектрическом слое 105 композитного GI слоя и буферный слой 102 используют для улучшения контактных характеристик НТПК, SiNx в третьем диэлектрическом слое 107 композитного GI слоя используют для блокирования паров воды и ионов металлов, и SiON во втором диэлектрическом слое 106 в основном используют для улучшения электропроводности контакта между первым диэлектрическим слоем 105 и третьим диэлектрическим слоем 107 (плотность: SiNx>SiON>SiO2).

В данном случае композитный подзатворный слой, включающий три вышеупомянутых диэлектрических слоя, может не только улучшить характеристику контакта между им самим и слоем низкотемпературного поликристаллического кремния и предотвращать попадание паров воды и ионов металлов на поверхность раздела и внутрь слоя низкотемпературного поликристаллического кремния, но и улучшать характеристику контакта поверхности и электропроводность тонкой пленки.

Должно легко пониматься, что это просто один пример и композитный подзатворный слой может включать другое число слоев, например, четыре или пять, то есть специалист в данной области техники может выполнить четыре или пять диэлектрических слоев посредством четырех или пяти процессов плазмохимического осаждения из паровой фазы. Важно заметить, что плотность каждого слоя композитного подзатворного слоя последовательно увеличивается в порядке их формирования в данном способе изготовления.

Помимо этого толщина пленки первого диэлектрического слоя 105 существенно больше чем толщина пленки второго диэлектрического слоя 106 и третьего диэлектрического слоя 107. Таким образом может быть эффективно уменьшена паразитная емкость. Предпочтительно, толщина пленки SiO2 первого диэлектрического слоя составляет приблизительно от 1000 до 1500 ангстрем, толщина пленки SiON второго диэлектрического слоя составляет приблизительно от 100 до 1000 ангстрем, и толщина пленки SiNx третьего диэлектрического слоя составляет приблизительно от 100 до 500 ангстрем.

На Этапе S230 формируют электрод затвора 108 на композитном GI слое.

Следует сказать, что материал для вышеупомянутого электрода затвора может быть, предпочтительно, выбран из вольфрама, хрома, алюминия, молибдена и меди.

На Этапе S240 выполняют процесс ионной имплантации, используя электрод затвора 108 в качестве маски, чтобы сформировать электрод истока и электрод стока в области истока 103 и области стока 104, соответственно, на вышеупомянутом слое поликристаллического кремния через сквозные отверстия 110.

На Этапе S250 выполняют процесс активации, чтобы активировать примеси в электроде истока и электроде стока.

В заключение снова выполняют процесс плазмохимического осаждения из паровой фазы, чтобы сформировать пассивирующий слой, который может быть выполнен из SiO или SiNx.

В данном случае, на основании технологического процесса способа согласно настоящему изобретению, в итоге получают структуру тонкопленочного транзистора из низкотемпературного поликристаллического кремния, показанную на Фиг. 3.

В заключение, поскольку согласно настоящему изобретению учитывается отношение между плотностью каждого слоя композитного подзатворного слоя и плотностью других его слоев, каждый слой в композитном подзатворном слое тонкопленочного транзистора из низкотемпературного поликристаллического кремния, изготовленного способом согласно настоящему изобретению, имеет улучшенные характеристики контакта поверхности и электропроводности тонкой пленки. Также учитывается толщина пленки каждого слоя в композитном подзатворном слое, так что паразитная емкость может быть эффективно уменьшена, и таким образом, скорость срабатывания транзистора может быть повышена. А именно путем повышения качества формируемой пленки GI могут быть повышены электрическая характеристика и надежность тонкопленочного транзистора из низкотемпературного поликристаллического кремния.

Выше описаны просто предпочтительные варианты осуществления настоящего изобретения, которые не должны истолковываться как ограничивающие объем настоящего изобретения. Любые изменения или замены в техническом объеме, раскрытом в настоящем изобретении, которые легко очевидны любому специалисту в данной области техники, должны считаться включенными в объем настоящего изобретения. Соответственно, объем настоящего изобретения должен определяться только формулой изобретения.