Результат интеллектуальной деятельности: ДИСПЛЕЙ С АКТИВНОЙ МАТРИЦЕЙ, МИКРОСХЕМА ВОЗБУЖДЕНИЯ РАЗВЕРТКИ И СПОСОБ ИХ ИЗГОТОВЛЕНИЯ

Вид РИД

Изобретение

1. ОБЛАСТЬ ТЕХНИКИ

[0001] Настоящее раскрытие относится к технологии производства жидкокристаллических дисплеев (LCD) и, более конкретно, к дисплею с активной матрицей, микросхеме возбуждения развертки и к способу их изготовления.

2. ОПИСАНИЕ ИЗВЕСТНОГО УРОВНЯ ТЕХНИКИ

[0002] В настоящее время микросхемы возбуждения развертки имеют три типа сигналов управления для переключения состояния включено/выключено каждой строки дисплея с активной матрицей. Сигналами управления являются, соответственно, сигналы импульсов запускающего напряжения (STV), сигналы импульсов напряжения тактирования (CKV) и сигналы разрешения выхода (ОЕ). На Фиг. 1 показана форма волны известных сигналов возбуждения развертки. Как показано, сигналы STV управляют исходным состоянием первой строки. Сигналы CKV управляют частотой включения/выключения каждой строки. После детектирования переднего фронта сигналов STV сигналы ОЕ располагаются между состояниями включено/выключено каждой строки. Сигналы ОЕ сжимают выходное напряжение в течение периода высокого уровня. Сигналы ОЕ управляют временем переключения состояния включено/выключено каждой строки, так что состояния включено/выключено чередуются. Таким образом, устраняется задержка сигналов развертки из-за паразитной емкости.

[0003] Вышеупомянутые три типа сигналов управления генерируются микросхемами управления тактированием и передаются на стеклянную подложку микросхемой с ПО на микросхемы возбуждения данных. Сигналы управления должны также передаваться на микросхемы возбуждения развертки по трем линиям передачи на стеклянной подложке. Как таковая, конструкция дисплея с активной матрицей, особенно для дисплея с узкой окантовкой, очень сложная. Можно понять, что хотя некоторое число линий передачи расположено на микросхеме с ПО, сложность соединения увеличивается. Более того, необходимо некоторое число выходных контактов соответствующих микросхем управления тактированием и входных контактов соответствующих микро-схем возбуждения развертки, что приводит к дополнительным расходам.

РАСКРЫТИЕ

[0004] Цель изобретения заключается в том, чтобы предложить дисплей с активной матрицей, микросхему возбуждения развертки и способ их изготовления, чтобы уменьшить число линий передачи.

[0005] В одном аспекте микросхема возбуждения развертки для дисплея с активной матрицей включает: модуль задержки, причем на вход модуля задержки по ступают входные сигналы, которые должны подвергнуться двойной задержке, входные сигналы интегрируются начальными сигналами импульсов напряжения тактирования (CKV) и сигналами импульсов запускающего напряжения (STV), первый выход модуля задержки выводит сигналы разрешения выхода (ОЕ) после того, как входные сигналы пройдут первую часть задержки, второй выход модуля задержки выводит задержанные сигналы CKV после того, как входные сигналы пройдут вторую часть задержки, и сигналы ОЕ и задержанные сигналы CKV выводятся на линии развертки дисплея с активной матрицей.

[0006] При этом длительность сигналов STV равна t1, длительность начальных сигналов CKV равна t2, период времени начальных сигналов CKV равен Т, и при этом t1, t2 и Т удовлетворяют уравнению: t2<t1<t2+T.

[0007] При этом t1, t2 и Т удовлетворяют уравнению: t2<t1<Т.

[0008] При этом t1, t2 и Т удовлетворяют уравнению: T≤t1≤t2+T.

[0009] При этом модуль задержки включает 2n первых инвертеров и 2m вторых инвертеров, входные сигналы проходят через 2n первых инвертеров, чтобы вывести сигналы ОЕ через первый выход, входные сигналы проходят через 2n первых инвертеров и 2m вторых инвертеров, чтобы вывести задержанные сигналы CKV через второй выход, и при этом n и m являются натуральными числами.

[0010] При этом длительность задержки каждого из первых инвертеров составляет Δtn, и длительность задержки каждого из первых инвертеров составляет Δtm, и Δtn, Δtm, t1 и t2 удовлетворяют уравнениям: t2<(2n*Δtn+2m*Δtm)<t1 и 0<2m*Δtm<t2.

[0011] В еще одном аспекте дисплей с активной матрицей включает: микросхему управления тактированием, генерирующую начальные сигналы CKV и сигналы STV; микросхему интегрирования сигналов, вход микросхемы интегрирования сигналов соединен с выходом микросхемы управления тактированием, чтобы интегрировать начальные сигналы CKV и STV и генерировать входные сигналы; микросхему возбуждения развертки, включающую модуль задержки, вход модуля задержки соединен с выходом микросхемы интегрирования сигналов, чтобы принимать входные сигналы, модуль задержки дважды задерживает входные сигналы, и при этом первый выход модуля задержки выводит сигналы ОЕ, после того как входные сигналы пройдут первую часть задержки, второй выход модуля задержки выводит задержанные сигналы CKV после того как входные сигналы пройдут вторую часть задержки, и сигналы ОЕ и задержанные сигналы CKV выводятся на линии развертки дисплея с активной матрицей.

[0012] При этом длительность сигналов STV равна t1, длительность начальных сигналов CKV равна t2, период времени начальных сигналов CKV равен Т, и при этом t1, t2 и Т удовлетворяют уравнению: t2<t1<t2+T.

[0013] При этом t1, t2, и Т удовлетворяют уравнению: t2<t1<Т.

[0014] При этом t1, t2, и Т удовлетворяют уравнению: T≤t1≤t2+T.

[0015] При этом модуль задержки включает 2n первых инвертеров и 2m вторых инвертеров, входные сигналы проходят через 2n первых инвертеров, чтобы вывести сигналы ОЕ через первый выход, входные сигналы проходят через 2n первых инвертеров и 2m вторых инвертеров, чтобы вывести задержанные сигналы CKV через второй выход, и при этом n и m являются натуральными числами.

[0016] При этом длительность задержки каждого из первых инвертеров равна Δtn, и длительность задержки каждого из первых инвертеров равна Δtm, и Δtn, Δtm, t1 и t2 удовлетворяют уравнениям: t2<(2n*Δtn+2m*Δtm)<t1 и 0<2m*Δtm<t2.

[0017] При этом дисплей с активной матрицей кроме того включает по меньшей мере одну микросхему возбуждения развертки, и модуль задержки расположен в микросхеме возбуждения развертки.

[0018] В еще одном аспекте способ возбуждения развертки дисплея с активной матрицей с микросхемой управления тактированием и микросхемой возбуждения развертки включает: перекрывание начальных сигналов CKV и сигналов STV, генерируемых микросхемой управления тактированием, чтобы они стали входными сигналами микросхемы возбуждения развертки; двойную задержку входных сигналов модулем задержки микросхемы возбуждения развертки. При этом первый выход модуля задержки выводит сигналы ОЕ после того, как входные сигналы пройдут первую часть задержки, и второй выход модуля задержки выводит задержанные сигналы CKV после того, как входные сигналы пройдут вторую часть задержки, после чего сигналы ОЕ и задержанные сигналы CKV выводятся на линии развертки дисплея с активной матрицей.

[0019] При этом длительность сигналов STV равна t1, длительность начальных сигналов CKV равна t2, период времени начальных сигналов CKV равен Т, и при этом t1, t2, и Т удовлетворяют уравнению: t2<t1<t2+T.

[0020] При этом t1, t2 и Т удовлетворяют уравнению: t2<t1<Т.

[0021] При этом t1, t2 и Т удовлетворяют уравнению: T≤t1≤t2+T.

[0022] При этом модуль задержки включает 2n первых инвертеров и 2m вторых инвертеров, входные сигналы проходят через 2n первых инвертеров, чтобы вывести сигналы ОЕ через первый выход, входные сигналы проходят через 2n первых инвертеров и 2m вторых инвертеров, чтобы вывести задержанные сигналы CKV через второй выход, и при этом n и m являются натуральными числами.

[0023] При этом длительность задержки каждого из первых инвертеров равна Δtn, и длительность задержки каждого из вторых инвертеров равна Δtm, и Δtn, Δtm, t1 и t2 удовлетворяют уравнениям: t2<(2n*Δtn+2m*Δtm)<t1 и 0<2m*Δtm<t2.

[0024] В свете вышеизложенного, микросхема возбуждения развертки включает модуль задержки. На вход модуля задержки поступают входные сигналы, интегрированные начальными сигналами импульсов напряжения тактирования (CKV) и сигналами импульсов запускающего напряжения (STV). Входные сигналы задерживаются на первую часть задержки и вторую часть задержки, так что первый выход модуля задержки выводит сигналы разрешения выхода (ОЕ), и второй выход модуля задержки выводит задержанные сигналы CKV. Сигналы ОЕ и задержанные сигналы CKV выводятся на линии развертки дисплея с активной матрицей. Для передачи входных сигналов необходима только одна соответствующая линия передачи. Число линий передачи уменьшается, что благоприятно для узкой конструкции окантовки дисплея. С другой стороны, интервал между линиями передачи увеличивается, так что сложность соединений уменьшается. Кроме того, число выходных контактов микросхем управления тактированием и число входных контактов микросхем возбуждения развертки уменьшается, этим снижая расходы.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

[0025] Фиг. 1 - форма волны известных сигналов возбуждения развертки.

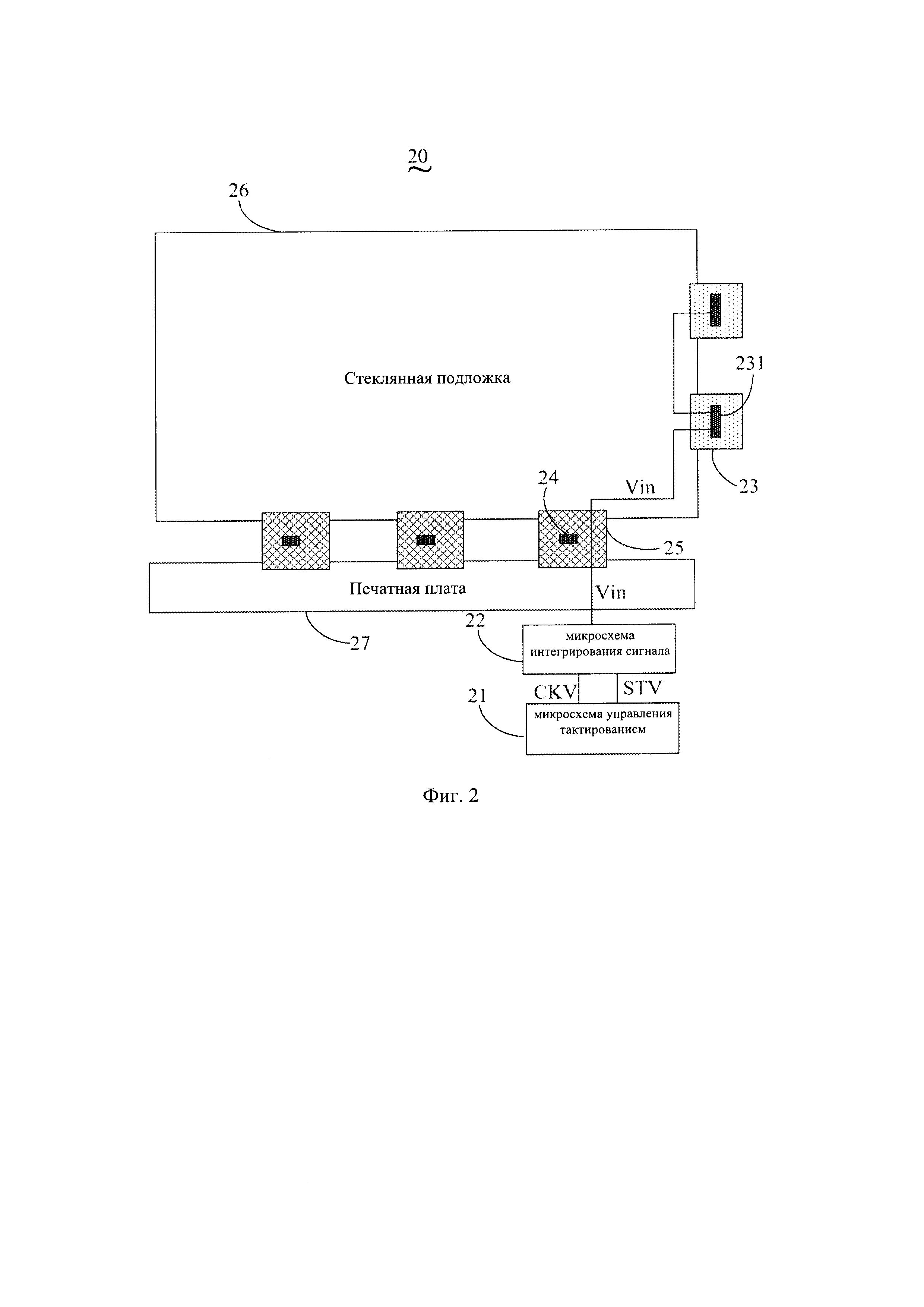

[0026] Фиг. 2 - схематический вид дисплея с активной матрицей в соответствии с одним вариантом осуществления.

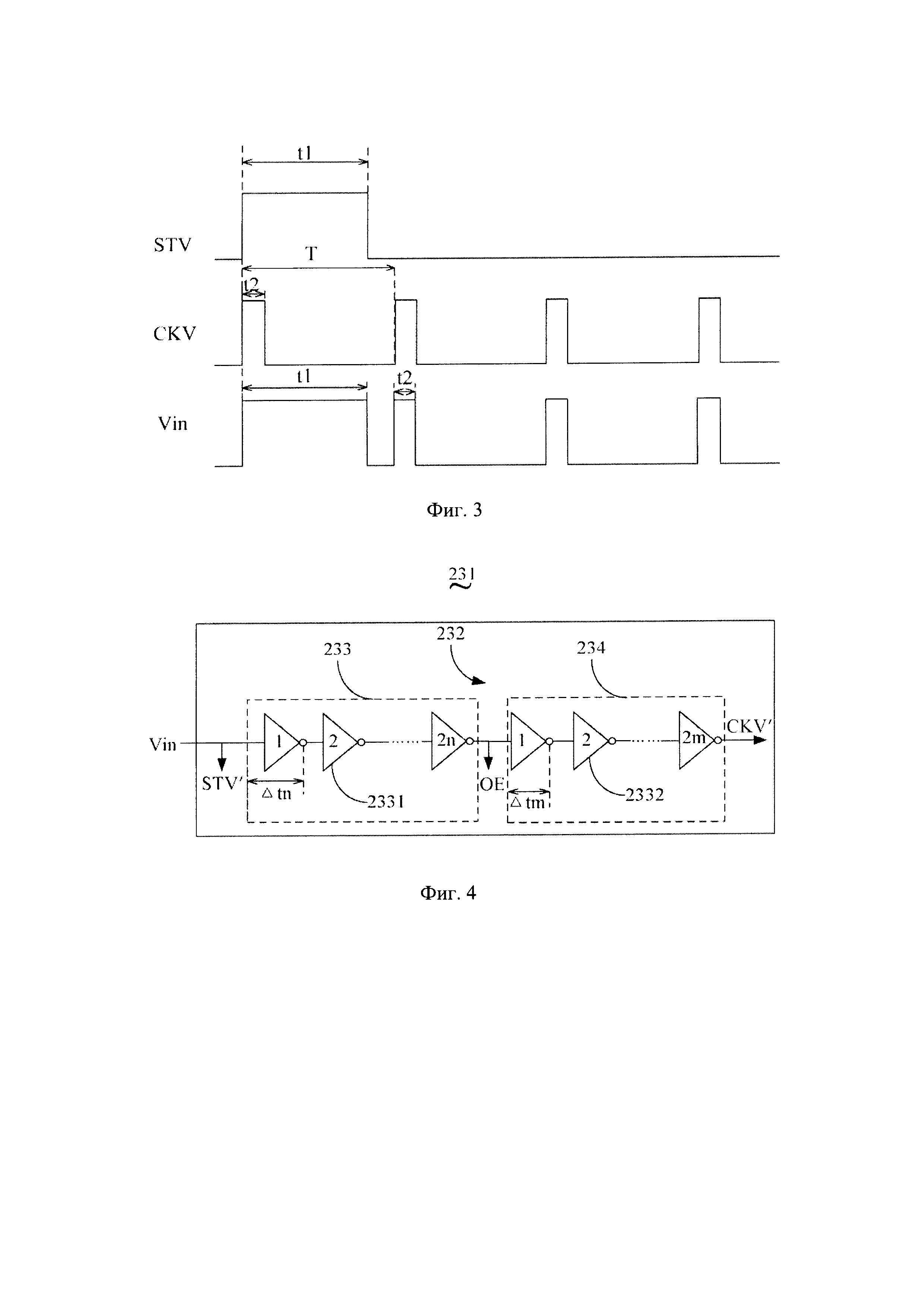

[0027] Фиг. 3 - начальные сигналы CKV и сигналы STV, которые удовлетворяют одному условию в соответствии с одним вариантом осуществления.

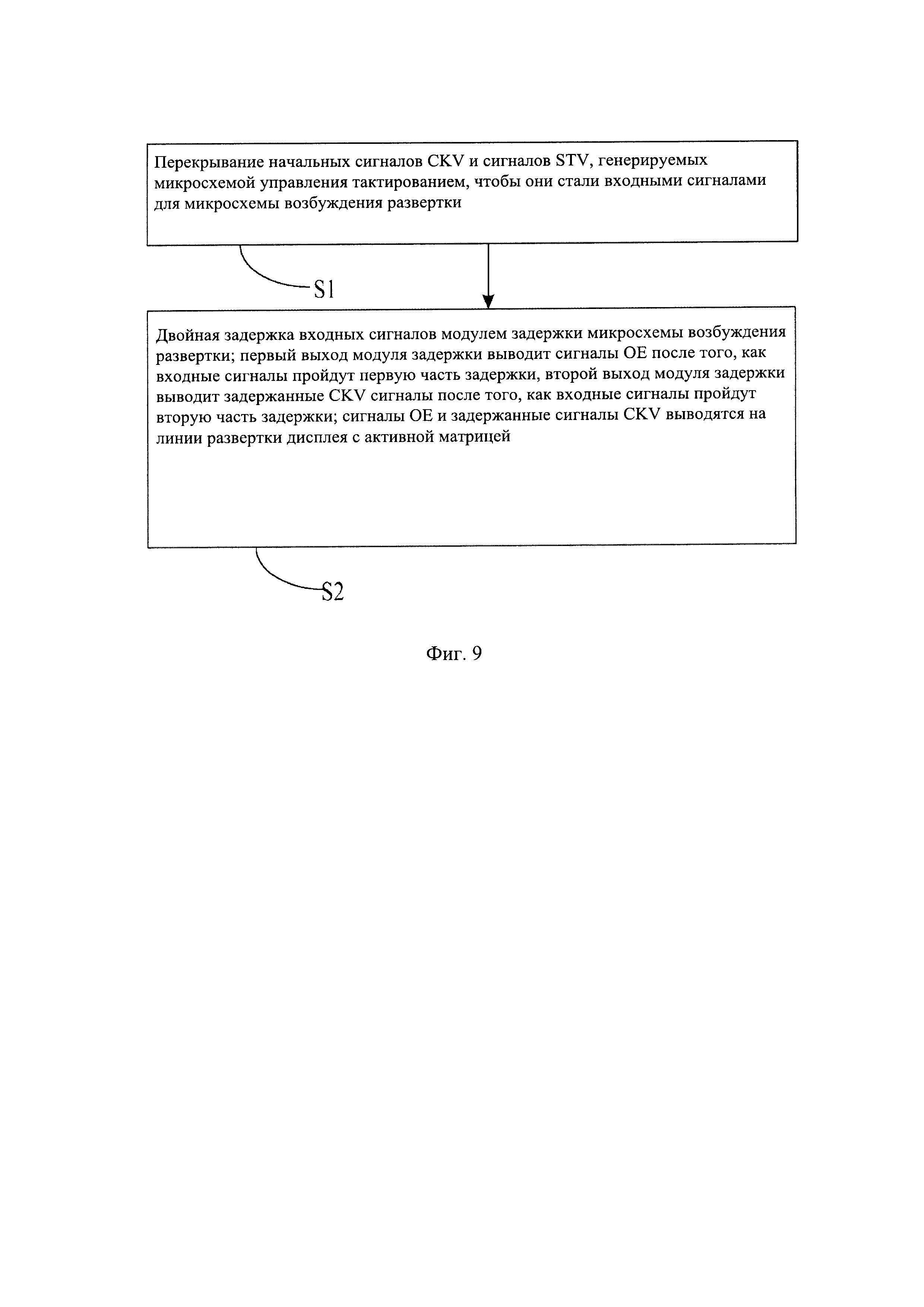

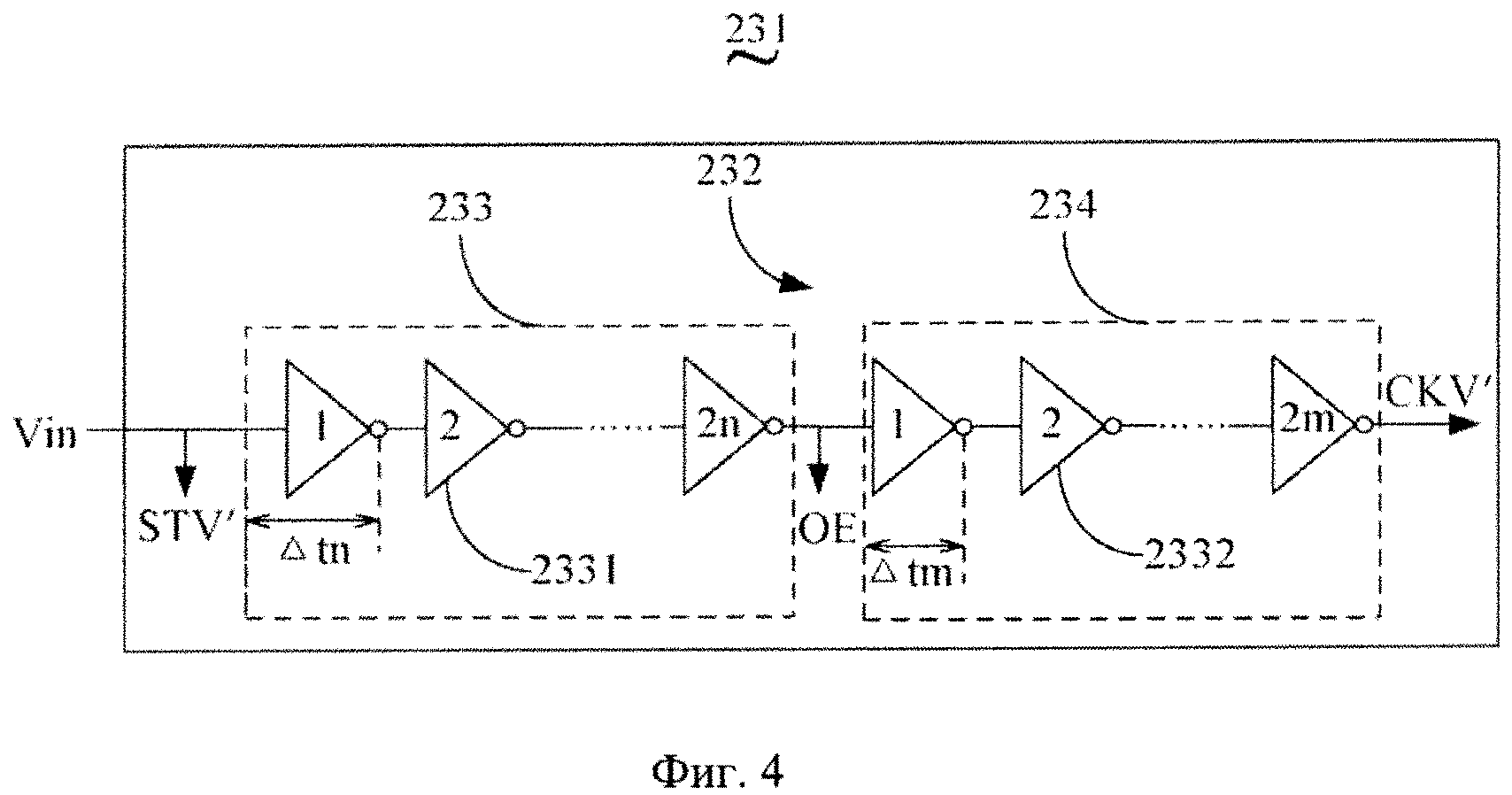

[0028] Фиг. 4 - схематический вид микросхемы возбуждения развертки с Фиг. 2.

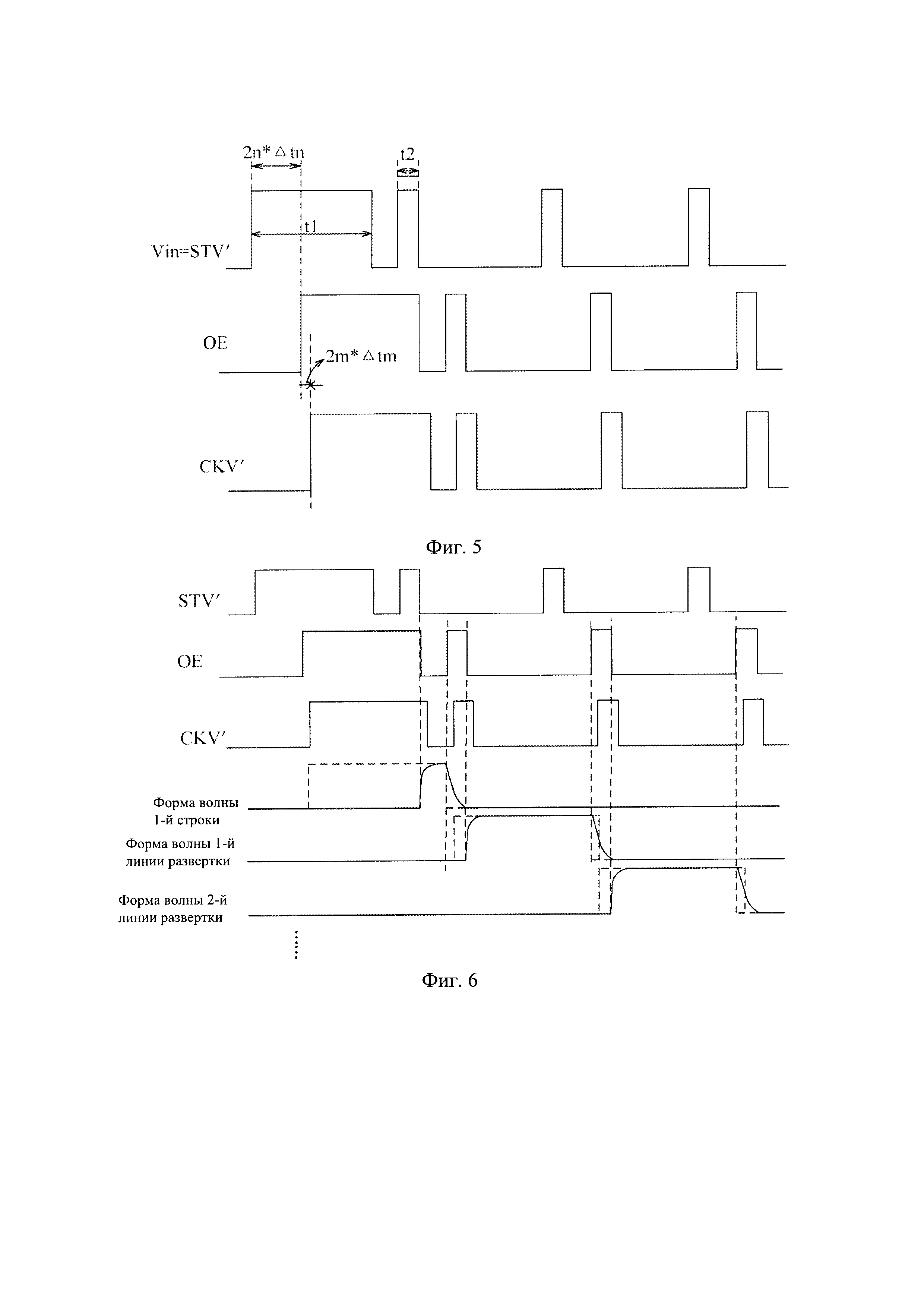

[0029] Фиг. 5 - моделированная форма волны, показывающая задержанные входные сигналы.

[0030] Фиг. 6 - форма волны сигналов возбуждения развертки дисплея с активной матрицей в соответствии с одним вариантом осуществления.

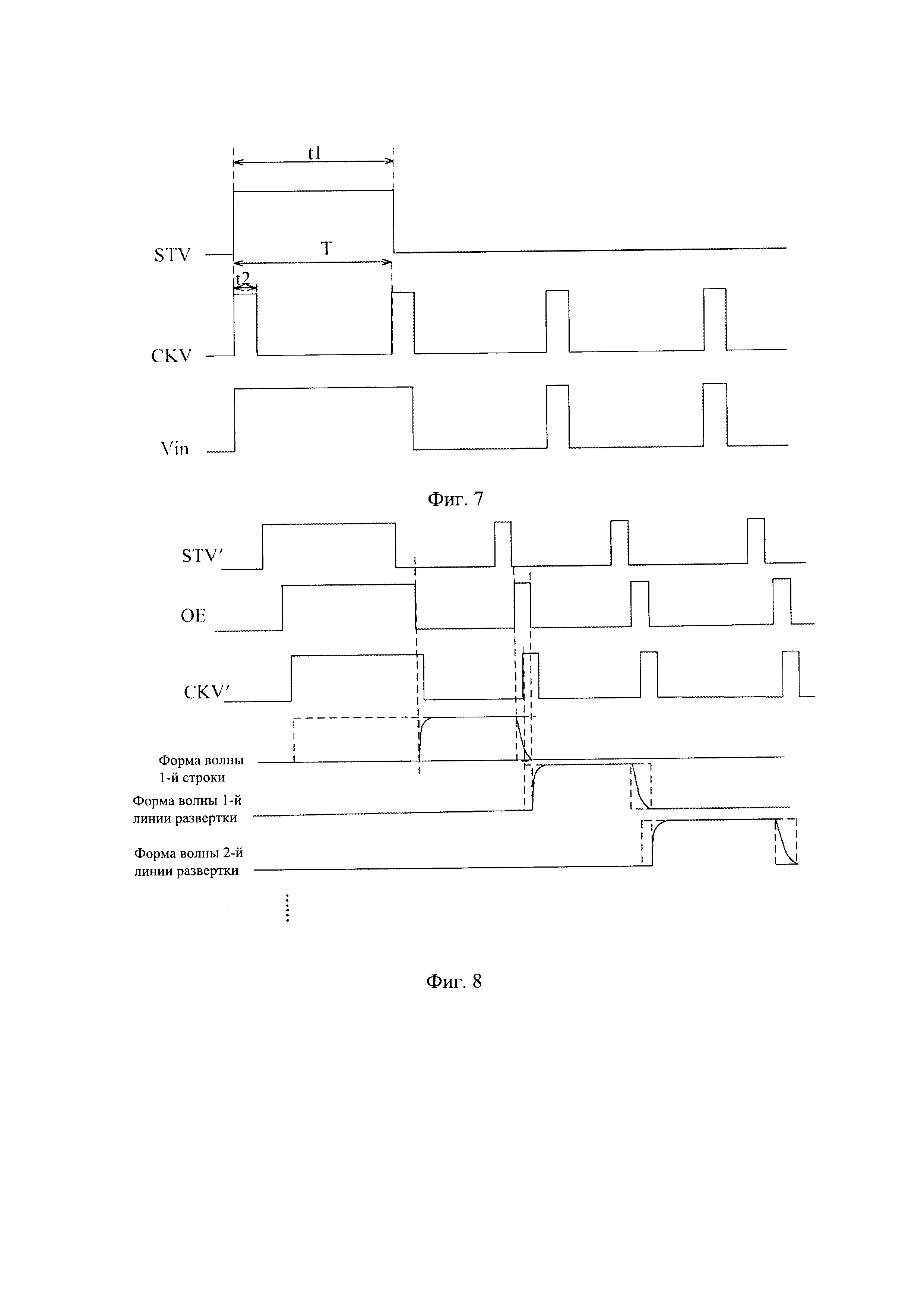

[0031] Фиг. 7 - начальные сигналы CKV и сигналы STV, которые удовлетворяют одному условию в соответствии с еще одним вариантом осуществления.

[0032] Фиг. 8 - форма волны сигналов возбуждения развертки дисплея с активной матрицей в соответствии с еще одним вариантом осуществления.

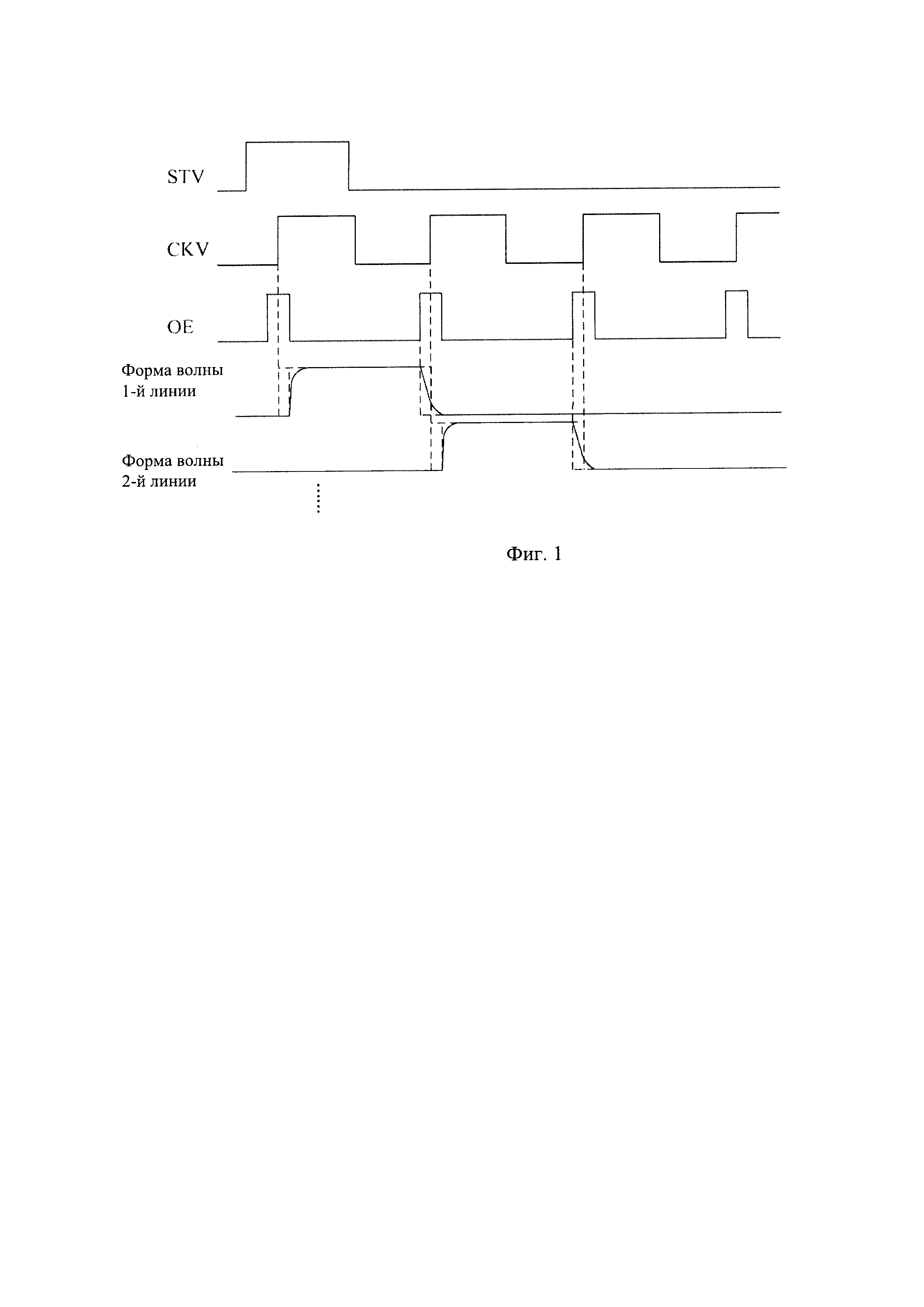

[0033] Фиг. 9 - схема процесса, иллюстрирующая способ возбуждения развертки дисплея с активной матрицей в соответствии с одним вариантом осуществления.

ПОДРОБНОЕ ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

[0034] Теперь варианты осуществления изобретения будут описаны более подробно со ссылками на прилагаемые чертежи, на которых показаны варианты осуществления изобретения.

[0035] На Фиг. 2 показан схематический вид дисплея с активной матрицей в соответствии с одним вариантом осуществления. Дисплей с активной матрицей 20 включает микросхему управления тактированием 21, микросхему интегрирования сигнала 22, и микросхему возбуждения развертки 23.

[0036] Микросхема управления тактированием 21 генерирует начальные сигналы CKV и сигналы STV.

[0037] Вход микросхемы интегрирования сигнала 22 соединен с выходом микросхемы управления тактированием 21, чтобы обеспечить перекрывание начальных сигналов CKV и сигналов STV для генерации входных сигналов Vin. На Фиг. 3 показаны начальные сигналы CKV и сигналы STV, которые удовлетворяют одному условию в соответствии с одним вариантом осуществления. Как показано, длительность начальных сигналов STV равна t1, длительность начальных сигналов CKV равна t2, и период времени начальных сигналов CKV равен Т. В одном варианте осуществления t1, t2 и Т удовлетворяют условию (1) "t2<t1<t2+T".

[0038] Микросхема возбуждения развертки 23 включает по меньшей мере одну микросхему возбуждения развертки 231 с модулем задержки 232 (также см. Фиг. 4).

[0039] На Фиг. 4 показан схематический вид модуля задержки 232 в соответствии с одним вариантом осуществления. Как показано, модуль задержки 232 расположен в микросхеме возбуждения развертки 231. Входные сигналы Vin подаются на вход модуля задержки 232 и затем дважды задерживаются на первую часть задержки 233 и вторую часть задержки 234. После того, как входные сигналы пройдут первую часть задержки 233, первый выход модуля задержки 232 выводит сигналы ОЕ. После того, как входные сигналы пройдут вторую часть задержки 234, второй выход модуля задержки 232 выводит задержанные сигналы CKV’. Сигналы ОЕ и задержанные сигналы CKV’ выводятся на линии развертки дисплея с активной матрицей 20.

[0040] Конкретно, модуль задержки 232 включает 2n первых инвертеров 2331 и 2m вторых инвертеров 2332. Входные сигналы Vin подаются на вход модуля задержки 232, чтобы действовать как сигналы STV микросхемы возбуждения развертки 231, чтобы запустить по меньшей мере один регистр первой строки. После подачи в модуль задержки 232 входные сигналы Vin проходят через 2n первых инвертеров 2331, чтобы вывести сигналы ОЕ через первый выход. Входные сигналы Vin затем проходят через 2m вторых инвертеров 2332, чтобы вывести задержанные сигналы CKV’ через второй выход. В данном варианте осуществления n и m являются натуральными числами.

[0041] На Фиг. 5 представлена моделированная форма волны, показывающая задержанные входные сигналы. В данном варианте осуществления длительность задержки каждого из первых инвертеров 2331 равна Δtn, длительность задержки каждого из первых инвертеров 2332 равна Δtm, и Δtn, Δtm, t1 и t2 удовлетворяют условию (2) и (3).

[0042] Касательно условия (2), уравнение "t2<(2n*Δtn+2m*Δtm)<t1" удовлетворяется так, что сигналы STV’ прилагаются только к регистрам в первой строке. Конкретно, уравнение "(2n*Δtn+2m*Δtm)<t1" приводит к тому, что могут быть запущены только регистры сдвига в первой строке, и уравнение "t2<(2n*Δtn+2m*Δtm)" приводит к тому, что регистры сдвига в первой строке могут быть запущены только один раз.

[0043] Касательно условия (3), уравнение "0<2m*Δtm<t2" удовлетворяется так, что передние фронты задержанных сигналов CKV’ находятся на высоком уровне сигналов ОЕ.

[0044] На Фиг. 6 показана форма волны сигналов возбуждения развертки дисплея с активной матрицей в соответствии с одним вариантом осуществления. Как показано, сигналы STV’, сигналы ОЕ, и задержанные сигналы CKV’ запускаются во время периода высокого уровня. Когда сигналы ОЕ находятся на высоком уровне, уровень напряжения всех каналов принудительно сжимается. Когда сигналы STV’ и задержанные сигналы CKV’ находятся на высоком уровне, сигналы ОЕ находятся на высоком уровне, и выходное напряжение принудительно сжимается. Таким образом, форма волны первой строки находится на низком уровне. Когда сигналы ОЕ находятся на низком уровне, и задержанные сигналы CKV’ находятся на высоком уровне, сигналы высокого уровня выводятся для запуска регистров в первой строке. Когда сигналы ОЕ переходят с низкого уровня на высокий уровень, выходное напряжение сигналов STV’ сжимается. Когда выходной уровень сигналов STV’ переходит с высокого на низкий, задержанные сигналы CKV’ переходят с низкого уровня на высокий уровень. Во время этого процесса сигналы ОЕ переходят с высокого уровня на низкий уровень, и запускается следующая строка, чтобы вывести высокий уровень. В данном варианте осуществления, когда передний фронт задержанных сигналов CKV’ находится в периоде высокого уровня сигналов ОЕ, уровень напряжения текущей строки сжимается перед запуском регистров в следующей строке. Таким образом, время переключения состояния включено/выключено каждой строки чередуется.

[0045] Из Фиг. 6 можно понять, что форма волны первой строки отличается от формы волны других строк, так что форма волны первой строки не должна приниматься во внимание. В данном варианте осуществления выход регистров в первой строке, который соответствует сигналам STV’, временно откладывается. Таким образом, необходимые данные могут быть выведены по истечении периода времени Т.

[0046] В других вариантах осуществления, когда вышеизложенные условия (2) и (3) сохраняются, и t1, t2 и Т удовлетворяют уравнению "Т≤t1≤t2+T", интегрирование начальных сигналов CKV и сигналов STV, чтобы получить входные сигналы Vin, происходит как показано на Фиг. 7. Подобно этому, выход первой и второй строк также временно откладывается, когда входные сигналы Vin действуют как сигналы STV’ микросхемы возбуждения развертки 231. Как показано на Фиг. 8, необходимые данные могут быть выведены по истечении периода времени 2Т.

[0047] В свете вышеизложенного, начальные сигналы CKV и сигналы STV, которые генерируются микросхемой управления тактированием 21, интегрируются, чтобы стать одним из входных сигналов Vin, и затем передаются на микросхему возбуждения развертки 231. Для передачи входных сигналов Vin необходима только одна линия передачи. Со ссылкой на Фиг. 2, дисплей с активной матрицей 20 кроме того включает по меньшей мере одну микросхему возбуждения данных 24, микросхему с ПО 25, стеклянную подложку 26 и печатную плату 27. Входные сигналы Vin передаются с печатной платы 27 на микросхему с ПО 25 микросхемы возбуждения данных 24 и затем передаются из линий передачи на микросхеме с ПО 25 на стеклянную подложку 26. После этого входные сигналы Vin передаются по одной линии передачи на стеклянной подложке 26 на микросхему возбуждения развертки 231.

[0048] На Фиг. 9 приведена схема процесса, иллюстрирующая способ возбуждения развертки дисплея с активной матрицей в соответствии с одним вариантом осуществления. Способ включает следующие этапы. На этапе S1 начальные сигналы CKV и сигналы STV, генерируемые микросхемой управления тактированием, перекрываются, чтобы стать входными сигналами микросхемы возбуждения развертки. Период времени начальных сигналов CKV равен Т, длительность начальных сигналов STV равна t1, длительность начальных сигналов CKV равна t2, и T1, t2 и Т удовлетворяют условию (1) "t2<t1<t2+T." На Фиг. 3 показан процесс перекрывания, когда t2<t1<T, и на Фиг. 7 показан процесс перекрывания, когда T≤t1≤t2+T.

[0049] На этапе S2 микросхема возбуждения развертки включает модуль задержки. На вход модуля задержки поступают входные сигналы, которые должны подвергнуться двойной задержке. Первый выход модуля задержки выводит сигналы ОЕ после того, как входные сигналы пройдут первую часть задержки. Второй выход модуля задержки выводит задержанные сигналы CKV’ после того, как входные сигналы пройдут вторую часть задержки. Сигналы ОЕ и задержанные сигналы CKV’ выводятся на линии развертки дисплея с активной матрицей. Модуль задержки включает 2n первых инвертеров и 2m вторых инвертеров. Входные сигналы действуют как сигналы STV микросхемы возбуждения развертки. Входные сигналы проходят через 2n первых инвертеров и 2m вторых инвертеров, задержанные сигналы CKV’ выводятся из второго выхода, и n и m являются натуральными числами.

[0050] В данном варианте осуществления длительность задержки каждого из первых инвертеров равна Δtn, и длительность задержки каждого из первых инвертеров равна Δtm. Уравнение "t2<(2n*Δtn+2m*Δtm)<t1" выполняется, так что сигналы STV’ подаются только на регистры в первой строке. Конкретно, уравнение "(2n*Δtn+2m*Δtm)<t1" приводит к тому, что могут быть запущены только регистры сдвига в первой строке, и уравнение "t2<(2n*Δtn+2m*Δtm)" приводит к тому, что регистры сдвига в первой строке могут быть запущены только один раз. Уравнение "0<2m*Δtm<t2" выполняется, так что передние фронты задержанных сигналов CKV’ находятся на высоком уровне сигналов ОЕ. На Фиг. 6 показана форма волны выхода первой строки, когда t2<t1<T. На Фиг. 8 показана форма волны выхода первой строки когда T≤t1≤t2+T.

[0051] В свете вышеизложенного, начальные сигналы CKV и сигналы STV, которые генерируются микросхемой управления тактированием, интегрируются, чтобы стать одним из входных сигналов, и затем передаются на микросхему возбуждения развертки. Входные сигналы подаются на вход модуля задержки микросхемы возбуждения развертки. Модуль задержки кроме того выполняет две части задержки на входных сигналах. После того, как входные сигналы пройдут первую часть задержки, первый выход модуля задержки выводит сигналы ОЕ. После того, как входные сигналы пройдут вторую часть задержки, второй выход модуля задержки выводит задержанные сигналы CKV’. Сигналы ОЕ и задержанные сигналы CKV’ выводятся на линии развертки дисплея с активной матрицей. При вышеописанной конфигурации число линий передачи уменьшается, что подходит для конструкции узкой окантовки. С другой стороны, интервал между линиями передачи увеличивается, так что сложность соединений уменьшается. Кроме того, число выходных контактов микросхем управления тактированием и число входных контактов микросхем возбуждения развертки уменьшается, так что расходы снижаются.

[0052] Можно полагать, что данные варианты осуществления и их преимущества будут поняты из вышеприведенного описания, и очевидно, что в них могут быть внесены разные изменения, но без нарушения сущности и объема изобретения или ущерба для его материальных преимуществ, при этом описанные выше примеры являются только предпочтительными или иллюстративными вариантами осуществления изобретения.