Результат интеллектуальной деятельности: МНОГОЗНАЧНЫЙ ТРИГГЕР

Вид РИД

Изобретение

Изобретение относится к области вычислительной техники, автоматики и может использоваться в различных цифровых структурах и системах автоматического управления, передачи информации и т.п.

В различных вычислительных и управляющих системах могут использоваться устройства, реализованные на основе триггеров, которые имеют два состояния в зависимости от потенциальных сигналов на входах [1-34]. Входные и выходные сигналы в классических триггерах представляют собой высокий или низкий потенциалы, соответствующие логической "1" или логическому "0" булевой алгебры.

В работе [35], а также монографии соавтора настоящей заявки [36, 37] показано, что булева алгебра является частным случаем более общей линейной алгебры, практическая реализация которой в структуре вычислительных и логических устройств автоматики нового поколения требует создания специальной элементной базы, реализуемой на основе логики с многозначным внутренним представлением сигналов, в которой эквивалентом стандартного логического сигнала является квант тока I0. Заявляемое устройство относится к этому типу вычислительных устройств.

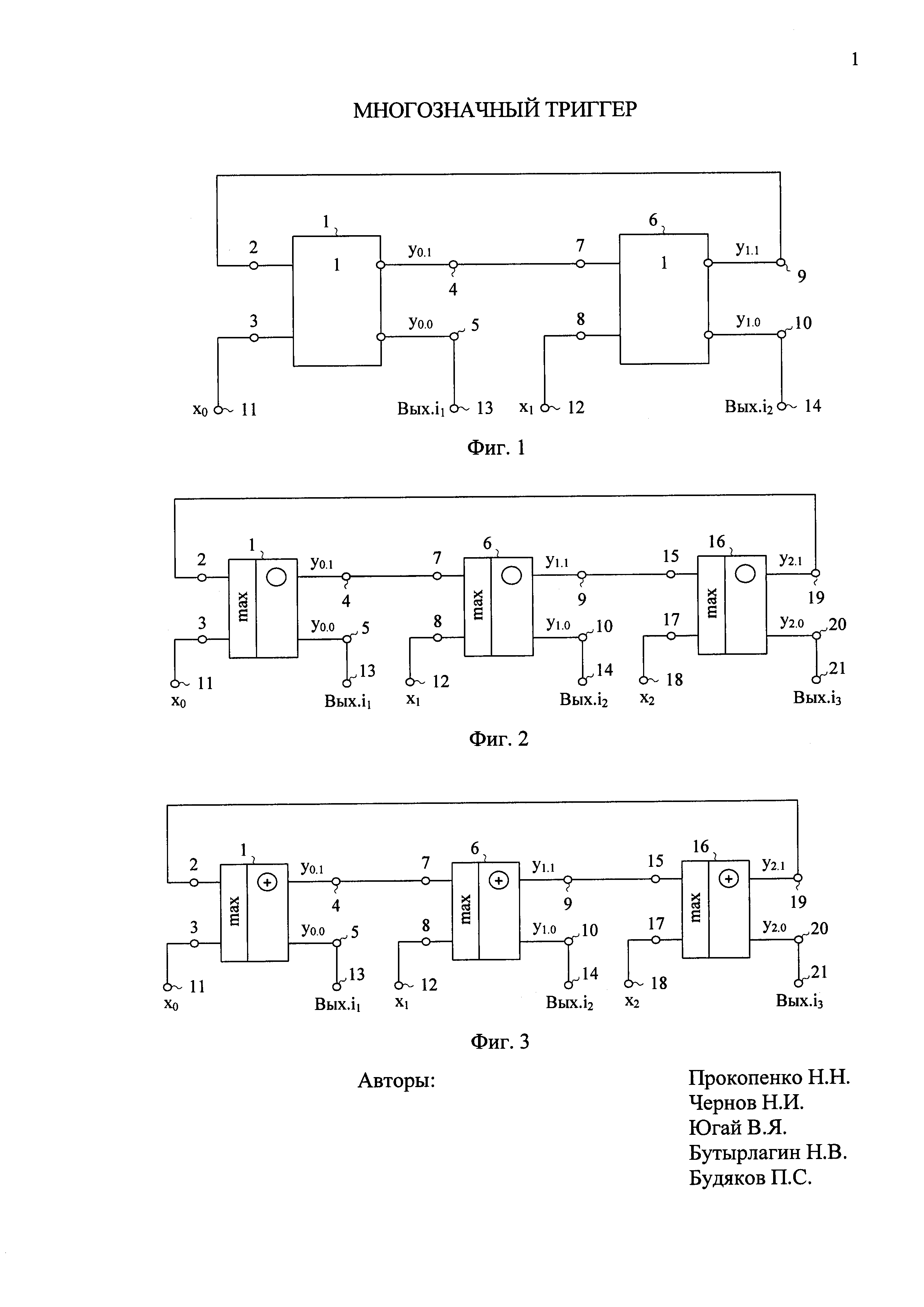

Ближайшим прототипом заявляемого устройства является RS-триггер, представленный в патенте RU 2514789. Он содержит (фиг. 1) первый (1) логический элемент с первым (2) и вторым (3) токовыми входами, а также первым (4) и вторым (5) токовыми выходами, второй логический элемент (6) с первым (7) и вторым (8) токовыми входами, а также первым (9) и вторым (10) токовыми выходами, причем первый (7) токовый вход второго (6) логического элемента соединен с первым (4) токовым выходом первого (1) логического элемента, второй (3) токовый вход первого (1) логического элемента соединен с первым (11) входом предустановки логического элемента памяти, второй (8) вход второго (6) логического элемента связан со вторым (12) входом предустановки состояния устройства, второй (5) токовый выход первого (1) логического элемента связан с первым (13) токовым выходом состояния устройства, второй (10) токовый выход второго (6) логического элемента связан со вторым (14) токовым выходом состояния устройства.

Существенный недостаток известного элемента памяти (триггера) состоит в том, что он не может выполнять функции многозначного логического элемента памяти (многозначного триггера).

Основная задача предлагаемого изобретения состоит в создании устройства, которое может иметь 2, 3, 4 и т.д. состояний, т.е. выполнять функции многозначного элемента памяти. В конечном итоге это позволяет повысить быстродействие специализированных вычислителей и создать элементную базу вычислительных устройств, работающих на принципах многозначной линейной алгебры [36, 37].

Поставленная задача решается тем, что в триггере (фиг. 1), содержащем первый (1) логический элемент с первым (2) и вторым (3) токовыми входами, а также первым (4) и вторым (5) токовыми выходами, второй логический элемент (6) с первым (7) и вторым (8) токовыми входами, а также первым (9) и вторым (10) токовыми выходами, причем первый (7) токовый вход второго (6) логического элемента соединен с первым (4) токовым выходом первого (1) логического элемента, второй (3) токовый вход первого (1) логического элемента соединен с первым (11) входом предустановки логического элемента памяти, второй (8) вход второго (6) логического элемента связан со вторым (12) входом предустановки состояния устройства, второй (5) токовый выход первого (1) логического элемента связан с первым (13) токовым выходом состояния устройства, второй (10) токовый выход второго (6) логического элемента связан со вторым (14) токовым выходом состояния устройства, предусмотрены новые элементы и связи - в качестве первого (1) и второго (6) логических элементов используются первый (1) и второй (6) логические элементы циклического сдвига, первый (9) выход второго (6) логического элемента циклического сдвига соединен с первым (15) токовым входом третьего (16) дополнительного логического элемента циклического сдвига, второй (17) вход третьего (16) дополнительного логического элемента циклического сдвига соединен с третьем (18) входом предустановки состояния устройства, первый (19) токовый выход третьего (16) дополнительного логического элемента циклического сдвига связан с первым (2) токовым входом первого (1) логического элемента циклического сдвига, а второй (20) токовый выход третьего (16) дополнительного логического элемента циклического сдвига соединен с третьим (21) выходом состояния устройства.

Схема RS-триггера - прототипа показана на фиг. 1. На фиг. 2 представлена схема заявляемого устройства в соответствии с п. 1 формулы изобретения.

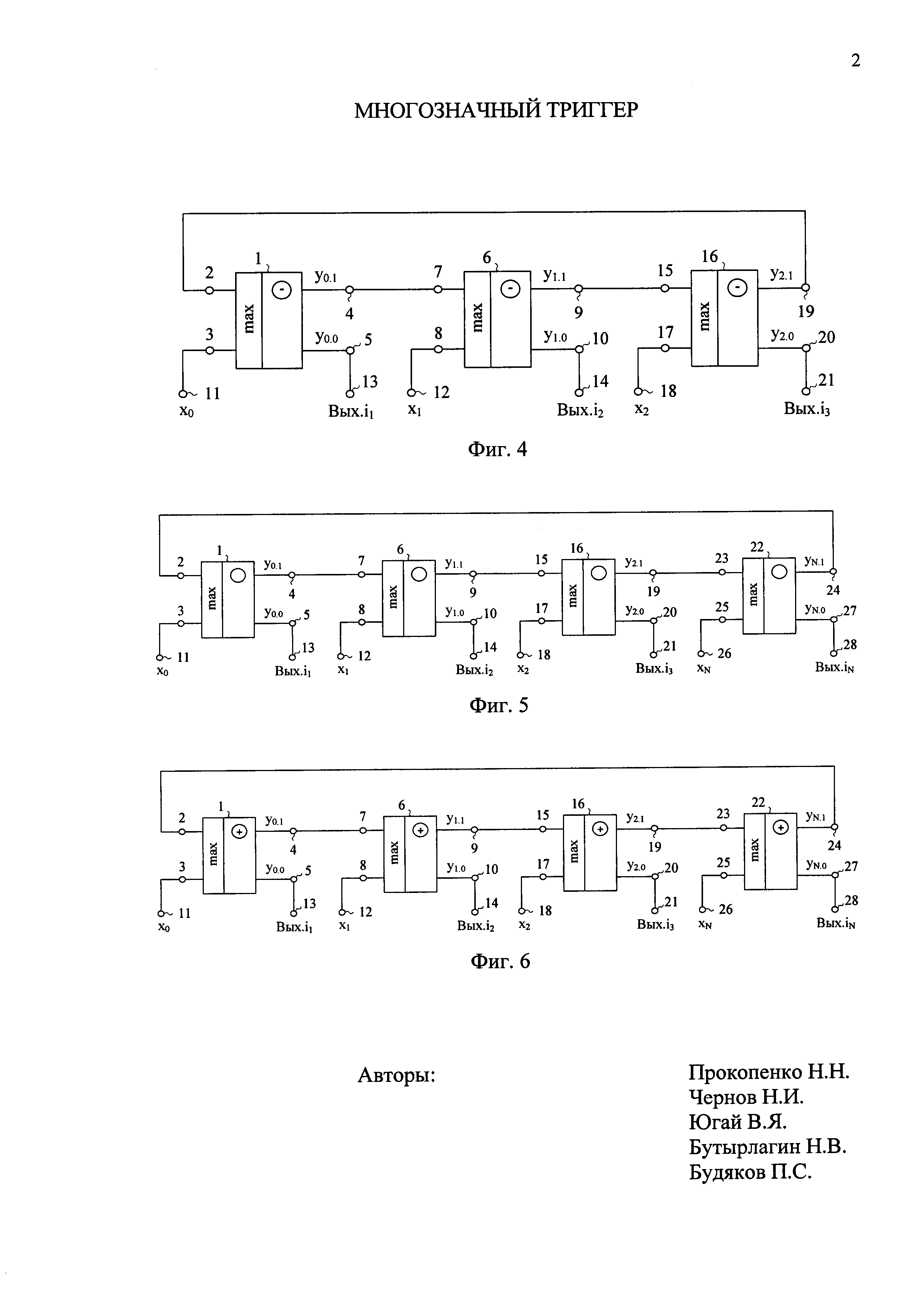

На фиг. 3 представлена схема заявляемого устройства в соответствии с п. 2 формулы изобретения для случая, когда в качестве первого (1) и второго (6) логических элементов циклического сдвига используются логические элементы прямого циклического сдвига.

На фиг. 4 представлена схема заявляемого устройства в соответствии с п. 3 формулы изобретения для случая, когда в качестве первого (1) и второго (6) логических элементов циклического сдвига используются логические элементы обратного циклического сдвига.

На фиг. 5 представлена схема заявляемого устройства в соответствии с п. 4 формулы изобретения.

На фиг. 6 представлен частный случай выполнения N-значного триггера фиг.5, реализующего операцию прямого циклического сдвига.

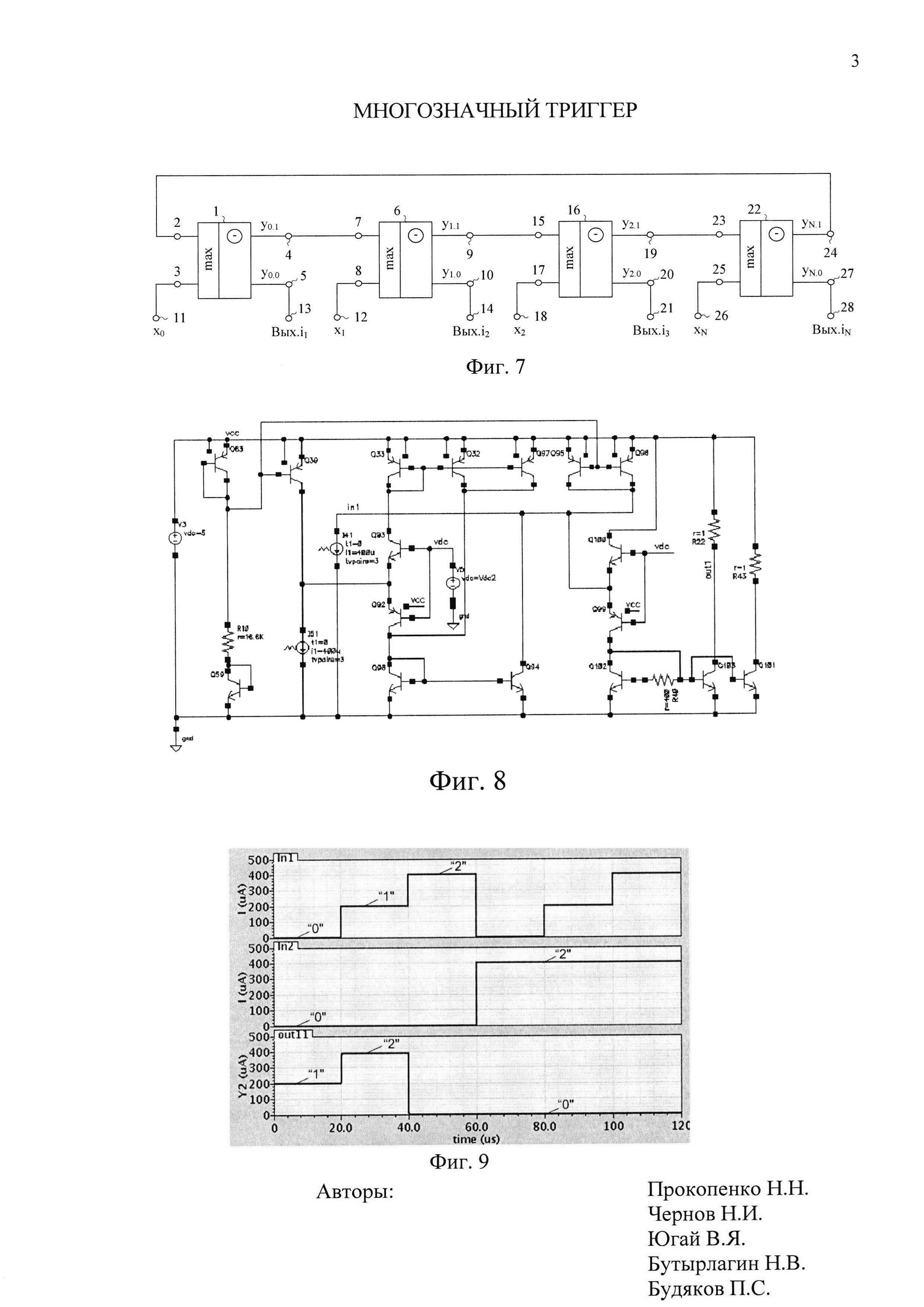

На фиг. 7 представлен частный случай выполнения N-значного триггера фиг. 5 реализующего операцию обратного циклического сдвига.

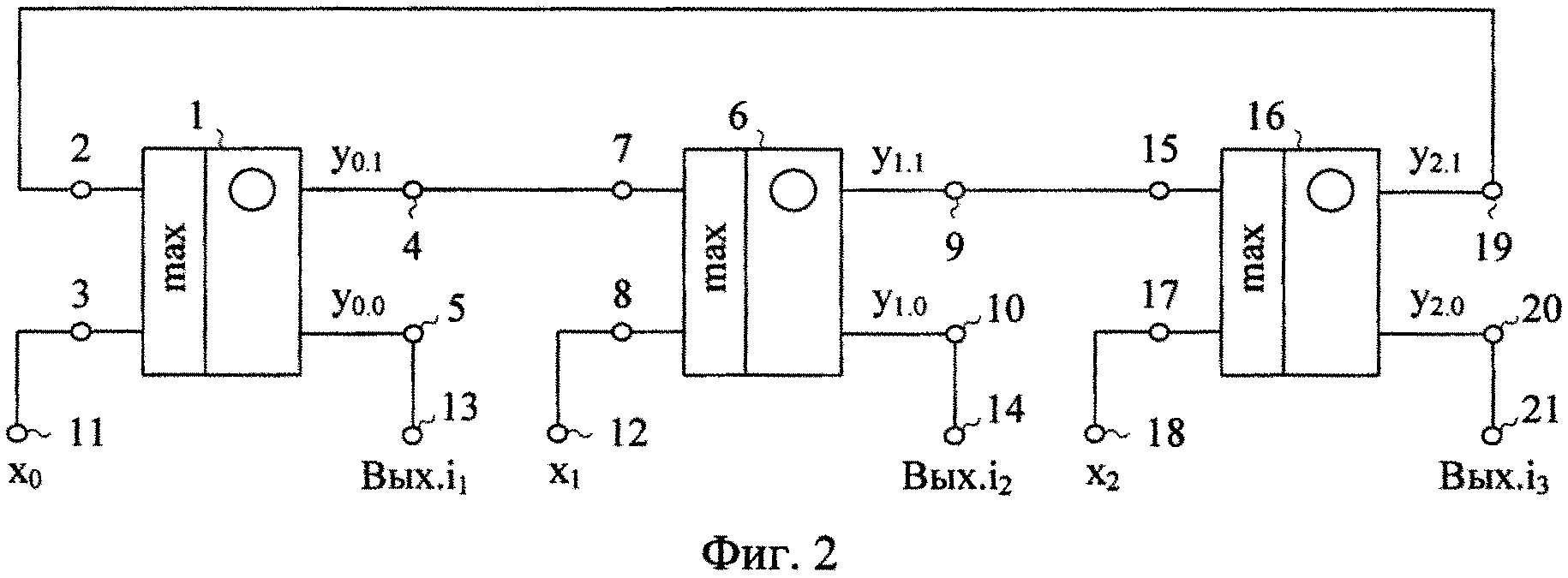

На фиг. 8 приведена схема логического элемента прямого циклического сдвига в среде Cadence на моделях транзисторов HJV Zarlink.

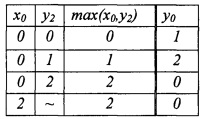

На фиг. 9 показаны входные и выходные токовые логические переменные схемы прямого циклического сдвига фиг. 8.

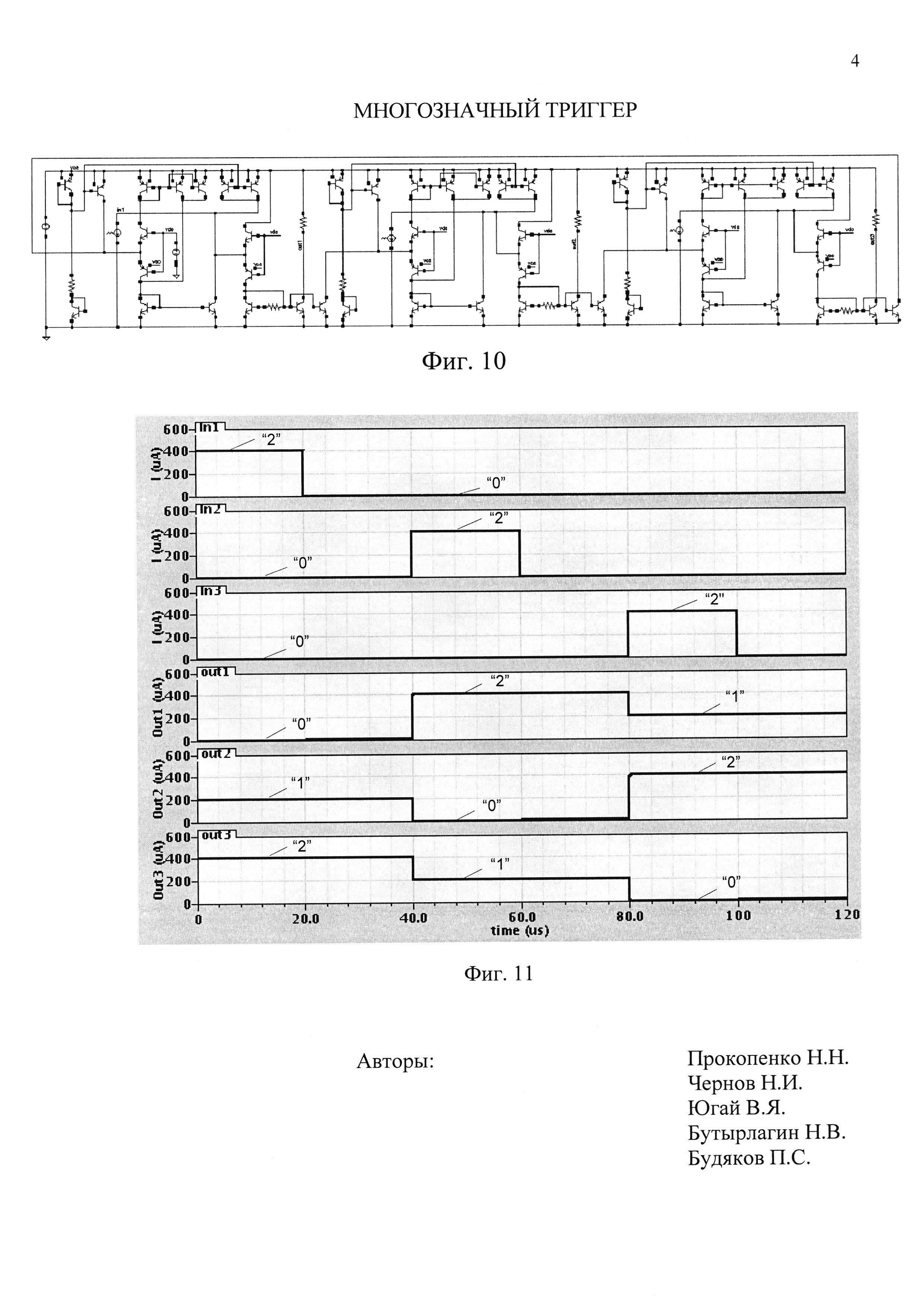

На фиг. 10 представлена схема заявляемого триггера (троичного элемента памяти) фиг. 3 в среде Cadence на моделях транзисторов HJV Zarlink.

На фиг. 11 приведены входные и выходные токовые логические переменные схемы троичного триггера (фиг. 10) при подаче токовых сигналов предустановки на входы In1, In2, In3.

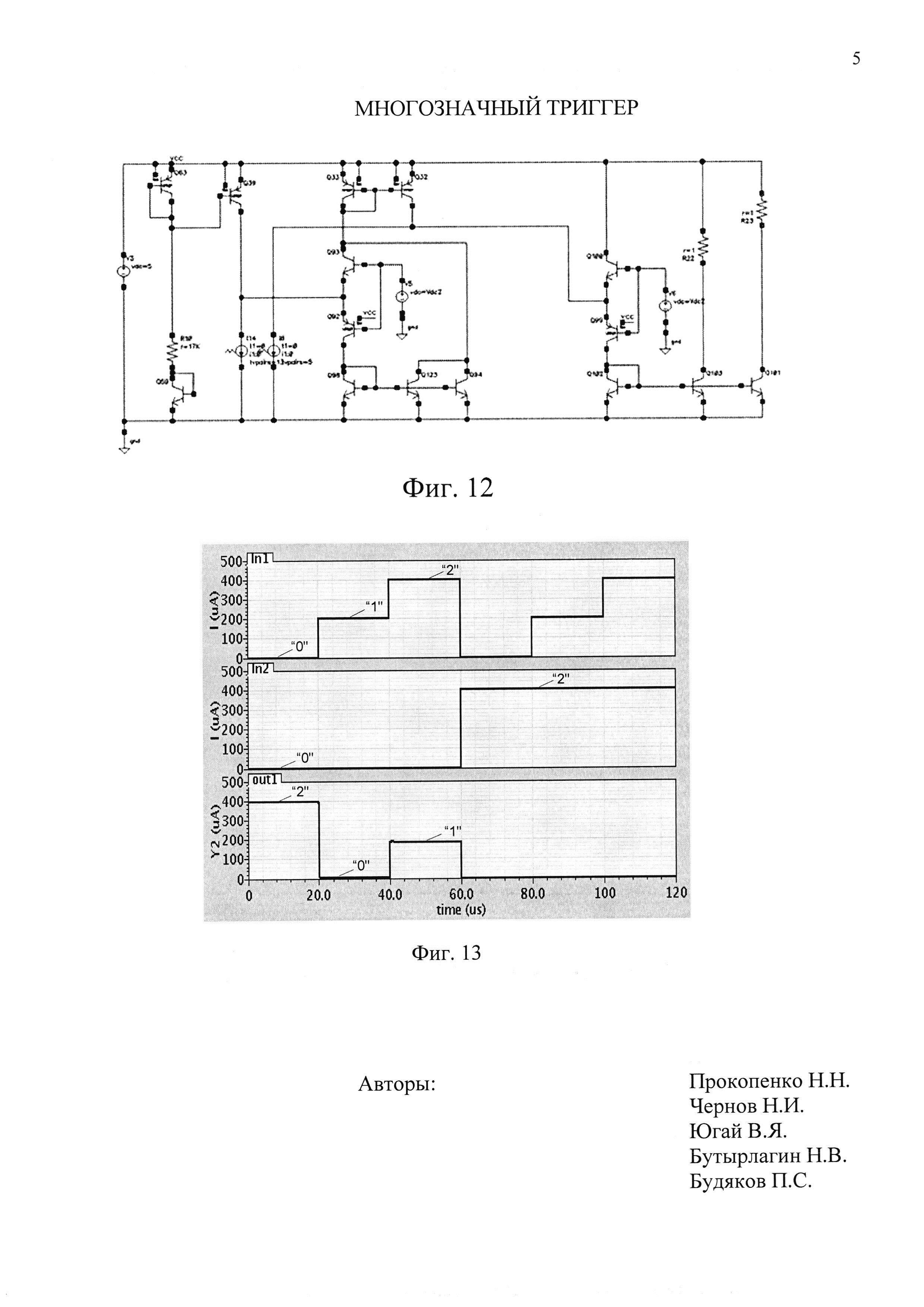

На фиг. 12 приведена схема логического элемента обратного циклического сдвига в среде Cadence на моделях транзисторов HJV Zarlink.

На фиг. 13 показаны входные и выходные токовые логические переменные схемы обратного циклического сдвига фиг. 12.

Триггер фиг. 2 (транзисторный логический элемент памяти) содержит первый (1) логический элемент с первым (2) и вторым (3) токовыми входами, а также первым (4) и вторым (5) токовыми выходами, второй логический элемент (6) с первым (7) и вторым (8) токовыми входами, а также первым (9) и вторым (10) токовыми выходами, причем первый (7) токовый вход второго (6) логического элемента соединен с первым (4) токовым выходом первого (1) логического элемента, второй (3) токовый вход первого (1) логического элемента соединен с первым (11) входом предустановки логического элемента памяти, второй (8) вход второго (6) логического элемента связан со вторым (12) входом предустановки состояния устройства, второй (5) токовый выход первого (1) логического элемента связан с первым (13) токовым выходом состояния устройства, второй (10) токовый выход второго (6) логического элемента связан со вторым (14) токовым выходом состояния устройства. В качестве первого (1) и второго (6) логических элементов используются первый (1) и второй (6) логические элементы циклического сдвига, первый (9) выход второго (6) логического элемента циклического сдвига соединен с первым (15) токовым входом третьего (16) дополнительного логического элемента циклического сдвига, второй (17) вход третьего (16) дополнительного логического элемента циклического сдвига соединен с третьем (18) входом предустановки состояния устройства, первый (19) токовый выход третьего (16) дополнительного логического элемента циклического сдвига связан с первым (2) токовым входом первого (1) логического элемента циклического сдвига, а второй (20) токовый выход третьего (16) дополнительного логического элемента циклического сдвига соединен с третьим (21) выходом состояния устройства.

На фиг. 3 в соответствии с п. 2 формулы изобретения в качестве первого (1) и второго (6) логических элементов циклического сдвига используются логические элементы прямого циклического сдвига.

На фиг. 4 в соответствии с п. 3 формулы изобретения в качестве первого (1) и второго (6) логических элементов циклического сдвига используются логические элементы обратного циклического сдвига.

На фиг. 5 в соответствии с п. 4 формулы изобретения первый (19) токовый выход второго (16) дополнительного логического элемента циклического сдвига связан с первым (2) токовым входом первого (1) логического элемента циклического сдвига через N-й (22) дополнительный элемент циклического сдвига, первый (23) токовый вход которого связан с первым (19) токовым выходом третьего (16) дополнительного логического элемента циклического сдвига, первый (24) выход соединен с первым (2) токовым входом первого (1) логического элемента циклического сдвига, второй (25) вход соединен с N-м входом (26) предустановки состояния устройства, а второй (27) токовый выход связан с N-м (28) токовым выходом устройства.

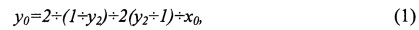

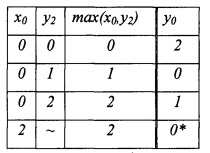

Рассмотрим работу многозначного триггера (троичного элемента памяти) (фиг. 3) на основе операции прямого циклического сдвига для случая, когда ее таблица истинности имеет вид:

Следует отметить, что данная таблица истинности является не полностью определенной - в ней отражены не все возможные значения аргументов x0, y2, а только значения, которые могут быть реализованы при работе троичного элемента памяти (фиг. 3). Соответствующая таблице истинности функция описывается уравнением

Как известно, различают два режима работы триггера:

- режим установки триггера в некоторое состояние;

- режим хранения этого состояния.

При подаче на второй токовый вход (3) первого логического элемента (1) управляющего сигнала в виде состояния логической "2" триггер (фиг. 3) переходит в установочный режим. На первый токовый вход (3) первого логического элемента (1) подается состояние логического "0". На первом (4) и втором (5) выходах первого логического элемента (1) получаем состояние логического "0". Далее состояние логического "0" подается на первый токовый вход (7) второго логического элемента (6). На второй токовой вход (8) второго логического элемента подается состояние логического "0". На первом (9) и втором (14) выходах второго логического элемента (6) получаем состояние логической "1". Далее состояние логической "1" подается на первый токовый вход (15) третьего логического элемента (16). На второй токовый вход (17) третьего логического элемента подается состояние логического "0". На первом (19) и втором (20) выходах третьего логического элемента (16) получаем состояние логической "2". При подаче состояния логической "2" на второй токовый вход (8) второго логического элемента (6) или на второй токовый вход (15) третьего логического элемента (16) триггер (фиг. 3) в установочном режиме работает аналогично. Управляющий сигнал подается только один раз на один из трех входов (3), (8), (17), после установочного режима схема триггера (фиг. 3) работает в режиме хранения.

В режиме хранения состояния логической "2" ток с первого токового выхода (19) третьего логического элемента (16) подается на первый токовый вход (2) первого логического элемента. На второй токовый вход (3) первого логического элемента (1) подается состояние логического "0". На первом (4) и втором (5) выходах первого логического элемента (1) получаем состояние логического "0". Далее состояние логического "0" подается на первый токовый вход (7) второго логического элемента (6). На второй токовой вход (8) второго логического элемента подается состояние логического "0". На первом (9) и втором (14) выходах второго логического элемента (6) получаем состояние логической "1". Далее состояние логической "1" подается на первый токовый вход (15) третьего логического элемента (16). На второй токовый вход (17) третьего логического элемента подается состояние логического "0". На первом (19) и втором (20) выходах третьего логического элемента (16) получаем состояние логической "2", которое с первого токового выхода (19) третьего логического элемента (16) подается на первый токовый вход (2) первого логического элемента.

Временные диаграммы фиг. 9, 11 показывают, что предлагаемый элемент памяти на основе трех логических элементов прямого циклического сдвига работоспособен - в режиме хранения его выходные токовые сигналы имеют 3 устойчивых состояния: "0" - 0 мкА, "1" - 200 мкА, "2" - 400 мкА.

Рассмотрим работу трехзначного триггера (фиг. 4) на основе операции обратного циклического сдвига.

В триггере для значности сигналов k>2 может использоваться функция обратного циклического сдвига (вычитание 1 по modk)  . Схема триггера на основе операции обратного циклического сдвига показана на фиг. 4, а его таблица истинности имеет вид:

. Схема триггера на основе операции обратного циклического сдвига показана на фиг. 4, а его таблица истинности имеет вид:

Для данной таблицы логическая функция в триггере может быть записана в виде уравнения:

Временные диаграммы фиг. 13 показывают, что предлагаемый трехзначный триггер на основе трех логических элементов обратного циклического сдвига работоспособен - в режиме хранения его выходные токовые сигналы имеют 3 устойчивых состояния: "0" - 0 мкА, "1" - 200 мкА, "2" - 400 мкА.

Таким образом, рассмотренные схемотехнические решения триггеров характеризуются многозначным состоянием внутренних сигналов и многозначным представлением сигнала на его токовом выходе и могут быть положены в основу вычислительных и управляющих устройств, использующих многозначную линейную алгебру, частным случаем которой является булева алгебра.

ЛИТЕРАТУРА

1. Патент US 2011/0121877, fig. 9.

2. Патент ЕР 06011821, fig. 2.

3. Патент US 5.994.936, fig. 3.

4. Патент US 5.327.020, fig. 1.

5. Патент US 6.362.674, fig. 4A.

6. Патент US 6.535.024.

7. Патент US 7.098.652, fig. 1, fig. 10.

8. Патент US 4.441.075 fig. 1.

9. Авторское свидетельство СССР 1390790.

10. Авторское свидетельство СССР 1193798.

11. Авторское свидетельство СССР 1370732.

12. Патент US 5.065.052, fig. 3, fig. 10.

13. Патент US 7.697.319, fig. 2.

14. Патент US 8.232.825, fig. 9.

15. Патент US 8.115.522 fig. 2.

16. Патент US 7.626.433.

17. Патент US 7.236.029 fig. 3.

18. Патент US 6.268.752 fig. 4.

19. Патент US 6.486.720.

20. Патентная заявка US 2002/0003443 fig. 4.

21. Патент US 6.714.060.

22. Патент US 5.025.174.

23. Патент US 5.945.858.

24. Патент US 5.892.382 fig. 2.

25. Патент US 5.844.437 fig. 2.

26. Патент US 5.220.212.

27. Патент US 5.815.019 fig. 1.

28. Патент US 5.541.544 fig. 1.

29. Патент US 5.001.361 fig. 3.

30. Патент US 5.969.556 fig. 1.

31. Патент US 4.156.819 fig. 2.

32. Патент US 4.779.009 fig. 4.

33. Патент US 4.309.625 fig. 4.

34. Патент US 3.305.728.

35. Малюгин В. Д. Реализация булевых функций арифметическими полиномами // Автоматика и телемеханика, 1982. №4. С. 84-93.

36. Чернов Н.И. Основы теории логического синтеза цифровых структур над полем вещественных чисел // Монография. - Таганрог: ТРТУ, 2001. - 147 с.

37. Чернов Н.И. Линейный синтез цифровых структур АСОИУ» // Учебное пособие Таганрог. - ТРТУ, 2004 г., 118 с.