Результат интеллектуальной деятельности: СЕЛЕКТОР ДВОИЧНЫХ ЧИСЕЛ

Вид РИД

Изобретение

Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны селекторы двоичных чисел (см., например, патент РФ 2300130, кл. G06F 7/02, 2007 г.), содержащие логические элементы и выполняющие селекцию меньшего из двух n-разрядных двоичных чисел, задаваемых двоичными сигналами.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных селекторов двоичных чисел, относятся ограниченные функциональные возможности, обусловленные тем, что не выполняется селекция большего из указанных двоичных чисел.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип селектор двоичных чисел (патент РФ 2363034, кл. G06F 7/02, 2009 г.), который содержит логические элементы и выполняет селекцию большего из двух n-разрядных двоичных чисел, задаваемых двоичными сигналами.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся ограниченные функциональные возможности, обусловленные тем, что не выполняется селекция меньшего из указанных двоичных чисел.

Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения селекции большего и меньшего из двух n-разрядных двоичных чисел, задаваемых двоичными сигналами, и аппаратурный состав, образованный из логических элементов.

Указанный технический результат при осуществлении изобретения достигается тем, что в селекторе двоичных чисел, содержащем 4n-4 элементов «Запрет» и 3n-4 элементов ИЛИ, которые сгруппированы в n групп так, что j-я ( ) группа содержит два элемента «Запрет» и элемент ИЛИ, а m-я (

) группа содержит два элемента «Запрет» и элемент ИЛИ, а m-я ( ) группа дополнительно содержит два элемента «Запрет» и два элемента ИЛИ, в r-й (

) группа дополнительно содержит два элемента «Запрет» и два элемента ИЛИ, в r-й ( ) группе выход i-го (

) группе выход i-го ( ) элемента «Запрет» соединен с i-м входом первого элемента ИЛИ, в m-й группе выход i-го элемента «Запрет», подключенного инвертирующим входом к первому входу (i+1)-го элемента ИЛИ, и выход (i+1)-го элемента ИЛИ, подключенного вторым входом к выходу (3-i)-го элемента «Запрет», соединены соответственно с инвертирующим и неинвертирующим входами (i+2)-го элемента «Запрет», в первой группе инвертирующий и неинвертирующий входы первого элемента «Запрет» подключены соответственно к неинвертирующему и инвертирующему входам второго элемента «Запрет», первому и второму входам первого элемента ИЛИ, выход i-го элемента «Запрет» первой группы и выход (i+2)-го элемента «Запрет» m-й группы соединены соответственно с инвертирующим входом i-го элемента «Запрет» второй группы и инвертирующим входом i-го элемента «Запрет» (m+1)-й группы, первый, второй входы первого элемента ИЛИ первой группы, неинвертирующие входы первого, второго элементов «Запрет» r-й группы и выход первого элемента «ИЛИ» j-й группы образуют соответственно первый, (n+1)-й, r-й, (n+r)-й входы и j-й выход селектора двоичных чисел, особенность заключается в том, что в j-ю и r-ю группы введены соответственно элемент И и два дополнительных элемента ИЛИ, в r-й группе первый, второй входы и выход i-го дополнительного элемента ИЛИ соединены соответственно с неинвертирующим входом i-го, инвертирующим входом (3-i)-го элементов «Запрет» и i-м входом элемента И, а i-й вход элемента И первой группы и выход элемента И j-й группы подключены соответственно к i-му входу первого элемента ИЛИ первой группы и (n+j)-му выходу селектора двоичных чисел.

) элемента «Запрет» соединен с i-м входом первого элемента ИЛИ, в m-й группе выход i-го элемента «Запрет», подключенного инвертирующим входом к первому входу (i+1)-го элемента ИЛИ, и выход (i+1)-го элемента ИЛИ, подключенного вторым входом к выходу (3-i)-го элемента «Запрет», соединены соответственно с инвертирующим и неинвертирующим входами (i+2)-го элемента «Запрет», в первой группе инвертирующий и неинвертирующий входы первого элемента «Запрет» подключены соответственно к неинвертирующему и инвертирующему входам второго элемента «Запрет», первому и второму входам первого элемента ИЛИ, выход i-го элемента «Запрет» первой группы и выход (i+2)-го элемента «Запрет» m-й группы соединены соответственно с инвертирующим входом i-го элемента «Запрет» второй группы и инвертирующим входом i-го элемента «Запрет» (m+1)-й группы, первый, второй входы первого элемента ИЛИ первой группы, неинвертирующие входы первого, второго элементов «Запрет» r-й группы и выход первого элемента «ИЛИ» j-й группы образуют соответственно первый, (n+1)-й, r-й, (n+r)-й входы и j-й выход селектора двоичных чисел, особенность заключается в том, что в j-ю и r-ю группы введены соответственно элемент И и два дополнительных элемента ИЛИ, в r-й группе первый, второй входы и выход i-го дополнительного элемента ИЛИ соединены соответственно с неинвертирующим входом i-го, инвертирующим входом (3-i)-го элементов «Запрет» и i-м входом элемента И, а i-й вход элемента И первой группы и выход элемента И j-й группы подключены соответственно к i-му входу первого элемента ИЛИ первой группы и (n+j)-му выходу селектора двоичных чисел.

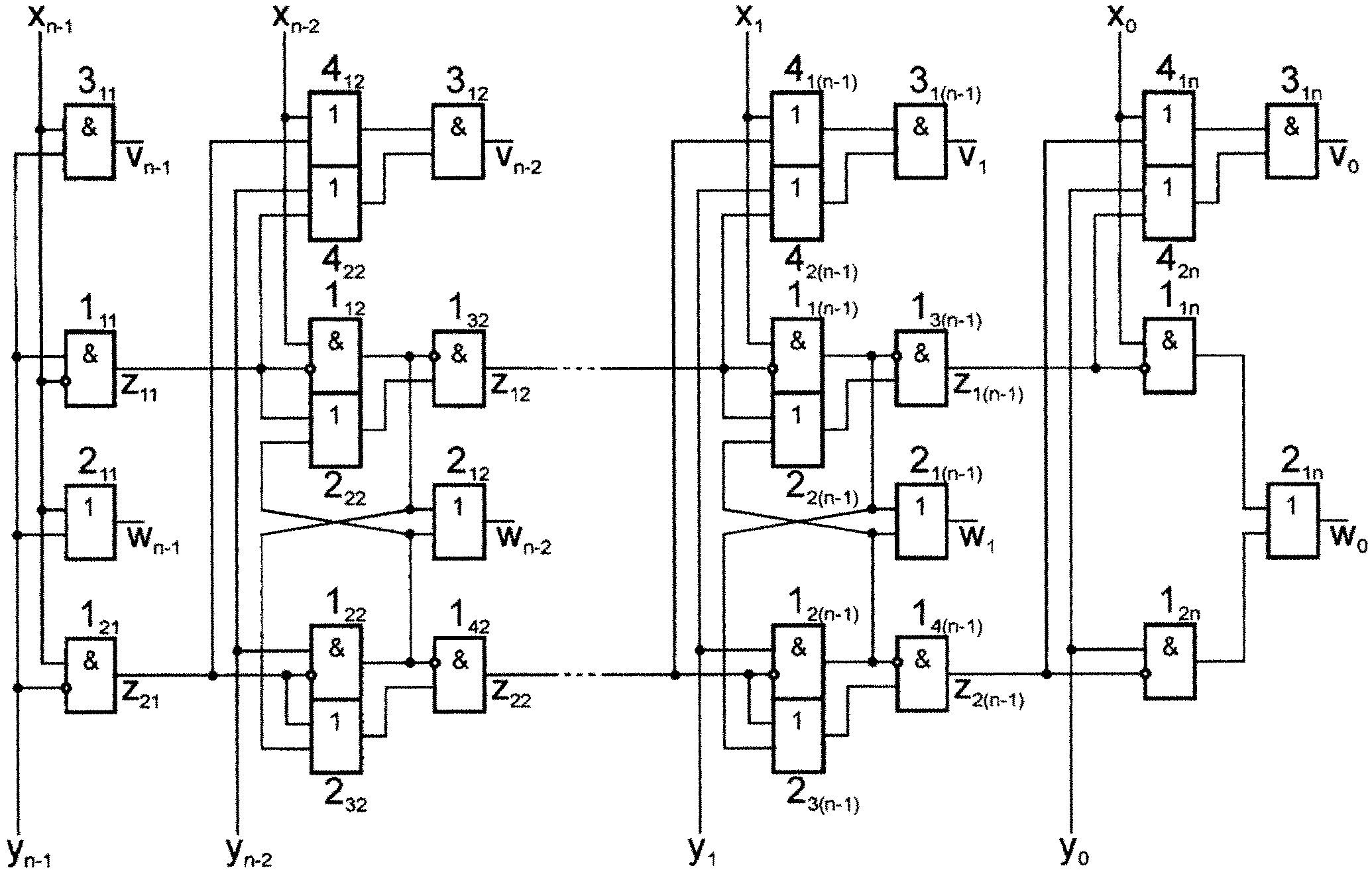

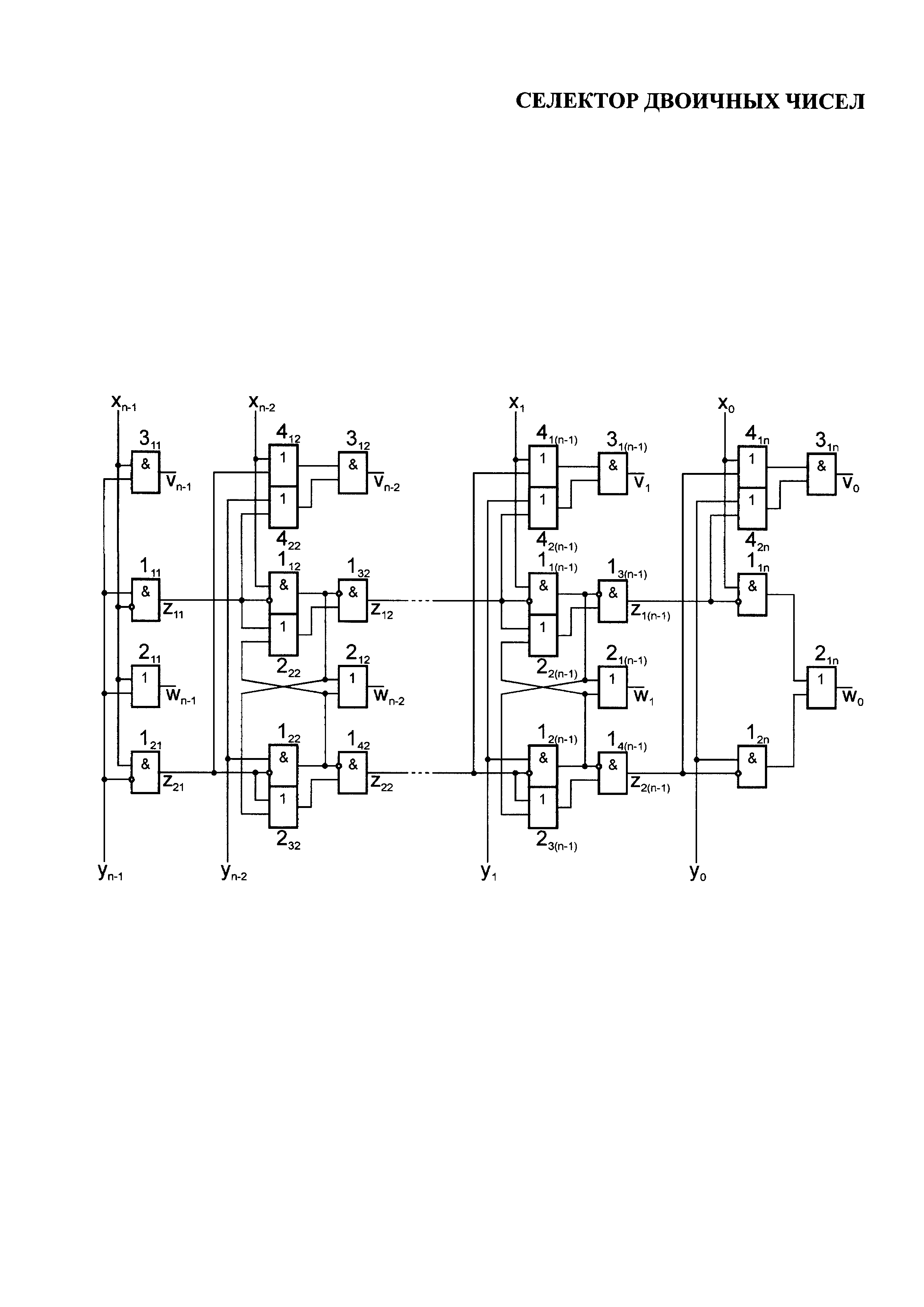

На чертеже представлена схема предлагаемого селектора двоичных чисел.

Селектор двоичных чисел содержит 4n-4 элементов «Запрет» 111, 121, 112, …, 14(n-1), 11n, 12n (третий снизу рис. в табл. 3.5 на с. 103 в книге Справочник по цифровой вычислительной технике. Малиновский Б.Н., Александров В.Я., Боюн В.П. и др. / Под ред. Б.Н. Малиновского. Киев: Техника, 1974 г.), 3n-4 элементов ИЛИ 211, 212, …, 23(n-1), 21n, n элементов «И» 311, …, 31n и 2n-2 дополнительных элементов ИЛИ 412, …, 42(n-1), 41n, 42n, причем все элементы сгруппированы в n групп так, что j-я ( ) группа содержит элементы 11j, 12j, 21j, 31j, m-я (

) группа содержит элементы 11j, 12j, 21j, 31j, m-я ( ) группа дополнительно содержит элементы 13m, 14m, 22m, 23m, а r-я (

) группа дополнительно содержит элементы 13m, 14m, 22m, 23m, а r-я ( ) группа дополнительно содержит элементы 41r, 42r, выход элемента 1ir (

) группа дополнительно содержит элементы 41r, 42r, выход элемента 1ir ( ), первый, второй входы и выход элемента 4ir соединены соответственно с i-ым входом элемента 21r, неинвертирующим входом элемента 1ir, инвертирующим входом элемента 1(3-i)r и i-м входом элемента 31r, выход элемента 1im, подключенного инвертирующим входом к первому входу элемента 2(i+1)m, и выход элемента 2(i+1)m, подключенного вторым входом к выходу элемента 1(3-i)m, соединены соответственно с инвертирующим и неинвертирующим входами элемента 1(i+2)m, инвертирующий и неинвертирующий входы элемента 111 подключены соответственно к неинвертирующему и инвертирующему входам элемента 121, первым и вторым входам элементов 211, 311, выходы элементов 1i1 и 1(i+2)m соединены соответственно с инвертирующими входами элементов 1i2 и 1i(m+1), а первый, второй входы элемента 211, неинвертирующие входы элементов 11r, 12r и выходы элементов 21j, 31j образуют соответственно первый, (n+1)-й, r-й, (n+r)-й входы и j-й, (n+j)-й выходы селектора двоичных чисел.

), первый, второй входы и выход элемента 4ir соединены соответственно с i-ым входом элемента 21r, неинвертирующим входом элемента 1ir, инвертирующим входом элемента 1(3-i)r и i-м входом элемента 31r, выход элемента 1im, подключенного инвертирующим входом к первому входу элемента 2(i+1)m, и выход элемента 2(i+1)m, подключенного вторым входом к выходу элемента 1(3-i)m, соединены соответственно с инвертирующим и неинвертирующим входами элемента 1(i+2)m, инвертирующий и неинвертирующий входы элемента 111 подключены соответственно к неинвертирующему и инвертирующему входам элемента 121, первым и вторым входам элементов 211, 311, выходы элементов 1i1 и 1(i+2)m соединены соответственно с инвертирующими входами элементов 1i2 и 1i(m+1), а первый, второй входы элемента 211, неинвертирующие входы элементов 11r, 12r и выходы элементов 21j, 31j образуют соответственно первый, (n+1)-й, r-й, (n+r)-й входы и j-й, (n+j)-й выходы селектора двоичных чисел.

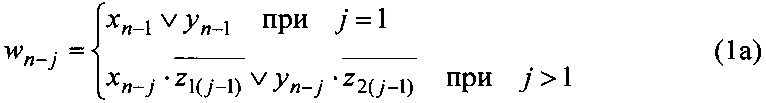

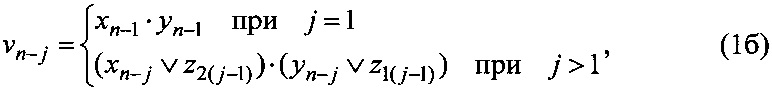

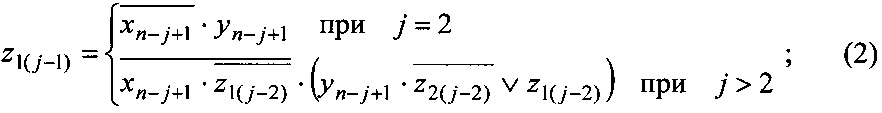

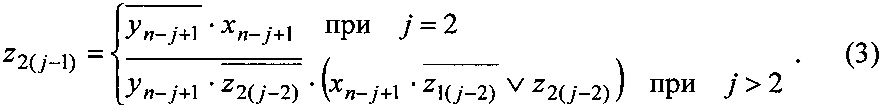

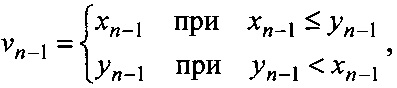

Работа предлагаемого селектора двоичных чисел осуществляется следующим образом. На его первый, …, n-й и (n+1)-й, …, (2n)-й входы подаются соответственно произвольные двоичные сигналы xn-1, …, x0∈{0,1} и yn-1, …, y0∈{0,1}, которые задают подлежащие обработке n-разрядные двоичные числа xn-1…x0 и yn-1…y0 (xn-1, yn-1 и x0, yQ определяют значения старших и младших разрядов соответственно). Тогда сигналы на j-ом ( ) и (n+j)-м выходах предлагаемого селектора будут определяться выражениями

) и (n+j)-м выходах предлагаемого селектора будут определяться выражениями

и

где

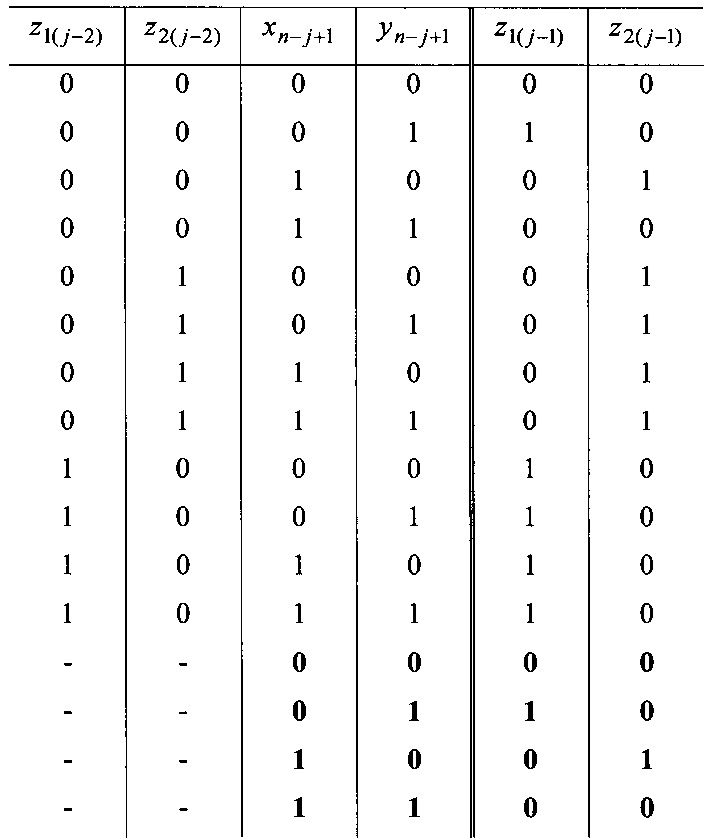

В представленной ниже таблице приведены значения реализуемых выражениями (2), (3) функций на всех возможных наборах значений их аргументов. Жирным в таблице выделены значения функций и их аргументов при j=2.

Анализ данных, приведенных в таблице, позволяет заключить, что:

1) если z1(j-2)=z2(j-2)=0 и xn-j+1=yn-j+1, то z1(j-1)=z2(j-l)=0;

2) если z1(j-2)=z2(j-2)=0 и xn-j+1>yn-j+1 (z1(j-2)=z2(j-2)=0 и yn-j+1>xn-j+1), то z1(j-1)=0 и z2(j-1)=1 (z1(j-1)=1 и z2(j-1)=0);

3) если z1(j-2)=0 и z2(j-2)=1 (z1(j-2)=1 и z2(j-2)=0), то z1(j-1)=0 и z2(j-1)=1 (z1(j-1)=1 и z2(j-1)=0);

4) если xn-1=yn-1 или xn-1>yn-1 (yn-1>xn-1), то соответственно z11=z21=0 или z11=0 и z21=1 (z11=1 и z21=0).

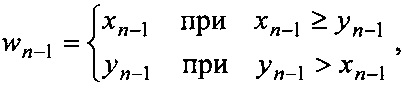

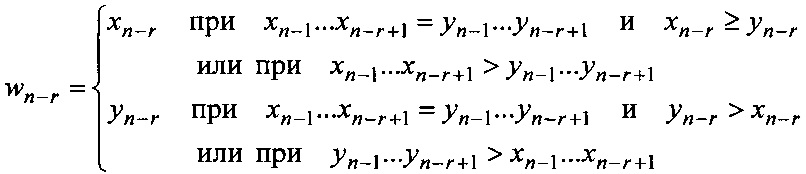

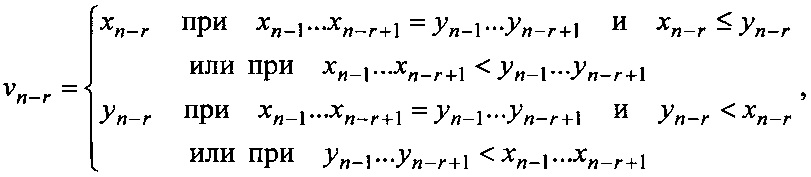

Таким образом, на первом, r-м ( ) и (n+1)-м, (n+r)-м выходах предлагаемого селектора согласно (1) соответственно получим

) и (n+1)-м, (n+r)-м выходах предлагаемого селектора согласно (1) соответственно получим

и

где xn-1…xn-r+1 и yn-1…yn-r+1 - фрагменты n-разрядных двоичных чисел xn-1…x0 и yn-1…y0. Следовательно, с учетом последних четырех выражений имеем wn-1…w0=max(xn-1…x0, yn-1…y0), vn-1…v0=min(xn-1…x0, yn-1…y0), где wn-1…w0 и vn-1…v0 - n-разрядные двоичные числа, задаваемые двоичными сигналами w0, …, wn-1, v0, …, vn-1∈{0,1} (wn-1, vn-1 и w0, v0 определяют значения старших и младших разрядов соответственно).

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый селектор двоичных чисел обладает более широкими по сравнению с прототипом функциональными возможностями, так как обеспечивает селекцию большего и меньшего из двух n-разрядных двоичных чисел, задаваемых двоичными сигналами. При этом аппаратурный состав указанного селектора образован из логических элементов.

Селектор двоичных чисел, содержащий 4n-4 элементов «Запрет» и 3n-4 элементов ИЛИ, которые сгруппированы в n групп так, что j-я группа содержит два элемента «Запрет» и элемент ИЛИ, а m-я группа дополнительно содержит два элемента «Запрет» и два элемента ИЛИ, в r-й группе выход i-го элемента «Запрет» соединен с i-м входом первого элемента ИЛИ, в m-й группе выход i-го элемента «Запрет», подключенного инвертирующим входом к первому входу (i+1)-го элемента ИЛИ, и выход (i+1)-го элемента ИЛИ, подключенного вторым входом к выходу (3-i)-го элемента «Запрет», соединены соответственно с инвертирующим и неинвертирующим входами (i+2)-го элемента «Запрет», в первой группе инвертирующий и неинвертирующий входы первого элемента «Запрет» подключены соответственно к неинвертирующему и инвертирующему входам второго элемента «Запрет», первому и второму входам первого элемента ИЛИ, выход i-го элемента «Запрет» первой группы и выход (i+2)-го элемента «Запрет» m-й группы соединены соответственно с инвертирующим входом i-го элемента «Запрет» второй группы и инвертирующим входом i-го элемента «Запрет» (m+1)-й группы, первый, второй входы первого элемента ИЛИ первой группы, неинвертирующие входы первого, второго элементов «Запрет» r-й группы и выход первого элемента ИЛИ j-й группы образуют соответственно первый, (n+1)-й, r-й, (n+r)-й входы и j-й выход селектора двоичных чисел, отличающийся тем, что в j-ю и r-ю группы введены соответственно элемент «И» и два дополнительных элемента ИЛИ, в r-й группе первый, второй входы и выход i-го дополнительного элемента ИЛИ соединены соответственно с неинвертирующим входом i-го, инвертирующим входом (3-i)-го элементов «Запрет» и i-м входом элемента И, а i-й вход элемента И первой группы и выход элемента И j-й группы подключены соответственно к i-му входу первого элемента ИЛИ первой группы и (n+j)-му выходу селектора двоичных чисел.