Результат интеллектуальной деятельности: ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО

Вид РИД

Изобретение

Изобретение относится к вычислительной технике и может быть использовано для вычисления логических функций в отказоустойчивых, радиационно-стойких программируемых логических интегральных схемах (ПЛИС).

Известно программируемое логическое устройство, содержащее первую, вторую и третью группы D-триггеров количеством по m·2n (n - число входных переменных, m - число выходных функций), третью группу D-триггеров количеством 2(n-1)m, группу m(n-1) элементов И, счетчик, группу m·2n элементов И с тремя состояниями на выходе, дешифратор, группу m(n-1) элементов ИЛИ, вторую группу m·2n элементов И с тремя состояниями на выходе и m блоков вычисления функций, каждый блок вычисления функций содержит группу 4·2n элементов И с тремя состояниями на выходе, два D-триггера, Т-триггер, RS-триггер фиксации импульса, пять элементов ИЛИ, три элемента И, четыре инвертора, n групп элементов 2·2 НЕ-И-ИЛИ (в каждую i-ю группу входит 2n-1 элементов, i=1, n), элемент задержки, дополнительную группу элементов И с тремя состояниями на выходе (патент РФ №2146840 от 20.03.2000, кл. G11C 17/00, G06F 7/00).

Недостатком известного устройства являются высокие аппаратурные затраты, выраженные в количестве транзисторов, на реализацию логической функции в программируемых логических интегральных схемах (ПЛИС).

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является программируемое логическое устройство, содержащее группу n инверторов, n групп передающих транзисторов (n - число входных переменных) по 2i, i=1, n транзисторов в группе, группу 2n инверторов настройки, выходной инвертор, входы n переменных, группу 2n входов настройки, выход устройства, причем затвор каждого нечетного транзистора i-й группы передающих транзисторов i=1, n подключен к выходу i-го инвертора группы n инверторов, затвор каждого четного транзистора i-й группы передающих транзисторов подключен к i-му входу входов n переменных, истоки 2n транзисторов n-й группы подключены к выходам инверторов группы 2n инверторов настройки, входы которых являются группой 2n входов настройки, стоки четных и нечетных транзисторов n-й группы объединены и подключены к истокам соответствующих 2n-1 транзисторов n-1-й группы, стоки которых объединены и подключены к истокам соответствующих 2n-2 транзисторов n-2-й группы и так далее, стоки двух последних транзисторов 1-й группы объединены и подключены ко входу выходного инвертора, выход которого является выходом устройства, входы n переменных подключены ко входам соответствующих инверторов из группы n инверторов (Строганов А., Цыбин С. Программируемая коммутация в ПЛИС: взгляд изнутри // Компоненты и технологии. - 2010. - №11. С.56-62 Рис.9, 12 [Электронный ресурс]. - URL: http://www.kit-e.ru/articles/plis/2010_11_56.php, 12.11.12 г.).

Недостатком известного устройства, принятого за прототип, является низкая отказо- и сбоеустойчивость относительно отказов транзисторов в условиях воздействия радиации.

Это обусловлено следующими обстоятельствами. Технические средства прототипа ориентированы на вычисление логических функций в отсутствие отказов (сбоев). Отказ или сбой всего одного транзистора в процессе вычислений может привести к неправильному результату.

Так, при сбое всего одного транзистора (в случае попадания тяжелых заряженных частиц внутрь микросхемы при радиационном воздействии) в одном из инверторов группы n инверторов группы 2n инверторов настройки, выходном инверторе, классифицируемом как SET (Single Event Transient - кратковременное изменение состояния выхода логического элемента), кратковременно изменяющих состояние логических элементов, при задании на входах n переменных соответствующего набора переменных для считывания информации с конкретного входа группы 2n входов настройки может быть сформировано неверное логическое значение на выходе устройства вследствие изменения логического состояния конкретного инвертора группы n инверторов группы 2n инверторов настройки, либо изменится логическое состояние выходного инвертора, либо сформируется неверный адрес и будет активирован неверный путь в дереве из передающих транзисторов в составе n групп передающих транзисторов.

Также может кратковременно измениться состояние одного из передающих транзисторов в составе n групп передающих транзисторов (с открытого на закрытое) при правильном функционировании инверторов группы n инверторов группы 2n инверторов настройки, выходном инверторе и правильном активировании затворов соответствующих передающих транзисторов.

Все это может привести к запоминанию неверного значения логической функции во внешних по отношению к устройству элементах памяти.

В случае отказов, классифицируемых, например, как SEL (Single Event Latch) - тиристорный эффект, требующий для восстановления обязательного снятия питания, SEGR (Single Event Gate Rupture) - «разрыв» вентиля, вызванный ионизацией вследствие тиристорного эффекта, даже повторные вычисления не позволят получить правильный результат.

Задачей изобретения является повышение отказоустойчивости относительно сбоев и отказов транзисторов.

Поставленная задача решена за счет того, что в известное устройство, содержащее группу n инверторов переменных, n групп основных передающих транзисторов (n - число входных переменных) по 2i, i=1, n транзисторов в группе, группу 2n инверторов настройки, выходной инвертор, входы n переменных, 2n входы настройки, выход устройства, причем входы настройки подключены ко входам соответствующих инверторов из группы 2n инверторов настройки, входы i-x инверторов подключены к соответствующим к i-м входам входов n переменных, затвор каждого четного транзистора i-й группы из n групп передающих транзисторов подключен к i-му входу входов n переменных, затвор каждого нечетного транзистора i-й группы из n групп передающих транзисторов подключен к выходу i-го инвертора группы n инверторов переменных, входы которых подключены к i-му входу входов n переменных, стоки четных и нечетных - двух передающих транзисторов первой группы - объединены и подключены ко входу выходного инвертора, выход которого является выходом устройства, каждый инвертор из группы 2n инверторов настройки, группы n инверторов переменных, выходной инвертор содержит основной транзистор n-МОП, основной транзистор p-МОП, вход напряжения питания, вход «Ноль вольт», вход инвертора, выход инвертора, причем затворы основных транзисторов n-МОП и p-МОП объединены и являются входом инвертора, сток основного транзистора n-МОП подключен ко входу напряжения питания, сток основного транзистора p-МОП подключен к выходу инвертора, дополнительно введены 2n+1-1 подгрупп дополнительных передающих транзисторов для каждого основного четного и нечетного транзистора n групп передающих транзисторов, состоящие из трех транзисторов, причем затворы дополнительных передающих транзисторов j-й подгруппы 2.j (j=1…2n+1-1) объединены и подключены к затвору соответствующего четного или нечетного основного транзистора в n группах передающих транзисторов (по 2i, i=1, n транзисторов в группе, где n - число входных переменных), сток первого дополнительного транзистора в каждой из подгрупп дополнительных передающих транзисторов подключен к стоку соответствующего основного транзистора, исток первого дополнительного транзистора подключен к истоку основного транзистора и стокам второго и третьего дополнительных транзисторов, истоки которых объединены и подключены к стокам объединенных четных и нечетных передающих транзисторов n+1-й группы и так далее, объединенные истоки второго и третьего дополнительных транзисторов последней группы 2.n передающих транзисторов подключены к выходам соответствующих инверторов из группы 2n инверторов настройки, каждый инвертор из группы 2n инверторов настройки, группы n инверторов переменных, выходной инвертор содержит три дополнительных транзистора n-МОП и три дополнительных транзистора p-МОП, причем затворы всех дополнительных транзисторов n-МОП и трех дополнительных транзисторов p-МОП объединены и подключены ко входу инвертора, исток первого дополнительного транзистора p-МОП подключен ко входу «Ноль вольт» и к истоку третьего дополнительного транзистора p-МОП, сток дополнительного транзистора p-МОП подключен в истоку основного транзистора p-МОП, сток второго дополнительного транзистора p-МОП подключен к истоку третьего дополнительного транзистора p-МОП, сток которого подключен к выходу инвертора, исток первого дополнительного транзистора n-МОП подключен к выходу инвертора, а сток первого дополнительного транзистора n-МОП подключен к истоку основного транзистора n-МОП, исток второго дополнительного транзистора n-МОП подключен к выходу инвертора, сток второго дополнительного транзистора n-МОП подключен к истоку третьего дополнительного транзистора n-МОП и стоку основного транзистора n-МОП, сток третьего дополнительного транзистора n-МОП подключен ко входу напряжения питания инвертора.

Признаки прототипа, совпадающие с существенными признаками заявляемого изобретения, - содержит группу n инверторов переменных, n групп основных передающих транзисторов (n - число входных переменных) по 2i, i=1, n транзисторов в группе, группу 2n инверторов настройки, выходной инвертор, входы n переменных, 2n входы настройки, выход устройства, каждый инвертор из группы 2n инверторов настройки, группы n инверторов переменных, выходной инвертор содержит основной транзистор n-МОП, основной транзистор p-МОП, вход напряжения питания, вход «Ноль вольт», вход инвертора, выход инвертора.

Признаки заявляемого технического решения, отличительные от прототипа, - введены 2n+1-1 подгрупп дополнительных передающих транзисторов для каждого основного четного и нечетного транзистора n групп передающих транзисторов, состоящие из трех транзисторов, каждый инвертор из группы 2n инверторов настройки, группы n инверторов переменных, выходной инвертор содержит три дополнительных транзистора n-МОП и три дополнительных транзистора p-МОП.

Отличительные признаки в сочетании с известными позволяют повысить отказоустойчивость устройства относительно отказов транзисторов путем реализации логических функций, толерантных к константным или инверсным отказам одной переменной.

Введение 2n+1-1 подгрупп дополнительных передающих транзисторов и соответствующих новых связей для каждого основного четного и нечетного транзистора n групп передающих транзисторов, состоящих из трех транзисторов, позволяет обеспечить отказо- и сбоеустойчивость передачи информации от группы 2n инверторов настройки к выходному инвертору путем реализации логической функции, толерантной к константным или инверсным отказам одной переменной, соответствующей четному и нечетному транзистору в n группах передающих транзисторов.

Введение трех дополнительных транзисторов n-МОП и трех дополнительных транзисторов p-МОП и соответствующих новых связей в каждый инвертор из группы 2n инверторов настройки, группы n инверторов переменных, выходной инвертор позволяет обеспечить отказо- и сбоеустойчивость группы 2n инверторов настройки, группы n инверторов переменных, выходного инвертора путем реализации в них функции, толерантной к константным или инверсным отказам одного транзистора в подсхемах подключения напряжения питания:

где x - переменные состояния основного 1 и дополнительных 2, 3, 4 транзисторов n-МОП, и подсхеме подключения шины «Ноль вольт» путем реализации функции, двойственной функции (1):

где y - переменные состояния основного 1 и дополнительных 2, 3, 4 транзисторов p-МОП.

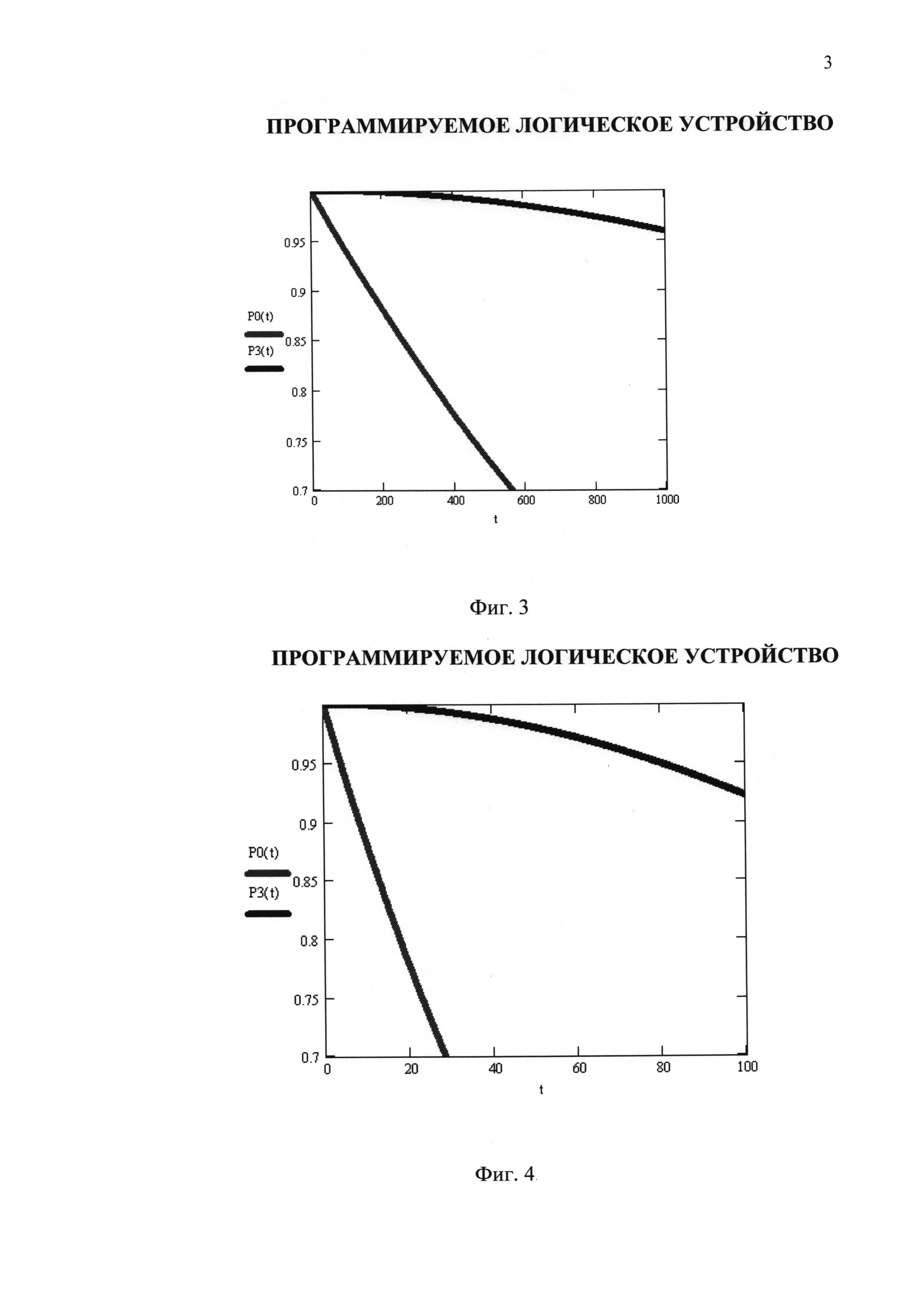

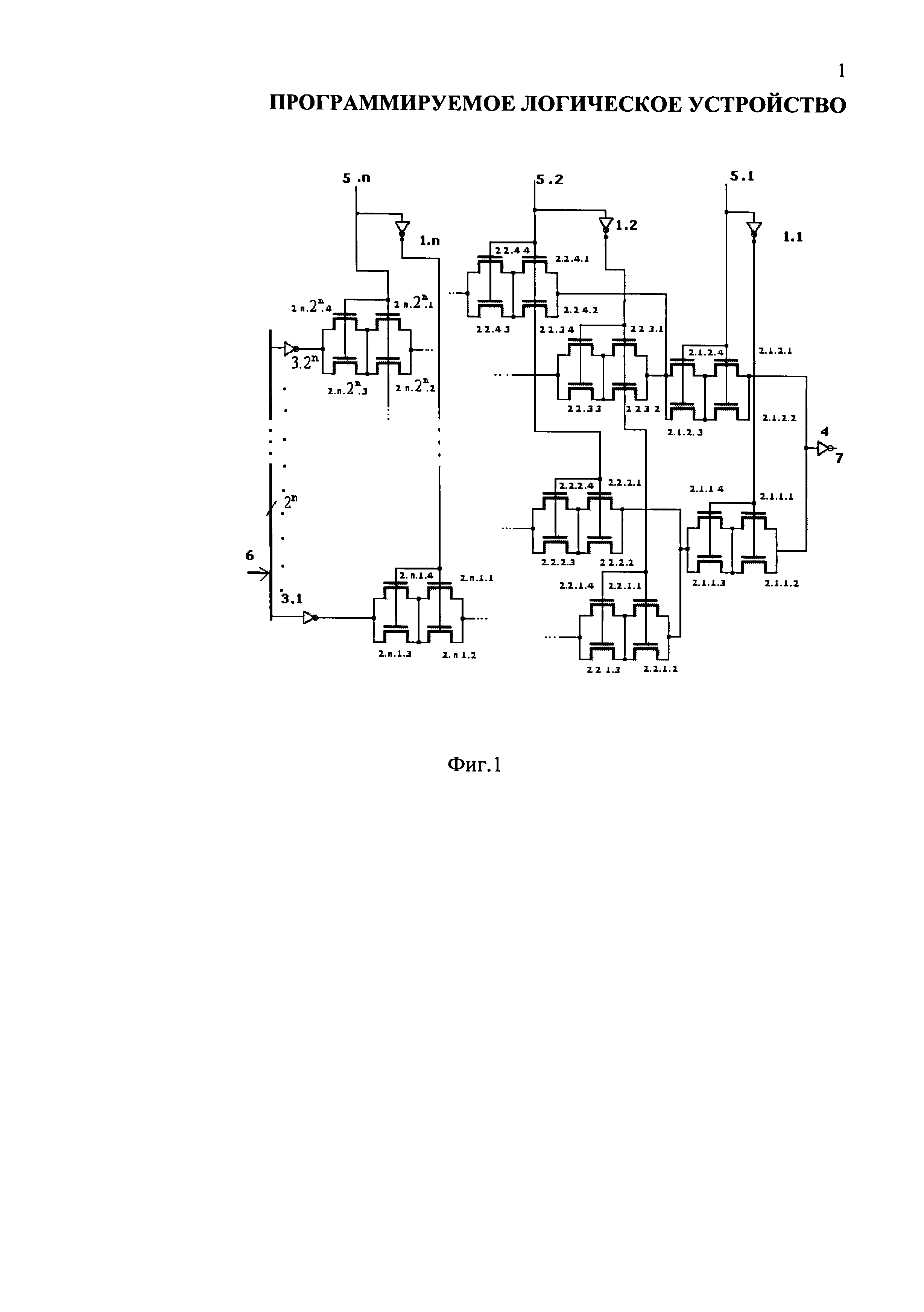

На фиг.1 изображена схема электрическая структурная программируемого логического устройства.

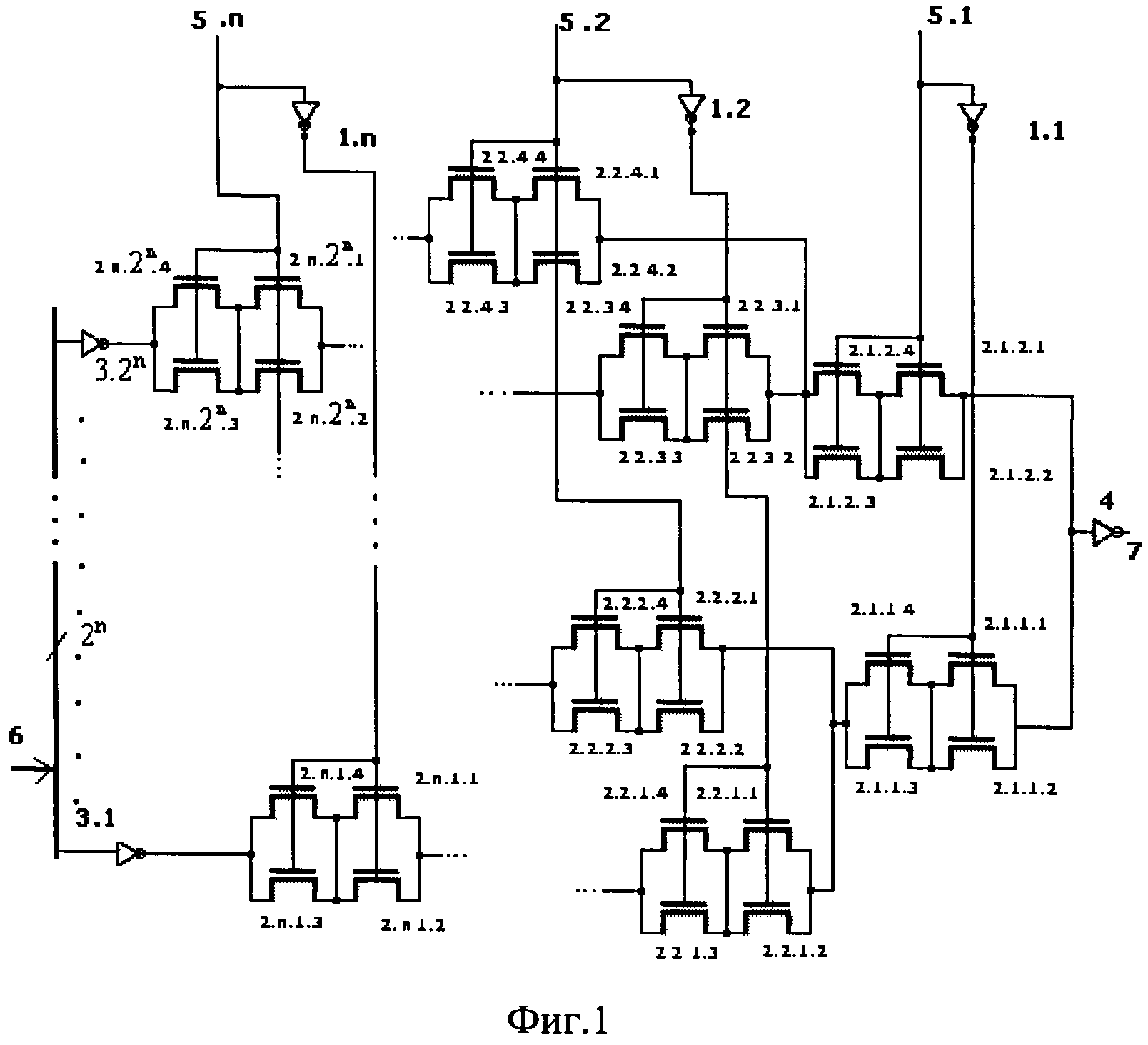

На фиг.2 изображена схема электрическая структурная инвертора группы 2n инверторов настройки (группы n инверторов переменных, выходного инвертора).

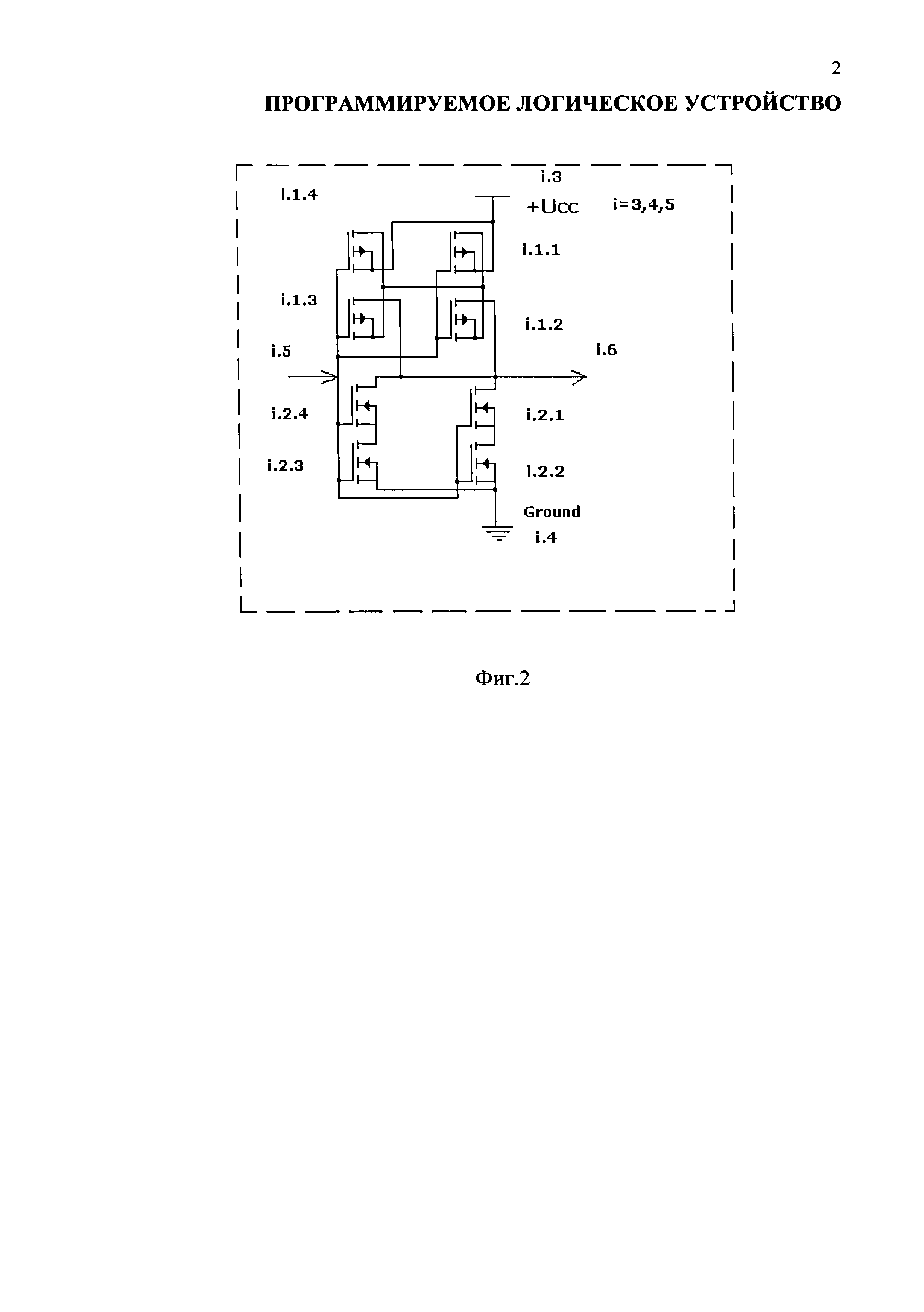

На фиг.3 изображены графики изменения вероятности безотказной работы прототипа (Р0) и предлагаемого устройства (Р3) с учетом экспоненциальной модели отказов (сбоев) и интенсивности отказов одного транзистора λ=10-5 при n=4.

На фиг.4 изображены графики изменения вероятности безотказной работы прототипа (Р0) и предлагаемого устройства (Р3) с учетом экспоненциальной модели отказов (сбоев) и интенсивности отказов одного транзистора λ=10-4 при n=5.

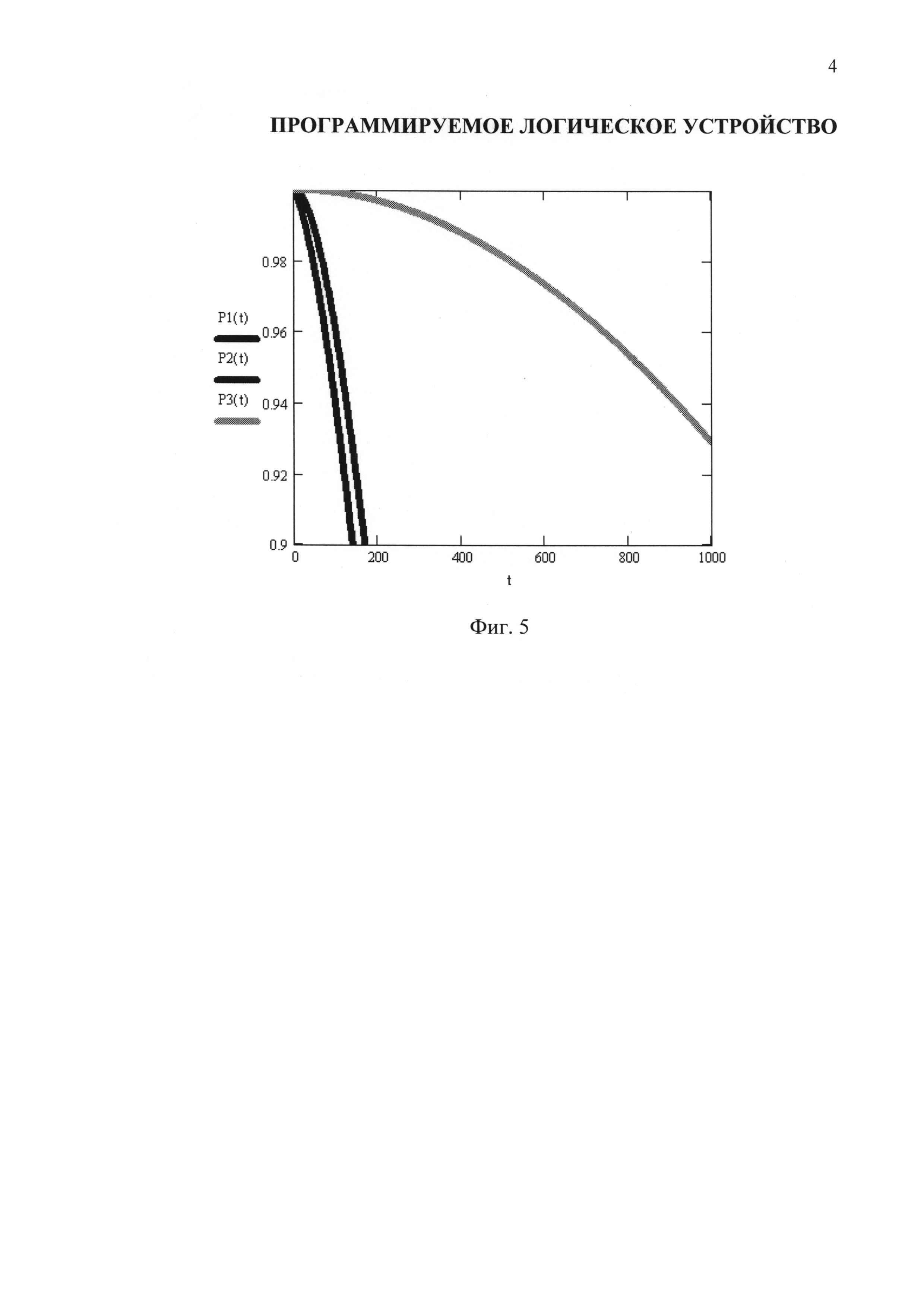

На фиг.5 изображены графики изменения вероятности безотказной работы троированного прототипа (Р1), троированного прототипа с тремя мажоритарами (Р2) и предлагаемого устройства (Р3) с учетом экспоненциальной модели отказов (сбоев) и интенсивности отказов одного транзистора λ=10-5 при n=5.

Программируемое логическое устройство содержит группу n инверторов переменных 1, n групп основных передающих транзисторов 2 (n - число входных переменных) по 2i, i=1, n транзисторов в группе, группу 2n инверторов настройки 3, выходной инвертор 4, входы n переменных 5, 2n входы настройки 6, выход устройства 7.

Входы настройки 6 подключены ко входам соответствующих инверторов из группы 2n инверторов настройки 3.

Входы i-x инверторов подключены к соответствующим к i-м входам входов n переменных 5.i.

Затвор каждого четного транзистора i-й группы 2.i из n групп передающих транзисторов 2 подключен к i-му входу входов n переменных 5.i.

Затвор каждого нечетного транзистора i-й группы 2.i из n групп передающих транзисторов 2 подключен к выходу i-го инвертора группы n инверторов переменных 1.i, входы которых подключены к i-му входу входов n переменных 5.i.

Стоки четных и нечетных - двух передающих транзисторов первой группы 2.1 - объединены и подключены ко входу выходного инвертора 4, выход которого является выходом устройства 7.

Каждый i-й (i∈1, 3, 4) инвертор из группы 2n инверторов настройки 3, группы n инверторов переменных 1, выходной инвертор содержит основной транзистор n-МОП i.1.1, основной транзистор p-МОП i.2.1, вход напряжения питания i.3, вход «Ноль вольт» i.4, вход инвертора i.5, выход инвертора i.6.

Причем затворы основных транзисторов n-МОП i.1.1 и p-МОП i.2.1 объединены и являются входом инвертора i.5, сток основного транзистора n-МОП i.1.1 подключен ко входу напряжения питания i.3, сток основного транзистора p-МОП i.2.1 подключен к выходу инвертора i.6.

С целью повышения отказо- и сбоеустойчивости устройства относительно отказов транзисторов в условиях воздействия радиации дополнительно введены 2n+1-2 подгрупп дополнительных передающих транзисторов для каждого основного четного и нечетного транзистора n групп передающих транзисторов 2 (n - число входных переменных) по 2i, i=1, n транзисторов в группе, состоящие из трех транзисторов,

Причем затворы дополнительных передающих транзисторов j-й подгруппы 2.j (j=1…2n+1-2) объединены и подключены к затвору соответствующего четного 2.i.2γ (γ=1…2i, i=1, n) или нечетного 2.i.2γ-1 основного транзистора в n группах передающих транзисторов 2 (по 2i, i=1, n транзисторов в группе, где n - число входных переменных), сток первого дополнительного транзистора 2.i.ξ.2 (ξ=1…2i, i=1, n) в каждой из 2.j (j=1…2n+1-2) подгрупп дополнительных передающих транзисторов подключен к стоку соответствующего основного транзистора 2.i.ξ.1, исток первого дополнительного транзистора 2.i.ξ.2 подключен к истоку основного транзистора 2.i.ξ.1 и стокам второго 2.i.ξ.3 и третьего 2.i.ξ.4 дополнительных транзисторов, истоки которых объединены и подключены к стокам объединенных четных 2.i+1.2γ (γ=1…2i, i=1, n) и нечетных 2.i+1.2γ-1 передающих транзисторов n+1-й группы 2.n+1 и так далее, объединенные истоки второго 2.n.ξ.3 и третьего 2.n.ξ.4 дополнительных транзисторов последней группы 2.n передающих транзисторов подключены к выходам соответствующих ξ-x (ξ=1…2i, i=1, n) инверторов из группы 2n инверторов настройки 3.

Каждый i-й (i∈1,3,4) инвертор из группы 2n инверторов настройки 3, группы n инверторов переменных 1, выходной инвертор содержит три дополнительных транзистора n-МОП i.1.2, i.1.3, i.1.4 и три дополнительных транзистора p-МОП i.2.2, i.2.3, i.2.4.

Причем затворы всех дополнительных транзисторов n-МОП i.1.2, i.1.3, i.1.4 и трех дополнительных транзисторов p-МОП i.2.2, i.2.3, i.2.4 объединены и подключены ко входу i.5 инвертора, исток первого дополнительного транзистора p-МОП i.2.2 подключен ко входу «Ноль вольт» i.4 и к истоку третьего дополнительного транзистора p-МОП i.2.3, сток дополнительного транзистора p-МОП i.2.2 подключен к истоку основного транзистора p-МОП i.2.1, сток второго дополнительного транзистора p-МОП i.2.3 подключен к истоку третьего дополнительного транзистора p-МОП i.2.4, сток которого подключен к выходу i.6 инвертора, исток первого дополнительного транзистора n-МОП к 1.2 подключен к выходу i.6 инвертора, а сток первого дополнительного транзистора n-МОП i.1.2 подключен к истоку основного транзистора n-МОП i.1.1, исток второго дополнительного транзистора n-МОП i.1.3 подключен к выходу i.6 инвертора, сток второго дополнительного транзистора n-МОП i.1.3 подключен к истоку третьего дополнительного транзистора n-МОП i.1.4 и стоку основного транзистора n-МОП i.1.1, сток третьего дополнительного транзистора n-МОП i.1.4 подключен ко входу напряжения питания инвертора i.3.

Программируемое логическое устройство работает в следующих режимах:

1) программирования;

2) вычислений;

3) вычислений в случае сбоев и отказов;

4) ограниченной функциональности в крайнем случае большого количества отказов.

1) Режим программирования. В этом режиме устройство работает аналогично прототипу.

При этом с помощью внешних по отношению к устройству технических средств на 2n входах настройки 6 устанавливаются логические уровни, соответствующие логической функции n переменных, которую необходимо вычислять (таблице истинности заданной логической функции n переменных, содержащей 2n строк).

Так, для реализации функции сложения по модулю два (исключающего ИЛИ) четырех переменных (n=4), x4⊕x3⊕x2⊕x1, где xi - сигнал на входах 5.4,5.3,52.5.1, на входах 6 (6.0…6.15) устанавливаются следующие логические уровни (Строганов А., Цыбин С. Программируемая коммутация в ПЛИС: взгляд изнутри // Компоненты и технологии. - 2010. - №11. С.56-62. Рис.9 [Электронный ресурс]. - URL: http://www.kit-e.ru/articles/plis/2010_11_56.php. Дата обращения 12.01.13 г.) - табл.1:

На выходах инверторов группы 2n инверторов настройки 3 устанавливаются значения, инверсные логическим уровням, устанавливаемым на 2n входах настройки 6.

2) Режим вычислений

При поступлении на входы n переменных 5 с помощью внешних по отношению к устройству технических средств некоторого из 2n набора (табл.1 - 5.4…5.1) активизируется одна из 2n цепочек в n группах 2 передающих транзисторов, состоящих из подгрупп, включающих один основной транзистор и три дополнительных передающих транзистора - «четверку» транзисторов (четные «четверки» транзисторов непосредственно с соответствующего входа n переменных 5, если он равен логической единице, нечетные «четверки» транзисторов - через соответствующий инвертор группы n инверторов переменных 1 с выхода соответствующего инвертора группы 2n инверторов настройки 3 через выходной инвертор 4 на выход устройства 7).

Так, при поступлении на входы n переменных 5 набора 0111 (набор №7) «набирается» цепочка со входа 6, на котором установлен логический ноль, через инвертор 3.8, на выходе которого устанавливается логическая единица через «четную четверку транзисторов» 2.4.8 (2.4.8.1, 2.4.8.2, 2.4.8.3, 2.4.8.4), через «четную четверку транзисторов» 2.3.3 (2.3.3.1, 2.3.3.2, 2.3.3.3, 2.3.3.4), через «четную четверку транзисторов» 2.2.2 (2.2.2.1, 2.2.2.2, 2.2.2.3, 2.2.2.4), через «нечетную четверку транзисторов» 2.1.1 (2.1.1.1, 2.1.1.2, 2.1.1.3, 2.1.1.4), через инвертор 4, на выходе которого устанавливается логическая единица, поскольку на вход поступает ноль - и на выходе 7 формируется логическая единица, то есть 0⊕1⊕1⊕1=1.

3) Режим вычисления в случае отказов и сбоев

Предполагается, что на входах 6 настройки присутствует правильная информация и она, в случае отказов и сбоев, защищена от искажений средствами, внешними по отношению к предлагаемому устройству.

Тогда при отказах, сбоях одного транзистора, например третьего («становится» константой 1 - постоянно открыт), в подсхеме подключения напряжения питания каждого инвертора в группе 2n инверторов настройки 3 за счет реализации в ней функции, толерантной к константным или инверсным отказам одного транзистора, функция подсхемы не меняется:

где x - переменные состояния основного 1 и дополнительных 2, 3, 4 транзисторов n-МОП, которые должны быть равны, но третий транзистор отказал. То есть напряжение питания будет подключено правильно.

То же происходит и в случае отказа, например, второго транзистора («становится» равным 0 - постоянно закрыт) в подсхеме подключения шины «Ноль вольт»:

где y - переменные состояния основного 1 и дополнительных 2, 3, 4 транзисторов p-МОП, которые должны быть равны, но второй транзистор отказал. То есть шина «Ноль вольт» будет подключена правильно.

Таким образом, на выходах инверторов в группе 2n инверторов настройки 3 даже при описанных отказах транзисторов будет правильная информация.

Аналогично вышеописанному сохранится правильная информация при указанных отказах и на выходах инверторов группы n инверторов переменных 1, и на выходе выходного инвертора 4.

При отказах одного транзистора в «четверках транзисторов» передача информации через эту четверку все равно произойдет, и при этом правильно.

Так, в рассмотренном выше примере, если в «четверке» (2.1.1.1-В1, 2.1.1.2-В2, 2.1.1.3-В3, 2.1.1.4-В4) возникнет сбой передающего транзистора 2.1.1.4 (третьего дополнительного передающего транзистора, обозначенного как В4, - допустим, он изменит свое состояние), то это не приведет к изменению функции:

Аналогично не произойдет изменения функций (1), (2) при соответствующих сбоях соответствующих транзисторов, то есть при инверсии соответствующих переменных.

Аналогично не произойдет изменения функции (5) при описанных выше константных отказах транзисторов.

4) Режим ограниченной функциональности

Режим задается при обнаружении по результатам тестирования большего, чем допустимое, количества отказов. При этом не допускается полного отказа (более одного отказа в схеме подключения напряжения питания и более одного отказа в схеме подключения шины «Ноль вольт») выходного инвертора 4.

В остальных случаях возможно использование «половинного» устройства - работоспособной половины, четверти и т.д.

Это достигается постоянным сигналом на старшем входе из входов n переменных 5 и использованием устройства для реализации функций n-1 переменной. Тогда используется соответствующая половина входов настройки и транзисторов группы 2n инверторов настройки. Например, при работоспособной нижней половине транзисторов n групп передающих транзисторов 2 возможна настройка для реализации функции сложения по модулю два (исключающего ИЛИ) трех переменных (n=3) вместо четырех - табл.2:

При работоспособной верхней половине транзисторов n групп передающих транзисторов 2 - табл.3:

Оценка технико-экономической эффективности

В отличие от прототипа, в котором не допускается ни одного сбоя и/или отказа ни одного транзистора, в предлагаемом устройстве допускается отказ одного транзистора в каждой из подсхем подключения напряжения питания и/или подключения шины «Ноль вольт» - каждого инвертора в группе 2n инверторов настройки 3 - всего 2·2n=2n+1 отказов, в каждом инверторе группы n инверторов переменных 1 - всего 2n отказов, выходном инверторе 4 - всего 2 отказа, допускается отказ одного транзистора в каждой «четверке транзисторов» - всего 2n+1-2 отказ.

Всего в предлагаемом устройстве допускается  отказ.

отказ.

Сравним предлагаемое устройство и прототип по вероятности безотказной работы с учетом экспоненциальной модели отказов (сбоев).

Оценим сложность прототипа. С учетом инверторов 1 по входам переменных, в каждом из которых 2 транзистора (2n), выходного инвертора 4 (в котором 2 транзистора), инверторов (в каждом из которых 2 транзистора) в группе 2n инверторов настройки 3 получим всего транзисторов в прототипе:

Поэтому вероятность безотказной работы прототипа с учетом экспоненциальной модели отказов (сбоев) и интенсивности отказов λ одного транзистора описывается выражением:

Сложность предлагаемого устройства в 4 раза больше:

Вероятность безотказной работы предлагаемого устройства с учетом экспоненциальной модели отказов (сбоев) и интенсивности отказов λ одного транзистора и в связи с вышеприведенным обоснованием описывается выражением:

На фиг.2 изображены графики изменения вероятности безотказной работы прототипа (Р0) и предлагаемого устройства (Р3) с учетом экспоненциальной модели отказов (сбоев) и интенсивности отказов одного транзистора λ=10-5 при n=4.

На фиг.3 изображены графики изменения вероятности безотказной работы прототипа (Р0) и предлагаемого устройства (Р3) с учетом экспоненциальной модели отказов (сбоев) и интенсивности отказов одного транзистора λ=10-4 при n=5.

Покажем, что предлагаемое устройство обеспечивает выигрыш в вероятности безотказной работы даже по сравнению с троированным прототипом:

Для троирования прототипа с одним мажоритарным элементом (элементом голосования по большинству голосов), на который необходимо 24 транзистора, получим вероятность:

Для троирования с тремя мажоритарами с целью предотвращения фатальных отказов в самом мажоритаре:

На фиг.4 изображены графики изменения вероятности безотказной работы троированного прототипа (Р1), троированного прототипа с тремя мажоритарами (Р2) и предлагаемого устройства (Р3) с учетом экспоненциальной модели отказов (сбоев) и интенсивности отказов одного транзистора λ=10-5 при n=5.

Таким образом, по вероятности безотказной работы предлагаемое устройство выигрывает не только по сравнению с прототипом, но даже и по сравнению с троированным прототипом с тремя мажоритарами.

Достижение технического результата изобретения подтверждается приведенными оценками.

Программируемое логическое устройство, содержащее группу n инверторов переменных, n групп, n - число входных переменных, основных передающих транзисторов по 2, i=1, n транзисторов в группе, группу 2 инверторов настройки, выходной инвертор, входы n переменных, 2 входы настройки, выход устройства, причем входы настройки подключены ко входам соответствующих инверторов из группы 2 инверторов настройки, входы i-x инверторов подключены к соответствующим к i-м входам входов n переменных, затвор каждого четного транзистора i-й группы из n групп передающих транзисторов подключен к i-му входу входов n переменных, затвор каждого нечетного транзистора i-й группы из n групп передающих транзисторов подключен к выходу i-го инвертора группы n инверторов переменных, входы которых подключены к i-му входу входов n переменных, стоки четных и нечетных - двух передающих транзисторов первой группы - объединены и подключены ко входу выходного инвертора, выход которого является выходом устройства, каждый инвертор из группы 2 инверторов настройки, группы n инверторов переменных, выходной инвертор - содержит основной транзистор n-МОП, основной транзистор р-МОП, вход напряжения питания, вход «Ноль вольт», вход инвертора, выход инвертора, причем затворы основных транзисторов n-МОП и р-МОП объединены и являются входом инвертора, сток основного транзистора n-МОП подключен ко входу напряжения питания, сток основного транзистора р-МОП подключен к выходу инвертора, отличающееся тем, что дополнительно введены 2-1 подгрупп дополнительных передающих транзисторов для каждого основного четного и нечетного транзистора n групп передающих транзисторов, состоящие из трех транзисторов, причем затворы дополнительных передающих транзисторов 1-й подгруппы 2.1 объединены и подключены к затвору соответствующего четного или нечетного основного транзистора в 1 группе передающих транзисторов, сток первого дополнительного транзистора в каждой из подгрупп дополнительных передающих транзисторов подключен к стоку соответствующего основного транзистора, исток первого дополнительного транзистора подключен к истоку основного транзистора и стокам второго и третьего дополнительных транзисторов, истоки которых объединены и подключены к стокам объединенных четных и нечетных передающих транзисторов 2-й группы, транзисторы j-х подгрупп 2.j, j=2…2-1 соединяются аналогично, затворы дополнительных передающих транзисторов объединены и подключены к затвору соответствующего четного или нечетного основного транзистора в n группах передающих транзисторов, по 2, i=1, n транзисторов в группе, где n - число входных переменных, сток первого дополнительного транзистора в каждой из подгрупп дополнительных передающих транзисторов подключен к стоку соответствующего основного транзистора, исток первого дополнительного транзистора подключен к истоку основного транзистора и стокам второго и третьего дополнительных транзисторов, истоки которых объединены и подключены к стокам объединенных четных и нечетных передающих транзисторов n+1-й группы, объединенные истоки второго и третьего дополнительных транзисторов последней группы 2.n передающих транзисторов подключены к выходам соответствующих инверторов из группы 2 инверторов настройки, каждый инвертор из группы 2 инверторов настройки, группы n инверторов переменных, выходной инвертор содержит три дополнительных транзистора n-МОП и три дополнительных транзистора р-МОП, причем затворы всех дополнительных транзисторов n-МОП и трех дополнительных транзисторов р-МОП объединены и подключены ко входу инвертора, исток первого дополнительного транзистора р-МОП подключен ко входу «Ноль вольт» и к истоку третьего дополнительного транзистора р-МОП, сток первого дополнительного транзистора р-МОП подключен к истоку основного транзистора р-МОП, сток второго дополнительного транзистора р-МОП подключен к истоку третьего дополнительного транзистора р-МОП, сток которого подключен к выходу инвертора, исток первого дополнительного транзистора n-МОП подключен к выходу инвертора, а сток первого дополнительного транзистора n-МОП подключен к истоку основного транзистора n-МОП, исток второго дополнительного транзистора n-МОП подключен к выходу инвертора, сток второго дополнительного транзистора n-МОП подключен к истоку третьего дополнительного транзистора n-МОП и стоку основного транзистора n-МОП, сток третьего дополнительного транзистора n-МОП подключен ко входу напряжения питания инвертора.