Результат интеллектуальной деятельности: ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО

Вид РИД

Изобретение

Изобретение относится к вычислительной технике и может быть использовано для вычисления систем логических функций в программируемых логических интегральных схемах (ПЛИС).

Известно программируемое логическое устройство, содержащее первую, вторую и третью группы D-триггеров количеством по m·2n (n - число входных переменных, m - число выходных функций), третью группу D-триггеров количеством 2(n-1)m, группу m(n-1) элементов И, счетчик, группу m·2n элементов И с тремя состояниями на выходе, дешифратор, группу m(n-1) элементов ИЛИ, вторую группу m·2n элементов И с тремя состояниями на выходе и m блоков вычисления функций, каждый блок вычисления функций содержит группу 4·2n элементов И с тремя состояниями на выходе, два D-триггера, Т-триггер, RS-триггер фиксации импульса, пять элементов ИЛИ, три элемента И, четыре инвертора, n групп элементов 2·2 НЕ-И-ИЛИ (в каждую i-ю группу входит 2n-1 элементов, i=1, n), элемент задержки, дополнительную группу элементов И с тремя состояниями на выходе (патент РФ №2146840 от 20.03.2000, кл. G11C 17/00, G06F 7/00).

Недостатком известного устройства являются высокие аппаратурные затраты, выраженные в количестве транзисторов, на реализацию логической функции в программируемых логических интегральных схемах (ПЛИС).

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является программируемое логическое устройство, содержащее группу n инверторов, n групп передающих транзисторов (n - число входных переменных) по 2i, i=1, n транзисторов в группе, группу 2n инверторов настройки, выходной инвертор, входы n переменных, группу 2n входов настройки, выход устройства,

причем затвор каждого нечетного транзистора i-й группы передающих транзисторов i=1, n подключен к выходу i-го инвертора группы n инверторов, затвор каждого четного транзистора i-й группы передающих транзисторов подключен к i-му входу входов n переменных, истоки 2n транзисторов n-ой группы подключены к выходам инверторов группы 2n инверторов настройки, входы которых являются группой 2n входов настройки, стоки четных и нечетных транзисторов n-й группы объединены и подключены к истокам соответствующих 2n-1 транзисторов n-1-й группы, стоки которых объединены и подключены к истокам соответствующих 2n-2 транзисторов n-2-й группы и так далее, стоки двух последних транзисторов 1-й группы объединены и подключены ко входу выходного инвертора, выход которого является выходом устройства, входы n переменных подключены ко входам соответствующих инверторов из группы n инверторов (Строганов А., Цыбин С. Программируемая коммутация в ПЛИС: взгляд изнутри // Компоненты и технологии. - 2010. - № 11. С. 56-62 Рис. 9, 12 [Электронный ресурс]. - URL: http://www.kit-e.ru/articles/plis/2010_11_56.php 12.11.12 г.)

Недостатком известного устройства, принятого за прототип, является высокая временная сложность проверки работоспособности (диагностирования).

Это обусловлено следующими обстоятельствами. Технические средства прототипа ориентированы на реализацию в зависимости от настройки одной конкретной логической функции n переменных в совершенной дизъюнктивной нормальной форме (СДНФ). Поэтому для проверки работоспособности в общем случае требуется проверить активирование всех 2n цепочек передающих транзисторов, то есть необходимо 2n шагов (тактов). Все 2n наборов значений переменных для осуществления такой проверки надо фиксировать на соответствующих n входах устройства и оценивать выходную реакцию - реализуемую логическую функцию.

Кроме того, необходимо проверять реализацию всех функций - на это необходимо  тактов.

тактов.

В связи с этим требуется, по существу, полный перебор значений на входах устройства.

Задачей изобретения является обеспечение снижения временной сложности проверки работоспособности (диагностирования) путем введения режима «быстрого» диагностирования наряду с режимом обычного диагностирования.

Поставленная задача была решена за счет того, что в заявляемом устройстве, содержащем группу n инверторов переменных, n групп передающих транзисторов (n - число входных переменных) по 2i, i=1, n транзисторов в группе, группу 2n инверторов настройки, выходной инвертор, входы n переменных, 2n входов настройки, выход устройства,

причем затвор каждого четного транзистора i-й группы из n групп передающих транзисторов подключен к i-му входу входов n переменных, стоки четных и нечетных транзисторов n-ой группы объединены и подключены к истокам соответствующих 2n-1 транзисторов n-1-й группы, стоки которых объединены и подключены к истокам соответствующих 2n-2 транзисторов n-2-й группы и так далее, стоки двух последних транзисторов 1-й группы объединены и подключены ко входу выходного инвертора, выход которого является выходом устройства, входы n переменных подключены ко входам соответствующих инверторов из группы n инверторов,

дополнительно введены группа 2 n транзисторов переменных, группа 2n транзисторов отключения настройки, инвертор управления группой транзисторов переменных, транзистор управления тестом, вход задания сигнала, диагностические выходы, вход управления тестом,

причем истоки 2n транзисторов n-й группы количеством 2n являются диагностическими выходами устройства и подключены к стокам соответствующим из 2n транзисторов группы 2n транзисторов отключения настройки, истоки которых подключены к выходам соответствующих инверторов группы 2n инверторов настройки, входы которых являются группой 2n входов настройки, затворы транзисторов группы 2n транзисторов отключения настройки подключены к затворам нечетных транзисторов группы 2 n транзисторов переменных и к выходу инвертора управления группой транзисторов, а затворы четных транзисторов группы 2 n транзисторов переменных подключены ко входу управления тестом, входу инвертора управления группой транзисторов переменных, вход задания сигнала подключен к истоку транзистора управления тестом, сток которого подключен ко входу выходного инвертора, а затвор транзистора управления тестом подключен ко входу управления тестом.

Признаки прототипа, совпадающие с существенными признаками заявляемого изобретения, следующие:

содержит группу n инверторов переменных, n групп передающих транзисторов (n - число входных переменных) по 2i, i=1, n транзисторов в группе, группу 2n инверторов настройки, выходной инвертор, входы n переменных, 2n входов настройки, выход устройства.

Признаки заявляемого технического решения, отличительные от прототипа, следующие: содержит группу 2 n транзисторов переменных, группу 2n транзисторов отключения настройки, инвертор управления группой транзисторов переменных, транзистор управления тестом, вход задания сигнала, диагностические выходы, вход управления тестом.

Отличительные признаки в сочетании с известными позволяют снизить временную сложность проверки работоспособности (диагностирования) путем одновременной проверки всех транзисторов в n группах передающих транзисторов с помощью дополнительных транзисторов переменных, используя группу 2n транзисторов отключения настройки, инвертор управления группой транзисторов переменных, вход управления тестом, вход задания сигнала, диагностические выходы, вход управления тестом.

Введение группы 2 n транзисторов переменных позволяет обеспечить активировапие (установку в состояние логической единицы) затворов всех или отдельных транзисторов в n группах передающих транзисторов сигналами на входах n переменных.

Введение группы 2n транзисторов отключения настройки позволяет отключать выходы инверторов группы 2n инверторов настройки для оценки результатов подачи реверсного сигнала одновременно по всем транзисторам в n группах передающих транзисторов.

Введение инвертора управления группой транзисторов переменных позволяет блокировать выходы инверторов в группе n инверторов переменных для обеспечения «быстрого» диагностирования.

Введение транзистора управления тестом позволяет во время режима «быстрого» диагностирования подавать реверсный сигнал, проходящий по всем транзисторам в n группах передающих транзисторов со входа задания сигнала.

Введение входа задания сигнала позволяет подавать тестовый сигнал «единица» или «ноль» через транзистор управления тестом, который проходит по всем транзисторам в n группах передающих транзисторов.

Введение диагностических выходов позволяет обеспечить снятие выходной реакции на тестовые сигналы как в предлагаемом режиме «быстрого» диагностирования - для оценки прохождения теста по всем транзисторам в n группах передающих транзисторов, так и в режиме обычного диагностирования - для оценки работоспособности инверторов в группе 2n инверторов настройки.

Введение входа управления тестом позволяет переключать режимы тестирования с обычного (на входе управления тестом - «ноль») на «быстрое» диагностировние (на входе управления тестом - «единица»).

Изменение связей по сравнению с известным устройством обеспечивает реализацию как режима вычислений программируемых по входам настройки логических функций, так и диагностирование - обычное по дереву транзисторов - по одной из ветвей в n групп передающих транзисторов, так и «быстрое» диагностирование.

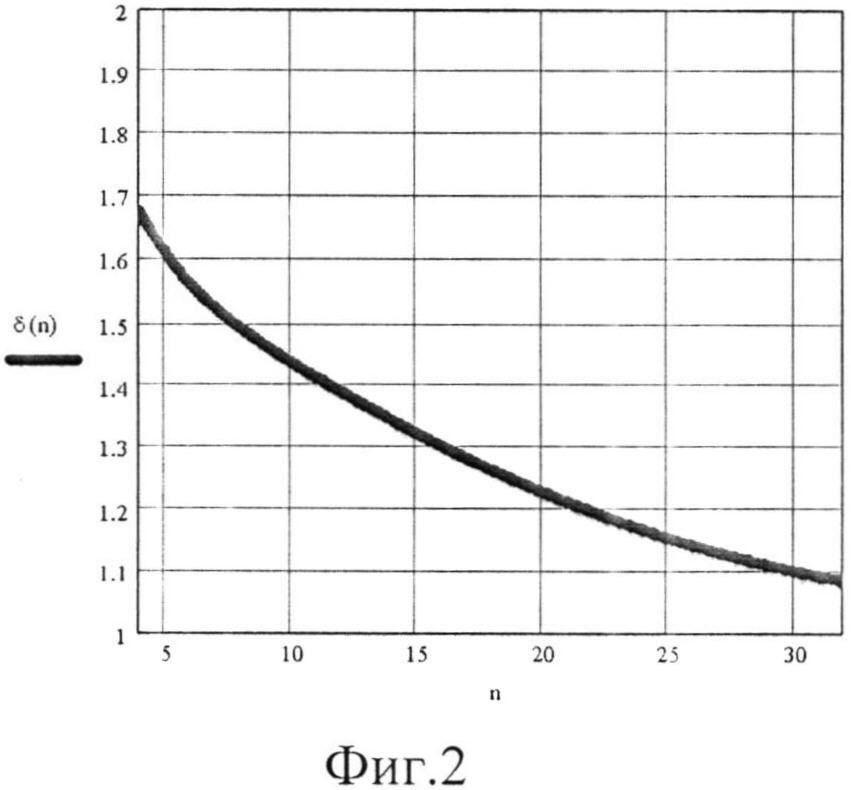

На Фиг. 1 изображена схема электрическая структурная программируемого логического устройства.

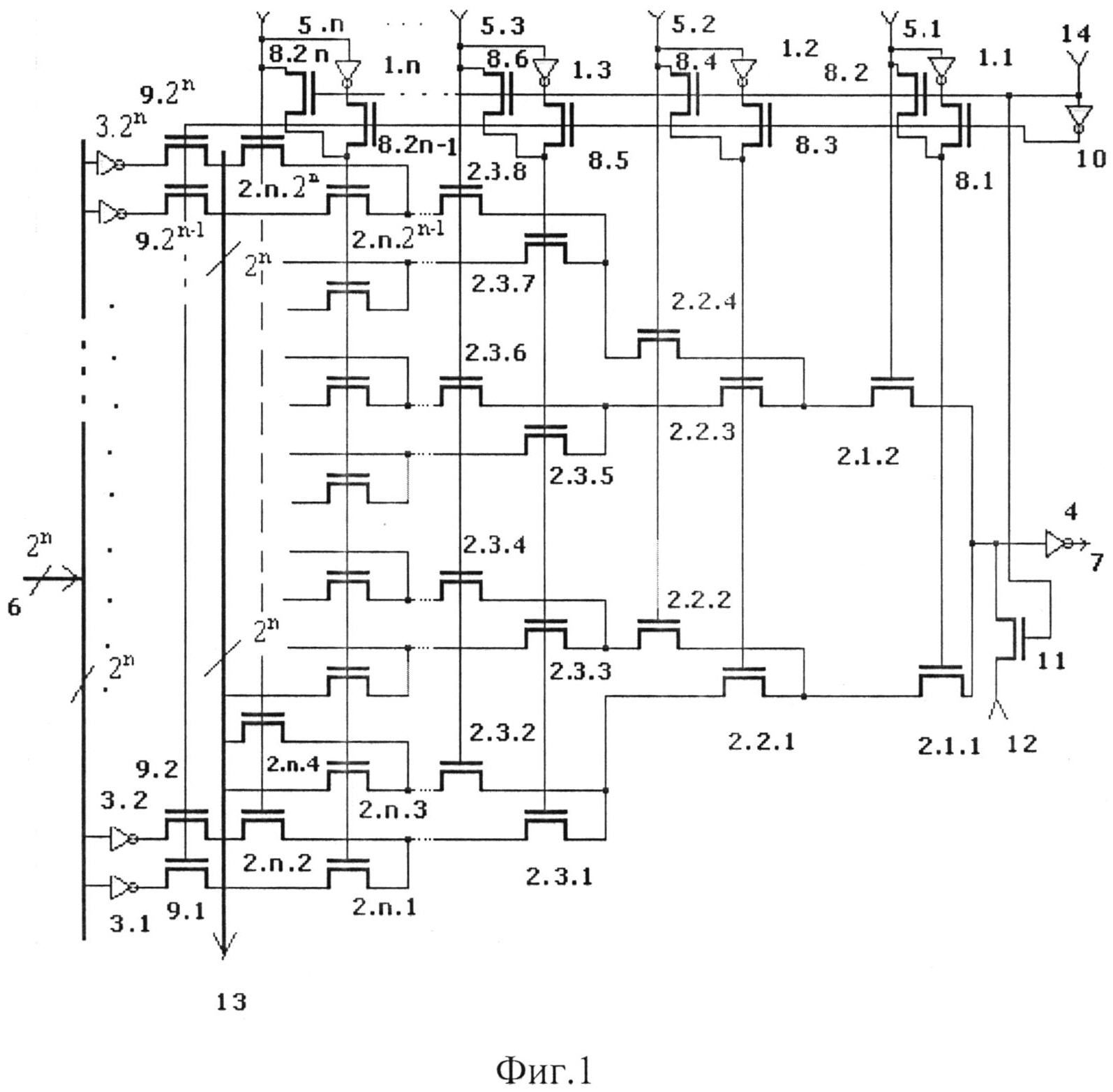

На Фиг. 2 представлен график изменения относительных аппаратных затрат в транзисторах программируемого логического устройства по сравнению с прототипом.

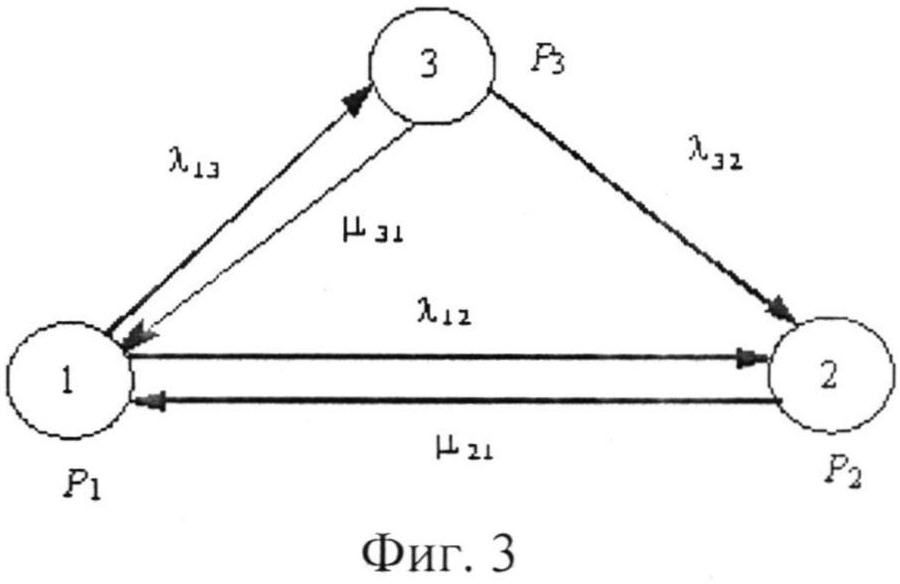

На Фиг. 3. изображен график Марковской цепи программируемого логического устройства.

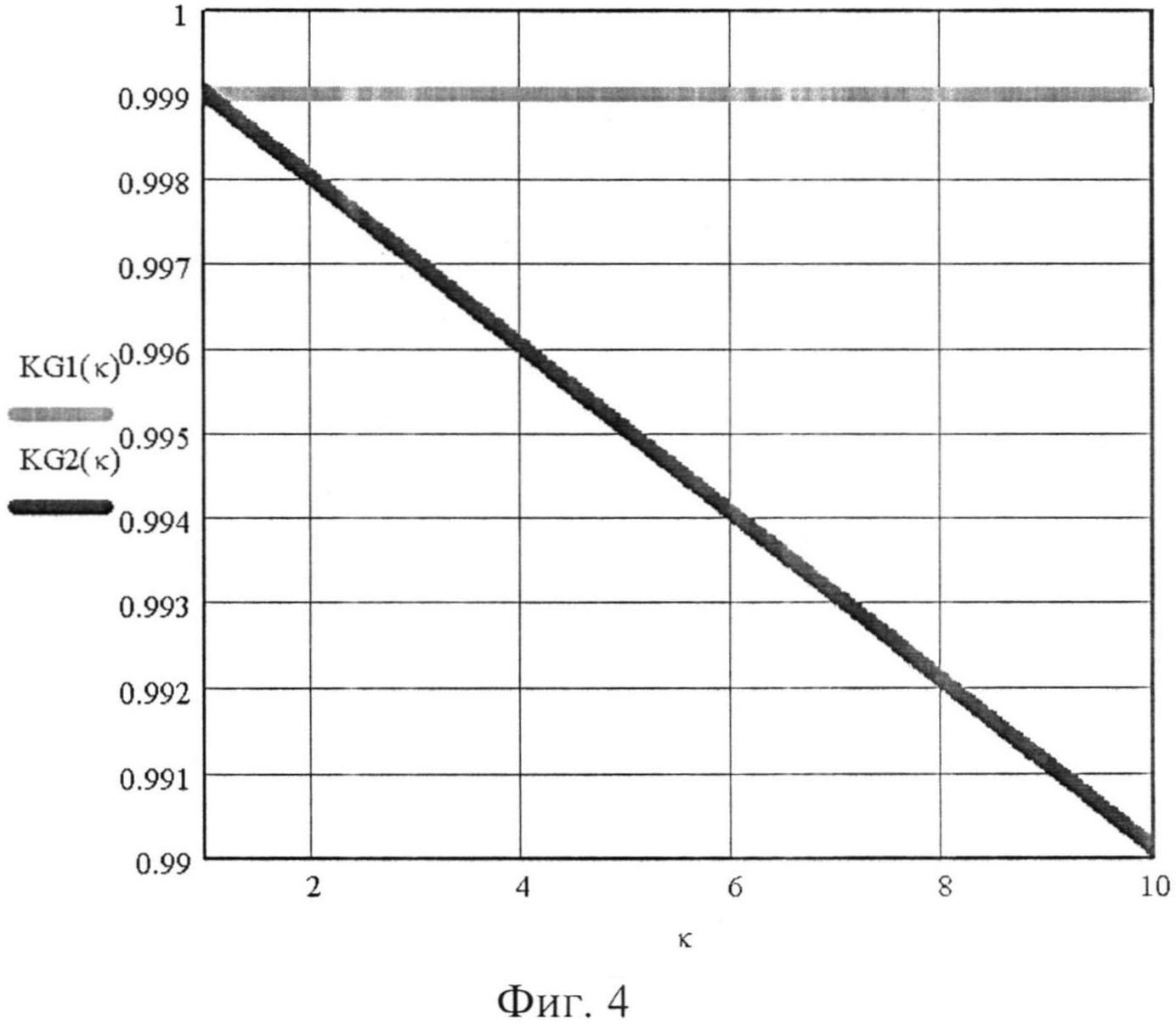

На Фиг 4. изображен график изменения коэффициента готовности прототипа KG2 в зависимости от увеличения времени k тестирования Т3 по сравнению с коэффициентом готовности предлагаемого устройства KG1 при λ=10-9; µ=10-3; ξ=1,7; Td=10-4; Т3=10-7.

Программируемое логическое устройство содержит группу n инверторов переменных 1, n групп передающих транзисторов 2 (n - число входных переменных) по 2i, i=1, n транзисторов в группе, группу 2n инверторов настройки 3, выходной инвертор 4, входы n переменных 5, 2n входов настройки 6, выход устройства 7, группу 2n транзисторов переменных 8, группу 2n транзисторов отключения настройки 9, инвертор 10 управления группой транзисторов переменных, транзистор управления тестом 11, вход задания сигнала 12, диагностические выходы 13, вход управления тестом 14.

Затвор каждого четного транзистора i-й группы 2.i из n групп передающих транзисторов 2 подключен к i-му входу входов n переменных 5.i.

Стоки четных и нечетных транзисторов n-й группы 2.n объединены и подключены к истокам соответствующих 2n-1 транзисторов n-1-й группы 2.n-1, стоки которых объединены и подключены к истокам соответствующих 2n-2 транзисторов n-2-й группы 2.n-2 и так далее, стоки двух последних транзисторов 1-й группы 2.1 объединены и подключены ко входу выходного инвертора 4.

Выход выходного инвертора 4 является выходом устройства 7.

Входы i-x инверторов группы n инверторов переменных 1.i подключены к соответствующим i-м входам входов n переменных 5.i.

Затвор каждого нечетного транзистора i-й группы 2.i передающих транзисторов 2 i=1,n подключен к объединенным истокам соответствующих нечетных и четных транзисторов группы 2 n транзисторов переменных 8, нечетный из которых подключен к выходу i-го инвертора группы n инверторов переменных 1.i, а четный из которых подключен к i-му входу входов n переменных 5.i.

Истоки 2n транзисторов n-й группы 2.n количеством 2n являются диагностическими выходами 13 устройства и подключены к стокам соответствующих 2n транзисторов отключения настройки 9, истоки которых подключены к выходам соответствующих инверторов группы 2n инверторов настройки 3, входы которых являются группой 2n входов настройки 6.

Затворы транзисторов группы 2n транзисторов отключения настройки 9 подключены к затворам нечетных транзисторов группы 2n транзисторов переменных 8 и к выходу инвертора 10 управления группой транзисторов.

Затворы четных транзисторов группы 2n транзисторов переменных 8 подключены ко входу управления тестом 14 и входу инвертора 10 управления группой транзисторов переменных.

Вход задания сигнала 12 подключен к истоку транзистора реверса 11, сток которого подключен ко входу выходного инвертора 4, а затвор транзистора реверса 11 подключен ко входу управления тестом 14.

Программируемое логическое устройство работает в следующих режимах:

1) программирование; 2) вычисление; 3) обычное тестирование; 4) «быстрое» тестирование.

Устройство может быть использовано и после обнаружения отказов предлагаемым образом - в режиме ограниченной функциональности.

1) Программирование. В этом режиме устройство работает аналогично прототипу. На входе управления тестом 14 установлен логический ноль, что приводит к активированию затворов нечетных транзисторов в группе 2n транзисторов переменных 8 через инвертор управления группой транзисторов переменных 10, затворов группы 2n транзисторов отключения настройки, причем четные транзисторы в группе 2n транзисторов переменных 8 отключены, отключен и транзистор управления тестом 11. При этом с помощью внешних по отношению к устройству технических средств на 2n входах настройки 6 устанавливаются логические уровни, соответствующие логической функции n переменных, которую необходимо вычислять (таблице истинности заданной логической функции n переменных, содержащей 2n строк). Так, дли реализации функции сложения по модулю два (исключающего ИЛИ) четырех переменных (n=4) х4⊕х3⊕х2⊕х1, где xi - сигнал на входах 5.4, 5.3, 5.2, 5.1 - на входах 6 (6.0…6.15) устанавливаются следующие логические уровни (Строганов А., Цыбин С. Программируемая коммутация в ПЛИС: взгляд изнутри // Компоненты и технологии. - 2010. - №11. С. 56-62 Рис. 9 [Электронный ресурс]. - URL:http://www.kit-e.ru/articles/plis/2010_11_56.php Дата обращения 12.01.13 г) - Табл. 1

На выходах инверторов группы 2n инверторов настройки 3 устанавливаются значения, инверсные логическим уровням, устанавливаемым на 2n входах настройки 6.

2) Вычисление. В этом режиме на входе управления тестом 14 установлен логический ноль, что приводит к активированию затворов нечетных транзисторов в группе 2n транзисторов переменных 8 через инвертор управления группой транзисторов переменных 10, затворов группы 2n транзисторов отключения настройки 9, причем четные транзисторы к группе 2 n транзисторов переменных 8 отключены, отключен и транзистор управления тестом 11. Поэтому устройство работает аналогично прототипу.

При поступлении на входы n переменных 5 с помощью внешних по отношению к устройству технических средств некоторого из 2n набора (табл. 1 - 5.4…5.1) активизируется одна из 2n цепочек в n группах 2 передающих транзисторов (четные транзисторы непосредственно с соответствующего входа n переменных 5, если он равен логической единице, нечетные - через соответствующий инвертор группы n инверторов переменных 1 и нечетный транзистор группы 2 n транзисторов переменных 8, если он равен нулю) с выхода соответствующего инвертора группы 2n инверторов настройки 3 через транзисторы группы 2n транзисторов отключения настройки 9, через выходной инвертор 4 на выход устройства 7.

Так, при поступлении на входы n переменных 5 набора 0101 (набор №5) «набирается» цепочка «четный транзистор» 2.4.6-2.3.3-2.2.2-2.1.1 со входа 6.5, на котором установлен логический ноль, через инвертор 3.6, через инвертор 4 - и на выходе 7 формируется логический ноль: 0⊕1⊕0⊕1=0.

3) Обычное тестирование. В этом режиме на входе управления тестом 14 установлен логический ноль, что приводит к активированию затворов нечетных транзисторов в группе 2n транзисторов переменных 8 через инвертор управления группой транзисторов переменных 10, затворов группы 2n транзисторов отключения настройки 9, причем четные транзисторы в группе 2n транзисторов переменных 8 отключены, отключен и транзистор управления тестом 11. Поэтому устройство работает аналогично прототипу.

При помощи внешних по отношению к устройству технических средств на 2n входах настройки 6 устанавливаются логические уровни, соответствующие некоторой тестовой логической функции n переменных, которую необходимо вычислять (таблице истинности заданной логической функции n переменных, содержащей 2n строк).

Далее на входы n переменных 5 при помощи внешних по отношению к устройству технических средств поочередно подаются все 2n наборов. Активизируются все 2n цепочек в n группах передающих транзисторов с выхода соответствующего инвертора группы 2n инверторов настройки 3, через группу 2n транзисторов отключения настройки 9, через выходной инвертор 4 на выход устройства 7, по которому внешние по отношению к устройству технические средства оценивают работоспособность устройства.

Тестовых функций в общем случае должно быть несколько для исключения возможного неправильного влияния различных наборов друг на друга как в группе 2n инверторов настройки 3, так и в n группах 2 передающих транзисторов (все нули, все единицы, чередование нулей и единиц и пр.). Поэтому в общем случае требуется больше, чем 2n тактов.

Состояние группы 2n инверторов настройки может контролироваться с помощью диагностических выходов 13.

4) «Быстрое» тестирование

В этом режиме на входе управления тестом 14 установлена логическая единица, что приводит к активированию затворов четных транзисторов в группе 2n транзисторов переменных 8, нечетные транзисторы в группе 2n транзисторов переменных 8 отключены, отключены и транзисторы группы 2n транзисторов отключения настройки 9. Активируется затвор транзистора управления тестом 11, через который со входа управления тестом поступает тестовый логический уровень.

Отключенные нечетные транзисторы в группе 2n транзисторов переменных 8 приводят к тому, что на нечетные транзисторы n групп передающих транзисторов 2 (n - число входных переменных) по 2i, i=1, n транзисторов в группе будет поступать одинаковый сигнал с соответствующего входа n входов переменных 5.

Отключенные транзисторы группы 2n транзисторов отключения настройки 9 отключают выходы инверторов группы 2n инверторов настройки 3 и на диагностических выходах 13 может наблюдаться состояние последней n-й группы из n групп передающих транзисторов 2 с помощью внешних по отношению к устройству технических средств.

На n входов переменных 5 устанавливаются логические единицы (например, 1111 для n=4), активирующие затворы всех транзисторов n групп передающих транзисторов 2 через четные транзисторы группы 2n транзисторов переменных.

При подаче с помощью внешних по отношению к устройству технических средств на вход задания сигнала 12 тестового сигнала «логическая единица» на диагностических выходах 13 с помощью внешних по отношению к устройству технических средств должны наблюдаться 2n логических единиц, а при подаче с помощью внешних по отношению к устройству технических средств на вход задания сигнала 12 тестового сигнала «логический ноль» на диагностических выходах 13 с помощью внешних по отношению к устройству технических средств должны наблюдаться 2n логических нулей при отсутствие отказов.

Для проверки отсутствия отказов типа «постоянная единица на затворе» в транзисторах n групп передающих транзисторов 2 на входы и переменных 5 может быть подано n наборов с одним нулем в одной из n позиций, например 1110, 1101, 1011, 0111 для n=4.

5) Режим ограниченной функциональности

Режим задается при обнаружении, как правило, одного отказа по результатам тестирования.

При обнаружении одного отказа в дереве передающих транзисторов n групп передающих транзисторов 2 или инверторов группы 2n инверторов настройки 3 возможно использование «половинного» устройства - работоспособной половины.

Это достигается постоянным сигналом на старшем входе из входов n переменных 5 и использованием устройства для реализации функций n-1 переменной. Тогда используется соответствующая половина входов настройки и транзисторов группы 2n инверторов настройки. Например, при работоспособной верхней половине транзисторов n групп передающих транзисторов 2 возможна настройка для реализации функции сложения по модулю два (исключающего ИЛИ) трех переменных (n=3) вместо четырех - Табл. 2.

При работоспособной нижней половине транзисторов n групп передающих транзисторов 2 - Табл. 3.

Такая настройка возможна также и при обнаружении отказов типа «постоянный ноль», «постоянная единица» по старшему входу 5.4.

При обнаружении дополнительного к вышеописанному отказу отказа по входу 5.3, либо в инверторе 1.3 группы n инверторов переменных относительно Табл. 2 необходимы следующие настройки - Табл. 4, 5.

При обнаружении дополнительного отказа по входу 5.2, либо в инверторе 1.2 группы n инверторов переменных относительно Табл. 2 необходимы следующие настройки - Табл. 6, 7.

При обнаружении дополнительного отказа по входу 5.1, либо в инверторе 1.1 группы n инверторов переменных относительно Табл. 3 необходимы следующие настройки - Табл. 8, 9.

Оценка технико-экономической эффективности

Технические средства прототипа в общем случае обеспечивают тестирование путем проверки реализации некоторой одной логической функции за Т2=2n шагов (тактов) с фиксацией на выходе 7 одного из 2n значений логической функции. Это соответствует экспоненциальной сложности тестирования.

В предлагаемом устройстве необходимо два такта для проверки прохождения по всем транзисторам групп 2 сигнала «логический ноль», «логическая единица» по диагностическим выходам 13.

Для проверки отсутствия отказа «постоянная единица» на затворах транзисторов групп 2 возможен дополнительный тест «бегущий ноль» по входам n переменных 5 - сложностью n.

Для проверки группы n инверторов переменных в режиме обычного тестирования также возможен дополнительный гест «бегущий ноль» по входам n переменных 5 - сложностью n.

В режиме обычного тестирования также могут быть проверено состояние группы 2n инверторов настройки по диагностическим выходам 13.

Таким образом, получаем тест линейной сложности:

Таким образом, снижение временной сложности проверки работоспособности (диагностирования) определяется выражением:

Так, при n=4 получаем:

При n=5 получаем:

При n=6 получаем:

При n=7 получаем:

Однако аппаратные затраты в предлагаемом устройстве выше, чем в прототипе.

Покажем, что положительный эффект снижения временной сложности диагностирования превосходит негативные последствия некоторого увеличения аппаратных затрат.

Аппаратные затраты прототипа в количестве транзисторов описываются выражением:

где 2n+1-2 транзисторов в n группах передающих транзисторов 2 (n - число входных переменных) но 2i, i=1, n транзисторов в группе, 2·2n транзисторов в группе 2n инверторов настройки 3 (два транзистора на инвертор), 2·n+2 транзисторов в группе n инверторов переменных и в выходном инверторе.

В предлагаемом устройстве дополнительно к (7) введено:

транзисторов, где 2n транзисторов в группе 2n транзисторов отключения настройки 9, 2·n транзисторов в группе 2n транзисторов переменных плюс инвертор управления группой транзисторов переменных (2 транзистора) плюс транзистор управления тестом.

Итого получаем в предлагаемом устройстве следующее количество транзисторов:

Тогда относительные аппаратные затраты в транзисторах на модификацию прототипа с целью «быстрого» диагностирования для различных n представляют собой выражение:

На Фиг. 2 представлен график изменения относительных аппаратных затрат в транзисторах для «быстрого» диагностирования при различных n.

Видим, что относительные аппаратные затраты уменьшаются с увеличением n и при очень больших n становятся меньше 10%.

Оценим показатель надежности - коэффициент готовности с помощью Марковской модели программируемого логического устройства с «быстрым» диагностированием.

Рассмотрим Марковскую модель программируемого логического устройства с «быстрым» диагностированием (Фиг. 3).

Вершина 1 - состояние работоспособности (вероятность его Р1), вершина 2 - состояние отказа (вероятность Р2), λ12 - интенсивность отказов, µ21 - интенсивность восстановления, вершина 3 - состояние тестирования-диагностирования (вероятность Р3), в которое осуществляется переход с интенсивностью

,

,

где Td - периодичность диагностирования,

,

,

где Т3 - время прохождения теста, λ32 - интенсивность отказов во время тестирования.

Пусть µ21 - интенсивность восстановления определяется, например, скоростью процедуры замены устройства резервным. Примем допущение о том, что λ12=λ32.

Получим решение соответствующей системы алгебраических уравнений Колмогорова для установившегося режима:

В чем выражается «быстрота»? В уменьшении Т3 - времени прохождения теста, то есть в увеличении  . Какой ценой? Ценой увеличения λ12=λ32.

. Какой ценой? Ценой увеличения λ12=λ32.

Необходимо установить, приведет ли такой подход к увеличению коэффициента готовности KГ=P1? Получим коэффициент готовности KГ=P1(λ,µ).

Выразим KГ=Р1 из второго уравнения через P2, P3:

Далее, из третьего уравнения:

Из четвертого получим:

То есть:

Выражаем KГ=P1(λ, µ):

,

,

.

.

Таким образом, получаем:

С учетом λ12=λ32=λ, µ21=µ получим коэффициент готовности:

Учтем увеличение времени тестирования Т3 у прототипа в k раз:

Учтем некоторое увеличение интенсивности отказов при введении дополнительной аппаратуры у предлагаемого устройства:

На Фиг. 4 изображены графики для некоторых значений λ, µ, ξ, Td, T3 в зависимости от k.

Видим, что 70% ускорение диагностирования (ξ=1,7) обеспечивает больший коэффициент готовности даже при 70% увеличении интенсивности отказов (k).

Достижение технического результата изобретения подтверждается приведенными оценками.

Программируемое логическое устройство, содержащее группу n инверторов переменных, n групп передающих транзисторов (n - число входных переменных) по 2, i=1, n транзисторов в группе, группу 2 инверторов настройки, выходной инвертор, входы n переменных, 2 входов настройки, выход устройства, причем затвор каждого четного транзистора i-й группы из n групп передающих транзисторов подключен к i-му входу входов n переменных, стоки четных и нечетных транзисторов n-ой группы объединены и подключены к истокам соответствующих 2 транзисторов n-1-й группы, стоки которых объединены и подключены к истокам соответствующих 2 транзисторов n-2-й группы, транзисторы в группах n-3, n-4…2 соединены аналогично, стоки двух последних транзисторов 1-й группы объединены и подключены ко входу выходного инвертора, выход которого является выходом устройства, входы n переменных подключены ко входам соответствующих инверторов из группы n инверторов, отличающееся тем, что в него дополнительно введены группа 2n транзисторов переменных, группа 2 транзисторов отключения настройки, инвертор управления группой транзисторов переменных, транзистор управления тестом, вход задания сигнала, диагностические выходы, вход управления тестом, причем истоки 2 транзисторов n-й группы количеством 2 являются диагностическими выходами устройства и подключены к стокам соответствующим из 2 транзисторов группы 2 транзисторов отключения настройки, истоки которых подключены к выходам соответствующих инверторов группы 2 инверторов настройки, входы которых являются группой 2 входов настройки, затворы транзисторов группы 2 транзисторов отключения настройки подключены к затворам нечетных транзисторов группы 2n транзисторов переменных и к выходу инвертора управления группой транзисторов, а затворы четных транзисторов группы 2n транзисторов переменных подключены ко входу управления тестом, входу инвертора управления группой транзисторов переменных, вход задания сигнала подключен к истоку транзистора управления тестом, сток которого подключен ко входу выходного инвертора, а затвор транзистора управления тестом подключен ко входу управления тестом.