Результат интеллектуальной деятельности: СПОСОБ ЭЛЕКТРОТЕРМОТРЕНИРОВКИ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ

Вид РИД

Изобретение

Изобретение относится к области микроэлектроники и может быть использовано для повышения качества электротермотренировки интегральных микросхем. Сущность изобретения состоит в новом способе электрической активации микросхемы, обеспечивающем переключение максимального числа компонентов.

Известны способы активации компонентов микросхем (Патенты США 5986917, 6352868 др.), в соответствии с которыми в составе микросхемы размещаются дополнительные функциональные узлы, назначение которых состоит в обеспечении возможности доступа к максимальному числу транзисторов с целью их активации во время ЭТТ. Применение данных способов приводит к усложнению устройства, увеличению площади кристалла и связанных с ней технических и стоимостных характеристик изделия.

Известен способ электротермотренировки интегральных микросхем, приведенный в авторском свидетельстве SU 1449950 A1, G01R 31/28, в соответствии с которым на входы микросхемы подаются псевдослучайные последовательности импульсов, выводы питания подключаются к источнику импульсного испытательного воздействия. Потенциал входа ″земля″ остается неизменным. Недостаток способа заключается в неопределенности состояний внутренних узлов микросхемы из-за случайного характера переключения цепей.

Наиболее близким к заявляемому способу является способ проведения ЭТТ в условиях стрессового электрического воздействия на полупроводниковую память, описанный в патенте US 6445630 B2, G11C 7/00. В соответствии с данным способом импульсные испытательные воздействия подаются на управляющие входы микросхемы и вход питания. Потенциал входа ″земли″ устанавливается постоянным. В зависимости от сочетания фаз указанных импульсных воздействий обеспечивается переключение элементов микросхемы.

Недостаток приведенного способа воздействия на компоненты тренируемой микросхемы состоит в узкой области применения, ограниченной комбинационной логикой. Тактируемые триггерные элементы, ячейки памяти запоминающих устройств, конечные автоматы устанавливаются случайным образом в неопределенные внутренние состояния, не изменяющиеся во времени.

Таким образом, неопределенное количество элементов микросхемы (транзисторов) не подвергается тренировке в полном объеме, что снижает эффективность решения задачи повышения надежности выпускаемых изделий.

Целью настоящего изобретения является создание способа электрического воздействия на микросхему при проведении электротермотренировки, обеспечивающего переключение всех узлов микросхемы. Технический результат, получаемый при использовании данного способа, состоит в повышении надежности микросхем за счет увеличения количества элементов, подвергшихся стрессовому воздействию во время проведения ЭТТ.

Поставленная цель достигается тем, что микросхема помещается в условия повышенной температуры окружающей среды, на управляющие входы микросхемы, на входы питания, в том числе, и на входы ″земля″ подается последовательность сигналов, фазовые соотношения которых обеспечивают установку внутренних узлов микросхемы в требуемые состояния.

Сущность способа раскрывается на примере микропроцессорных интегральных схем, изготавливаемых по КМДП технологии.

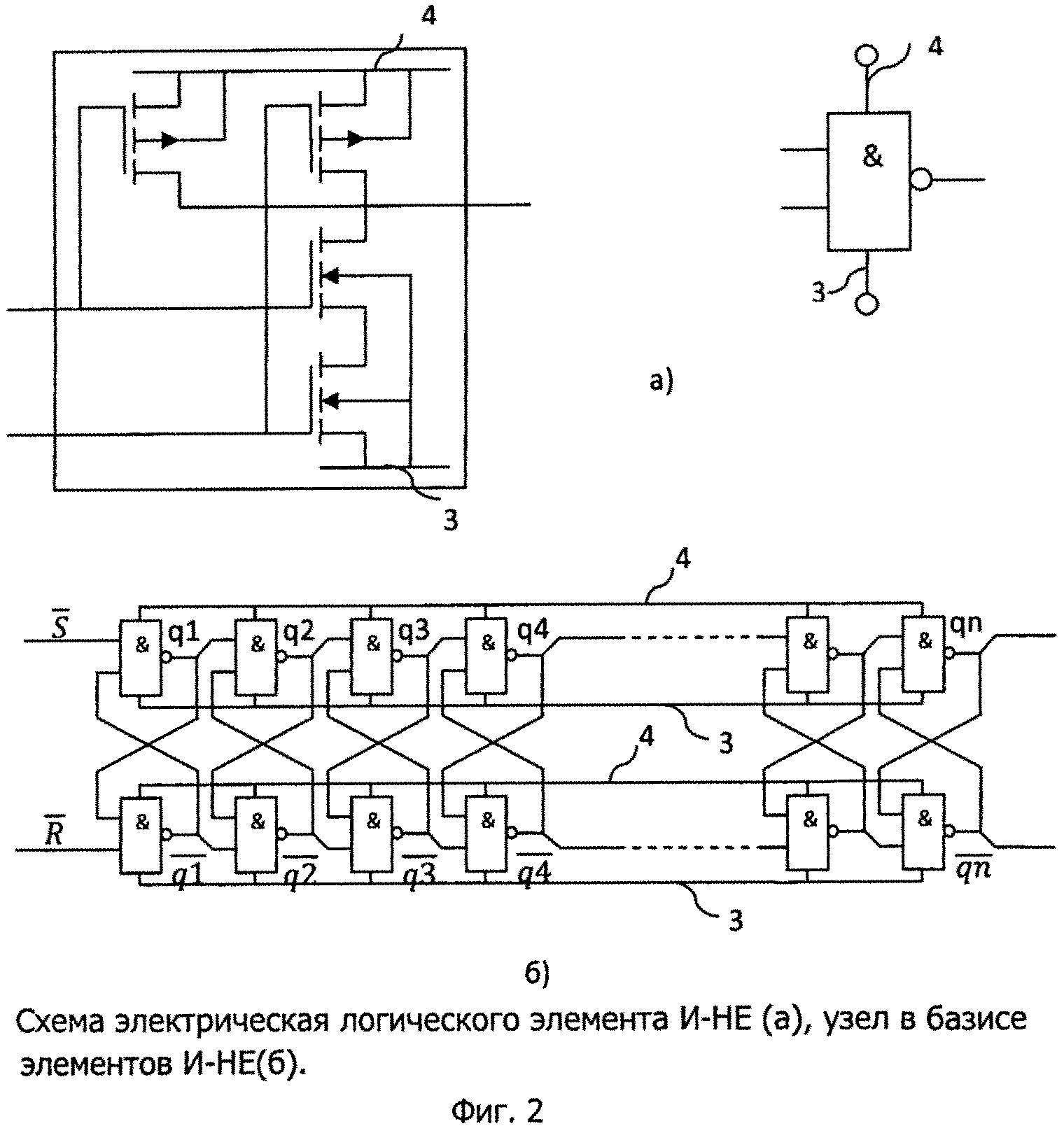

Базовым элементом цифровой интегральной микросхемы является инвертор, схема и диаграмма работы которого приведена на фиг.1. Инвертор содержит два МДП (Металл-Диэлектрик-Полупроводник) - транзистора p- и n-типа соответственно 1 и 2. Инвертор имеет первую шину питания 3, вторую шину питания 4, на которые в рабочем режиме работы подаются низкий (земля) и высокий (+ питание) потенциалы соответственно. А также управляющий вход 5 и инверсный выход 6.

Уровню ″лог.1″ на управляющем входе 5 инвертора соответствует закрытое состояние транзистора p-типа 1 и открытое состояние транзистора n-типа 2, формирующего на выходной шине 6 уровень низкого потенциала шины 3 ″лог.0″. Аналогично, при воздействии на его управляющий вход 5 уровня ″лог.0″ - на выходе 6 инвертора будет формироваться уровень высокого потенциала шины 4 ″лог.1″ открытым транзистором p-типа 1. Очевидно, что для узлов микросхемы, построенных с использованием только инверторов без обратных связей, применение известного способа активации оправдано и позволяет в полном объеме проводить тренировку всех транзисторов.

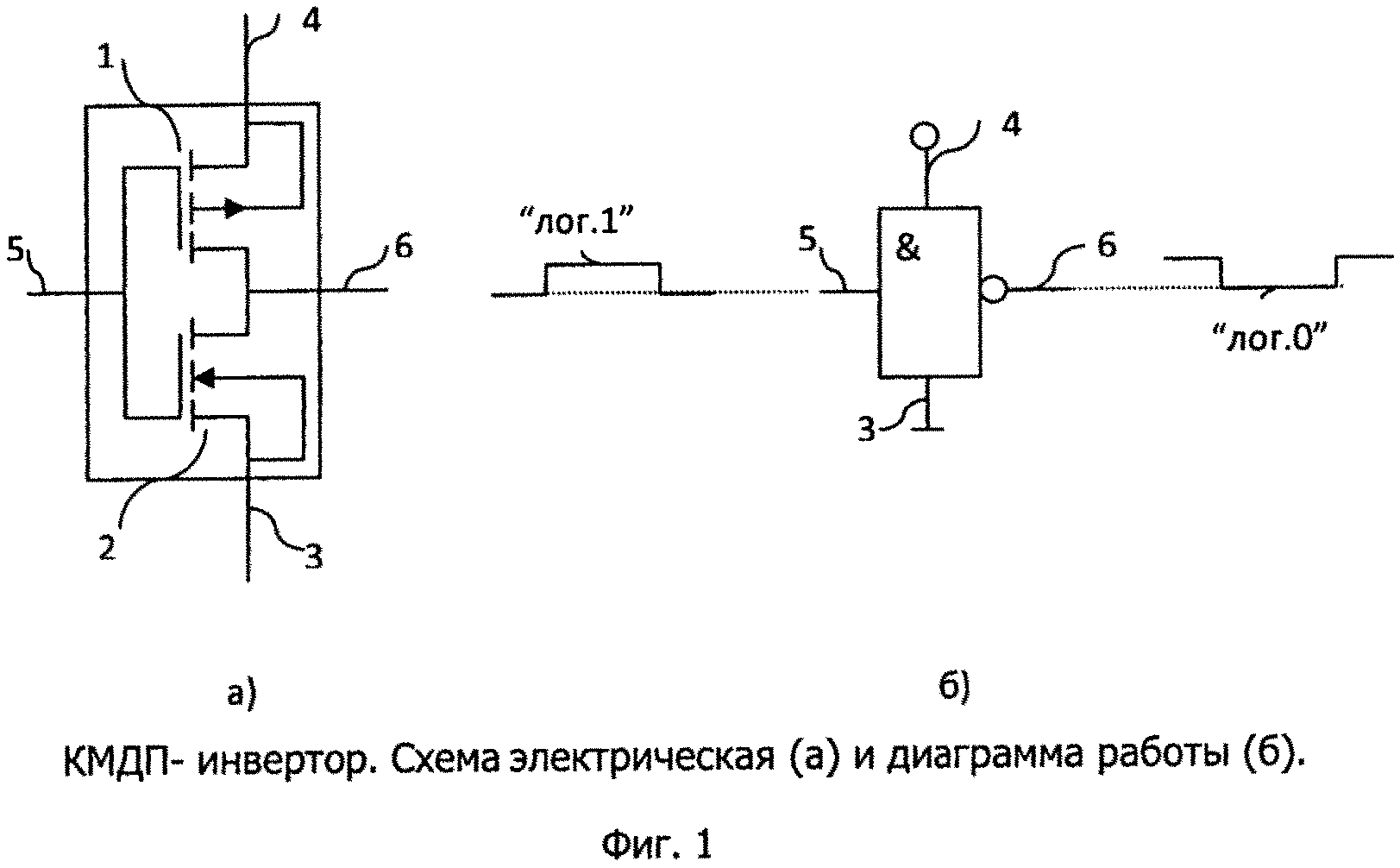

В случае, когда в состав интегральной микросхемы входят узлы на многовходовых логических элементах с обратными связями, элементы памяти, запоминающие устройства и т.п., применение известного способа становиться неэффективным. Снижение эффективности иллюстрируется на примере анализа поведения простейшего узла с обратными связями, реализованного в базисе элементов И-НЕ, схема которого изображена на фиг.2.

Схема б) содержит последовательную цепь R-S-триггеров, построенных на двухвходовых вентилях И-НЕ. На входы установки  ,

,  и вход шины питания 4 в соответствии с известным способом подается последовательность импульсов. Физически это может выглядеть, как подсоединение указанных входов к генератору импульсных последовательностей, общая шина которого, в свою очередь соединена с входом ″земля″ 3 устройства.

и вход шины питания 4 в соответствии с известным способом подается последовательность импульсов. Физически это может выглядеть, как подсоединение указанных входов к генератору импульсных последовательностей, общая шина которого, в свою очередь соединена с входом ″земля″ 3 устройства.

При воздействии на входы  и

и  импульсной последовательности при неизменном потенциале шины питания 4, прямые выходы qi и инверсные

импульсной последовательности при неизменном потенциале шины питания 4, прямые выходы qi и инверсные  находятся в неопределенных состояниях, не меняющихся в процессе электротермотренировки. Отсутствие событий переходов между логическими состояниями ″лог.0″ и ″лог.1″ означает исключение из процесса соответствующих элементов микросхемы. Изменением уровня потенциала питания 4 также нельзя добиться определенности внутренних состояний прямых qi и инверсных выходов

находятся в неопределенных состояниях, не меняющихся в процессе электротермотренировки. Отсутствие событий переходов между логическими состояниями ″лог.0″ и ″лог.1″ означает исключение из процесса соответствующих элементов микросхемы. Изменением уровня потенциала питания 4 также нельзя добиться определенности внутренних состояний прямых qi и инверсных выходов  и, следовательно, нельзя инициировать требуемые переключения.

и, следовательно, нельзя инициировать требуемые переключения.

Очевидно, что данный способ активации тем более не применим для больших интегральных схем со сложной функциональной организацией.

Целью настоящего изобретения является создание способа электрической активации микросхем, обеспечивающего полное прямое ″0-1″ и обратное ″1-0″ переключения всех внутренних узлов.

Технический результат, достигаемый при реализации изобретения, заключается в повышении надежности микросхем в результате увеличения количества элементов микросхемы, подвергающихся тренировке.

Поставленная цель достигается тем, что на микросхему подается импульсная последовательность испытательных воздействий, обеспечивающая полную определенность внутренних состояний микросхемы и переходов между логическими уровнями ″лог.0″ и ″лог.1″.

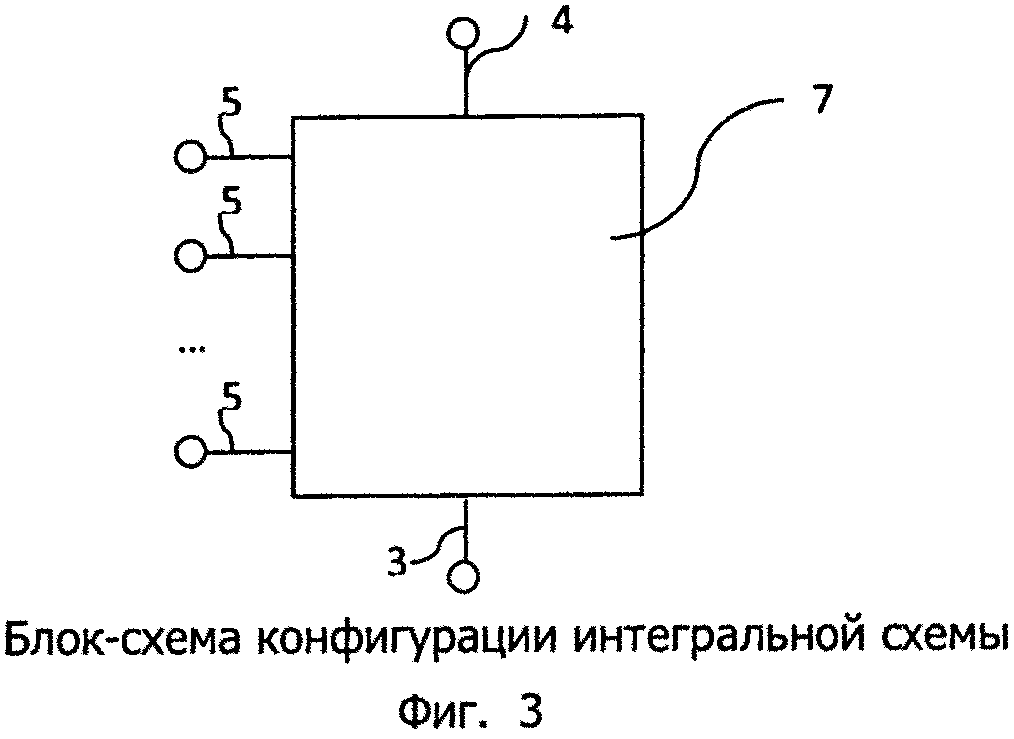

На фиг.3 приведена блок-схема конфигурации интегральной схемы 7 с управляющими входами 5, входами ″земля″ 3 и питания 4.

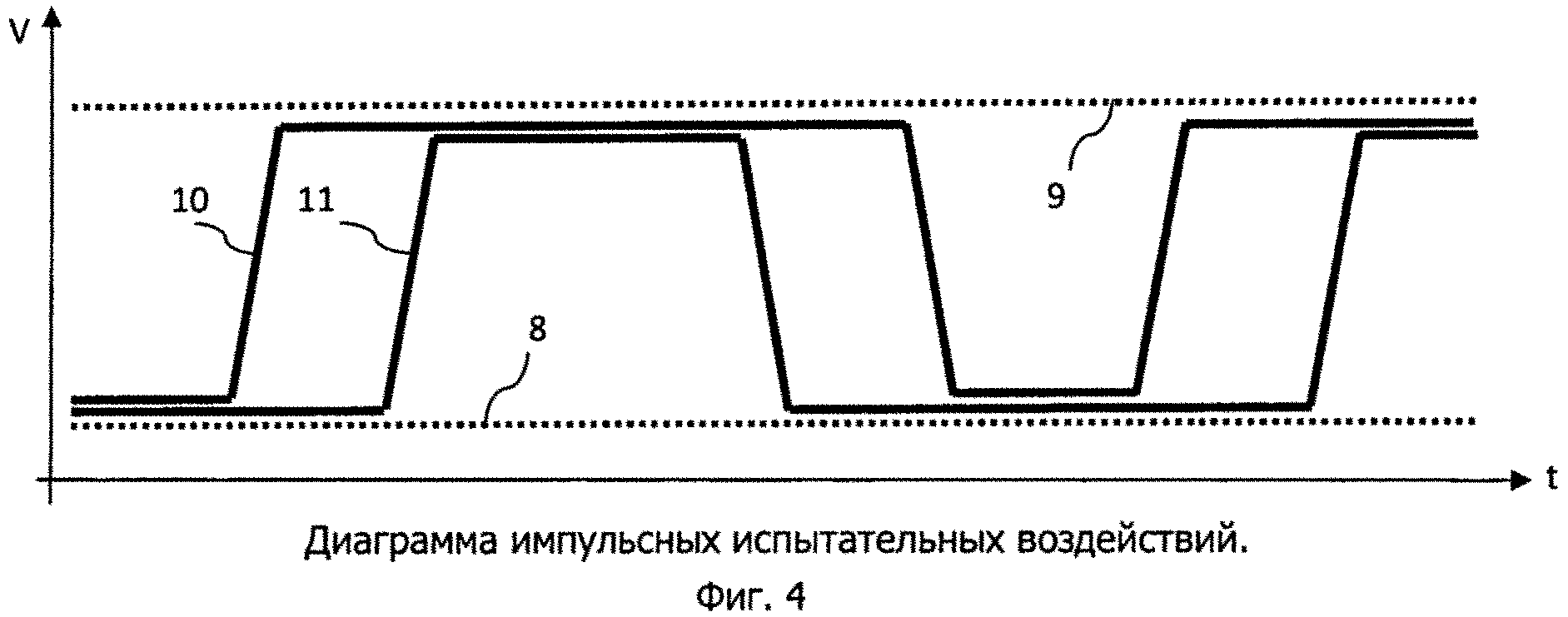

На фиг.4 приведена диаграмма импульсных испытательных воздействий, обеспечивающих получение технического результата в соответствии с целью изобретения.

Первое испытательное воздействие 10 прикладывается к входу питания 4 микросхемы, второе 11 - к входу ″земля″ 3. Амплитуда их изменений находится в диапазоне уровней рабочих напряжений микросхемы, соответствующих ″земле″ 8 и питанию 9. На информационные и управляющие входы 5 микросхемы могут подаваться как испытательные воздействия 10, 11, так и фиксированные уровни ″земля″ 8, питание 9.

Диаграмма импульсных испытательных воздействий имеет три характерных режима, которые условно можно обозначить как режимы ″00″, ″01″, ″11″, соответствующие напряжениям, установленным на входах ″земля″ 3 и питания 4 микросхемы.

В режиме ″00″ потенциалы всех внутренних узлов микросхемы, очевидно, установлены в состояние с низким потенциалом ″лог.0″.

После перехода импульсных испытательных воздействий в режим ″01″, при котором к входу питания 4 прикладывается напряжение, соответствующее рабочему, внутренние узлы устанавливаются в логические состояния, определяемые конфигурацией схемы. Таким образом, достигается эффект переключения части внутренних узлов из состояний ″лог.0″ в состояния ″лог.1″.

Следующий за ним режим ″11″, при котором потенциал входа ″земля″ изменяется до рабочего уровня микросхемы, инициирует переключение состояний остальных узлов микросхемы в состояния ″лог.1″. Таким образом, достигается переключение всех внутренних узлов микросхемы из состояния ″лог.0″ в состояние ″лог.1.″

Далее следует переход в режим ″01″. При этом часть узлов не меняет своего состояния, тогда как остальные переходят в ″лог.0″. Следует заметить, что множество новых состояний в текущем режиме может отличаться от множества состояний в предыдущем аналогичном режиме.

Переход в режим ″00″ инициирует процесс переключения остальных внутренних узлов микросхемы в состояния ″лог.0″, тем самым завершая процесс обратного переключения всех узлов.

Таким образом, периодическое импульсное воздействие рассмотренного вида обеспечивает соответствующие циклические изменения состояний узлов микросхемы. При этом меняющиеся потенциалы внутренних узлов не выходят за рамки допустимых рабочих потенциалов в любой момент времени. Это означает, очевидно, что переходы между состояниями осуществляются элементами микросхемы в режимах, подобных режимам работы при их штатной эксплуатации.

Способ электротермотренировки интегральных микросхем, заключающийся в том, что микросхему помещают в условия повышенной температуры окружающей среды, на выводы питания микросхемы подают последовательность импульсов напряжения, отличающийся тем, что на вывод “земля” микросхемы подают последовательность импульсов напряжения, фронт нарастания которых формируют с задержкой относительно фронта нарастания соответствующего импульса на выводе питания, а спад импульсов на выводе “земля” формируют до начала формирования спада соответствующего импульса на выводе питания.