Результат интеллектуальной деятельности: ЯЧЕЙКА УСТРОЙСТВА СЧИТЫВАНИЯ ФОТОПРИЕМНЫХ МАТРИЦ С АНАЛОГО-ЦИФРОВЫМ ПРЕОБРАЗОВАНИЕМ

Вид РИД

Изобретение

Техническое решение относится к области интегральной микроэлектроники и может быть использовано в системах приема и обработки оптической информации с многоэлементных приемников излучения.

Известна ячейка устройства считывания фотоприемных матриц с аналого-цифровым преобразованием (Matthew G. Brown, Justin Baker, Curtis Colonero, Joe Costa, Tom Gardner, Mike Kelly, Ken Schultz, Brian Tyrell, Jim Wey «Digital-pixel Focal Plane Array Development» Proc. of SPIE Vol.7608, p.p.76082H-1-76082H-10). В составе ячейки выполнены входной узел, счетчик, компаратор, узел вычитания заряда, схема памяти. В качестве интегрирующей емкости использована паразитная емкость затвора компаратора. Входной узел соединен с входом компаратора и с узлом вычитания заряда, который соединен со схемой памяти, с реверсивным счетчиком и выходной цепью компаратора.

Устройство разработано для двухцветной фотоприемной матрицы, выполнено на полупроводниковой подложке по технологии КМОП 90 нм. Рабочая температура близка к температуре жидкого азота. Для задания смещения на фотодиодах используется настраиваемая схема прямой инжекции. Вывод данных осуществляется параллельно. Принцип работы заключается в следующем: входной фототок интегрируется на маленькой паразитной емкости затвора компаратора до тех пор, пока напряжение на ней не достигнет порогового напряжения срабатывания компаратора. Частота выходных импульсов компаратора пропорциональна входному фототоку. Импульс, вырабатываемый компаратором, увеличивает значение счетчика и осуществляет сброс узла интегрирования. Затем акт интегрирования повторяется.

В качестве ближайшего аналога известна ячейка устройства считывания фотоприемных матриц с аналого-цифровым преобразованием (Fabrice Guellec, Arnaud Peizerat, Michaël Tchagaspanian, Eric de Boniol, Sylvette Bisotto, Laurent Mollard, Pierre Castelein, Jean-Paul Zanatta, Patrick Maillart, Michel Zécri, Jean-Christophe Peyrard «A 25µm pitch LWIR focal plane array with pixel-level 15-bit ADC providing high well capacity and targeting 2 mK NETD», Proc. of SPIE Vol.7660, p.p.76603T-1-76603T-10). В составе ячейки выполнены входной узел, интегрирующая емкость с одной из обкладок, закороченной на землю, счетчик, ключ, компаратор, N-разрядная схема памяти. Входной узел выполнен в составе транзистора. Счетчик выполнен N-разрядным. Транзистор истоком соединен с фотодиодом, стоком - со второй из обкладок интегрирующей емкости, ключом и первым входом компаратора, его затвор выполнен с возможностью подачи на него потенциала величиной, равной управляющему напряжению. Второй вход компаратора выполнен с возможностью подачи на него сигнала порогового напряжения. Выход компаратора соединен с ключом и входом N-разрядного счетчика. Ключ выполнен с возможностью реализации положений замыкания-размыкания, в положении замыкания с возможностью замыкания первого входа компаратора с выходом компаратора, в положении размыкания - с возможностью подачи на указанный вход компаратора напряжения сброса. N-разрядный выход счетчика соединен с N-разрядным входом N-разрядной схемы памяти. N-разрядный счетчик выполнен с возможностью подачи на него сигнала сброса, N-разрядная схема памяти выполнена с возможностью реализации режимов записи и считывания.

Устройство выполнено на полупроводниковой подложке.

Рабочая температура близка к температуре жидкого азота. Для задания смещения фотодиода используется схема прямой инжекции. Вывод данных осуществляется параллельно. Принцип работы заключается в следующем: ток фотодиода разряжает интегрирующую емкость до тех пор, пока напряжение на ней не достигнет некоторого порогового значения срабатывания компаратора. После этого компаратор вырабатывает «логическую 1», открывая тем самым ключ, через который происходит зарядка интегрирующей емкости до заданного значения. Далее акт интегрирования повторяется. N-разрядный счетчик считает число импульсов, выработанных компаратором. Число срабатываний компаратора из счетчика записывается схемой памяти. Используемый счетчик построен на динамических триггерах.

В приведенных технических решениях отсутствуют возможности снижения энергопотребления, снижения количества управляющих сигналов, реализации последовательного, упрощенного, вывода данных, миниатюризации ячейки. К причинам, препятствующим достижению ниже указанного технического результата, относится следующее.

В конструкции ячейки присутствует компаратор, схема памяти. Использование компаратора обуславливает повышенное энергопотребление. Кроме того, в конструкции присутствует счетчик, построенный на динамических триггерах. Реализация счетчика обуславливает наличие относительно большого количества транзисторов, поскольку включает необходимость транзисторов сброса, что препятствует миниатюризации ячейки и снижению количества управляющих сигналов. Использование схемы памяти предполагает параллельный вывод данных посредством многоразрядных шин, что усложняет вывод данных, делая сложной и дорогой топологию.

Достигаемым техническим результатом является:

- снижение энергопотребления;

- снижение количества управляющих сигналов;

- реализация последовательного, упрощенного, вывода данных;

- миниатюризация ячейки.

Технический результат достигается в ячейке устройства считывания фотоприемных матриц с аналого-цифровым преобразованием, содержащей входной узел, интегрирующую емкость с одной из обкладок, закороченной на землю, счетчик, в которой выполнены триггер Шмитта, сдвиговый регистр, а счетчик реализован с отсутствием сброса, m-разрядным, входной узел выполнен в составе первого, второго и третьего полевых транзисторов, при этом первый транзистор, предназначенный для остановки счета, выполнен с возможностью подачи на его исток потенциала, равного по величине напряжению питания аналоговой части, на затвор - сигнала остановки счета, сток первого транзистора соединен с истоком второго транзистора, предназначенного для зарядки интегрирующей емкости, сток второго транзистора соединен со второй обкладкой интегрирующей емкости, затвор второго транзистора соединен с первым выходом триггера Шмитта и вторым входом m-разрядного счетчика, третий транзистор, предназначенный для задания смещения фотодиода, выполнен с возможностью использования его затвора в качестве входа задания подпорогового режима транзистора, с возможностью соединения его истока с фотодиодом, сток третьего транзистора соединен со стоком второго транзистора, второй обкладкой интегрирующей емкости и с входом триггера Шмитта, с входом триггера Шмитта также соединены сток второго транзистора и вторая обкладка интегрирующей емкости, первый выход триггера Шмитта соединен со вторым входом m-разрядного счетчика, а второй выход триггера Шмитта соединен с первым входом m-разрядного счетчика, выход m-разрядного счетчика, выполненный m-разрядным, соединен m-разрядной шиной передачи данных с m-разрядным входом сдвигового регистра, в сдвиговом регистре выполнены также вход, предназначенный для соединения с выходом сдвигового регистра предыдущей ячейки, вход для подачи сигнала загрузки числа из счетчика в сдвиговый регистр, вход для подачи сигнала считывания информации из сдвигового регистра и вход для подачи инвертированного сигнала считывания информации из сдвигового регистра, выход сдвигового регистра предназначен для соединения его с входом сдвигового регистра последующей ячейки.

В ячейке первый и второй транзисторы выполнены р-канальными, с возможностью подачи потенциала к их подложкам, равного величине напряжения питания аналоговой части, третий транзистор выполнен n-канальным, с его подложкой, закороченной на землю.

В ячейке сдвиговый регистр выполнен в составе m динамических D-триггеров, каждый с пятью входами и одним выходом, первый вход первого динамического D-триггера, выполнен как вход, являющийся входом сдвигового регистра, предназначенным для соединения с выходом сдвигового регистра предыдущей ячейки, первый вход каждого последующего динамического D-триггера соединен с выходом предыдущего динамического D-триггера, выход последнего, m-того, динамического D-триггера, являющийся выходом сдвигового регистра, предназначен для соединения его с входом сдвигового регистра последующей ячейки, второй вход каждого динамического D-триггера подсоединен к m-разрядной шине передачи данных с соответствием номера разряда шины номеру D-триггера, образуя в совокупности второй, m-разрядный, вход сдвигового регистра, связанного m-разрядной шиной передачи данных с выходом m-разрядного счетчика, третьи входы динамических D-триггеров соединены между собой с образованием входа для подачи сигнала загрузки числа из счетчика в сдвиговый регистр, в сдвиговом регистре являющегося входом для подачи сигнала загрузки числа из счетчика в сдвиговый регистр, четвертые входы динамических D-триггеров соединены между собой с образованием входа для подачи сигнала считывания информации из сдвигового регистра, в сдвиговом регистре являющегося входом для подачи сигнала считывания информации из сдвигового регистра, пятые входы динамических D-триггеров соединены между собой с образованием входа для подачи инвертированного сигнала считывания информации из сдвигового регистра, сдвиговом регистре являющегося входом для подачи инвертированного сигнала считывания информации из сдвигового регистра.

В ячейке каждый из m-тых динамических D-триггеров выполнен на девяти полевых транзисторах, при этом первый, второй, шестой и седьмой транзисторы динамического D-триггера выполнены p-канальными и с возможностью подачи потенциала на их подложки, равного по величине рабочему напряжению, третий, четвертый, пятый, восьмой, девятый транзисторы динамического D-триггера выполнены n-канальными, с их подложками, закороченными на землю, исток первого транзистора динамического D-триггера выполнен с возможностью подачи на него потенциала, равного по величине рабочему напряжению, его сток соединен с истоком второго транзистора динамического D-триггера, а затвор соединен с затвором четвертого транзистора динамического D-триггера, между соединенными затворами первого и четвертого транзисторов динамического D-триггера выполнен первый вход динамического D-триггера, сток второго транзистора динамического D-триггера соединен с истоком третьего транзистора динамического D-триггера, а также соединен со стоком пятого транзистора динамического D-триггера и с соединенными затворами шестого и девятого транзисторов динамического D-триггера, затвор второго транзистора динамического D-триггера соединен с затвором восьмого транзистора динамического D-триггера, соединенные затворы второго и восьмого транзисторов динамического D-триггера соединены с пятым входом динамического D-триггера, сток третьего транзистора динамического D-триггера соединен с истоком четвертого транзистора динамического D-триггера, затвор третьего транзистора динамического D-триггера соединен с затвором седьмого транзистора динамического D-триггера, соединенные затворы третьего и седьмого транзисторов динамического D-триггера соединены с четвертым входом динамического D-триггера, сток четвертого транзистора динамического D-триггера выполнен с возможностью соединения его с точкой, в которой потенциал равен нулю, исток пятого транзистора динамического D-триггера соединен со вторым входом динамического D-триггера, подсоединяемым к поразрядной шине передачи данных с соответствием номера разряда шины номеру динамического D-триггера, затвор пятого транзистора динамического D-триггера соединен с третьим входом динамического D-триггера, исток шестого транзистора динамического D-триггера выполнен с возможностью подачи на него потенциала, равного по величине рабочему напряжению, его сток соединен с истоком седьмого транзистора динамического D-триггера, а затвор шестого транзистора динамического D-триггера соединен с затвором девятого транзистора динамического D-триггера, соединенные затворы шестого и девятого транзисторов динамического D-триггера соединены со стоком пятого транзистора динамического D-триггера и соединены с соединенными стоком второго транзистора динамического D-триггера и истоком третьего транзистора динамического D-триггера, сток седьмого транзистора динамического D-триггера соединен с истоком восьмого транзистора динамического D-триггера, между соединенными стоком седьмого транзистора динамического D-триггера и истоком восьмого транзистора динамического D-триггера выполнен выход динамического D-триггера, сток восьмого транзистора динамического D-триггера соединен с истоком девятого транзистора динамического D-триггера, сток девятого транзистора динамического D-триггера выполнен с возможностью соединения его с точкой, в которой потенциал равен нулю.

В ячейке триггер Шмитта выполнен в составе десяти полевых транзисторов, при этом первый, третий, пятый, седьмой и девятый транзисторы триггера Шмитта выполнены p-канальными и с возможностью подачи потенциала на подложку, равного по величине рабочему напряжению, второй, четвертый, шестой, восьмой, десятый транзисторы триггера Шмитта выполнены n-канальными, с их подложками, закороченными на землю, исток первого транзистора триггера Шмитта соединен с истоком пятого транзистора триггера Шмитта, сток первого транзистора триггера Шмитта соединен с истоком второго транзистора триггера Шмитта, сток второго транзистора триггера Шмитта соединен со стоком шестого транзистора триггера Шмитта, затворы первого и второго транзистора триггера Шмитта соединены друг с другом, между соединенными затворами первого и второго транзисторов триггера Шмитта выполнен вход триггера Шмитта, затворы пятого и шестого транзистора триггера Шмитта соединены друг с другом, соединенные затворы пятого и шестого транзистора триггера Шмитта подсоединены между соединенными стоком первого транзистора триггера Шмитта и истоком второго транзистора триггера Шмитта, сток пятого транзистора триггера Шмитта соединен с истоком шестого транзистора триггера Шмитта, исток третьего транзистора триггера Шмитта выполнен с возможностью подачи на него потенциала, равного по величине рабочему напряжению, его сток подсоединен между соединенными истоками первого и пятого транзисторов триггера Шмитта, затвор третьего транзистора триггера Шмитта подсоединен между соединенными стоком пятого транзистора триггера Шмитта и истоком шестого транзистора триггера Шмитта, исток четвертого транзистора триггера Шмитта подсоединен между соединенными стоками второго и шестого транзисторов триггера Шмитта, сток четвертого транзистора триггера Шмитта выполнен с возможностью соединения его с точкой, в которой потенциал равен нулю, затвор четвертого транзистора триггера Шмитта подсоединен между соединенными стоком пятого транзистора триггера Шмитта и истоком шестого транзистора триггера Шмитта, посредством седьмого и восьмого транзисторов триггера Шмитта сформирован инвертор, предназначенный для усиления сигнала, посредством девятого и десятого транзисторов триггера Шмитта сформирован инвертор, предназначенный для формирования инверсного сигнала, исток седьмого транзистора триггера Шмитта выполнен с возможностью подачи на него потенциала, равного по величине рабочему напряжению, его сток соединен с истоком восьмого транзистора триггера Шмитта, сток восьмого транзистора триггера Шмитта выполнен с возможностью соединения его с точкой, в которой потенциал равен нулю, затворы седьмого и восьмого транзисторов триггера Шмитта соединены друг с другом, а также соединены с затвором третьего транзистора триггера Шмитта, с затвором четвертого транзистора триггера Шмитта, со стоком пятого транзистора триггера Шмитта и истоком шестого транзистора триггера Шмитта, соединение стока седьмого транзистора триггера Шмитта и истока восьмого транзистора триггера Шмитта выполнено с возможностью снятия сигнала, поступающего на первый выход триггера Шмитта, исток девятого транзистора триггера Шмитта выполнен с возможностью подачи на него потенциала, равного по величине рабочему напряжению, его сток соединен с истоком десятого транзистора триггера Шмитта, сток десятого транзистора триггера Шмитта выполнен с возможностью соединения его с точкой, в которой потенциал равен нулю, затворы девятого и десятого транзисторов триггера Шмитта соединены друг с другом, соединенные затворы девятого и десятого транзисторов триггера Шмитта подсоединены между стоком седьмого транзистора триггера Шмитта и истоком восьмого транзистора триггера Шмитта, между соединенными стоком девятого транзистора триггера Шмитта и истоком десятого транзистора триггера Шмитта выполнен второй выход триггера Шмитта.

В ячейке счетчик, реализованный с отсутствием сброса, выполнен асинхронным в составе m статических D-триггеров с тремя входами и двумя выходами, первый вход первого статического D-триггера, являющийся первым входом счетчика, предназначен для соединения со вторым выходом триггера Шмитта, второй вход первого статического D-триггера, являющийся вторым входом счетчика, предназначен для соединения с первым выходом триггера Шмитта и с затвором второго, предназначенного для зарядки интегрирующей емкости, транзистора, третий вход каждого статического D-триггера соединен с первым выходом этого же статического D-триггера, первый выход каждого статического D-триггера, кроме m-того, соединен с первым входом следующего статического D-триггера, второй выход каждого статического D-триггера, кроме т-того, соединен со вторым входом следующего статического D-триггера, второй выход каждого статического D-триггера предназначен для соединения с m-разрядной шиной передачи данных, с соответствием номера разряда шины номеру статического D-триггера, в совокупности формируя выход m-разрядного счетчика.

В ячейке каждый из m-тых статических D-триггеров выполнен на шестнадцати полевых транзисторах, при этом первый, третий, пятый, седьмой, девятый, одиннадцатый, тринадцатый, и пятнадцатый транзисторы статического D-триггера выполнены p-канальными и с возможностью подачи потенциала на их подложки, равного по величине рабочему напряжению, второй, четвертый, шестой, восьмой, десятый, двенадцатый, четырнадцатый и шестнадцатый транзисторы статического D-триггера выполнены n-канальными и с их подложками, закороченными на землю, исток первого транзистора статического D-триггера соединен с истоком второго транзистора статического D-триггера, между соединенными истоками выполнен третий вход статического D-триггера, сток первого транзистора статического D-триггера соединен с затвором третьего транзистора статического D-триггера, сток второго транзистора статического D-триггера соединен с затвором четвертого транзистора статического D-триггера, стоки первого и второго транзисторов, затворы третьего и четвертого транзисторов статического D-триггера соединены друг с другом, затворы первого, пятого, девятого, тринадцатого транзисторов статического D-триггера соединены друг с другом и первым входом статического D-триггера, затворы второго, шестого, десятого, четырнадцатого транзисторов статического D-триггера соединены друг с другом и вторым входом статического D-триггера, исток третьего транзистора статического D-триггера выполнен с возможностью подачи на него потенциала, равного по величине рабочему напряжению, сток третьего транзистора статического D-триггера соединен с истоком четвертого транзистора статического D-триггера, сток четвертого транзистора статического D-триггера выполнен с возможностью соединения его с точкой, в которой потенциал равен нулю, исток пятого транзистора статического D-триггера соединен с истоком шестого транзистора статического D-триггера, к соединенным истокам пятого и шестого транзисторов статического D-триггера подсоединен затвор третьего транзистора статического D-триггера, сток пятого транзистора статического D-триггера соединен со стоком шестого транзистора статического D-триггера, исток седьмого транзистора статического D-триггера выполнен с возможностью подачи на него потенциала, равного по величине рабочему напряжению, сток седьмого транзистора статического D-триггера соединен с истоком восьмого транзистора статического D-триггера, сток восьмого транзистора статического D-триггера выполнен с возможностью соединения его с точкой, в которой потенциал равен нулю, затворы седьмого и восьмого транзисторов статического D-триггера соединены друг с другом, соединенные затворы седьмого и восьмого транзисторов статического D-триггера подсоединены между стоком третьего транзистора статического D-триггера и истоком четвертого транзистора статического D-триггера, между стоком седьмого транзистора статического D-триггера и истоком восьмого транзистора статического D-триггера подсоединены соединенные стоки пятого и шестого транзисторов статического D-триггера, исток девятого транзистора статического D-триггера соединен с истоком десятого транзистора статического D-триггера, соединенные истоки девятого и десятого транзистора статического D-триггера подсоединены между стоком седьмого транзистора статического D-триггера и истоком восьмого транзистора статического D-триггера, сток девятого транзистора статического D-триггера соединен с затвором одиннадцатого транзистора статического D-триггера, сток десятого транзистора статического D-триггера соединен с затвором двенадцатого транзистора статического D-триггера, стоки девятого и десятого транзисторов статического D-триггера, затворы одиннадцатого и двенадцатого транзисторов статического D-триггера соединены друг с другом, исток одиннадцатого транзистора статического D-триггера выполнен с возможностью подачи на него потенциала, равного по величине рабочему напряжению, сток одиннадцатого транзистора статического D-триггера соединен с истоком двенадцатого транзистора статического D-триггера, сток двенадцатого транзистора статического D-триггера выполнен с возможностью соединения его с точкой, в которой потенциал равен нулю, соединение стока одиннадцатого транзистора статического D-триггера и истока двенадцатого транзистора статического D-триггера выполнено с возможностью снятия сигнала, поступающего на второй выход статического D-триггера, исток тринадцатого транзистора статического D-триггера соединен с истоком четырнадцатого транзистора статического D-триггера, между соединенными истоками тринадцатого и четырнадцатого транзисторов статического D-триггера подсоединен затвор одиннадцатого транзистора статического D-триггера, сток тринадцатого транзистора статического D-триггера соединен со стоком четырнадцатого транзистора статического D-триггера, исток пятнадцатого транзистора статического D-триггера выполнен с возможностью подачи на него потенциала, равного по величине рабочему напряжению, сток пятнадцатого транзистора статического D-триггера соединен с истоком шестнадцатого транзистора статического D-триггера, сток шестнадцатого транзистора статического D-триггера выполнен с возможностью соединения его с точкой, в которой потенциал равен нулю, затворы пятнадцатого и шестнадцатого транзисторов статического D-триггера соединены друг с другом, соединенные затворы пятнадцатого и шестнадцатого транзисторов статического D-триггера подсоединены между стоком одиннадцатого транзистора статического D-триггера и истоком двенадцатого транзистора статического D-триггера, между стоком пятнадцатого транзистора статического D-триггера и истоком шестнадцатого транзистора статического D-триггера подсоединены соединенные стоки тринадцатого и четырнадцатого транзисторов статического D-триггера и выполнен первый выход статического D-триггера.

Сущность технического решения поясняется нижеследующим описанием и прилагаемыми фигурами.

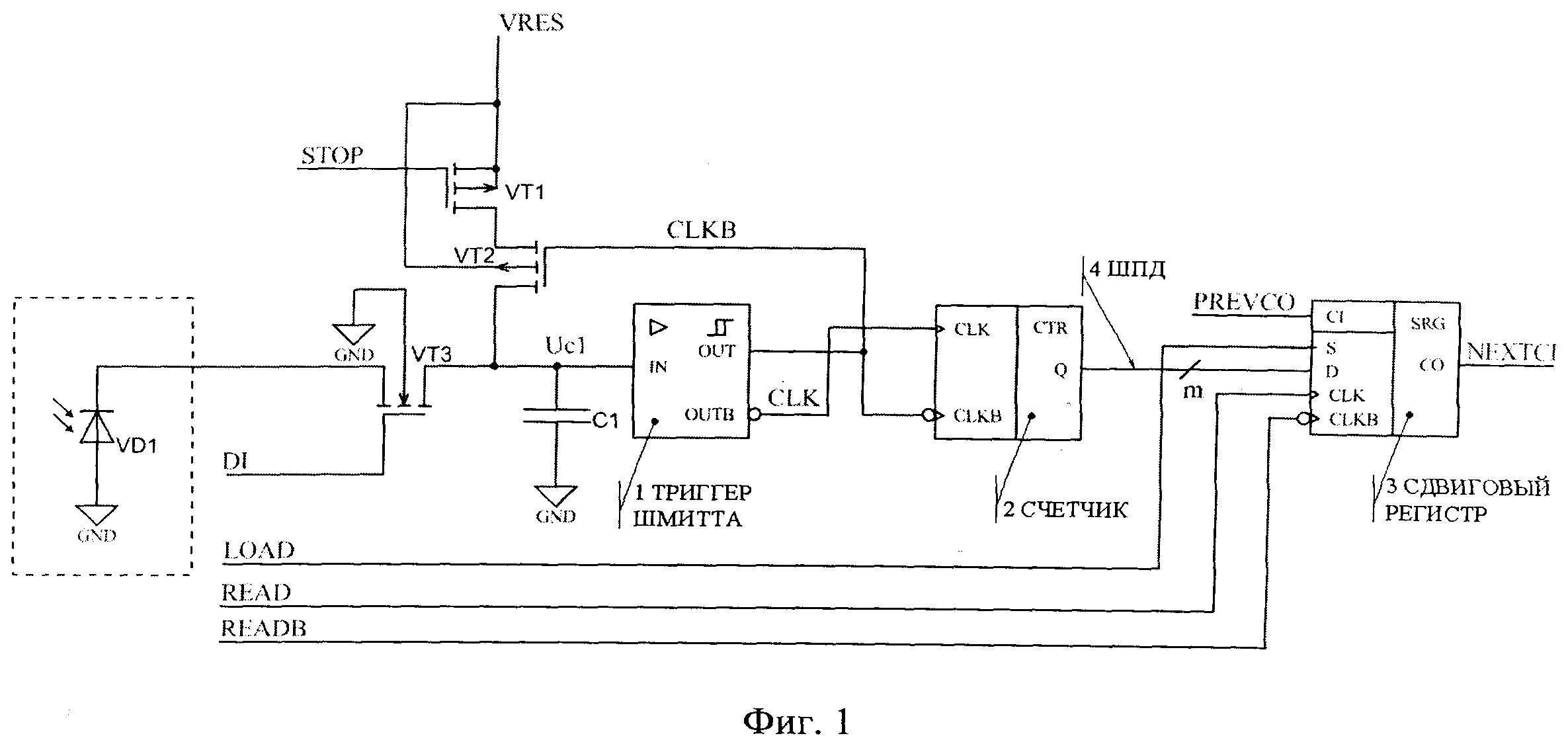

На Фиг.1 приведена электрическая принципиальная схема ячейки устройства считывания фотоприемных матриц с аналого-цифровым преобразованием, например, со счетчиком и сдвиговым регистром разрядностью m, где: 1 - триггер Шмитта; 2 - счетчик; 3 - сдвиговый регистр; 4 - шина передачи данных (ШПД); C1 - интегрирующая емкость; VT1 - первый транзистор (p-канальный транзистор для остановки счета); VT2 - второй транзистор (p-канальный транзистор для зарядки интегрирующей емкости); VT3 - третий транзистор (n-канальный транзистор для задания смещения фотодиода); VD1 - фотодиод.

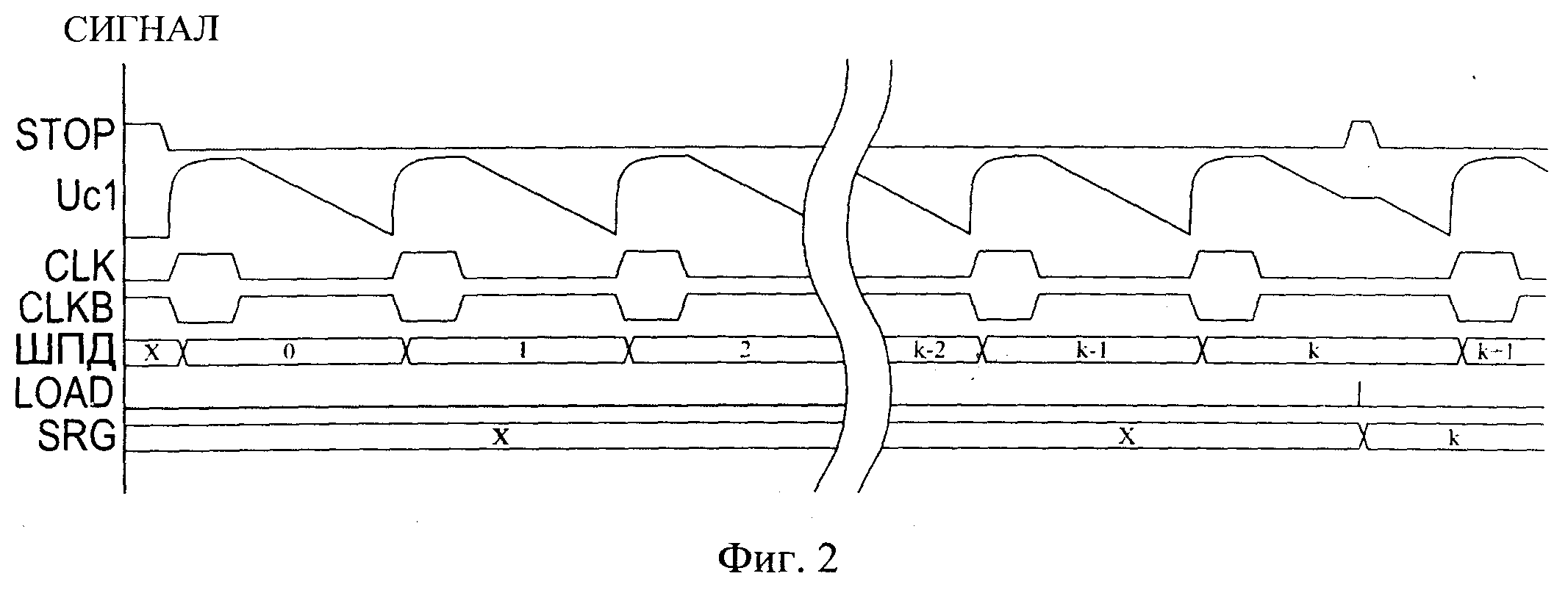

На Фиг.2 представлена временная диаграмма работы ячейки устройства считывания фотоприемных матриц с аналого-цифровым преобразованием при неизменном фототоке, где: сигнал STOP - сигнал остановки счета; сигнал Uc1 - напряжение на интегрирующей емкости; сигнал CLK - внутренний сигнал на выходе OUTB триггера Шмитта; сигнал CLKB - внутренний сигнал на выходе OUT триггера Шмитта; сигнал ШПД сигнал на поразрядной шине передачи данных от счетчика к сдвиговому регистру; сигнал LOAD - сигнал загрузки числа из счетчика в сдвиговый регистр; сигнал SRG - сигнал, отображающий изменение состояния сдвигового регистра.

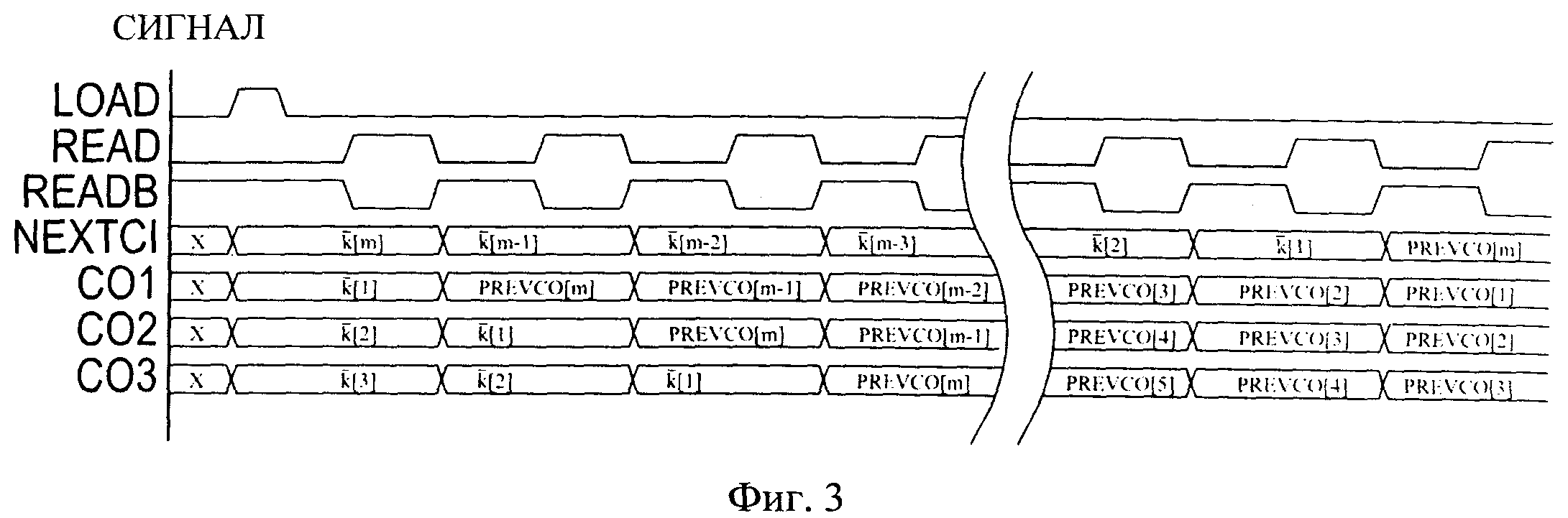

На Фиг.3 представлена временная диаграмма работы m-разрядного сдвигового регистра, построенного на m динамических D-триггерах, где: сигнал LOAD - сигнал загрузки числа из счетчика в сдвиговый регистр; сигналы READ, READB - сигналы считывания информации из сдвигового регистра; сигнал NEXTCI - сигнал на выходе сдвигового регистра, соединяющегося с входом последующей ячейки в матрице КИС (кремниевой интегральной схемы); сигналы CO1, CO2, CO3 - сигналы на выходах соответствующих m-тых динамических D-триггеров, первого, второго, третьего.

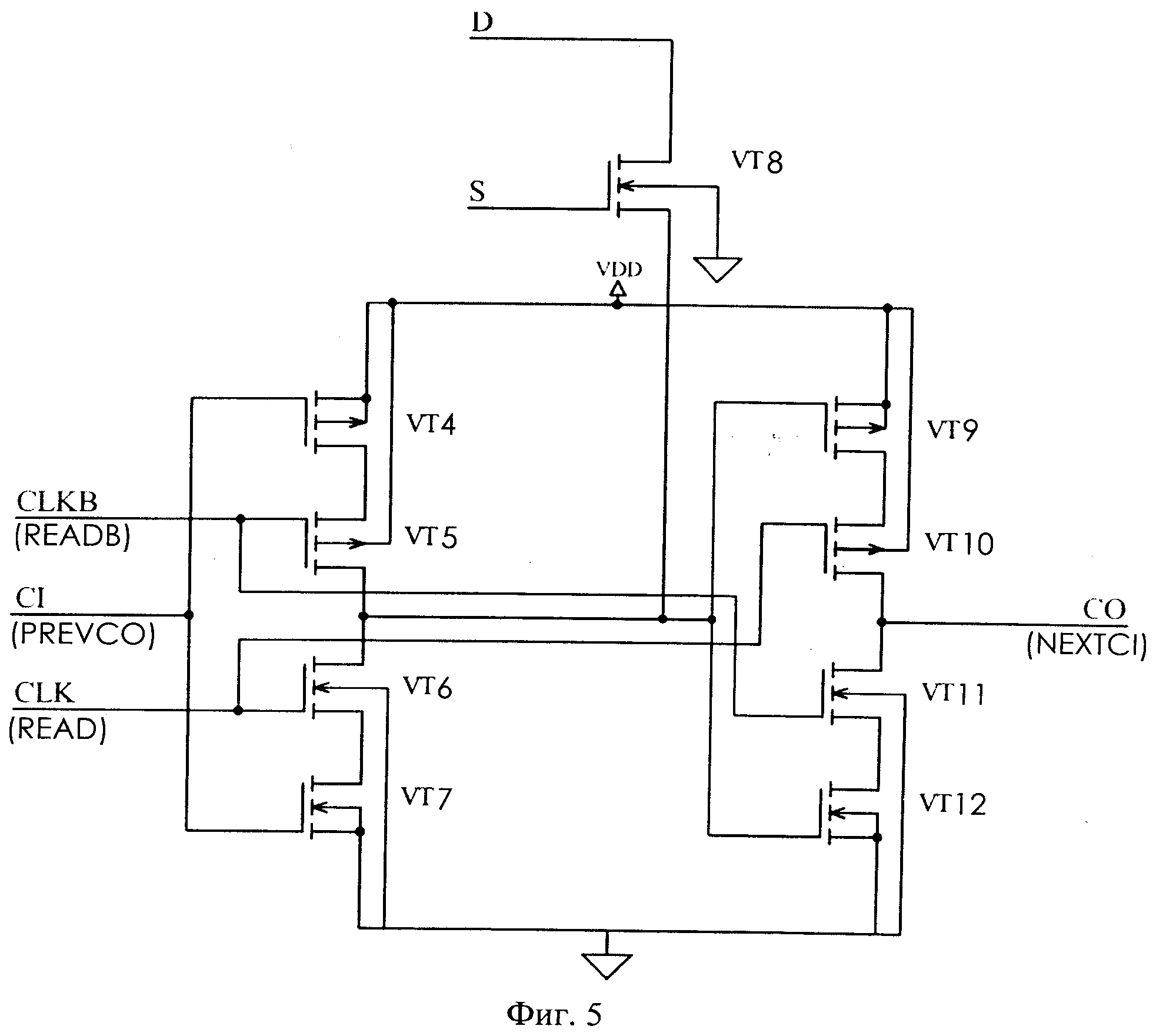

На Фиг.4 приведена электрическая принципиальная схема m-разрядного сдвигового регистра с параллельной загрузкой, построенного на m динамических D-триггерах, где Dd1, Dd2, Dd3, Ddm - соответственно, 1, 2, 3, m-тый динамический D-триггер; CO1, CO2, CO3, COm - сигналы, вырабатываемые на выходы, соответственно, 1, 2, 3, m-того динамического D-триггера; Qd1, Qd2, Qd3, Qdm - сигналы, поступающие на входы, соответственно, 1, 2, 3, m-того динамического D-триггера с m-разрядной шины передачи данных с соответствием номера динамического D-триггера номеру разряда шины.

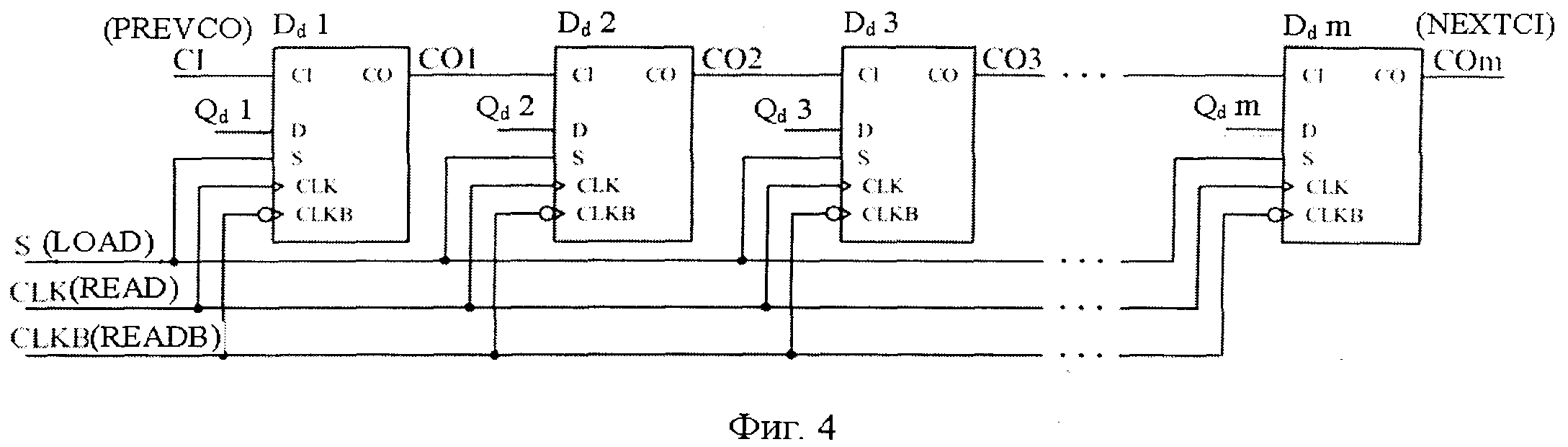

На Фиг.5 приведена электрическая принципиальная схема двухфазного динамического D-триггера, используемого в качестве одного из варианта выполнения функционального узла при реализации сдвигового регистра, где: VT4, VT5, VT9, VT10 - p-канальные транзисторы; VT6, VT7, VT8, VT11, VT12 - n-канальные транзисторы, VT4 - первый транзистор динамического D-триггера, VT5 - второй транзистор динамического D-триггера, VT6 - третий транзистор динамического D-триггера, VT7 - четвертый транзистор динамического D-триггера, VT8 - пятый транзистор динамического D-триггера, VT9 - шестой транзистор динамического D-триггера, VT10 - седьмой транзистор динамического D-триггера, VT11 - восьмой транзистор динамического D-триггера, VT12 - девятый транзистор динамического D-триггера.

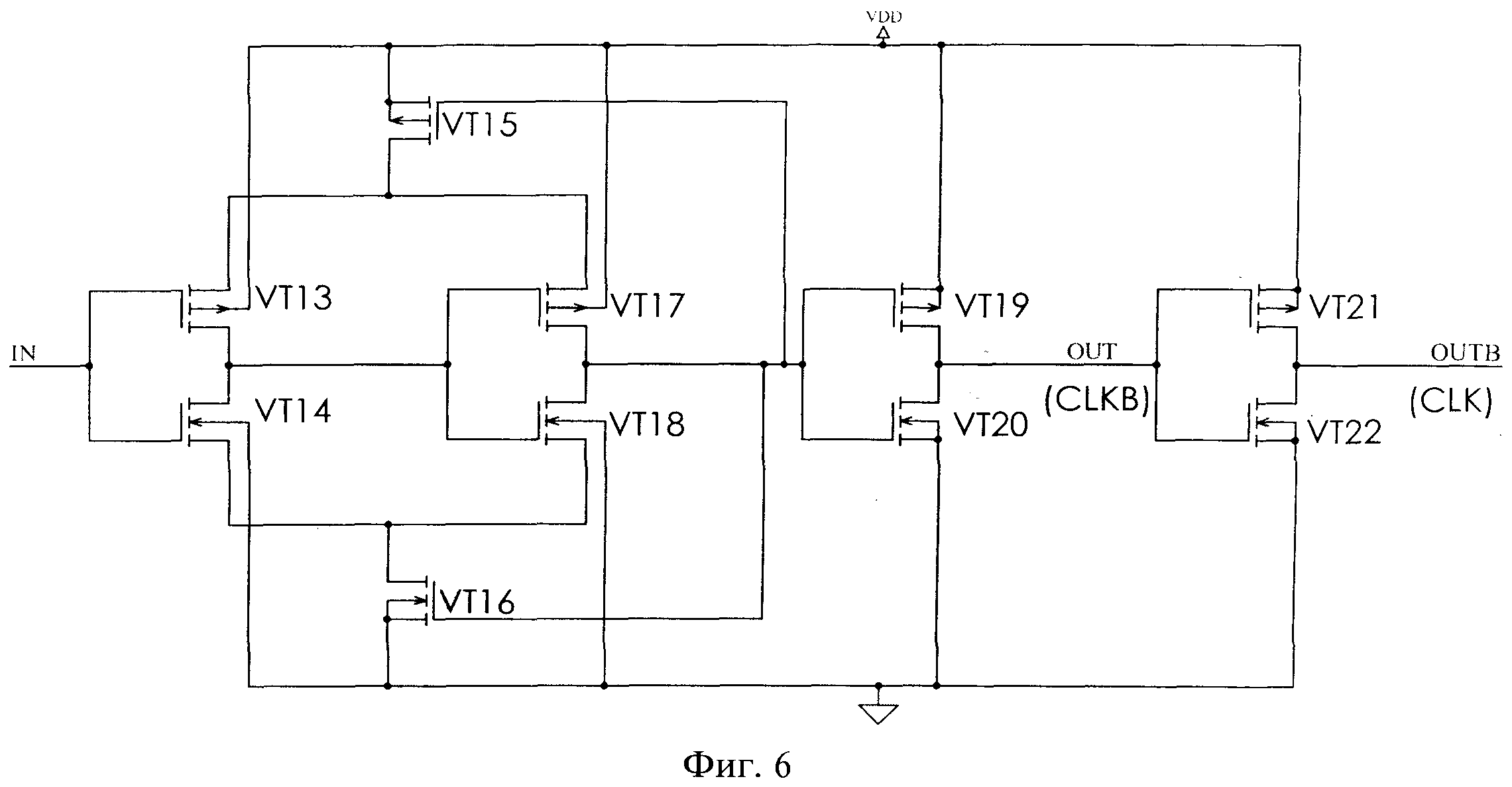

На Фиг.6 приведена электрическая принципиальная схема триггера Шмитта, как один из вариантов реализации, в котором: VT13, VT15, VT17, VT19, VT21 - p-канальные транзисторы; VT14, VT16, VT18, VT20, VT22 - n-канальные транзисторы, VT13 - первый транзистор триггера Шмитта, VT14 - второй транзистор триггера Шмитта, VT15 - третий транзистор триггера Шмитта, VT16 - четвертый транзистор триггера Шмитта, VT17 - пятый транзистор триггера Шмитта, VT18 - шестой транзистор триггера Шмитта, VT19 - седьмой транзистор триггера Шмитта, VT20 - восьмой транзистор триггера Шмитта, VT21 - девятый транзистор триггера Шмитта, VT22 - десятый транзистор триггера Шмитта.

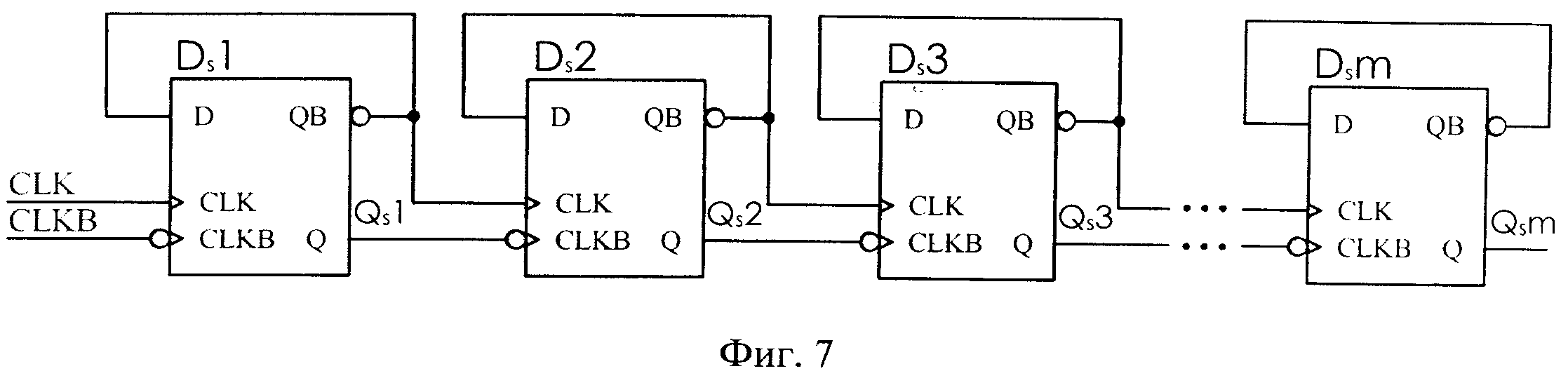

На Фиг.7 приведена электрическая принципиальная схема счетчика - m-разрядного асинхронного счетчика, построенного на m статических D-триггерах, как один из вариантов реализации, в которой: Ds1, Ds2, Ds3, Dsm - соответственно, 1, 2, 3, m-тый статический D-триггер счетчика; Qs1, Qs2, Qs3, Qsm - сигналы, вырабатываемые на вторые выходы, соответственно, 1, 2, 3, m-того статического D-триггера счетчика.

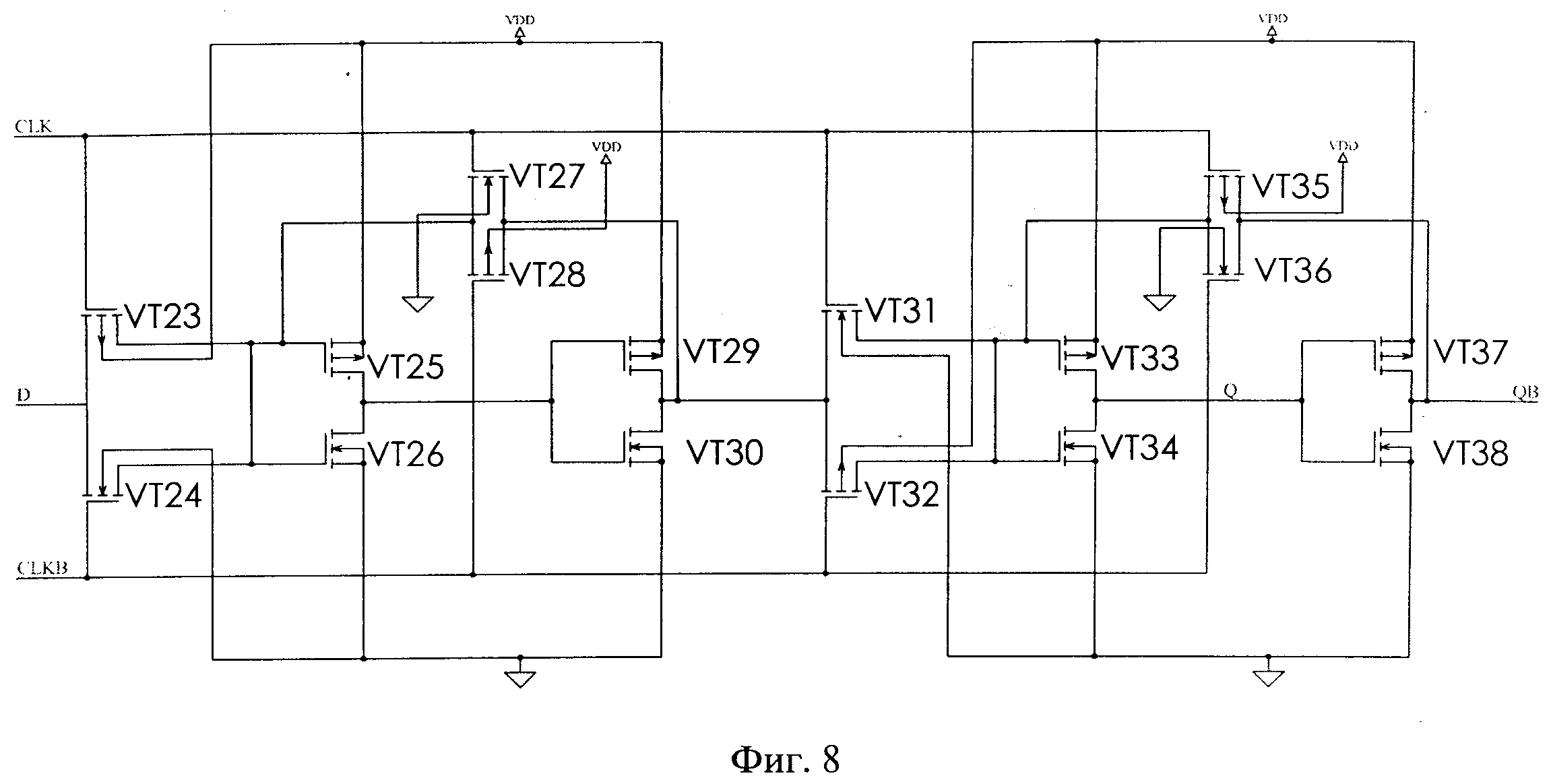

На Фиг.8 приведена электрическая принципиальная схема двухфазного статического D-триггера, используемого в качестве одного из варианта выполнения функционального узла при реализации асинхронного счетчика, где: VT23, VT25, VT27, VT29, VT31, VT33, VT35, VT37 - p-канальные транзисторы; VT24, VT26, VT28, VT30, VT32, VT34, VT36, VT38 - n-канальные транзисторы, VT23 - первый транзистор статического D-триггера, VT24 - второй транзистор статического D-триггера, VT25 - третий транзистор статического D-триггера, VT26 - четвертый транзистор статического D-триггера, VT27 - пятый транзистор статического D-триггера, VT28 - шестой транзистор статического D-триггера, VT29 - седьмой транзистор статического D-триггера, VT30 - восьмой транзистор статического D-триггера, VT31 - девятый транзистор статического D-триггера, VT32 - десятый транзистор статического D-триггера, VT33 - одиннадцатый транзистор статического D-триггера, VT34 - двенадцатый транзистор статического D-триггера, VT35 - тринадцатый транзистор статического D-триггера, VT36 - четырнадцатый транзистор статического D-триггера, VT37 - пятнадцатый транзистор статического D-триггера, VT38 - шестнадцатый транзистор статического D-триггера.

В предлагаемом техническом решении снижение энергопотребления достигается в результате отказа от использования компаратора и оказания предпочтения триггеру Шмитта. Указанный триггер имеет более низкое энергопотребление. Кроме того, использование триггера Шмитта обуславливает уменьшение площади ячейки, так как триггер Шмитта содержит меньшее количество транзисторов.

С другой стороны, в предлагаемом техническом решении счетчик реализован с отсутствием сброса. Благодаря исключению необходимости применения транзисторов для сброса, сокращается общее число транзисторов, и, следовательно, уменьшается площадь счетчика, а также количество управляющих сигналов.

Отказ от применения схемы памяти в ячейке и переход к использованию сдвигового регистра позволяет значительно упростить вывод данных, реализуя при этом не параллельный вывод данных, а последовательный. Таким образом, обеспечивается вывод данных из ячейки по однопроводной шине, в отличие от вышеприведенных аналогов, в которых в этих целях предусмотрены N-разрядные шины, что значительно упрощает топологию и ведет к уменьшению количества слоев металлизации.

В общем случае выполнения ячейка устройства считывания фотоприемных матриц с аналого-цифровым преобразованием (см. Фиг.1) содержит входной узел, интегрирующую емкость C1, триггер Шмитта 1, счетчик 2, сдвиговый регистр 3. Счетчик 2 реализован с отсутствием сброса.

Входной узел выполнен на полевых транзисторах, в составе первого, второго и третьего транзисторов, соответственно, VT1, VT2, VT3. Первый транзистор VT1, предназначенный для остановки счета, выполнен с возможностью подачи на его исток потенциала, равного по величине напряжению питания аналоговой части (см. Фиг.1 «VRES»), на затвор - сигнала остановки счета (см. Фиг.1, 2 «STOP»). Сток первого транзистора VT1 соединен с истоком второго транзистора VT2, предназначенного для зарядки интегрирующей емкости C1. Сток второго транзистора VT2 соединен со второй обкладкой интегрирующей емкости C1. Затвор второго транзистора VT2 соединен с первым выходом триггера Шмитта 1 (см. Фиг.1 «OUT») и вторым входом m-разрядного счетчика 2 (см. Фиг.1 «CLKB»). Третий транзистор VT3, предназначенный для задания смещения фотодиода VD1, выполнен с возможностью использования его затвора в качестве входа задания подпорогового режима транзистора (см. Фиг.1 «DI»), а также с возможностью соединения его истока с фотодиодом VD1. Стоки третьего транзистора VT3 и второго транзистора VT2 соединены друг с другом.

Одна из обкладок интегрирующей емкости C1 закорочена на землю. Вторая обкладка интегрирующей емкости C1 соединена со стоками третьего транзистора VT3 и второго транзистора VT2 и с входом триггера Шмитта (см. Фиг.1 «IN»). Интегрирующая емкость 0 заряжается и разряжается, посредством транзисторов VT1 и VT2 напряжение на ней Uc1 (см. Фиг.1 и 2 «Uc1») меняется в пределах верхнего и нижнего значений порогов срабатывания триггера Шмитта 1, возрастая до его верхнего значения, как только на затвор первого транзистора VT1 подается соответствующее значение сигнала STOP (сбрасывается значение сигнала STOP, останавливающее счет), а на затвор второго транзистора VT2 - соответствующее значение сигнала CLKB, и падая до нижнего, как только на затворе второго транзистора VT2 меняется значение сигнала CLKB (см. Фиг.2). Сигнал STOP меняется один раз за кадр, в момент записи в сдвиговый регистр 3.

Первый выход триггера Шмитта 1 (см. Фиг.1 «OUT») соединен с затвором второго транзистора VT2, вырабатываемый на входе сигнал CLKB поступает на затвор. С подачей соответствующего значения сигнала STOP, разрешающего счет, на затвор первого транзистора VT1 и сигнала CLKB на затвор второго транзистора VT2 начинается счет (см. Фиг.2). В любой момент подачей сигнала STOP на затвор первого транзистора VT1 со значением, отменяющим счет, последний может быть остановлен. Первый выход триггера Шмитта 1 (см. Фиг.1 «OUT») также соединен со вторым входом m-разрядного счетчика 2 (см. Фиг.1 «CLKB»), вырабатываемый на выходе сигнал CLKB поступает также на второй вход m-разрядного счетчика 2 (см. Фиг.1 «CLKB»). Второй выход триггера Шмитта 1 (см. Фиг.1 «OUTB»), предназначенный для вырабатываемого сигнала CLK, соединен с первым входом m-разрядного счетчика 2 (см. Фиг.1 «CLK»). Сигналы на выходах триггера Шмитта 1 - CLK и CLKB инвертированы друг относительно друга (см. Фиг.2 «CLK», «CLKB»), синхронизированы по времени.

Выход m-разрядного счетчика 2 (см. Фиг.1 «Q»), выполненный m-разрядным, соединен m-разрядной шиной передачи данных - ШПД 4 с m-разрядным входом (см. Фиг.1 «D») сдвигового регистра 3. ШПД 4 выполнена цифровой шиной, данные от счетчика 2 в сдвиговый регистр 3 поступают в цифровой форме (см. Фиг.2 «ШПД»). В сдвиговом регистре 3 выполнен вход (см. Фиг.1 «CI»), предназначенный для соединения с выходом сдвигового регистра предыдущей ячейки, на который поступает сигнал PREVCO (см. Фиг.1). Кроме того, в сдвиговом регистре 3 выполнены следующие входы. Вход для подачи сигнала загрузки числа из счетчика 2 в сдвиговый регистр 3 (см. Фиг.1 «S»), по которому подается сигнал LOAD (см. Фиг.1-3 «LOAD») - сигнал загрузки числа из счетчика в сдвиговый регистр. Сигнал LOAD необходимо подавать во время сигнала STOP (когда счет остановлен), чтобы избежать изменения значения счетчика 2 во время записи. Вход (см. Фиг.1 «CLK») для подачи сигнала считывания информации из сдвигового регистра (см. Фиг.3 «READ») и вход (см. Фиг.1 «CLKB») для подачи инвертированного сигнала считывания информации из сдвигового регистра (см. Фиг.3 «READB»). Выход (см. Фиг.1 «СО») сдвигового регистра 3 предназначен для соединения его с входом сдвигового регистра последующей ячейки, на который с выхода поступает сигнал NEXTCI (см. Фиг.1, 3 «NEXTCI»). Сдвиговый регистр 3 осуществляет поразрядный сдвиг, выводя число инверсное записанному со счетчика 2. На вход сигнала PREVCO (см. Фиг.1 «CI») данные поступают также поразрядно.

Во входном узле ячейки (см. Фиг.1) первый и второй транзисторы, соответственно, VT1 и VT2 выполнены p-канальными, с возможностью подачи потенциала к их подложкам, равного величине напряжения питания аналоговой части, а третий транзистор VT3 выполнен n-канальным, с подложкой, закороченной на землю.

В частном случае реализации ячейки выполнение сдвигового регистра базируется на использовании динамических триггеров. Сдвиговый регистр 3 выполнен в составе m динамических D-триггеров, снабженных пятью входами и одним выходом (см. Фиг.4).

Первый вход первого динамического D-триггера - Dd1 выполнен как вход, являющийся входом (см. Фиг.1, Фиг.4 «CI») сдвигового регистра 3, предназначенным для соединения с выходом сдвигового регистра предыдущей ячейки. Первый вход каждого последующего динамического D-триггера, Dd2-Ddm, соединен с выходом предыдущего динамического D-триггера, Dd1-Ddm-1. Выход последнего, m-того, динамического D-триггера, являющийся выходом сдвигового регистра 3, предназначен для соединения его с входом сдвигового регистра последующей ячейки. Второй вход (см. Фиг.4; «D») каждого динамического D-триггера, подсоединен к m-разрядной шине передачи данных - ШПД 4 с соответствием номера разряда шины номеру динамического D-триггера, на вторые входы динамических D-триггеров - Dd1-Ddm (см. Фиг.4; «D») поступают сигналы Qd1, Qd2, Qd3, Qdm, соответственно, 1, 2, 3, m-того динамического D-триггера с m-разрядной шины передачи данных. В совокупности вторые входы динамических D-триггеров - Dd1-Ddm образуют m-разрядный вход (см. Фиг.1 «D») сдвигового регистра 3, связанного поразрядной шиной передачи данных с выходом m-разрядного счетчика 2. Третьи входы (см. Фиг.4; «S») динамических D-триггеров - Dd1-Ddm соединены между собой с образованием входа для подачи сигнала загрузки числа из счетчика в сдвиговый регистр (см. Фиг.1-4 «LOAD»), который в сдвиговом регистре 3 является входом для подачи сигнала загрузки числа из счетчика 2 в сдвиговый регистр 3 (см. Фиг.1 «S»). Четвертые входы (см. Фиг.4 «CLK») динамических D-триггеров - Dd1-Ddm соединены между собой с образованием входа для подачи сигнала считывания информации из сдвигового регистра 3 (см. Фиг.1, 3, 4 «READ»), который в сдвиговом регистре 3 является входом (см. Фиг.1 «CLK») для подачи сигнала считывания информации из сдвигового регистра 3 (см. Фиг.3 «READ»). Пятые входы (см. Фиг.4 «CLKB») динамических D-триггеров - Dd1-Ddm соединены между собой с образованием входа для подачи инвертированного сигнала считывания информации из сдвигового регистра 3 (см. Фиг.1, 3, 4 «READB»), который в сдвиговом регистре 3 является входом (см. Фиг.1 «CLKB») для подачи инвертированного сигнала считывания информации из сдвигового регистра 3 (см. Фиг.3 «READB»).

На выходах динамических D-триггеров - Dd1-Ddm вырабатываются сигналы CO1, CO2, CO3, COm, соответственно, 1, 2, 3, m-того динамического D-триггера (см. Фиг.3, 4 «СО»), соответствующие числу, инверсно записанному со счетчика 2.

Каждый из m-тых динамических D-триггеров выполнен на девяти полевых транзисторах (см. Фиг.5). Первый, второй, шестой и седьмой транзисторы динамического D-триггера, соответственно, VT4, VT5, VT9 и VT10 выполнены p-канальными и с возможностью подачи потенциала на их подложки, равного по величине рабочему напряжению. Третий, четвертый, пятый, восьмой, девятый транзисторы динамического D-триггера, соответственно, VT6, VT7, VT8, VT11, VT12 выполнены n-канальными, с их подложками, закороченными на землю.

Исток первого транзистора динамического D-триггера VT4 выполнен с возможностью подачи на него потенциала, равного по величине рабочему напряжению. Сток первого транзистора динамического D-триггера VT4 соединен с истоком второго транзистора динамического D-триггера VT5, а затвор первого транзистора динамического D-триггера VT4 соединен с затвором четвертого транзистора динамического D-триггера VT7. Между соединенными затворами первого и четвертого транзисторов динамического D-триггера, соответственно, VT4 и VT7 выполнен первый вход динамического D-триггера (см. Фиг.4 и Фиг.5 «CI»). Сток второго транзистора динамического D-триггера VT5 соединен с истоком третьего транзистора динамического D-триггера VT6, а также соединен со стоком пятого транзистора динамического D-триггера VT8 и с соединенными затворами шестого и девятого транзисторов динамического D-триггера, соответственно, VT9 и VT12. Затвор второго транзистора динамического D-триггера VT5 соединен с затвором восьмого транзистора динамического D-триггера VT11. Соединенные затворы второго и восьмого транзисторов динамического D-триггера, соответственно, VT5 и VT11 соединены с пятым входом динамического D-триггера (см. Фиг.4 и Фиг.5 «CLKB»). Сток третьего транзистора динамического D-триггера VT6 соединен с истоком четвертого транзистора динамического D-триггера VT7, затвор третьего транзистора динамического D-триггера VT6 соединен с затвором седьмого транзистора динамического D-триггера VT10. Соединенные затворы третьего и седьмого транзисторов динамического D-триггера, соответственно, VT6 и VT10 соединены с четвертым входом динамического D-триггера (см. Фиг.4 и Фиг.5 «CLK»). Сток четвертого транзистора динамического D-триггера VT7 выполнен с возможностью соединения его с точкой, в которой потенциал равен нулю. Исток пятого транзистора динамического D-триггера VT8 соединен со вторым входом динамического D-триггера (см. Фиг.4 и Фиг.5 «D»), подсоединяемым к m-разрядной шине передачи данных - ШПД 4 с соответствием номера разряда шины номеру динамического D-триггера. Затвор пятого транзистора динамического D-триггера VT8 соединен с третьим входом динамического D-триггера (см. Фиг.4 и Фиг.5 «S»). Исток шестого транзистора динамического D-триггера VT9 выполнен с возможностью подачи на него потенциала, равного по величине рабочему напряжению. Сток шестого транзистора динамического D-триггера VT9 соединен с истоком седьмого транзистора динамического D-триггера VT10. Затвор шестого транзистора динамического D-триггера VT9 соединен с затвором девятого транзистора динамического D-триггера VT12. Соединенные затворы шестого и девятого транзисторов динамического D-триггера, соответственно, VT9 и VT12 соединены со стоком пятого транзистора динамического D-триггера VT8 и соединены с соединенными стоком второго транзистора динамического D-триггера VT5 и истоком третьего транзистора динамического D-триггера VT6. Сток седьмого транзистора динамического D-триггера VT10 соединен с истоком восьмого транзистора динамического D-триггера VT11. Между соединенными стоком седьмого транзистора динамического D-триггера VT10 и истоком восьмого транзистора динамического D-триггера VT11 выполнен выход динамического D-триггера (см. Фиг.4 и Фиг.5 «CO»). Сток восьмого транзистора динамического D-триггера VT11 соединен с истоком девятого транзистора динамического D-триггера VT12. Сток девятого транзистора динамического D-триггера VT12 выполнен с возможностью соединения его с точкой, в которой потенциал равен нулю.

В частном случае реализации ячейки триггер Шмитта 1 (см. Фиг.1) выполнен в составе десяти полевых транзисторов (см. Фиг.6). Первый, третий, пятый, седьмой и девятый транзисторы триггера Шмитта, соответственно, VT13, VT15, VT17, VT19 и VT21 выполнены p-канальными и с возможностью подачи потенциала на подложку, равного по величине рабочему напряжению. Второй, четвертый, шестой, восьмой, десятый транзисторы триггера Шмитта, соответственно, VT14, VT16, VT18, VT20 и VT22 выполнены n-канальными, с их подложками, закороченными на землю.

Исток первого транзистора триггера Шмитта VT13 соединен с истоком пятого транзистора триггера Шмитта VT17. Сток первого транзистора триггера Шмитта VT13 соединен с истоком второго транзистора триггера Шмитта VT14. Сток второго транзистора триггера Шмитта VT14 соединен со стоком шестого транзистора триггера Шмитта VT18. Затворы первого и второго транзистора триггера Шмитта, соответственно, VT13 и VT14 соединены друг с другом. Между соединенными затворами первого и второго транзисторов триггера Шмитта, соответственно, VT13 и VT14 выполнен вход триггера Шмитта (см. Фиг.1 и Фиг.6 «IN»). Затворы пятого и шестого транзистора триггера Шмитта, соответственно, VT17 и VT18 соединены друг с другом. Соединенные затворы пятого и шестого транзистора триггера Шмитта, соответственно, VT17 и VT18 подсоединены между соединенными стоком первого транзистора триггера Шмитта VT13 и истоком второго транзистора триггера Шмитта VT14. Сток пятого транзистора триггера Шмитта VT17 соединен с истоком шестого транзистора триггера Шмитта VT18. Исток третьего транзистора триггера Шмитта VT15 выполнен с возможностью подачи на него потенциала, равного по величине рабочему напряжению, его сток подсоединен между соединенными истоками первого и пятого транзисторов триггера Шмитта, соответственно, VT13 и VT17. Затвор третьего транзистора триггера Шмитта VT15 подсоединен между соединенными стоком пятого транзистора триггера Шмитта VT17 и истоком шестого транзистора триггера Шмитта VT18. Исток четвертого транзистора триггера Шмитта VT16 подсоединен между соединенными стоками второго и шестого транзисторов триггера Шмитта, соответственно, VT14 и VT18. Сток четвертого транзистора триггера Шмитта VT16 выполнен с возможностью соединения его с точкой, в которой потенциал равен нулю. Затвор четвертого транзистора триггера Шмитта VT16 подсоединен между соединенными стоком пятого транзистора триггера Шмитта VT17 и истоком шестого транзистора триггера Шмитта VT18. Посредством седьмого и восьмого транзисторов триггера Шмитта, соответственно, VT19 и VT20 сформирован инвертор, предназначенный для усиления сигнала. Посредством девятого и десятого транзисторов триггера Шмитта, соответственно, VT21 и VT22 сформирован инвертор, предназначенный для формирования инверсного сигнала. Исток седьмого транзистора триггера Шмитта VT19 выполнен с возможностью подачи на него потенциала, равного по величине рабочему напряжению, его сток соединен с истоком восьмого транзистора триггера Шмитта VT20. Сток восьмого транзистора триггера Шмитта VT20 выполнен с возможностью соединения его с точкой, в которой потенциал равен нулю. Затворы седьмого и восьмого транзисторов триггера Шмитта, соответственно, VT19 и VT20 соединены друг с другом, а также соединены с затвором третьего транзистора триггера Шмитта VT15, с затвором четвертого транзистора триггера Шмитта VT14, со стоком пятого транзистора триггера Шмитта VT17 и истоком шестого транзистора триггера Шмитта VT18. Соединение стока седьмого транзистора триггера Шмитта VT19 и истока восьмого транзистора триггера Шмитта VT20 выполнено с возможностью снятия сигнала, поступающего на первый выход триггера Шмитта (см. Фиг.1 и Фиг.5 «OUT»). Исток девятого транзистора триггера Шмитта VT21 выполнен с возможностью подачи на него потенциала, равного по величине рабочему напряжению, его сток соединен с истоком десятого транзистора триггера Шмитта VT22. Сток десятого транзистора триггера Шмитта VT22 выполнен с возможностью соединения его с точкой, в которой потенциал равен нулю. Затворы девятого и десятого транзисторов триггера Шмитта, соответственно, VT21 и VT22 соединены друг с другом. Соединенные затворы девятого и десятого транзисторов триггера Шмитта, соответственно, VT21 и VT22 подсоединены между стоком седьмого транзистора триггера Шмитта VT19 и истоком восьмого транзистора триггера Шмитта VT20. Между соединенными стоком девятого транзистора триггера Шмитта VT21 и истоком десятого транзистора триггера Шмитта VT22 выполнен второй выход триггера Шмитта.

В частном случае выполнения ячейки m-разрядный счетчик 2, который реализован с отсутствием сброса, (см. Фиг.1) выполнен асинхронным в составе m статических D-триггеров, в которых выполнено три входа (см. Фиг.7 «CLK», «CLKB», «D») и два выхода (см. Фиг.7 «QB», «Q»). Ds1, Ds2, Ds3, Dsm - соответственно, 1, 2, 3, m-тый статический D-триггер счетчика с вырабатываемыми на вторых выходах (см. Фиг.7 «Q») сигналами Qs1, Qs2, Qs3, Qsm, соответственно, 1, 2, 3, m-того статического D-триггера счетчика.

Первый вход (см. Фиг.7 «CLK») первого статического D-триггера - Ds1, являющийся первым входом счетчика 2 (см. Фиг.1 «CLK»), предназначен для соединения со вторым выходом триггера Шмитта 1 (см. Фиг.1 «OUTB»). Второй вход (см. Фиг.7 «CLKB») первого статического D-триггера - Ds1, являющийся вторым входом счетчика 2 (см. Фиг.1 «CLKB»), предназначен для соединения с первым выходом триггера Шмитта 1 (см. Фиг.1 «OUTB») и с затвором второго транзистора VT2 (см. Фиг.1), предназначенного для зарядки интегрирующей емкости C1. Третий вход (см. Фиг.7 «D») каждого статического D-триггера, Ds1-Dsm, соединен с первым выходом (см. Фиг.7 «QB») этого же статического D-триггера. Первый выход (см. Фиг.7 «QB») каждого статического D-триггера, кроме m-того, соединен с первым входом (см. Фиг.7 «CLK») следующего статического D-триггера. Второй выход (см. Фиг.7 «Q») каждого статического D-триггера, кроме m-того, соединен со вторым входом (см. Фиг.7 «CLKB») следующего статического D-триггера. Второй выход (см. Фиг.7 «CLKB») каждого статического D-триггера предназначен для соединения с m-разрядной шиной передачи данных - ШПД 4 (см. Фиг.1), с соответствием номера разряда шины номеру статического D-триггера, в совокупности формируя выход (см. Фиг.1 «Q») m-разрядного счетчика.

Каждый из m-тых статических D-триггеров выполнен на шестнадцати полевых транзисторах (см. Фиг.8). Первый, третий, пятый, седьмой, девятый, одиннадцатый, тринадцатый, и пятнадцатый транзисторы статического D-триггера, соответственно, VT23, VT25, VT27, VT29, VT31, VT33, VT35 и VT37 выполнены p-канальными и с возможностью подачи потенциала на их подложки, равного по величине рабочему напряжению. Второй, четвертый, шестой, восьмой, десятый, двенадцатый, четырнадцатый и шестнадцатый транзисторы статического D-триггера, соответственно, VT24, VT26, VT28, VT30, VT32, VT34, VT36 и VT38 выполнены n-канальными и с их подложками, закороченными на землю.

Исток первого транзистора статического D-триггера VT23 соединен с истоком второго транзистора статического D-триггера VT24. Между соединенными истоками выполнен третий вход статического D-триггера (см. Фиг.7 и Фиг.8 «D»). Сток первого транзистора статического D-триггера VT23 соединен с затвором третьего транзистора статического D-триггера VT25. Сток второго транзистора статического D-триггера VT24 соединен с затвором четвертого транзистора статического D-триггера VT26. Стоки первого и второго транзисторов, соответственно, VT23 и VT24, затворы третьего и четвертого транзисторов, соответственно, VT25 и VT26 статического D-триггера соединены друг с другом. Затворы первого, пятого, девятого, тринадцатого транзисторов статического D-триггера, соответственно, VT23, VT27, V31, VT35 соединены друг с другом и первым входом статического D-триггера (см Фиг.7 и Фиг.8 «CLK»). Затворы второго, шестого, десятого, четырнадцатого транзисторов статического D-триггера, соответственно, VT24, VT28, V32, VT36 соединены друг с другом и вторым входом статического D-триггера (см Фиг.7 и Фиг.8 «CLKB»). Исток третьего транзистора статического D-триггера VT25 выполнен с возможностью подачи на него потенциала, равного по величине рабочему напряжению. Сток третьего транзистора статического D-триггера VT25 соединен с истоком четвертого транзистора статического D-триггера VT26. Сток четвертого транзистора статического D-триггера VT26 выполнен с возможностью соединения его с точкой, в которой потенциал равен нулю. Исток пятого транзистора статического D-триггера VT27 соединен с истоком шестого транзистора статического D-триггера VT28. К соединенным истокам пятого и шестого транзисторов статического D-триггера, соответственно, VT27 и VT28 подсоединен затвор третьего транзистора статического D-триггера VT25. Сток пятого транзистора статического D-триггера VT27 соединен со стоком шестого транзистора статического D-триггера VT28. Исток седьмого транзистора статического D-триггера VT29 выполнен с возможностью подачи на него потенциала, равного по величине рабочему напряжению. Сток седьмого транзистора статического D-триггера VT29 соединен с истоком восьмого транзистора статического D-триггера VT30. Сток восьмого транзистора статического D-триггера VT30 выполнен с возможностью соединения его с точкой, в которой потенциал равен нулю. Затворы седьмого и восьмого транзисторов статического D-триггера, соответственно, VT29 и VT30 соединены друг с другом. Соединенные затворы седьмого и восьмого транзисторов статического D-триггера, соответственно, соответственно, VT29 и VT30 подсоединены между стоком третьего транзистора статического D-триггера VT25 и истоком четвертого транзистора статического D-триггера VT26. Между стоком седьмого транзистора статического D-триггера VT29 и истоком восьмого транзистора статического D-триггера VT30 подсоединены соединенные стоки пятого и шестого транзисторов статического D-триггера, соответственно, VT27 и VT28. Исток девятого транзистора статического D-триггера VT31 соединен с истоком десятого транзистора статического D-триггера VT32. Соединенные истоки девятого и десятого транзистора статического D-триггера, соответственно, VT31 и VT32 подсоединены между стоком седьмого транзистора статического D-триггера VT29 и истоком восьмого транзистора статического D-триггера VT30. Сток девятого транзистора статического D-триггера VT31 соединен с затвором одиннадцатого транзистора статического D-триггера VT33. Сток десятого транзистора статического D-триггера VT32 соединен с затвором двенадцатого транзистора статического D-триггера VT34. Стоки девятого и десятого транзисторов статического D-триггера, соответственно, VT31 и VT32, затворы одиннадцатого и двенадцатого транзисторов статического D-триггера, соответственно, VT33 и VT34 соединены друг с другом. Исток одиннадцатого транзистора статического D-триггера VT33 выполнен с возможностью подачи на него потенциала, равного по величине рабочему напряжению. Сток одиннадцатого транзистора статического D-триггера VT33 соединен с истоком двенадцатого транзистора статического D-триггера VT34. Сток двенадцатого транзистора статического D-триггера VT34 выполнен с возможностью соединения его с точкой, в которой потенциал равен нулю. Соединение стока одиннадцатого транзистора статического D-триггера VT33 и истока двенадцатого транзистора статического D-триггера VT34 выполнено с возможностью снятия сигнала, поступающего на второй выход статического D-триггера (см. Фиг.7 и Фиг.8 «Q»). Исток тринадцатого транзистора статического D-триггера VT35 соединен с истоком четырнадцатого транзистора статического D-триггера VT36. Между соединенными истоками тринадцатого и четырнадцатого транзисторов статического D-триггера, соответственно, VT35 и VT36 подсоединен затвор одиннадцатого транзистора статического D-триггера VT33. Сток тринадцатого транзистора статического D-триггера VT35 соединен со стоком четырнадцатого транзистора статического D-триггера VT36. Исток пятнадцатого транзистора статического D-триггера VT37 выполнен с возможностью подачи на него потенциала, равного по величине рабочему напряжению. Сток пятнадцатого транзистора статического D-триггера VT37 соединен с истоком шестнадцатого транзистора статического D-триггера VT38. Сток шестнадцатого транзистора статического D-триггера VT38 выполнен с возможностью соединения его с точкой, в которой потенциал равен нулю. Затворы пятнадцатого и шестнадцатого транзисторов статического D-триггера, соответственно, VT37 и VT38 соединены друг с другом. Соединенные затворы пятнадцатого и шестнадцатого транзисторов статического D-триггера, соответственно, VT37 и VT38 подсоединены между стоком одиннадцатого транзистора статического D-триггера VT33 и истоком двенадцатого транзистора статического D-триггера VT32. Между стоком пятнадцатого транзистора статического D-триггера VT37 и истоком шестнадцатого транзистора статического D-триггера VT38 подсоединены соединенные стоки тринадцатого и четырнадцатого транзисторов статического D-триггера, соответственно, VT35 и VT36 и выполнен первый выход статического D-триггера (см. Фиг.7 и Фиг.8 «QB»).

Устройство выполнено на полупроводниковой подложке.

Ячейка устройства считывания фотоприемных матриц с аналого-цифровым преобразованием функционирует следующим образом (см. Фиг.1-Фиг.3).

Смещение фотодиода VD1, являющегося фоточувствительным элементом фотоприемной матрицы, осуществляют посредством прямой инжекции. Посредством третьего транзистора VT3 задают смещение фотодиода VD1, его исток соединен с фотодиодом VD1, а сток соединен со второй обкладкой интегрирующей емкости С1 и с входом триггера Шмитта 1. Затвор третьего транзистора VT3 используют в качестве входа задания подпорогового режима транзистора (см. Фиг.1 «DI»). Напряжение DI выбирают экспериментальным образом. Ток фотодиода VD1 разряжает интегрирующую емкость С1 до тех пор, пока напряжение на ней - Uc1 не достигнет нижнего порога срабатывания триггера Шмитта 1 (см. Фиг.2 «Uc1»). После чего триггер Шмитта 1 вырабатывает на первом выходе (см. Фиг.1 «OUT») «логический 0» (см. Фиг.2 «CLKB») и открывает второй транзистор VT2. Посредством второго транзистора VT2 происходит зарядка интегрирующей емкости C1 до напряжения, соответствующего верхнему порогу срабатывания триггера Шмитта 1 (см. Фиг.2 «Uc1»). В результате на первом выходе триггера Шмитта 1 (см. Фиг.1 «OUT») устанавливается «логическая 1» (см. Фиг.2 «CLKB»). Далее акт интегрирования повторяется. Счетчик 2 считает число импульсов, вырабатываемых триггером Шмитта 1 (см. Фиг.2 «ШПД»). Число срабатываний триггера Шмитта 1 из m-разрядного счетчика 2 записывается в сдвиговый регистр 3

Акт интегрирования сигнала, поступающего с фоточувствительного элемента - фотодиода VD1, начинается в момент подачи сигнала STOP на затвор первого транзистора VT1, соответствующего «логическому 0» (см. Фиг.1 и Фиг.2 «STOP»). В результате подачи на затвор первого транзистора VT1 «логического 0» посредством первого и второго транзисторов, соответственно, VT1 и VT2 происходит зарядка интегрирующей емкости C1 (см. Фиг.1 и Фиг.2 «Uc1») до верхнего порога срабатывания триггера Шмитта 1 и на первом выходе триггера Шмитта 1 (см. Фиг.1 «OUT») устанавливается «логическая 1» (см. Фиг.2 «CLKB»). Второй транзистор VT2 запирается. Затем фототек начинает разряжать интегрирующую емкость C1 до напряжения нижнего порога срабатывания триггера Шмитта 1. По окончанию разрядки триггер Шмитта 1 вновь вырабатывает «логический 0», второй транзистор VT2 открывается, состояние счетчика 2 увеличивается на 1 (см. Фиг.2 «ШПД»). Далее акты интегрирования повторяются.

Запись числа актов интегрирования происходит при подаче на вход для подачи сигнала загрузки числа из счетчика 2 в сдвиговый регистр 3 (см. Фиг.1-4 «LOAD»), который в сдвиговом регистре 3 является входом для подачи сигнала загрузки числа из счетчика 2 в сдвиговый регистр 3 (см. Фиг.1 «S»), положительного импульса. Этот импульс подается когда на затворе первого транзистора VT1 сигнал STOP соответствует «логическому 0» (см. Фиг.1 и Фиг.2 «STOP») в целях предотвращения изменения значения счетчика 2.

Так как в частном случае реализации предлагаемого технического решения используются двухфазные триггеры для построения счетчика 2 и сдвигового регистра 3, то вывод данных осуществляется с помощью подачи на входы сдвигового регистра 3 - вход для подачи сигнала считывания информации из сдвигового регистра (см. Фиг.1 «CLK») и вход для подачи инвертированного сигнала считывания информации из сдвигового регистра (см. Фиг.1 «CLKB») сигналов READ, READB - сигналы считывания информации из сдвигового регистра, которые взаимно инверсны (см. Фиг.3). Вывод данных производится во время интегрирования последующего кадра, реализуя тем самым режим чтения во время записи. Также считывание может производиться в режиме чтения после записи.

В момент подачи сигнала STOP на затвор первого транзистора VT1, соответствующего «логической 1» (см. Фиг.1 и Фиг.2 «STOP»), значение напряжения Uc1 интегрирующей емкости C1 фиксируется и остается зафиксированным до подачи сигнала STOP на затвор первого транзистора VT1, соответствующего «логическому 0» (см. Фиг.1 и Фиг.2 «STOP»), что соответствует остановке счета. В момент подачи на затвор первого транзистора VT1 «логического 0», счет возобновляется, осуществляются циклы актов интегрирования, счет и запись. Происходит изменение состояния сдвигового регистра 3, что отражает на диаграмме сигнал SRG (см. Фиг 2 «SRG»).

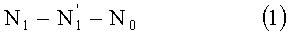

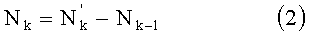

Для уменьшения числа транзисторов в счетчике отсутствует сброс. Таким образом, число срабатываний триггера Шмитта определяется следующим:

,

,

где N0 - значение счетчика после подготовительных кадров;

- значение счетчика после первого кадра;

- значение счетчика после первого кадра;

N1 - число срабатываний триггера Шмитта за первый кадр;

Nk-1 - значение счетчика после предыдущего кадра;

- значение счетчика после текущего кадра;

- значение счетчика после текущего кадра;

Nk - число срабатываний триггера Шмитта за текущий кадр.

Данное решение можно использовать в матрицах КИС. Таким образом, сдвиговый регистр соседних ячеек соединяется воедино, пронизывая весь чип по вертикали.