Результат интеллектуальной деятельности: ИНТЕГРАЛЬНАЯ СХЕМА ЗАДЕРЖКИ ВКЛЮЧЕНИЯ

Вид РИД

Изобретение

Предлагаемое изобретение относится к импульсной технике и может быть использовано для задержки включения нагрузки.

Известна схема задержки включения, содержащая интегрирующую R-C цепочку, выход которой соединен с базой транзистора, при этом нагрузка включена в коллекторную цепь транзистора [1].

Однако это устройство имеет недостаточную температурную стабильность времени задержки из-за существенной температурной зависимости порога включения биполярного транзистора.

Известен интегральный формирователь, содержащий латеральный транзистор p-n-р типа с дополнительной областью р-типа, расположенной внутри изолированного n-кармана данного транзистора между его коллектором и границей изолирующей области [2].

Однако использование латерального транзистора с дополнительной областью р-типа в известном устройстве приводит к некоторому увеличению площади на кристалле.

Наиболее близкой к предлагаемому изобретению по технической сущности и достигаемому результату является интегральная схема задержки включения, содержащая входной транзистор p-n-р типа и выходной транзистор n-p-n типа с нагрузкой в цепи коллектора, база входного транзистора подключена к токозадающей цепи, эмиттер соединен с шиной питания, а коллектор соединен с первым выводом конденсатора, второй вывод конденсатора и эмиттер выходного транзистора соединены с общей шиной, база выходного транзистора соединена с первым выводом резистора [3].

Однако известная интегральная схема задержки включения имеет повышенную мощность потребления, работоспособна в узком диапазоне изменения напряжения питания и имеет увеличенную площадь на кристалле из-за наличия схемы сравнения и источника опорного напряжения.

Техническим результатом предлагаемого изобретения является уменьшение площади, занимаемой схемой задержки включения на кристалле, уменьшение потребляемой мощности и расширение диапазона изменения напряжения питания.

Заявленный технический результат достигается тем, что в известной интегральной схеме задержки включения, содержащей входной транзистор p-n-р типа и выходной транзистор n-p-n типа с нагрузкой в цепи коллектора, база входного транзистора подключена к токозадающей цепи, эмиттер соединен с шиной питания, а коллектор соединен с первым выводом конденсатора, второй вывод конденсатора и эмиттер выходного транзистора соединены с общей шиной, база выходного транзистора соединена с первым выводом резистора, входной транзистор выполнен в виде латеральной структуры с дополнительной областью р-типа, которая расположена внутри изолированного n-кармана входного транзистора между его коллектором и границей изолирующей области данного n-кармана, при этом дополнительная область подключена к базе выходного транзистора, а второй вывод резистора соединен с общей шиной.

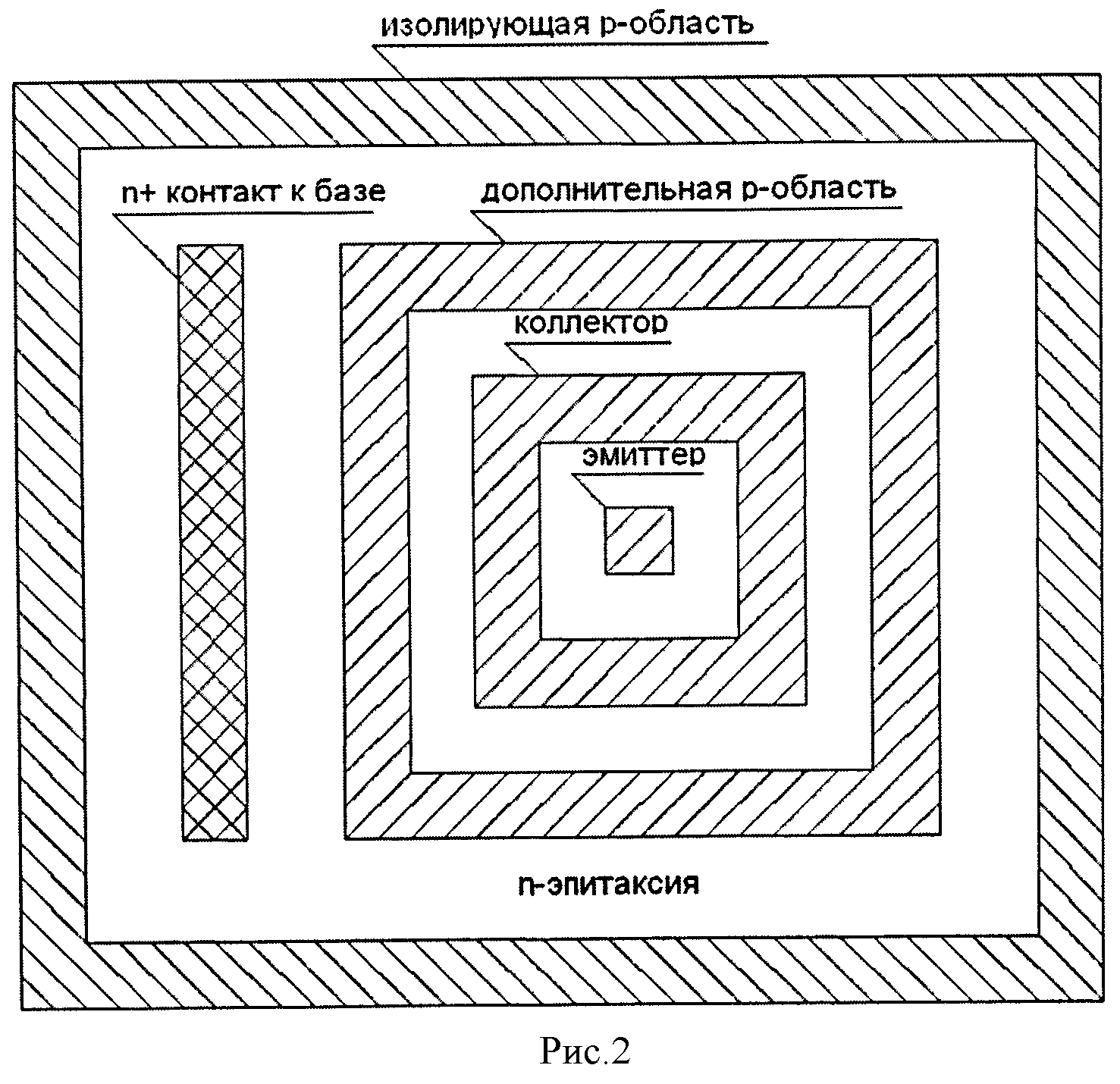

На рис.1 представлена эквивалентная электрическая схема предлагаемой интегральной схемы задержки включения.

Эквивалентная электрическая схема интегральной схемы задержки включения содержит входной транзистор 1, выходной транзистор 2, нагрузку 3, токозадающую цепь 4, шину 5 питания, конденсатор 6, общую шину 7, резистор 8 и дополнительный транзистор 9.

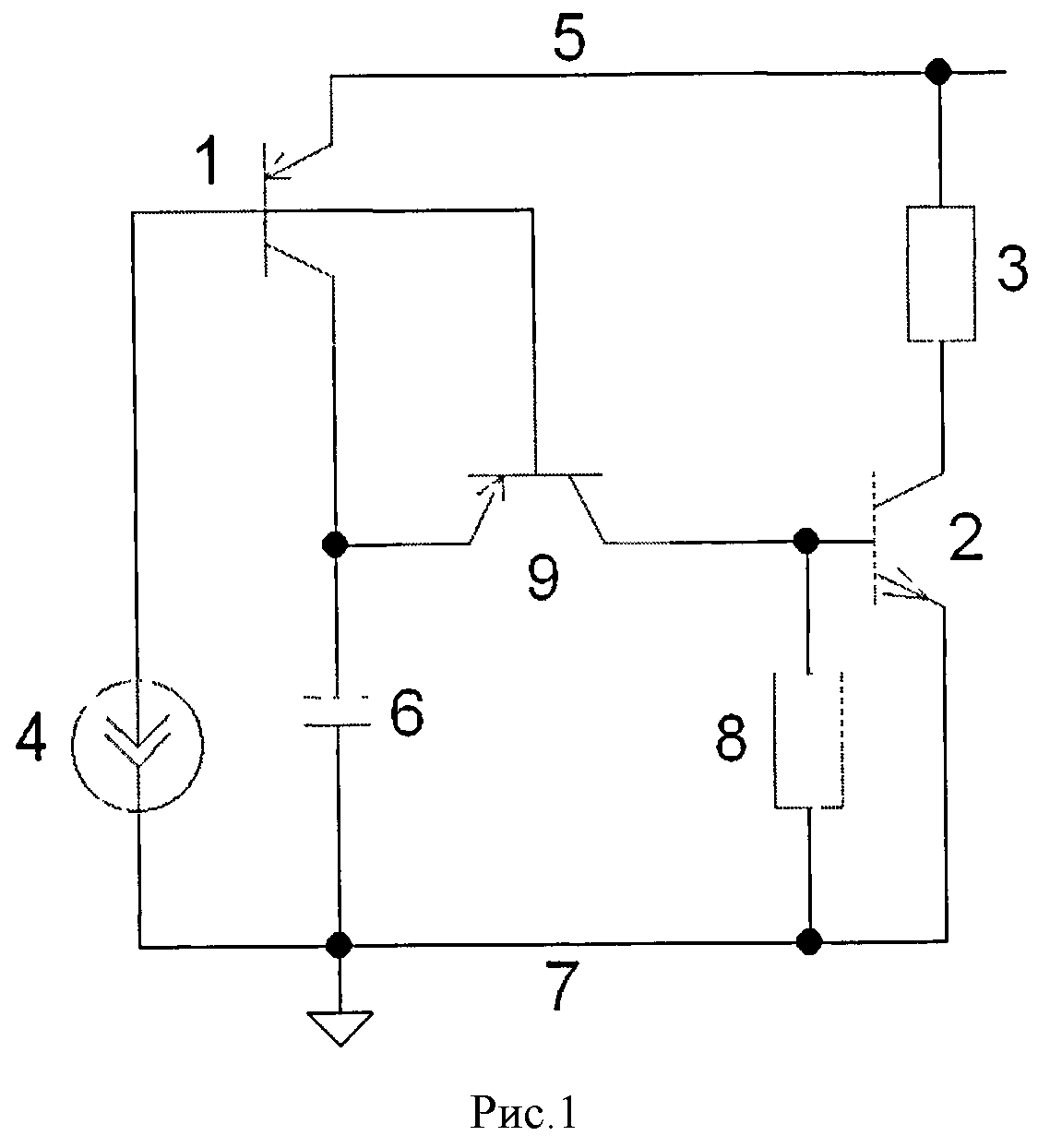

На рис.2 представлена конструкция входного транзистора p-n-p-типа с дополнительной областью р-типа.

Входной транзистор 1 выполнен в изолированном n-кармане, в котором расположены n+-область для подключения базового контакта, р-области эмиттера, коллектора и дополнительная р-область.

Данную конструкцию можно рассматривать как два p-n-р латеральных транзистора, расположенных в одной базовой n-области: входной транзистор (его эмиттер и коллектор обозначены на рис.2) и дополнительный транзистор, роль эмиттера которого выполняет коллектор входного транзистора, а роль коллектора - дополнительная р-область.

Интегральная схема задержки включения работает следующим образом. В исходном состоянии конденсатор 6 разряжен. При включении питания входной транзистор 1 начинает работать в активном режиме, и его коллекторный ток заряжает конденсатор 6. Дополнительная р-область смещена обратно, и ее ток практически равен нулю. Можно говорить, что дополнительный транзистор 9 работает в режиме отсечки. Резистор 8 замыкает на общую шину 7 незначительный паразитный ток, протекающий непосредственно от эмиттера входного транзистора 2 к дополнительной р-области. На стадии заряда конденсатора 6 выходной транзистор 2 заперт, и ток в нагрузке 3 отсутствует.

Конечное значение напряжения на конденсаторе 6 достигается, когда входной транзистор 1 переходит в режим насыщения. При этом открытый коллекторный переход начинает инжекцию неосновных носителей в направлении дополнительной р-области, и ток коллектора дополнительного транзистора 9 резко возрастает. Таким образом, после насыщения входного транзистора 1 можно считать, что дополнительный транзистор 9 переходит в активный режим. Выходной транзистор 2 отпирается, и в нагрузке 3 появляется ток.

Предложенная интегральная схема работоспособна в диапазоне напряжения питания, ограниченном лишь пробивными напряжениями активных элементов схемы.

Потребляемая мощность в предложенной интегральной схеме снижена за счет исключения опорного источника напряжения и схемы сравнения.

Можно считать, что роль источника опорного напряжения выполняет источник питания, а функции схемы сравнения - дополнительный транзистор 9, коллектор которого является выходом схемы сравнения. Действительно, коллекторный ток дополнительного транзистора 9 появляется в момент, когда напряжение на коллекторе входного транзистора 1 сравнивается с напряжением на шине 5 питания.

Исключение физических элементов схемы сравнения и опорного источника позволяет уменьшить площадь на кристалле.

Время задержки включения и для прототипа, и для предложенного технического решения определяется одним соотношением:

tЗД≈С·ΔU/I,

где C - емкость конденсатора, I - ток коллектора входного транзистора, ΔU -перепад напряжения на конденсаторе от начального значения U0 (для обеих схем можно считать, что U0≈0) до конечного U1, при котором появляется выходной сигнал. В прототипе U1 - напряжение опорного источника (U1 составляет часть питающего напряжения), в заявленном техническом решении U1 практически равно напряжению на шине 5 питания, поэтому при прочих равных условиях в заявленном техническом решении достигается большее время задержки, чем в прототипе. С другой стороны, для получения заданного времени задержки включения в предложенной схеме можно уменьшить емкость конденсатора и, следовательно, при реализации конденсатора в виде интегрального элемента достигается дополнительный выигрыш в площади на кристалле.

Новизна предлагаемого изобретения заключается в том, что в интегральной схеме задержки включения входной транзистор выполнен в виде латеральной структуры с дополнительной областью р-типа, которая расположена внутри изолированного n-кармана входного транзистора между его коллектором и границей изолирующей области данного n-кармана, при этом дополнительная область подключена к базе выходного транзистора, а второй вывод резистора соединен с общей шиной.

Технический результат предлагаемого изобретения реализуется лишь при совокупном использовании его отличительных признаков.

Важно заметить, что выполнение дополнительного транзистора 9 в отдельном изолированном кармане приведет к появлению проблемы согласования параметров входного и дополнительного транзисторов и не позволит добиться достаточного и воспроизводимого коэффициента передачи тока эмиттера входного транзистора 1 в цепь коллектора дополнительного транзистора 9. Иными словами, выходной ток «схемы сравнения» в этом случае непредсказуем, и практическое применение такой схемы напрямую невозможно. Именно в предложенной конструкции эмиттерный ток входного транзистора 1 практически без потерь передается в коллекторную цепь дополнительного транзистора 9. Этим можно проиллюстрировать неочевидность для специалистов предлагаемого изобретения.

Следовательно, предлагаемое изобретение неизвестно из уровня техники и соответствует критерию изобретательский уровень. Источники информации

1. httphttp://www.autosecret.net/tuning/elektro-tuning/1119-zaderzhka-vkljuchenija-rele

2. Описание изобретения к патенту РФ №2474044, H03K 5/01.

3. httphttp://madelectronics.ru/gadget/302/4.13.htm

Интегральная схема задержки включения, содержащая входной транзистор p-n-р типа и выходной транзистор n-p-n типа с нагрузкой в цепи коллектора, база входного транзистора подключена к токозадающей цепи, эмиттер соединен с шиной питания, а коллектор соединен с первым выводом конденсатора, второй вывод конденсатора и эмиттер выходного транзистора соединены с общей шиной, база выходного транзистора соединена с первым выводом резистора, отличающаяся тем, что входной транзистор выполнен в виде латеральной структуры с дополнительной областью р-типа, которая расположена внутри изолированного n-кармана входного транзистора между его коллектором и границей изолирующей области данного n-кармана, при этом дополнительная область подключена к базе выходного транзистора, а второй вывод резистора соединен с общей шиной.