Результат интеллектуальной деятельности: ЦИФРО-АНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ

Вид РИД

Изобретение

Предлагаемое изобретение относится к области измерительной и вычислительной техники, радиотехники, связи и может использоваться в структуре различных устройств обработки информации, измерительных приборах, системах телекоммуникаций и т.п.

В современной технике широкое применение находят цифроаналоговые преобразователи (ЦАП), работа которых основана на коммутации и суммировании n-опорных (весовых) токов, изменяющихся по закону 2nI0, где I0 - квант тока, n - разрядность ЦАП. Дальнейшее повышение быстродействия таких ЦАП - одна из проблем современной информационно-измерительной техники, решение которой позволит осуществить практическую реализацию новых систем связи и телекоммуникаций с более высокими качественными показателями.

Наиболее близким по технической сущности к заявляемому устройству является ЦАП, описанный в книге Воловича Г.И. Схемотехника аналоговых и аналого-цифровых электронных устройств. 2-е изд., испр. - М.: Издательский дом «Додэка-ХХ1», 2007. - С.397, рис.8.126. По данной архитектуре реализованы микросхемы ЦАП ряда ведущих микроэлектронных фирм [1-7], например AD7520, AD565, 572ПА1, МАХ555, 11 18ПА6, AD9750, TUIS5671, DAC904 и др.

ЦАП-прототип фиг.1 содержит блок коммутации весовых токов 1, токовый выход которого 2 связан с эталонным резистором 3, паразитный конденсатор 4, связанный с токовым выходом 2 блока коммутации весовых токов 1.

Существенный недостаток ЦАП-прототипа (фиг.1), функциональные схемы включения которого показаны на чертежах фиг.2, фиг.3, состоит в том, что предельная частота смены его входного кода ограничена, что обусловлено шунтирующим влиянием емкости (С4) паразитного конденсатора 4, связанного с токовым выходом 2 ЦАП. Для ряда современных ЦАП численное значение этой емкости достигает 20÷120 пФ (AD7520 - С4=30÷120 пФ, AD565 - С4=25 пФ и т.п.).

Действительно, при идеальных элементах коммутации (K1, К2,…, К4) весовых токов максимальная частота смены входного кода ЦАП-прототипа фиг.1 (фиг.2), являющаяся одним из параметров ЦАП, а также время установления переходного процесса (tуст) выходного напряжения ЦАП не удовлетворяют многим применениям:

где С4 - емкость паразитного конденсатора 4;

R3 - сопротивление эталонного резистора 3.

Основная задача предлагаемого изобретения состоит в увеличении предельной частоты смены входного кода ЦАП (частоты обновления) и снижении влияния паразитного конденсатора 4 на переходные процессы - уменьшении времени установления выходного напряжения ЦАП.

Поставленная задача достигается тем, что в цифроаналоговом преобразователе фиг.1, содержащем блок коммутации весовых токов 1, токовый выход которого 2 связан с эталонным резистором 3, паразитный конденсатор 4, связанный с токовым выходом 2 блока коммутации весовых токов 1, предусмотрены новые элементы и связи - с целью повышения быстродействия токовый выход 2 блока коммутации весовых токов 1 соединен со входом неинвертирующего усилителя напряжения 5 и токовым выходом 6 неинвертирующего усилителя тока 7, причем между выходом неинвертирующего усилителя напряжения 5 и токовым входом 8 неинвертирующего усилителя тока 7 включен элемент частотной коррекции 9.

На чертеже фиг.1 приведена принципиальная, а на чертеже фиг.2 - функциональная схемы ЦАП-прототипа.

На чертеже фиг.3 также представлена функциональная схема другого типового варианта включения ЦАП фиг.2, в котором его выход 2 согласован с инвертирующим преобразователем «ток-напряжение» на основе операционного усилителя (ОУ). Данное схемотехническое решение широко используется в информационно-измерительной и вычислительной технике [Волович Г.И. Схемотехника аналоговых и аналого-цифровых электронных устройств. 2-е изд., испр. - М.: Издательский дом «Додэка-ХХ1», 2007. - С.397, рис.8.12а]. Однако для многих применений оно неэффективно из-за повышенных требований к быстродействию операционного усилителя, стоимость которого оказывается значительно выше стоимости ЦАП.

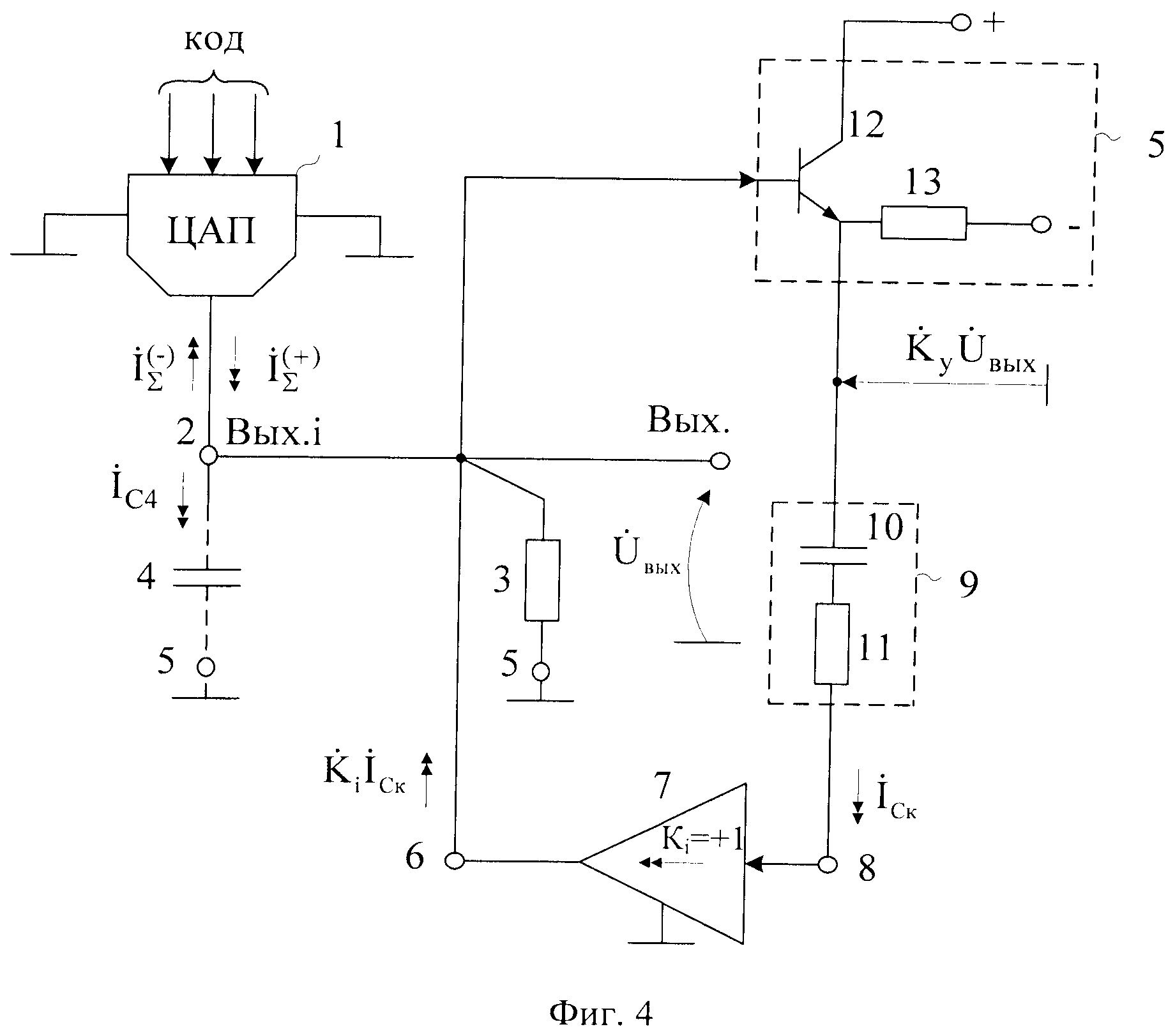

На чертеже фиг.4 представлена схема заявляемого устройства в соответствии с формулой изобретения.

На чертеже фиг.5 приведена эквивалентная схема ЦАП-прототипа фиг.2 в среде PSpice, а на чертеже фиг.6 показаны результаты компьютерного моделирования переходных процессов выходного напряжения ЦАП фиг.5 при разных значениях емкости паразитного конденсатора С4=Ск=Cvar=5÷20 пФ, сопротивлении эталонного 3 резистора R3=2 кОм и скачке выходного тока ЦАП ΔI=64 мкА, обусловленного сменой входного кода.

На чертеже фиг.7 приведены результаты компьютерного моделирования переходных процессов выходного напряжения ЦАП фиг.5 при разных значениях емкости паразитного конденсатора С4=Ск=0÷20 пФ, скачке выходного тока ЦАП ΔI=64 мкА, но более высоких значениях сопротивления эталонного резистора 3 (R2=100 кОм).

Для сравнения предельных возможностей второй типовой схемы включения ЦАП фиг.3 на чертеже фиг.8 в среде PSpice представлена эквивалентная схема ЦАП фиг.3, выход которого 2 подключается ко входу реального (т.е. инерционного) преобразователя «ток-напряжение» на основе ОУ, содержащего входной каскад с коэффициентом усиления Ку=1000, элементы частотной коррекции R1, C3 и буферный усилитель с Ку=1.

На чертеже фиг.9 приведены результаты компьютерного моделирования переходных процессов выходного напряжения ЦАП фиг.8 при значении емкости паразитного конденсатора C4=C1=20 пФ, скачке выходного тока ЦАП ΔI=64 мкА и емкости корректирующего конденсатора в структуре операционного усилителя С3=10 нФ, обеспечивающего перерегулирование переходного процесса 30,3%. При этом время установления переходного процесса равно tуст=190 нс.

На чертеже фиг.10 приведены результаты компьютерного моделирования переходных процессов выходного напряжения ЦАП фиг.8 при значении емкости паразитного конденсатора C4=C1=20 пФ, скачке выходного тока ЦАП ΔI=64 мкА и емкости корректирующего конденсатора в структуре операционного усилителя С3=55 нФ, обеспечивающего «нулевое» перерегулирование переходного процесса. При этом время установления переходного процесса равно tуст=210 нс. Сравнение графиков фиг.6, фиг.7 и графиков фиг.9, фиг.10 показывает, что известные схемотехнические решения ЦАП не обеспечивают высокого быстродействия - их время установления достаточно велико: tуст≥95÷210 нс.

На чертеже фиг.11 показана эквивалентная схема заявляемого ЦАП фиг.4 в среде Pspice на моделях транзисторов ФГУП НПП «Пульсар».

На чертеже фиг.12 приведены результаты компьютерного моделирования переходных процессов выходного напряжения ЦАП фиг.11 при емкости паразитного конденсатора С4=С1=20 пФ, сопротивлении эталонного резистора 3 R3=R1=2 кОм, скачке выходного тока ЦАП А1=64 мкА и разных значениях емкости корректирующего конденсатора 10 в структуре элемента частотной коррекции 9 (С10=Ск=С5=Cvar=0÷19.5 пФ). Из данных графиков следует, что предлагаемое техническое решение обеспечивает уменьшение времени установления переходного процесса выходного напряжения ЦАП фиг.11 более чем в 30 раз - с 95 нс до 2,6 нс.

Цифроаналоговый преобразователь фиг.4 содержит блок коммутации весовых токов 1, токовый выход которого 2 связан с эталонным резистором 3, паразитный конденсатор 4, связанный с токовым выходом 2 блока коммутации весовых токов 1. С целью повышения быстродействия токовый выход 2 блока коммутации весовых токов 1 соединен со входом неинвертирующего усилителя напряжения 5 и токовым выходом 6 неинвертирующего усилителя тока 7, причем между выходом неинвертирующего усилителя напряжения 5 и токовым входом 8 неинвертирующего усилителя тока 7 включен элемент частотной коррекции 9.

На чертеже фиг.4, в соответствии с п.2 формулы изобретения, элемент частотной коррекции 9 может быть выполнен в виде конденсатора 10.

На чертеже фиг.4, в соответствии с п.3 формулы изобретения, элемент частотной коррекции 9 может быть также выполнен в виде последовательно соединенных резистора 11 и конденсатора 10.

В схеме фиг.4 неинвертирующий усилитель напряжения 5 реализован на транзисторе 12 и вспомогательном транзисторе 13.

Рассмотрим работу ЦАП фиг.4.

Изменение выходного тока ЦАП при отсутствии неинвертирующего усилителя напряжения 5 и неинвертирующего усилителя тока 7 приводит к увеличению его выходного напряжения Uвых. При этом конденсатор 4 заряжается током Ic4 с постоянной времени, которая определяется элементами схемы 4 и 3 (см. формулу (1)).

Введение неинвертирующего усилителя напряжения 5 и неинвертирующего усилителя тока 7 качественно изменяет работу схемы. Теперь напряжение Uвых передается на выход неинвертирующего усилителя напряжения 5, что создает ток İск через элемент частотной коррекции 9. Данный ток поступает на вход 8 неинвертирующего усилителя тока 7 и создает дополнительный ток в выходной цепи ЦАП Iдоп=Кiİск, который способствует более быстрому перезаряду конденсатора 4. В конечном итоге это приводит к существенному уменьшению времени установления переходного процесса выходного напряжения ЦАП (фиг.12).

Если в качестве элемента частотной коррекции 9 используется только конденсатор 10, то для обеспечения работоспособности схемы необходимо выполнение условий:

Можно достаточно строго аналитически показать, что схема фиг.4 при выполнении условий (2) устойчива с учетом типовых инерционностей неинвертирующего усилителя напряжения 5 и неинвертирующего усилителя тока 7.

Таким образом, заявляемый ЦАП характеризуется существенными преимуществами в сравнении с прототипом по частоте смены входного кода и времени установления переходного процесса выходного напряжения. В предлагаемой схеме решена одна из проблем повышения быстродействия конкретного подкласса цифроаналоговых преобразователей.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 5.307.067 fig. 13

2. Патент US 4.774.498 fig. 2

3. Патент US 5.396.131 fig. 10

4. Патент US 5.376.937 fig. 3

5. Патент US 6.445.221 fig. 2

6. Аналоговые интегральные схемы: Элементы, схемы, системы и применения /под ред. Дж. Коннели. - М.: «Мир», 1977, с.337, рис.8.9.

7. Карки Джим. Сопряжение операционных усилителей со скоростным ЦАП. Глава 1. ЦАП с токовым выходом // Компоненты и технологии. -2010. - №12, www.kit-e.ru/articles/dac/2010_12_111.php