Результат интеллектуальной деятельности: БОРТОВОЙ СПЕЦВЫЧИСЛИТЕЛЬ

Вид РИД

Изобретение

Изобретение относится к области вычислительной техники, в частности к устройствам, выполняющим операцию быстрого преобразования Хартли (БПХ) массива действительных чисел. Изобретение может быть использовано в системах и устройствах цифровой обработки сигналов.

Известно устройство для быстрого действительного преобразования Хартли - Фурье [1].

Недостатком устройства является сложность аппаратной реализации недостаточное быстродействие из-за временных затрат на проведение операции двоично-инверсной перестановки входной информации.

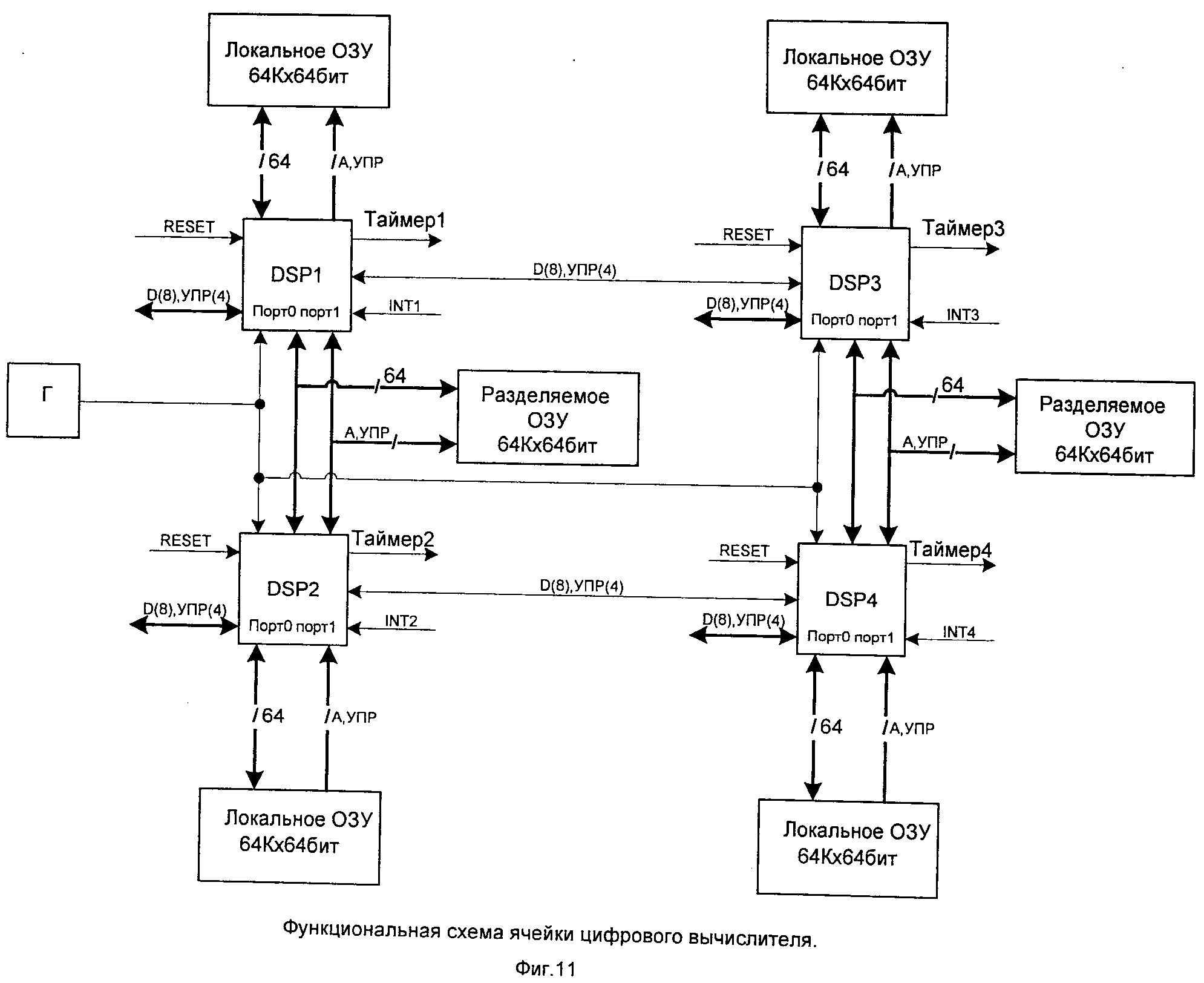

Наиболее близким по технической сущности к изобретению является устройство цифровой обработки радиолокационных сигналов на основе процессора Л1879 ВМ1 [2], содержащее первый процессор DSP, второй процессор DSP, третий процессор DSP, четвертый процессор DSP, первое локальное ОЗУ, второе локальное ОЗУ, третье локальное ОЗУ, четвертое локальное ОЗУ, первое разделяемое ОЗУ, второе разделяемое ОЗУ, генератор, а ячейка контроллера мультиплексного канала состоит из процессора DSP, локальное ОЗУ, первый контроллер мультиплексного канала, второй контроллер мультиплексного канала, третий контроллер мультиплексного канала, четвертый контроллер мультиплексного канала, генератор, первый усилитель, второй усилитель, третий усилитель, четвертый усилитель, первый трансформатор, второй трансформатор, третий трансформатор, четвертый трансформатор.

Описанное устройство как наиболее близкое к предлагаемому принято за прототип и представлено на фиг.11.

Недостатком устройства является сложность аппаратной реализации, высокий уровень шума.

Задачей изобретения является сокращение аппаратуры, снижение уровня шума и расширение функциональных возможностей.

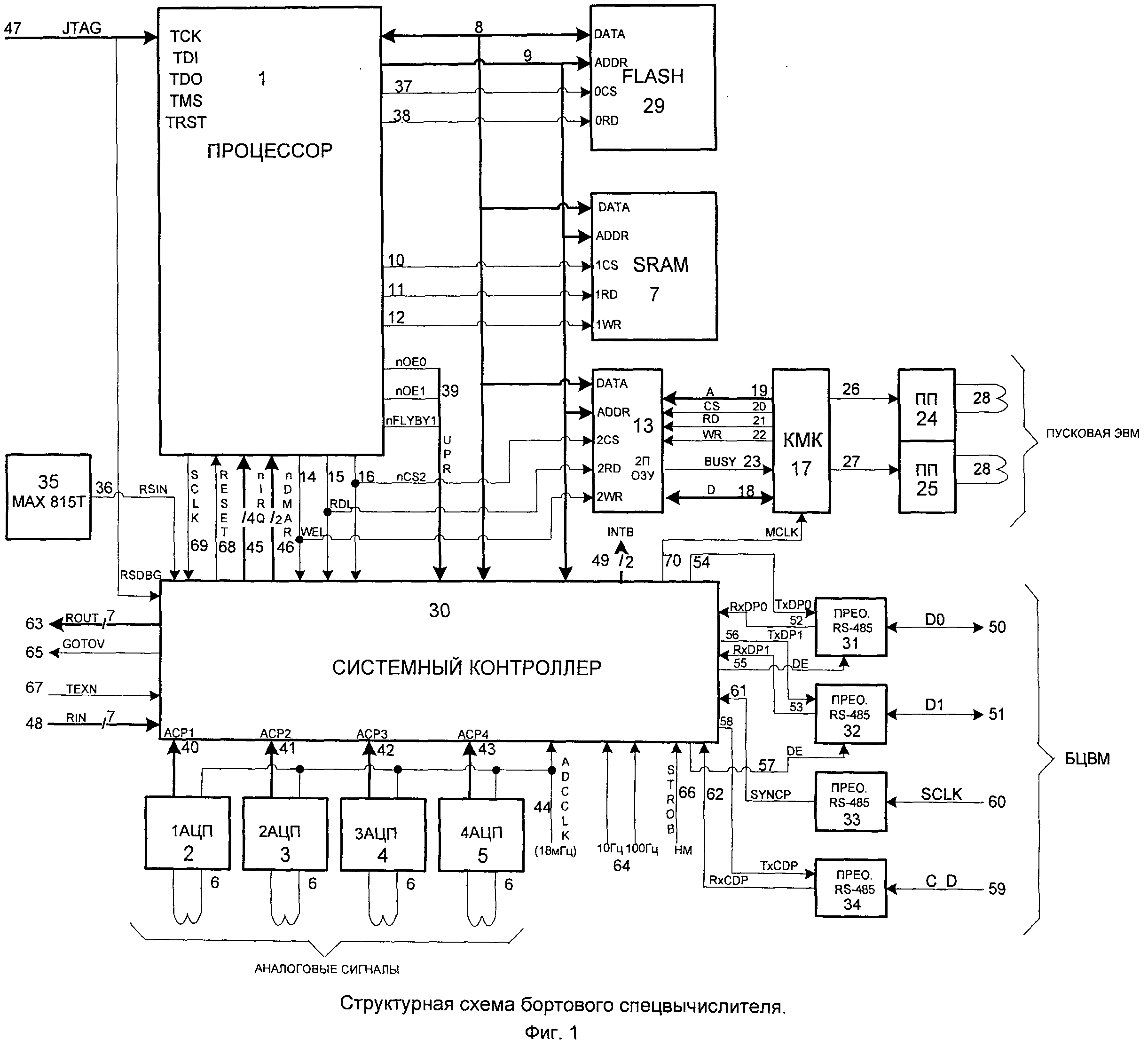

Сущность заявляемого изобретения, возможность его осуществления и промышленного использования поясняются чертежами, представленными на фиг.1…фиг.10, фиг.12…фиг.23, где:

- на фиг.1 представлена структурная схема бортового спецвычислителя;

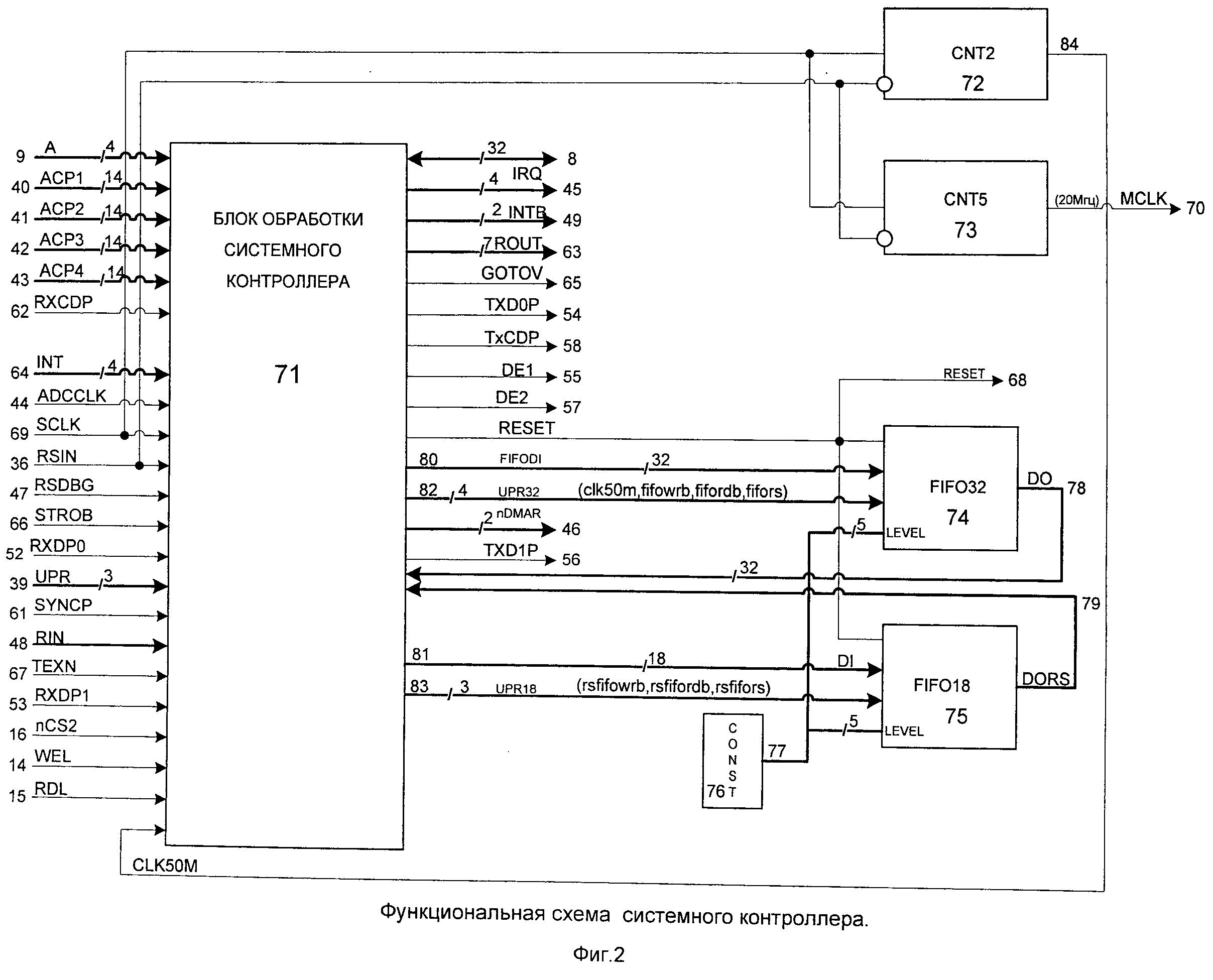

- на фиг.2 представлена функциональная схема системного контроллера;

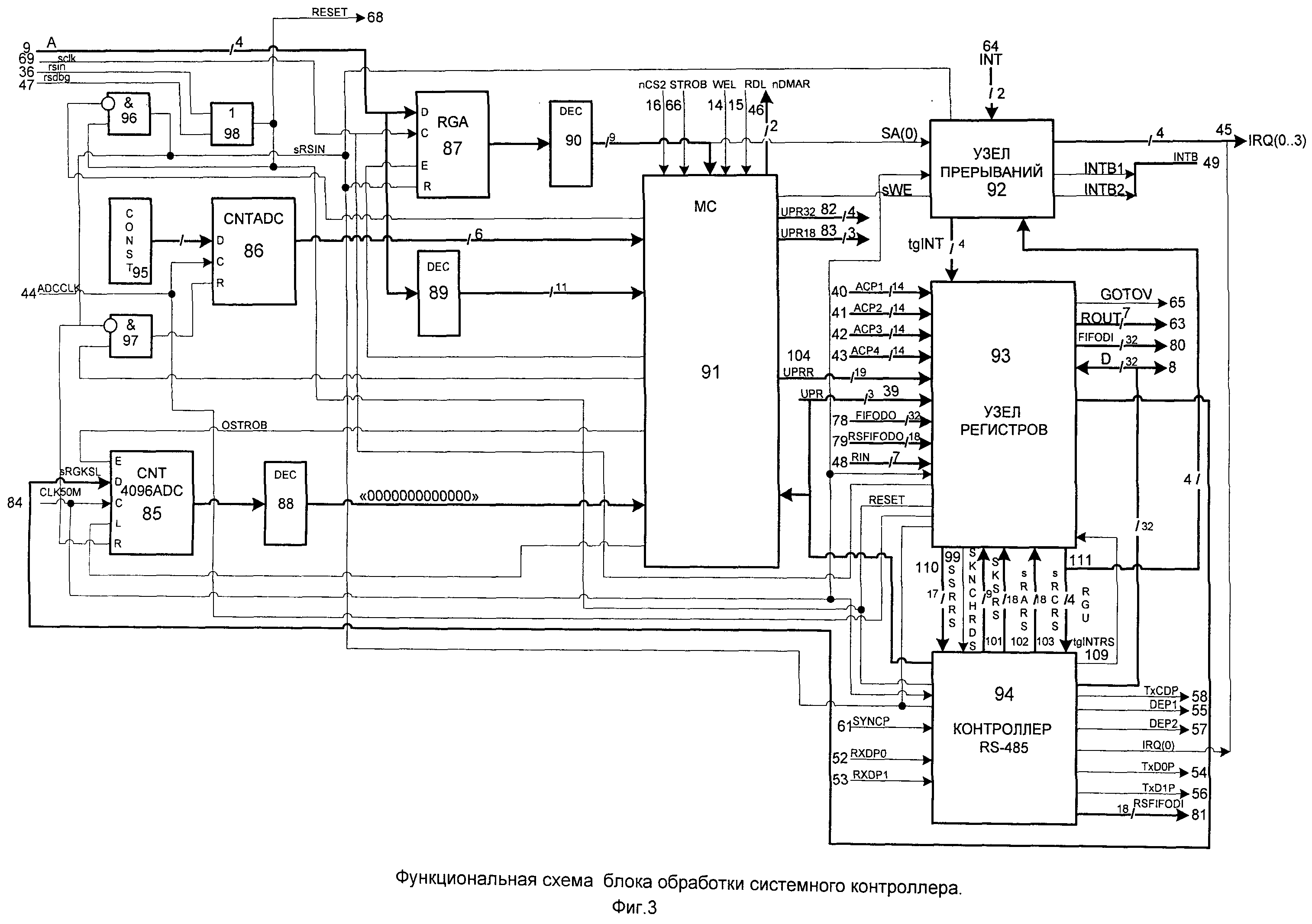

- на фиг.3 представлена функциональная схема блока обработки системного контроллера;

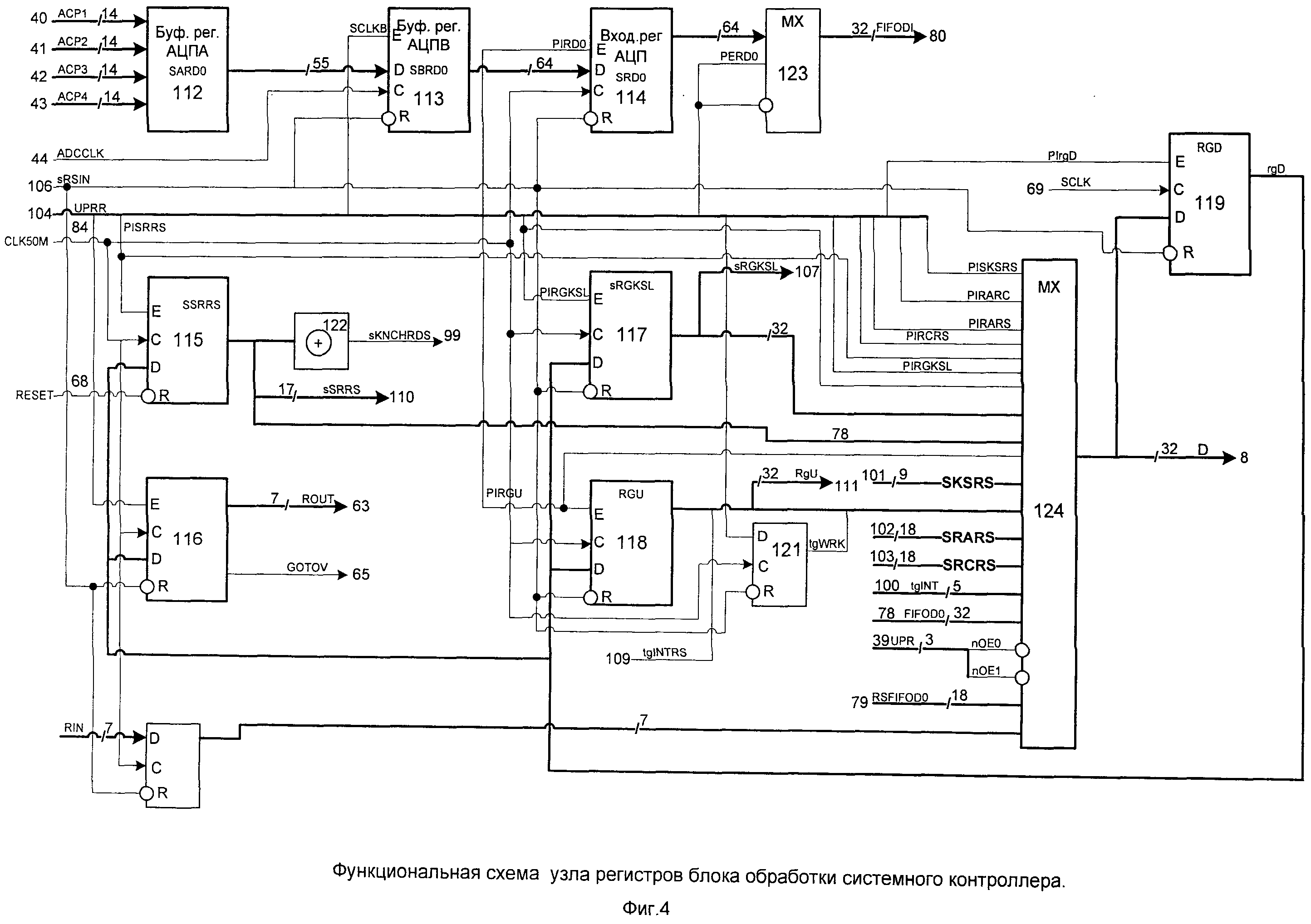

- на фиг.4 представлена функциональная схема узла регистров блока обработки системного контроллера;

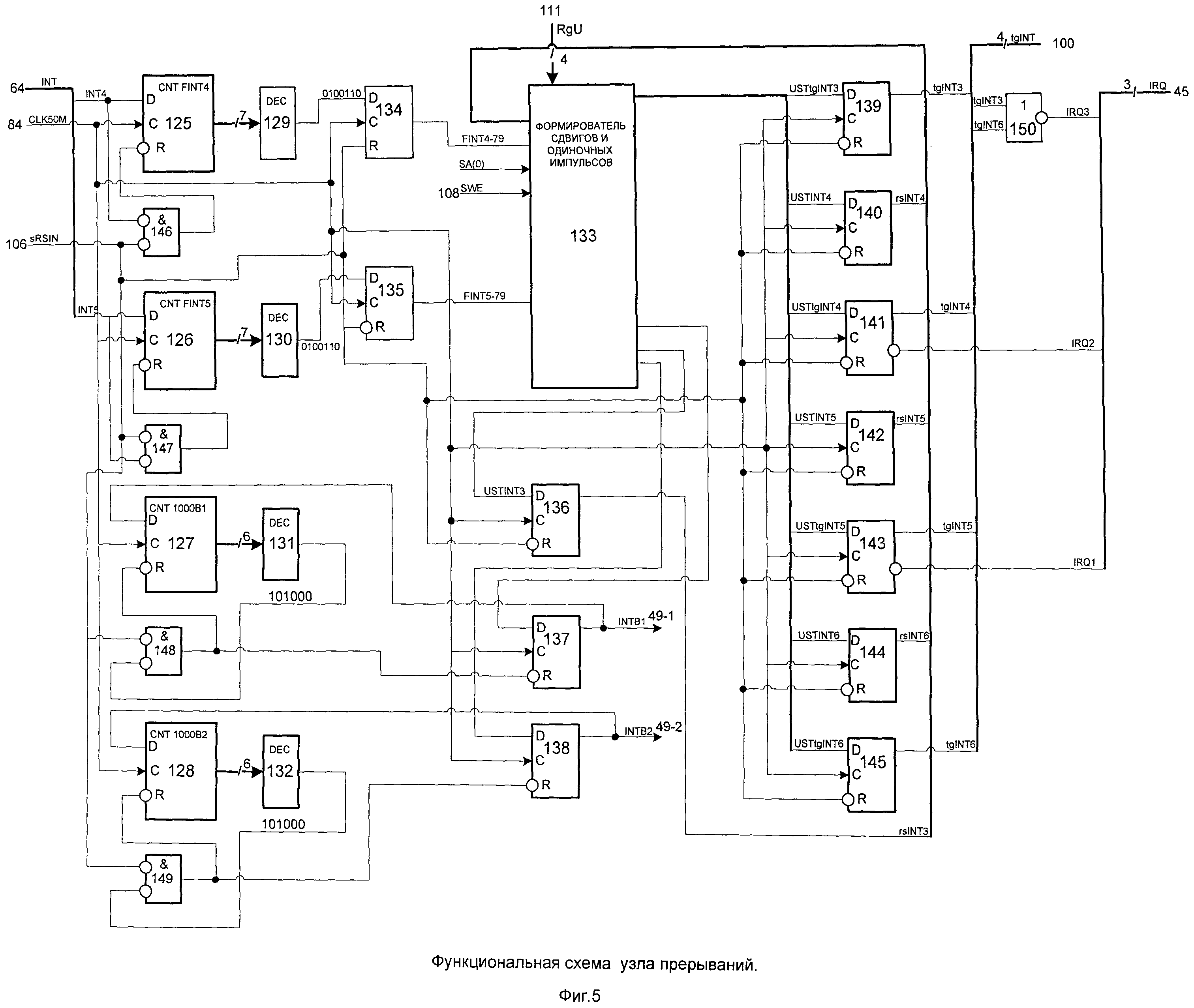

- на фиг.5 представлена функциональная схема узла прерываний;

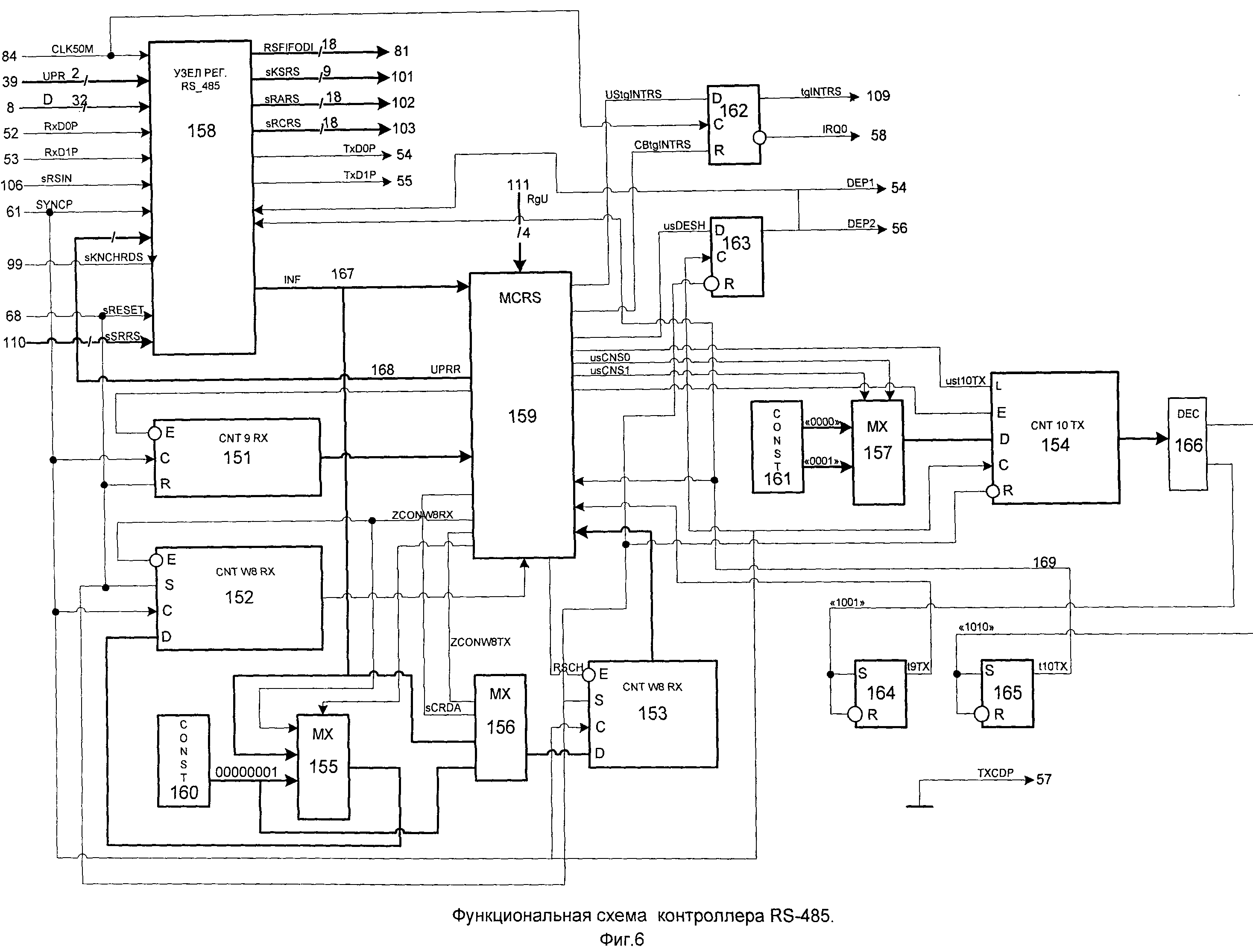

- на фиг.6 представлена функциональная схема контроллера RS-485;

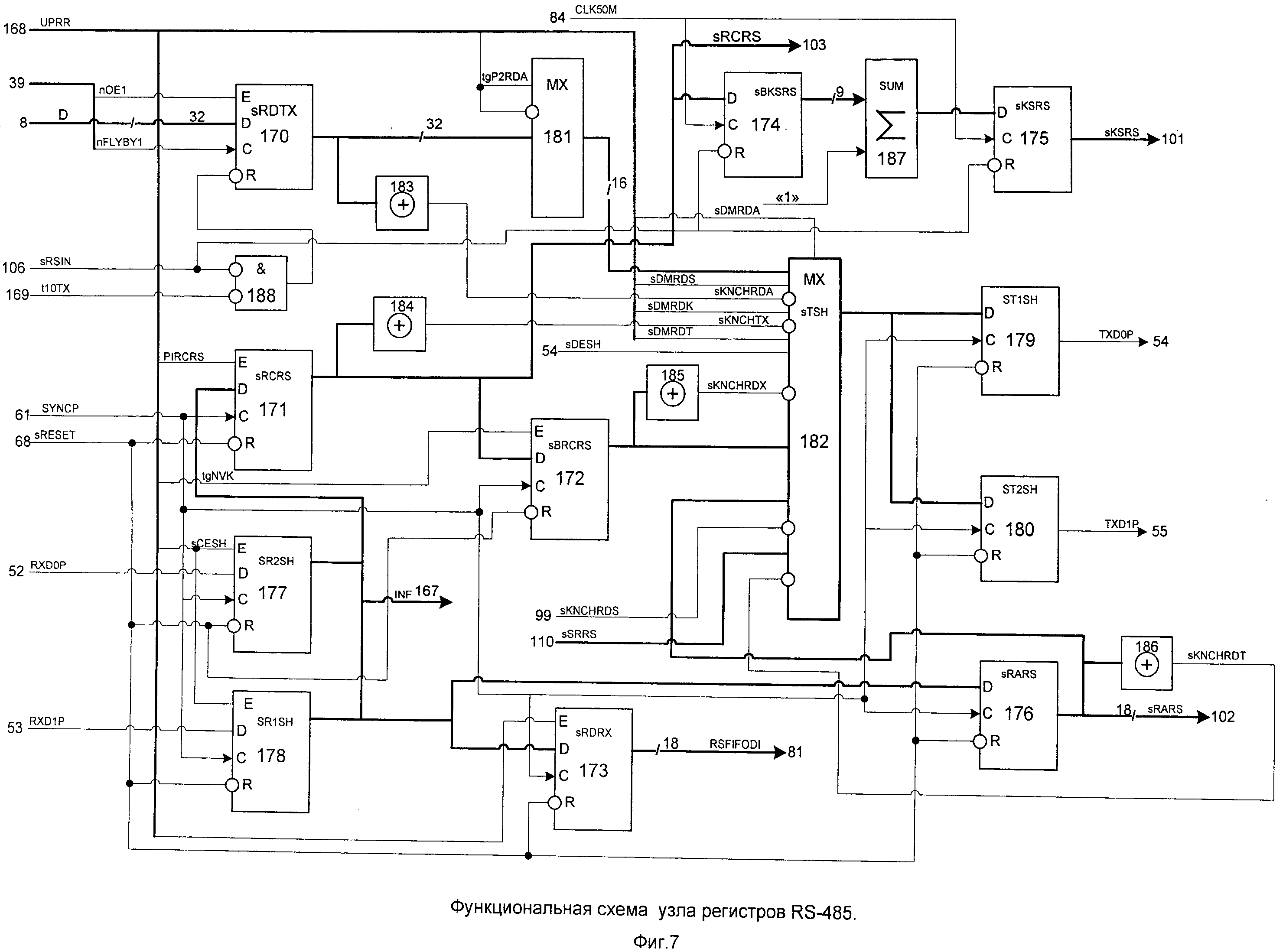

- на фиг.7 представлена функциональная схема узла регистров RS-485;

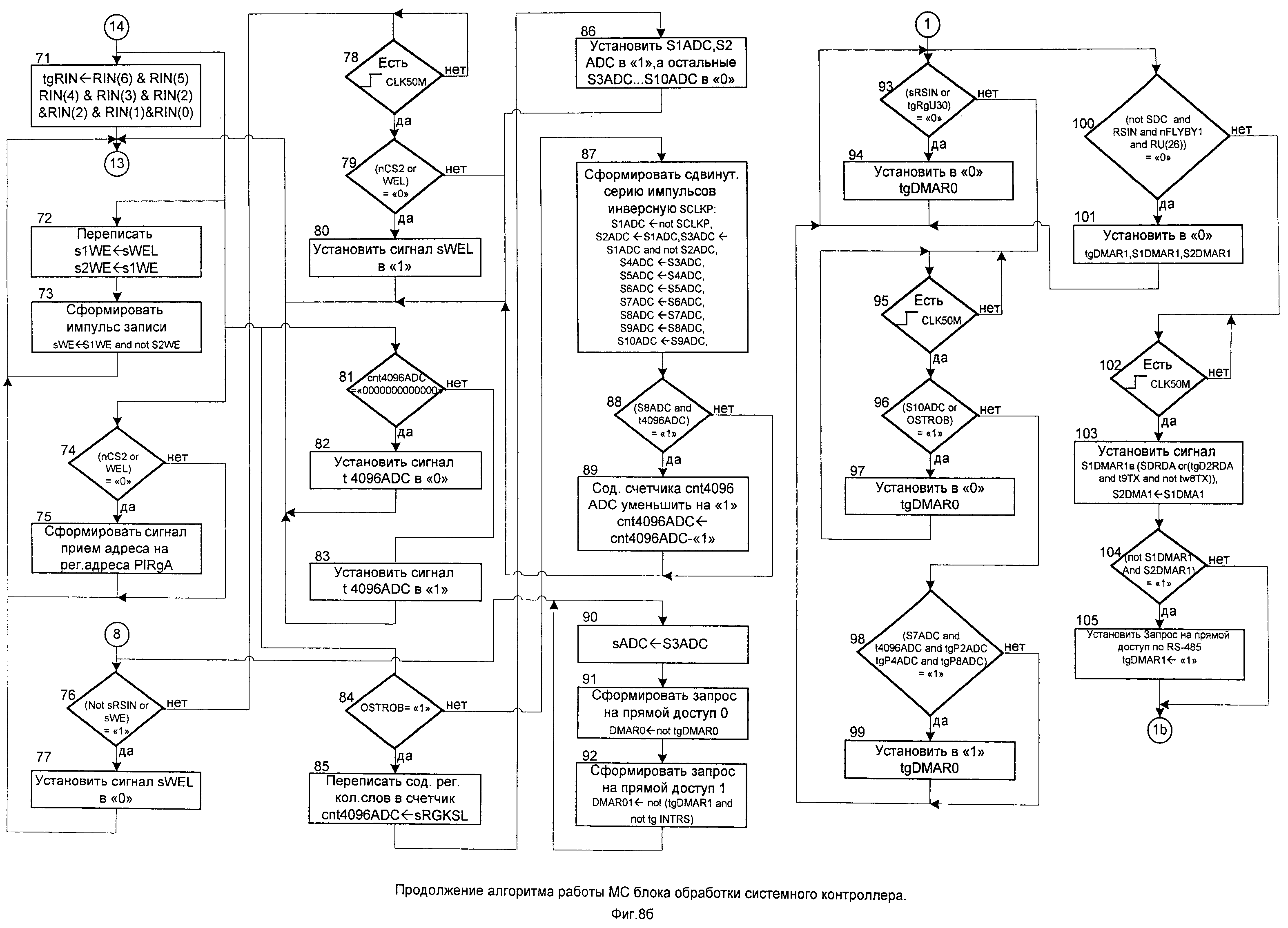

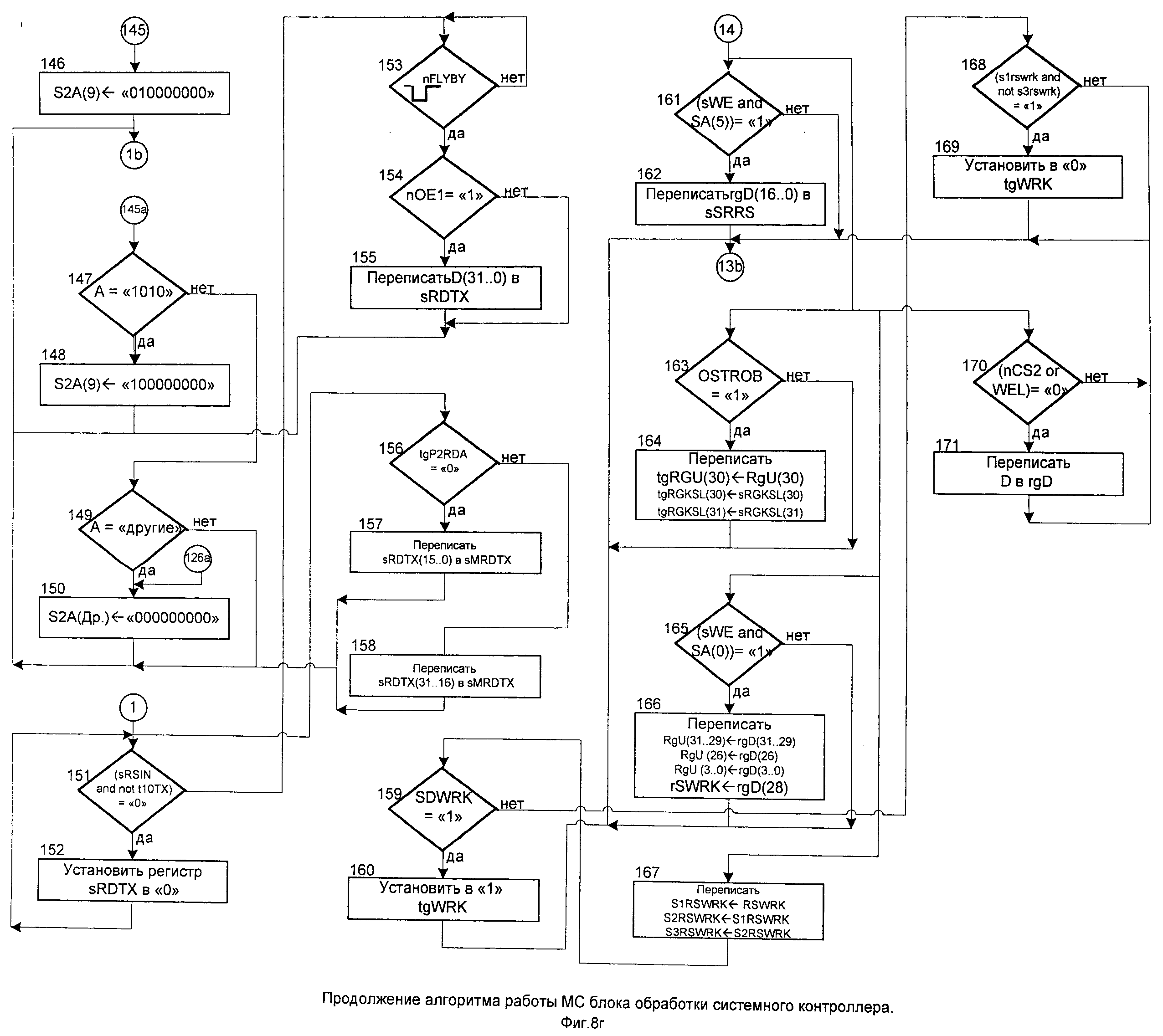

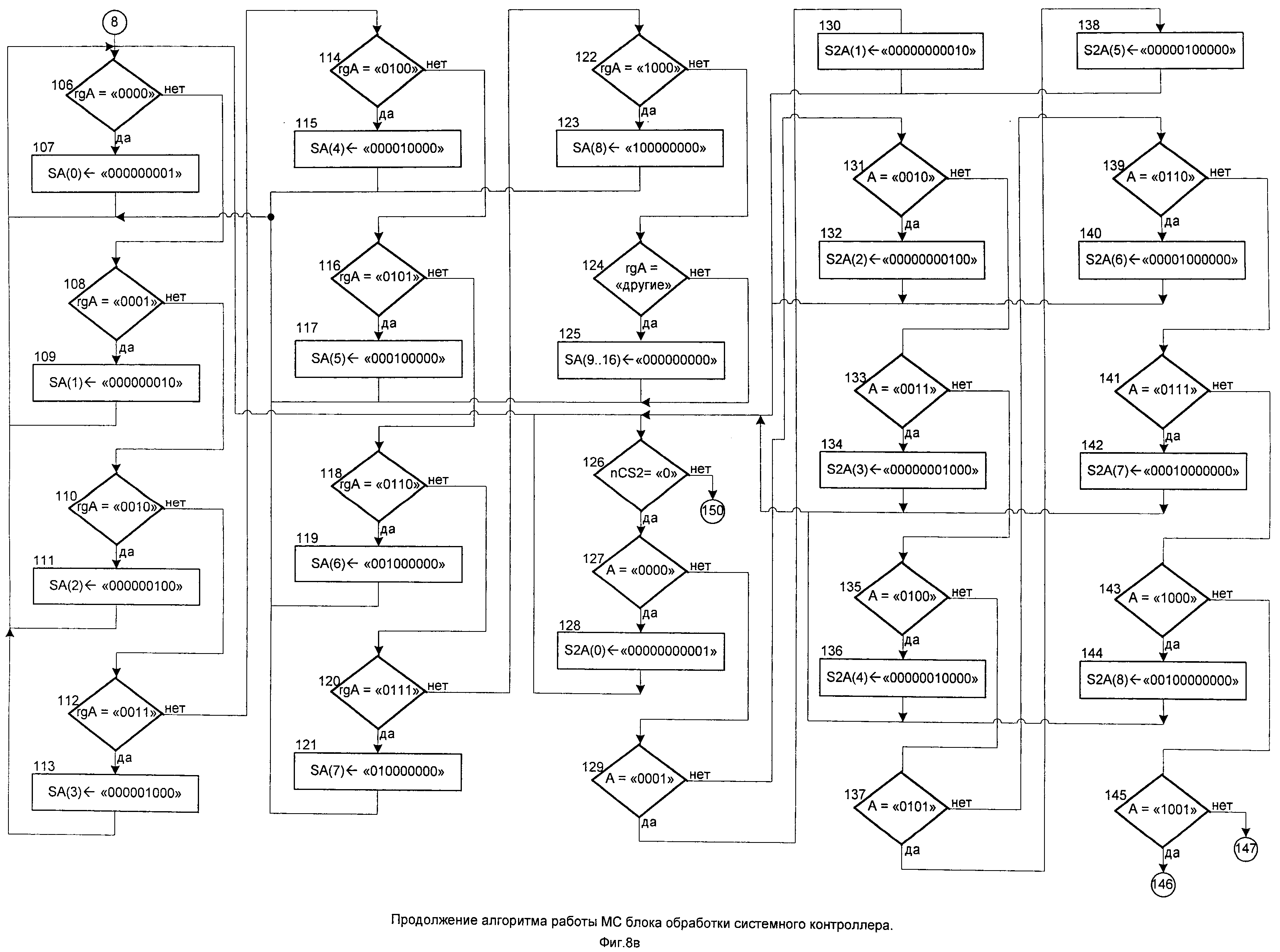

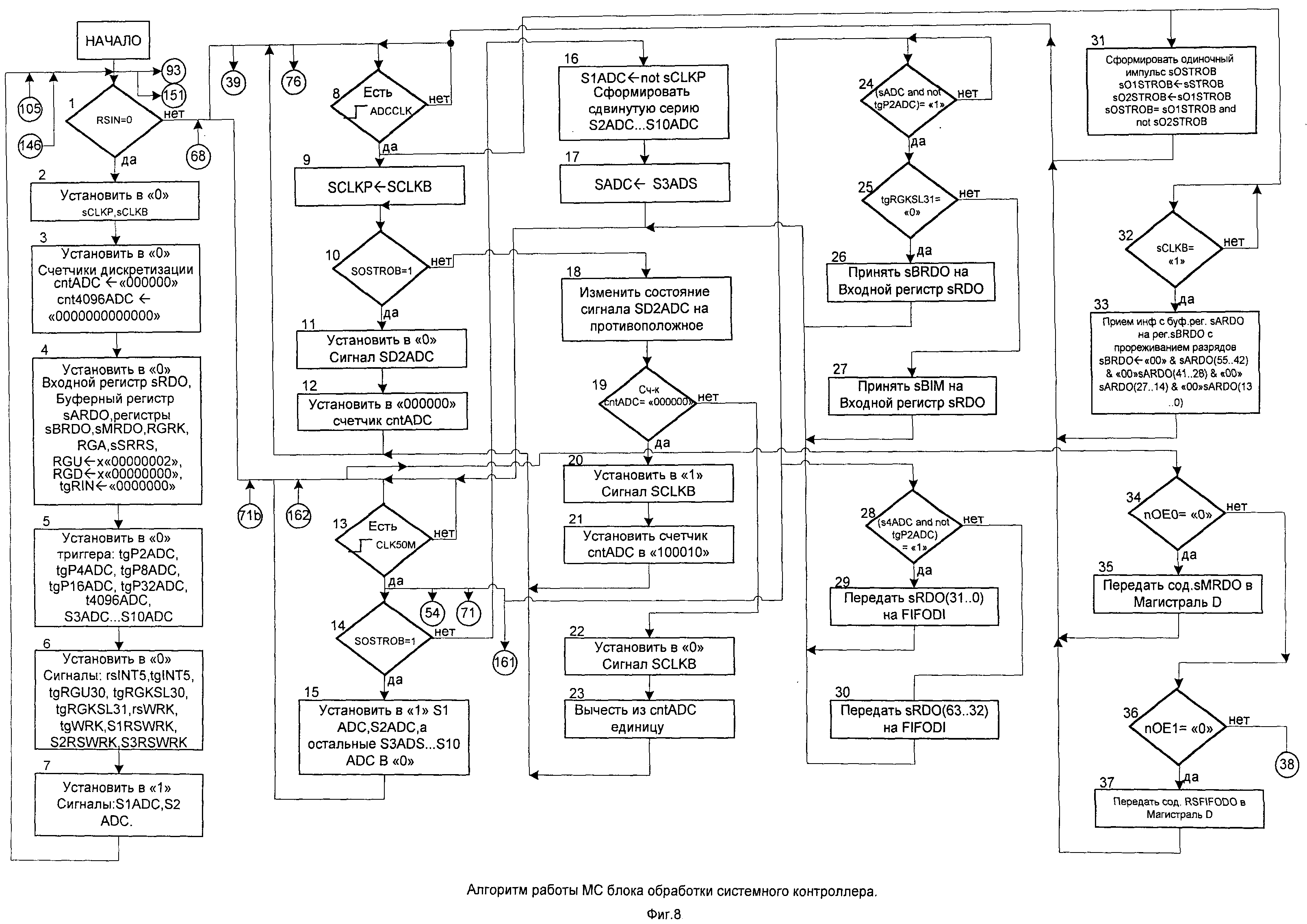

- на фиг.8, 8а, 8б, 8в, 8г представлен алгоритм работы МС блока обработки системного контроллера;

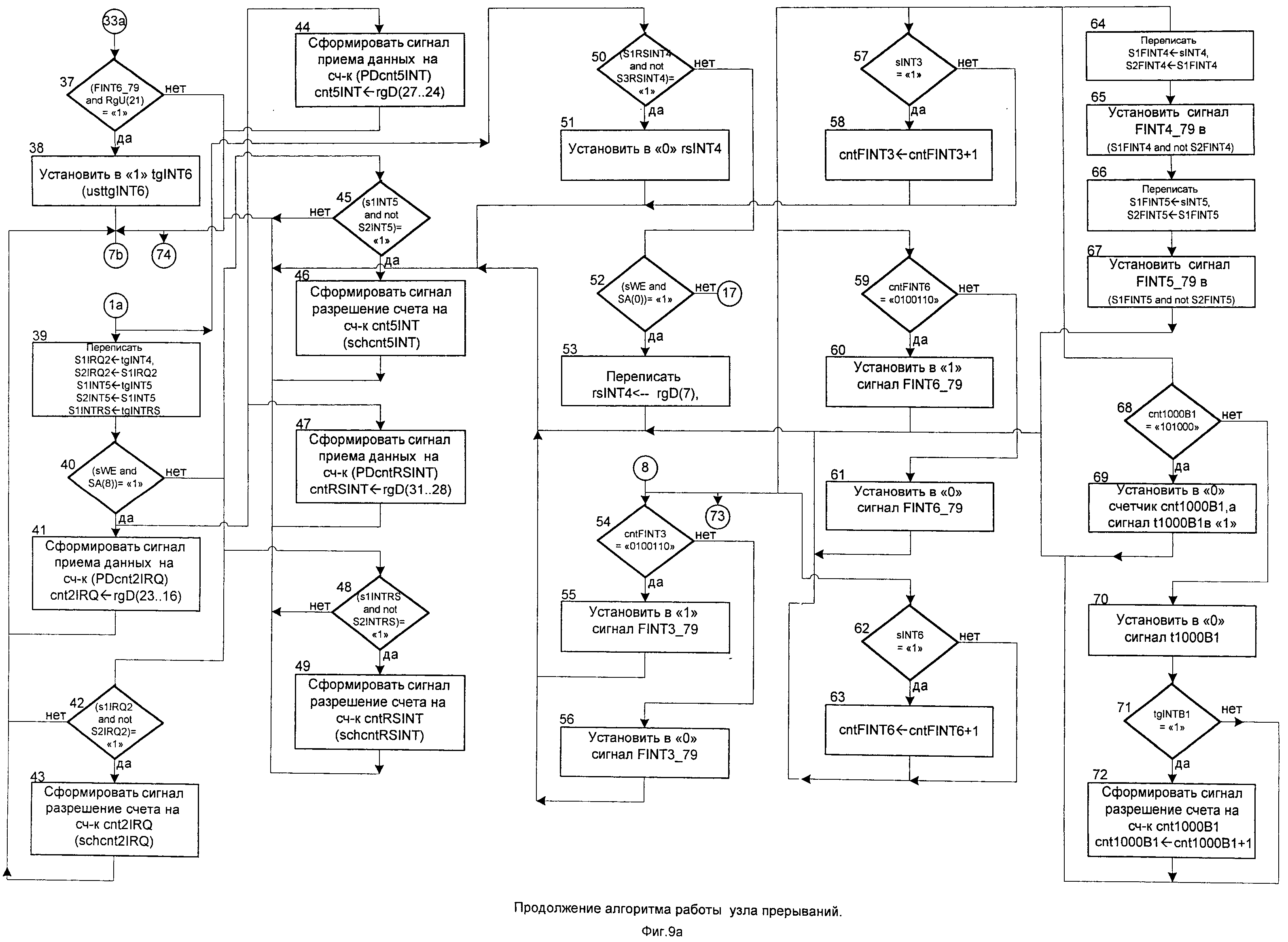

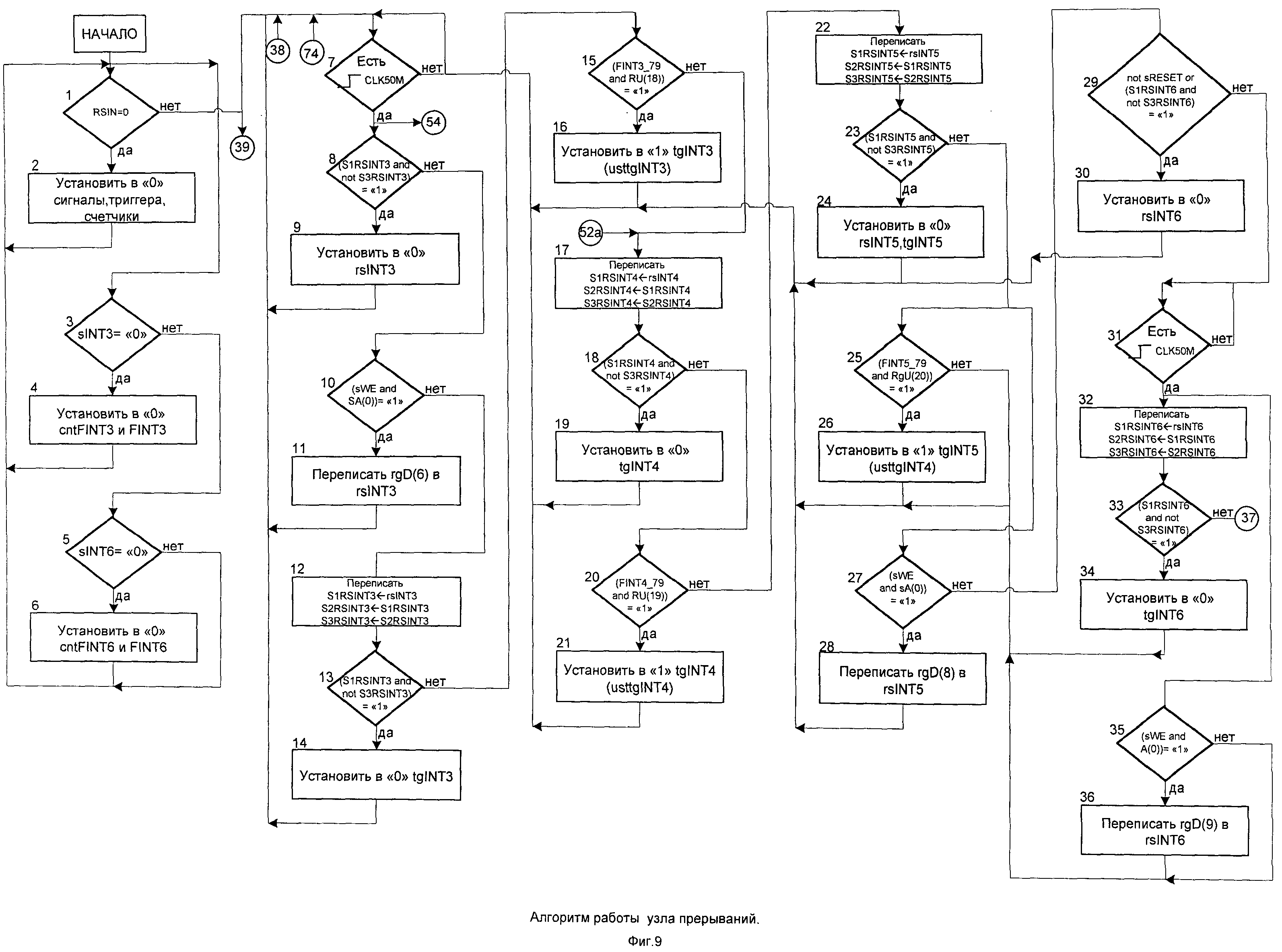

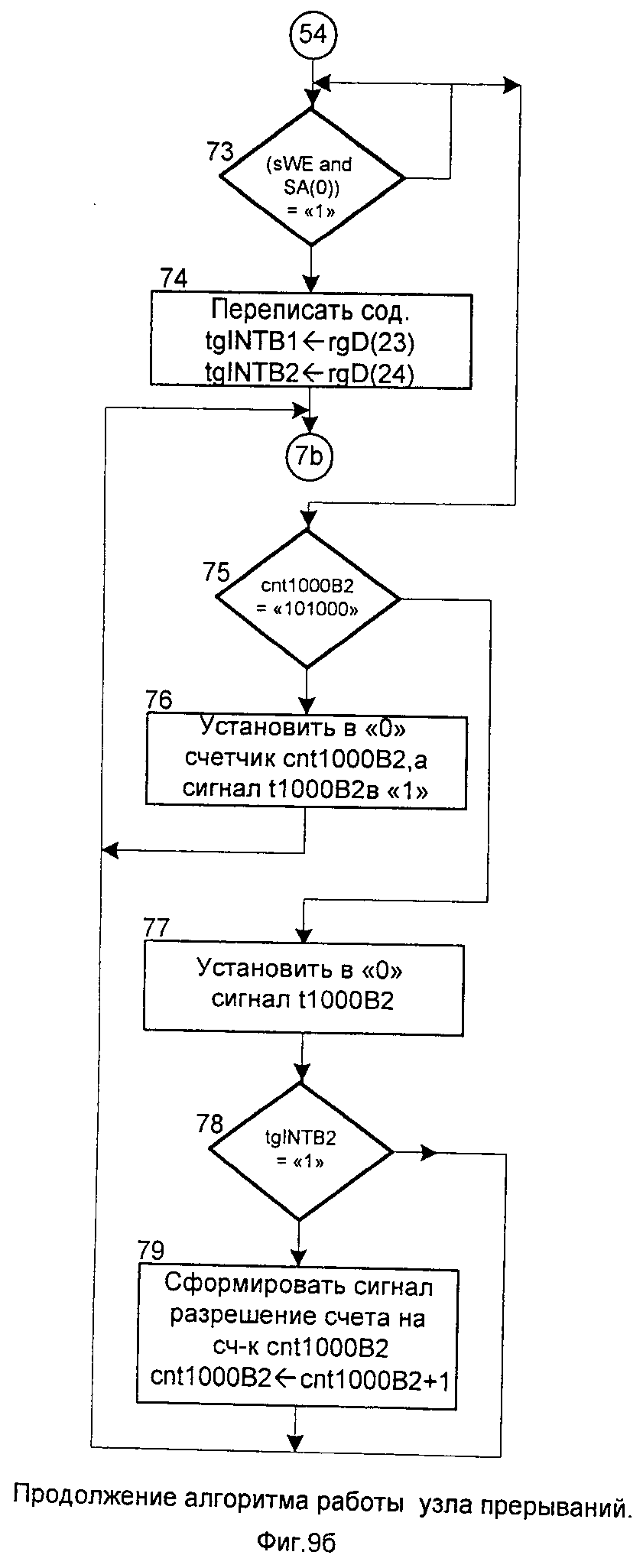

- на фиг.9, 9а, 9б представлен алгоритм работы узла прерываний;

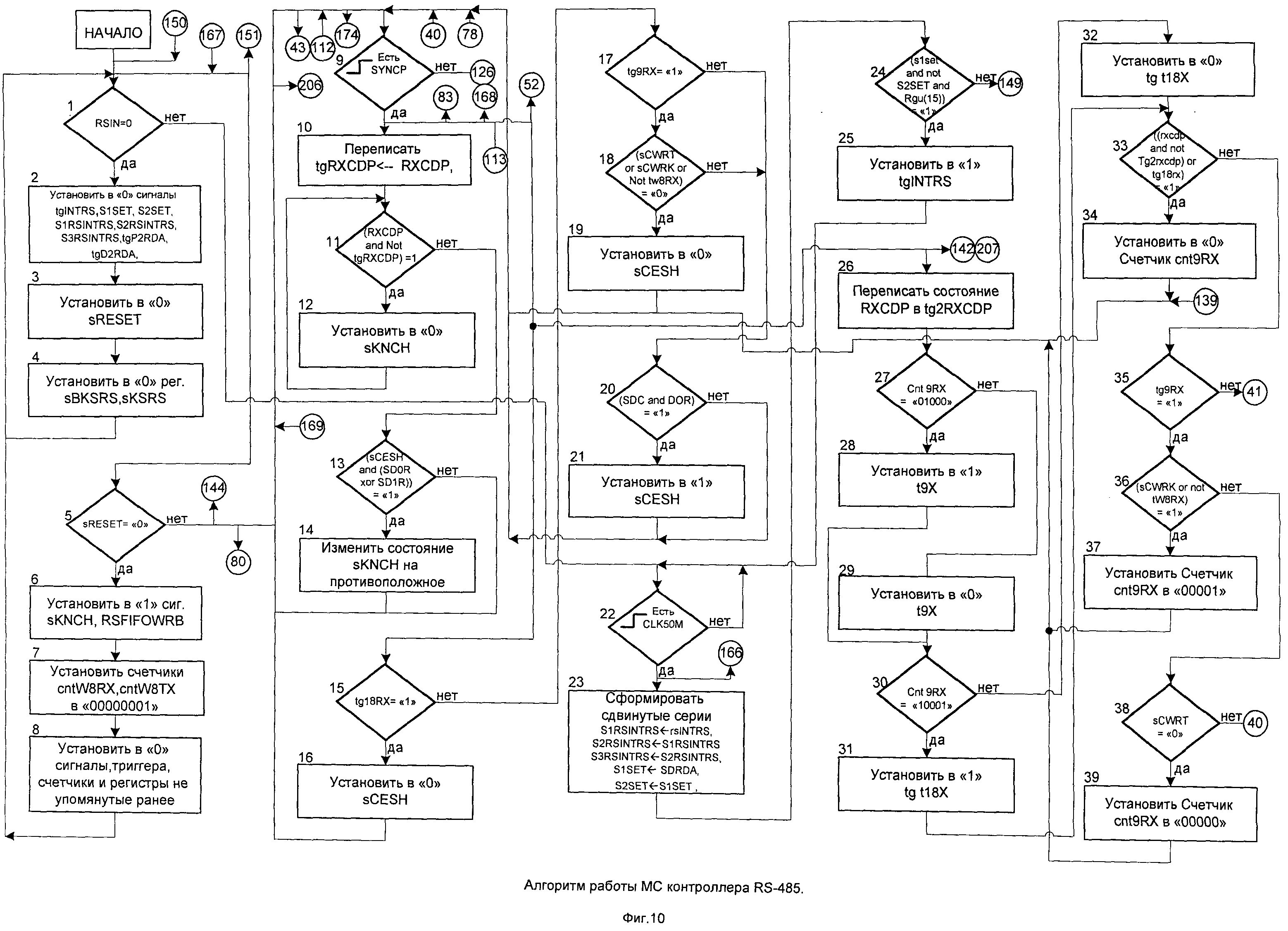

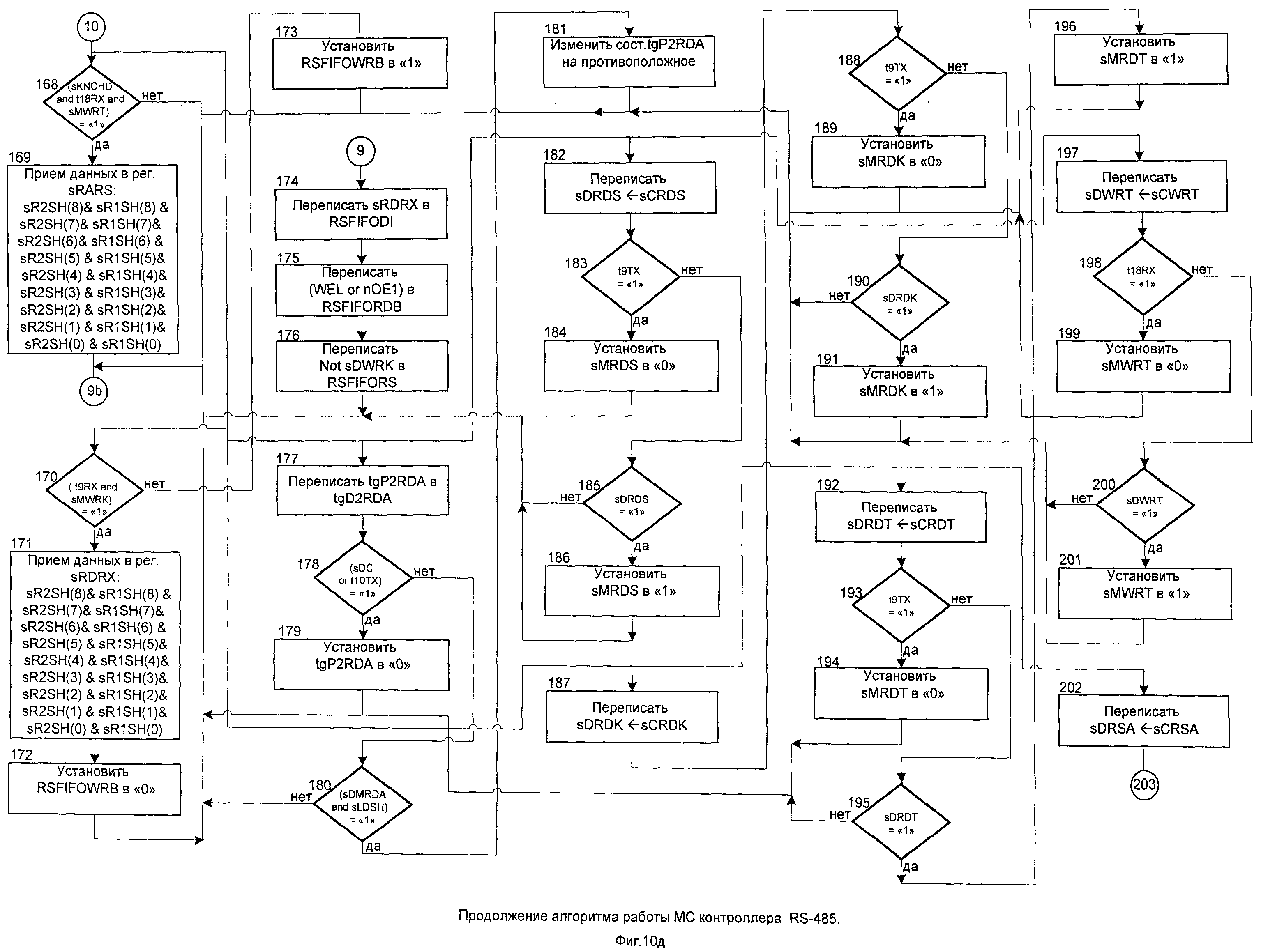

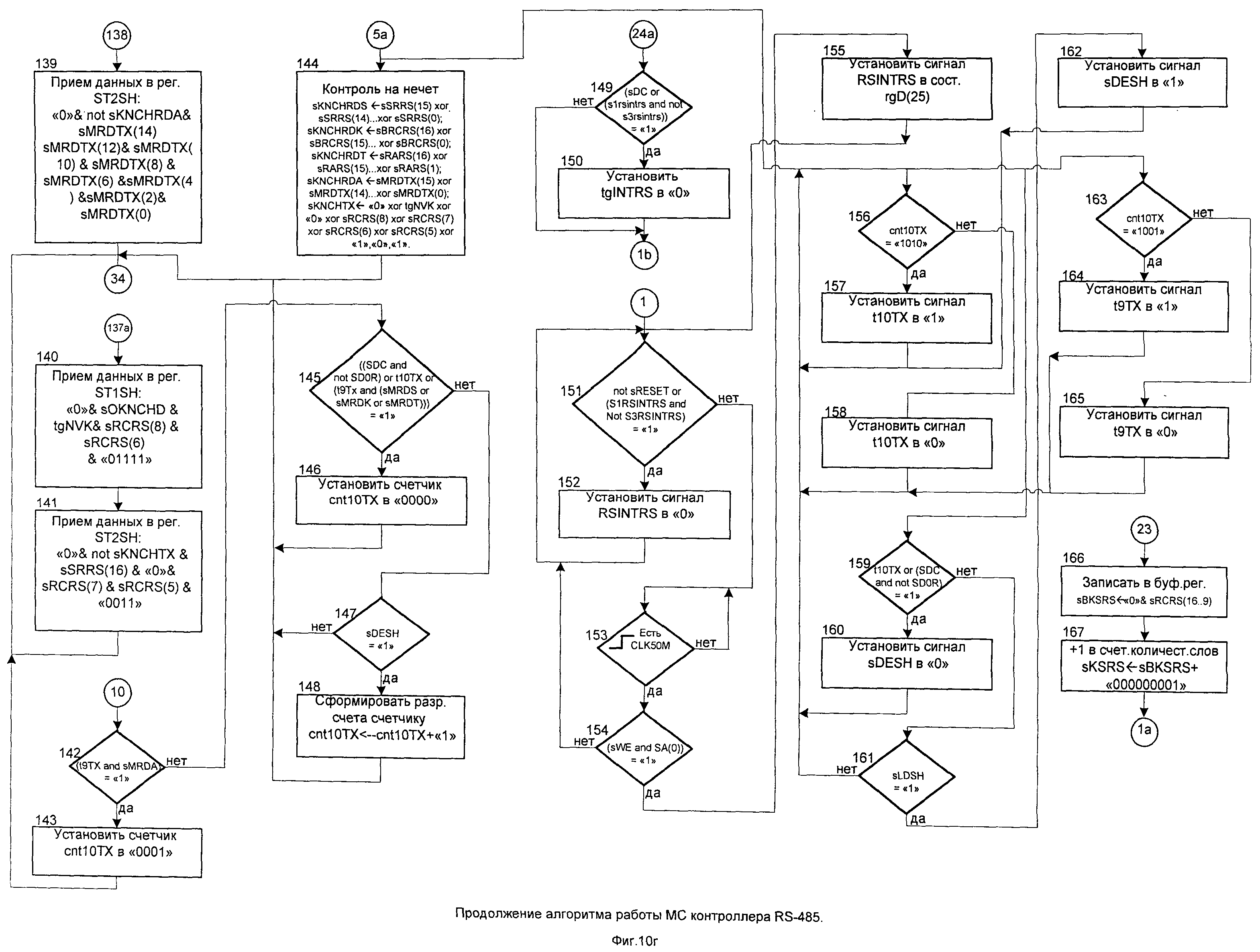

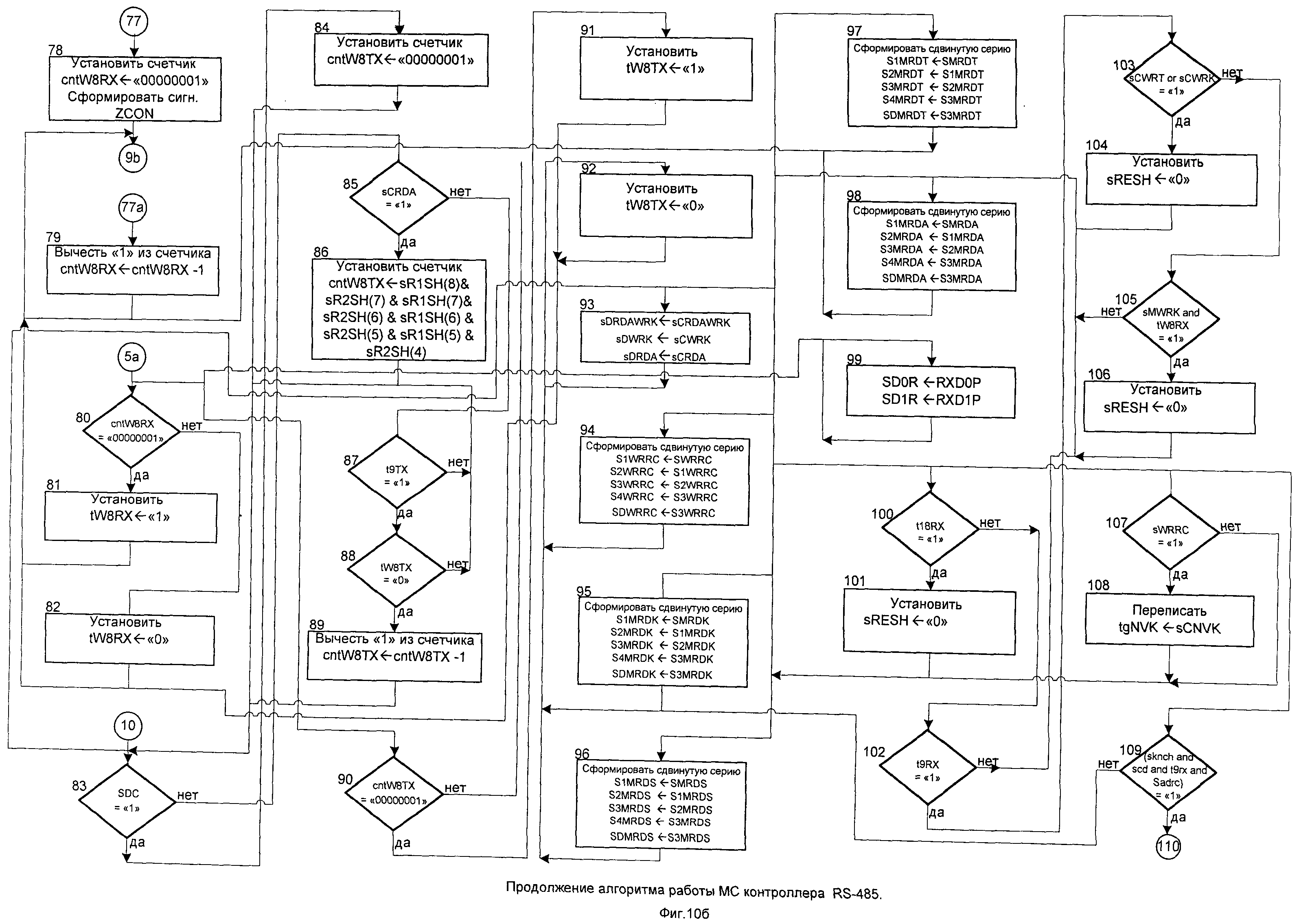

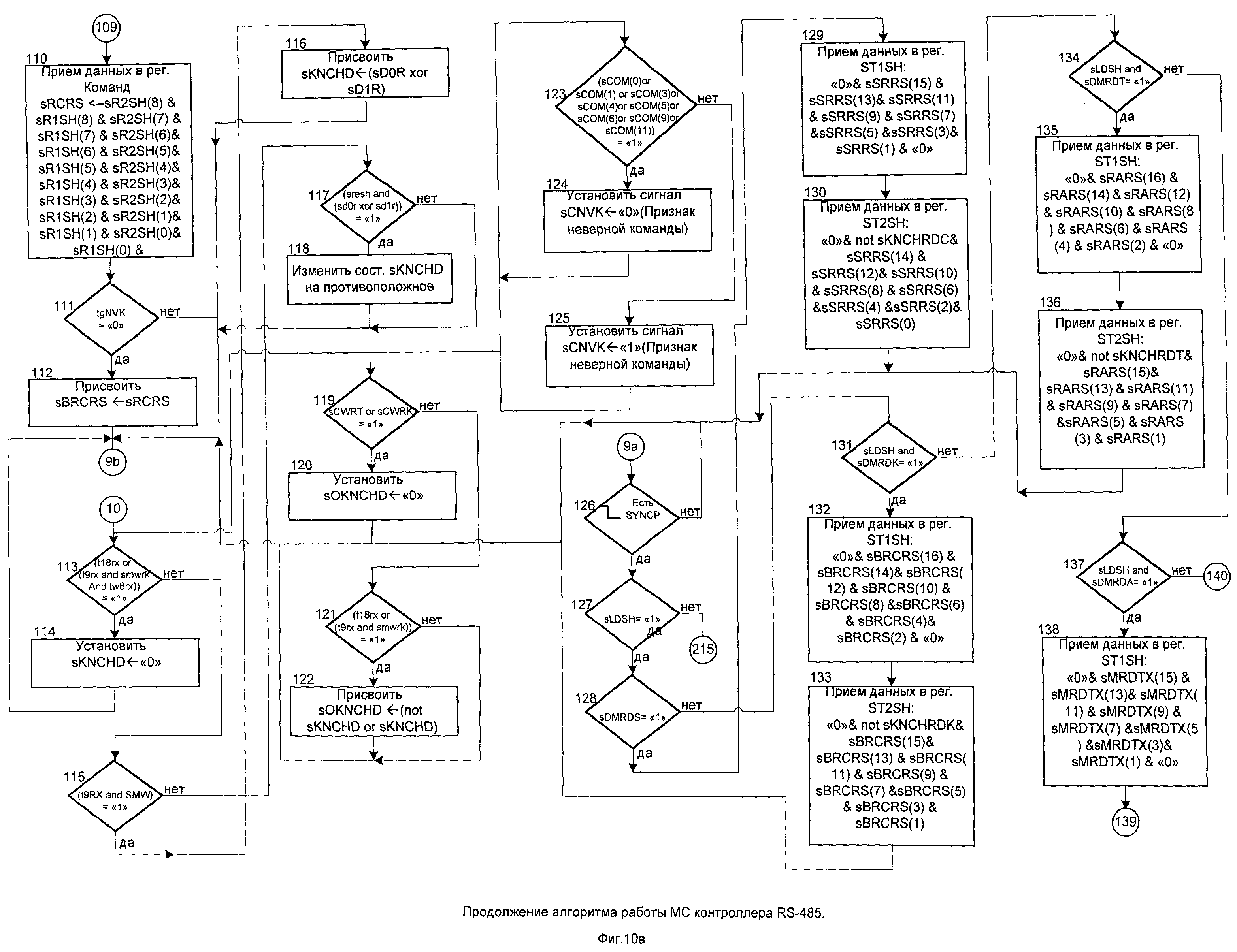

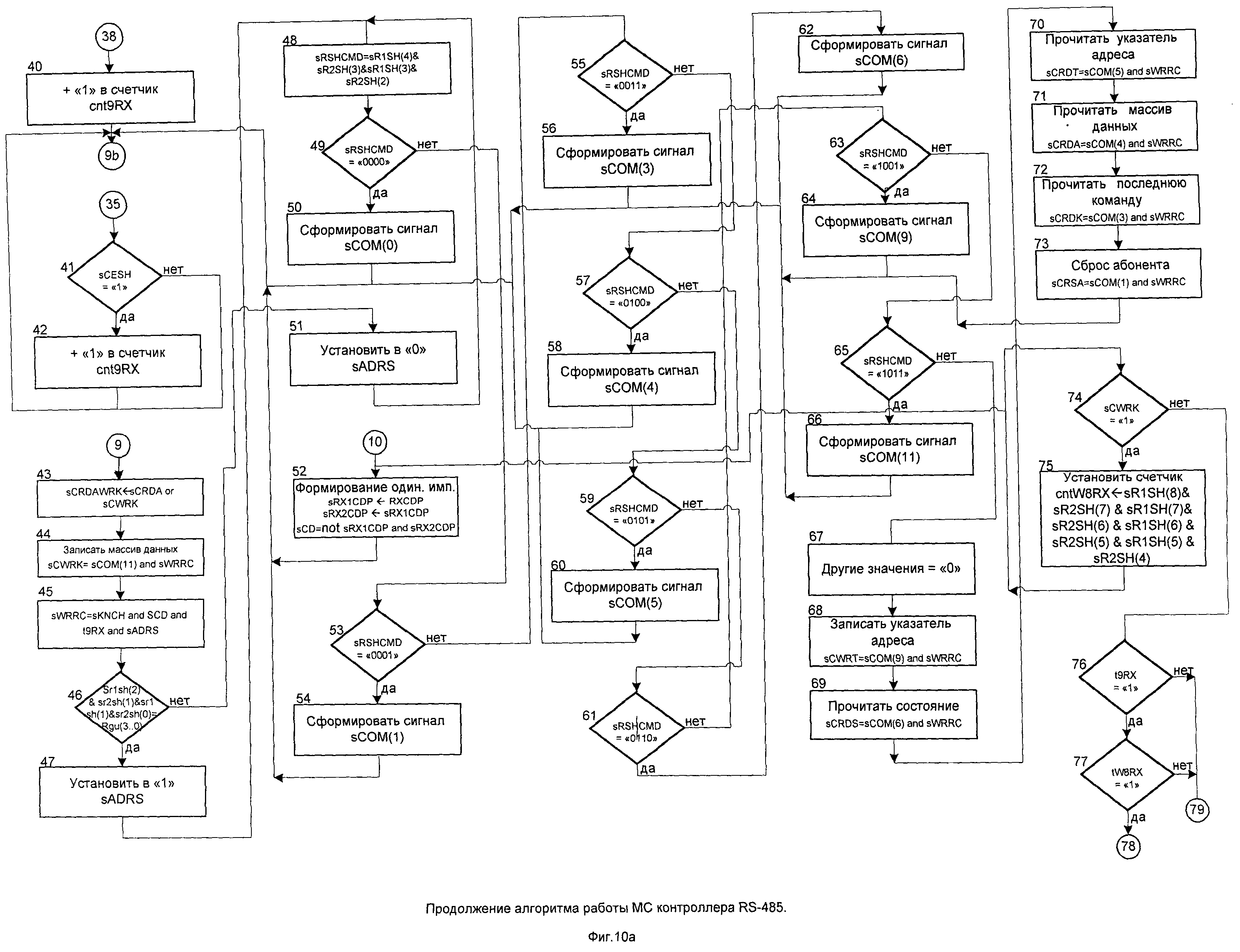

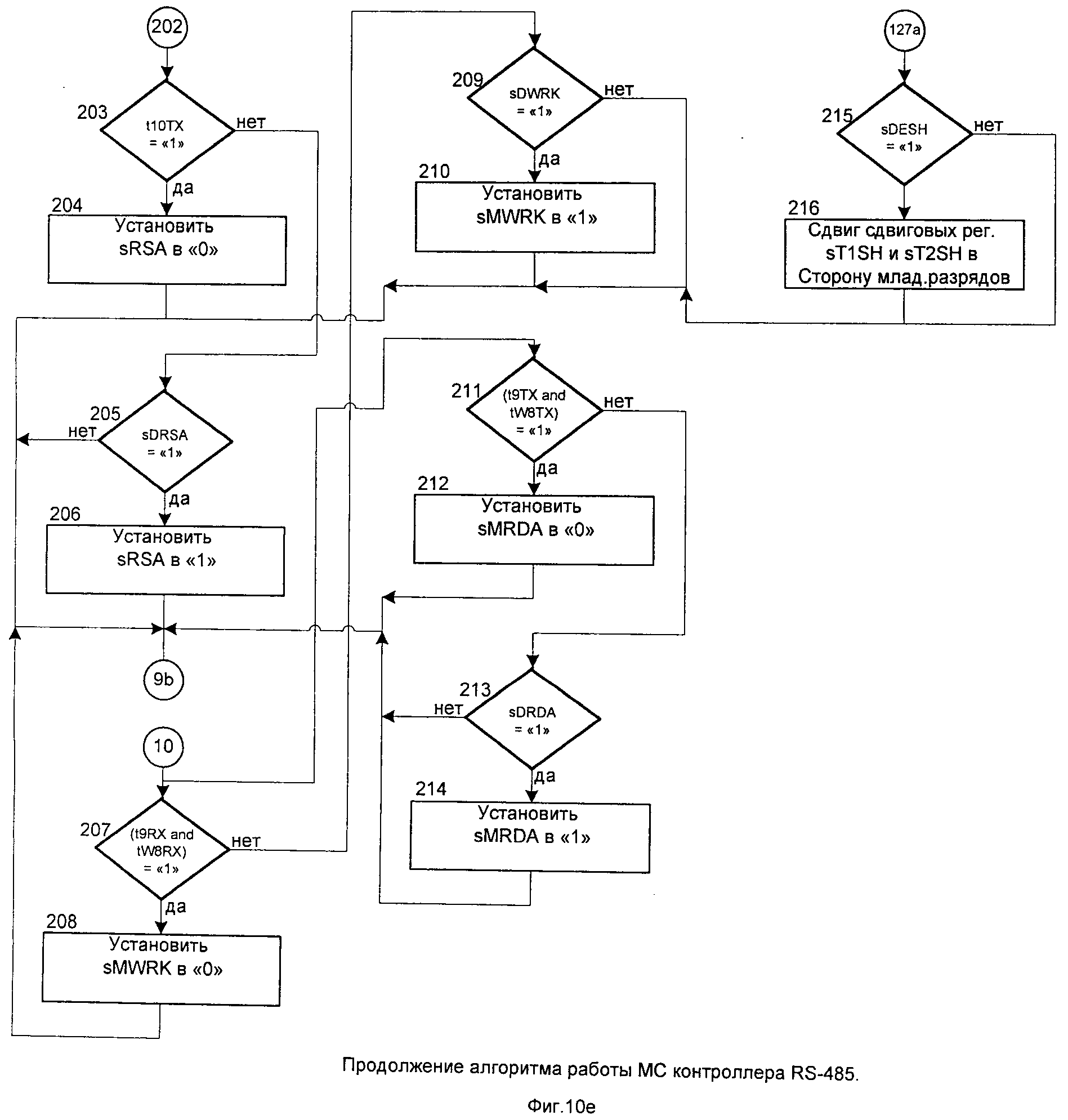

- на фиг.10, 10а, 10б, 10в, 10г, 10д, 10е представлен алгоритм работы МС контроллера RS-485;

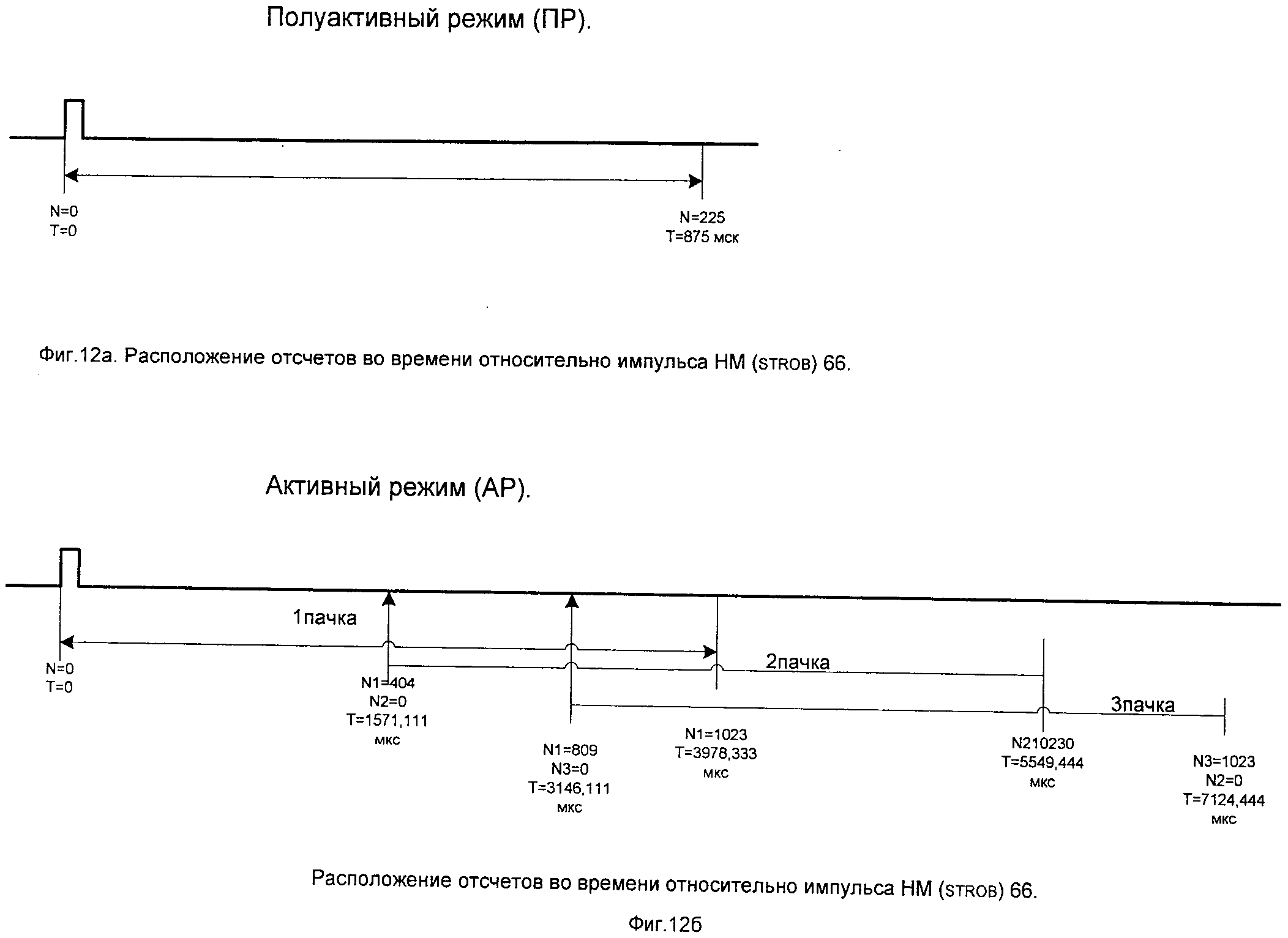

- на фиг.12а представлено расположение отсчетов во времени относительно импульса MM (STROB) 66 в полуактивном режиме;

- на фиг.12б представлено расположение отсчетов во времени относительно импульса НМ (STROB) 66 в активном режиме;

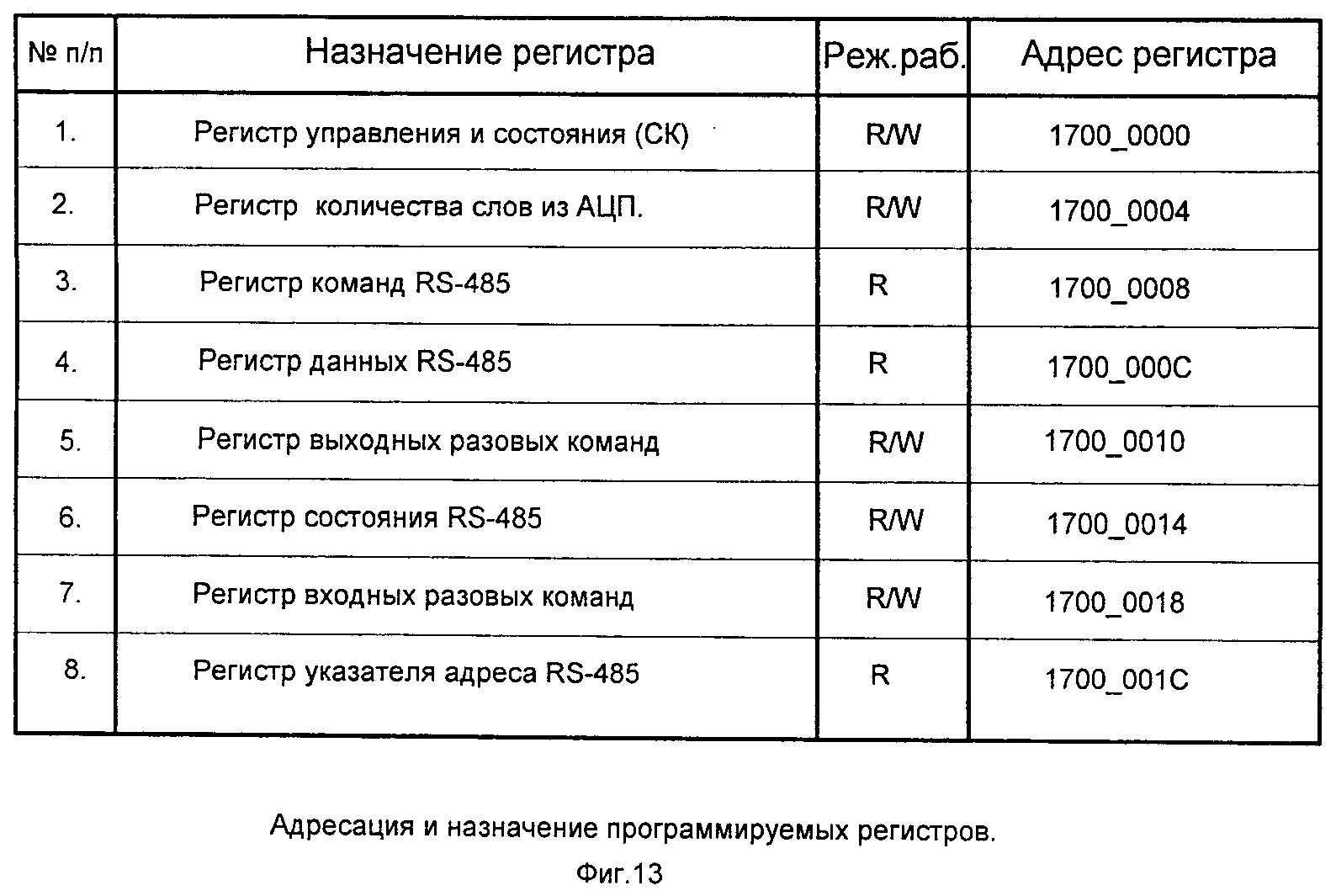

- на фиг.13 представлена адресация и назначение программируемых регистров;

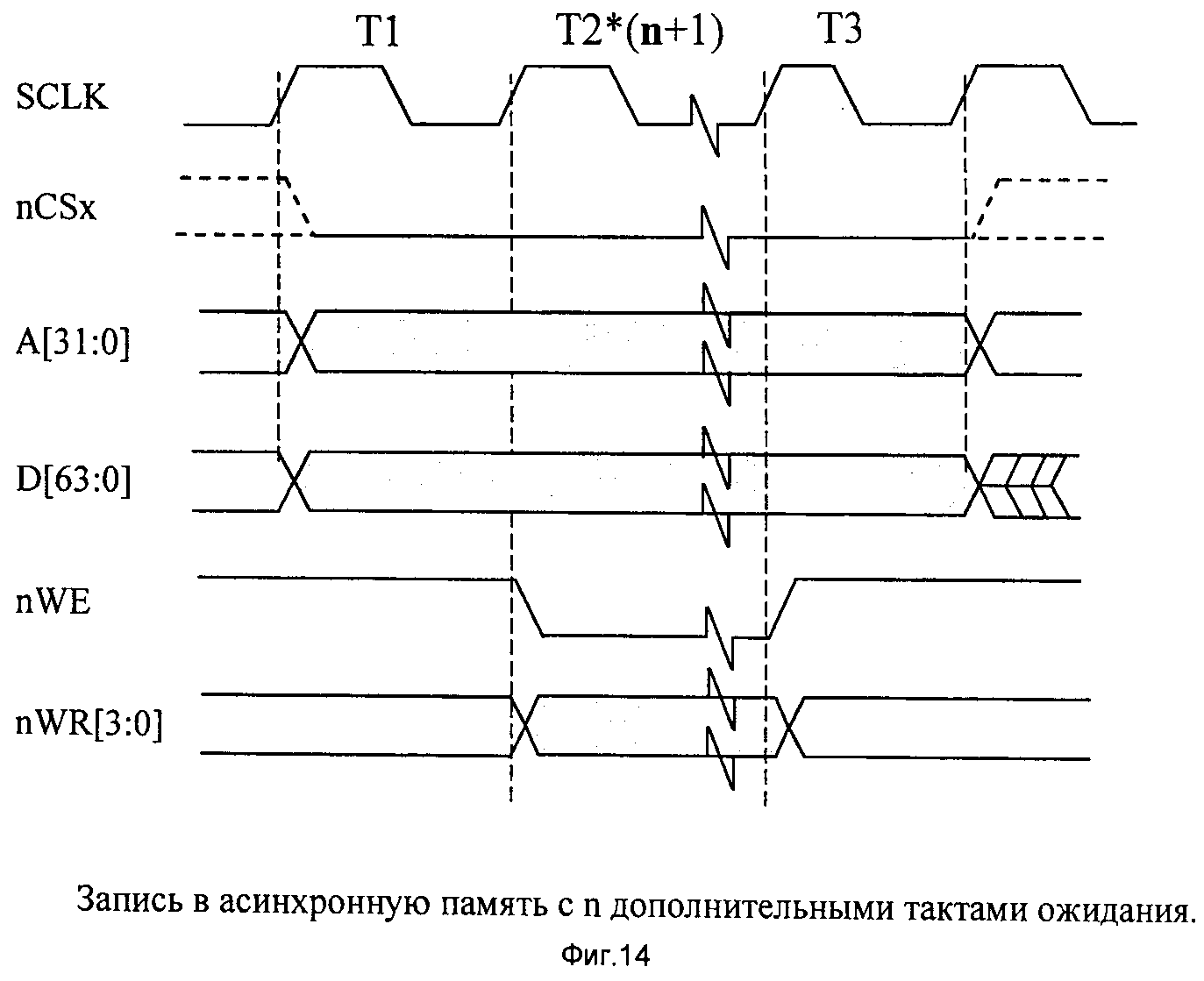

- на фиг.14 представлена запись в асинхронную память с n дополнительными тактами ожидания;

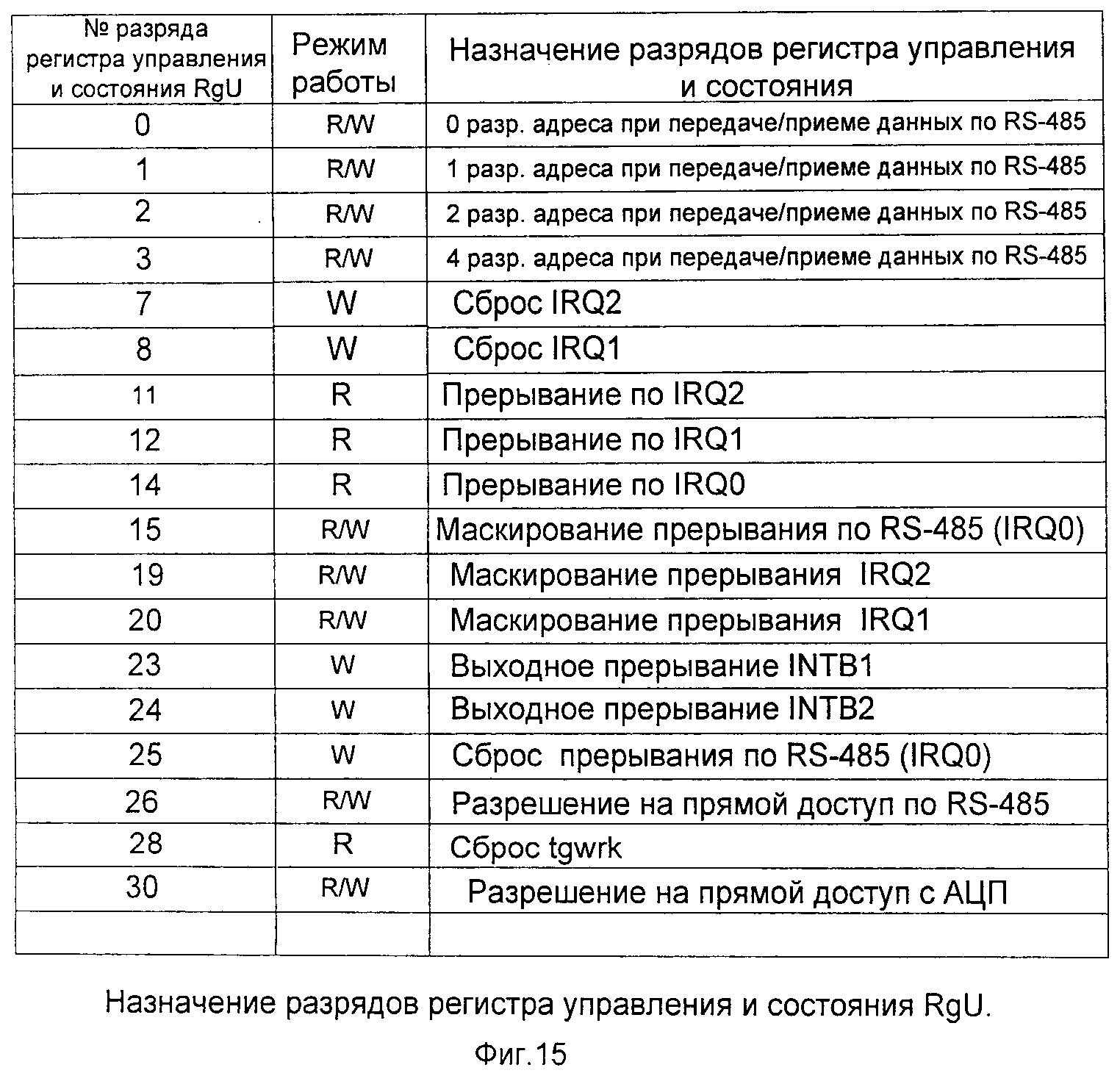

- на фиг.15 представлено назначение разрядов регистра управления и состояния RgU;

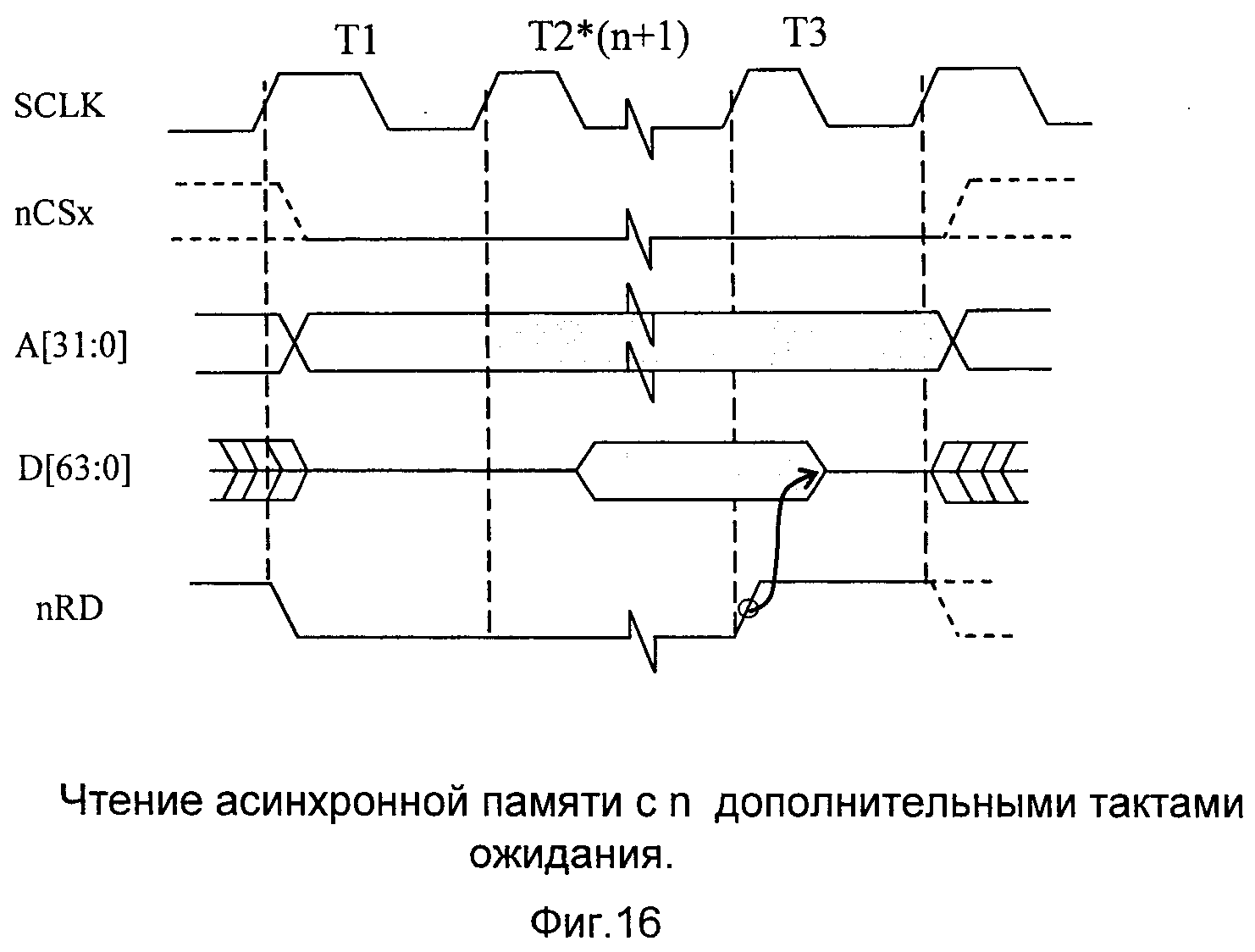

- на фиг.16 представлено чтение асинхронной памяти с n дополнительными тактами ожидания;

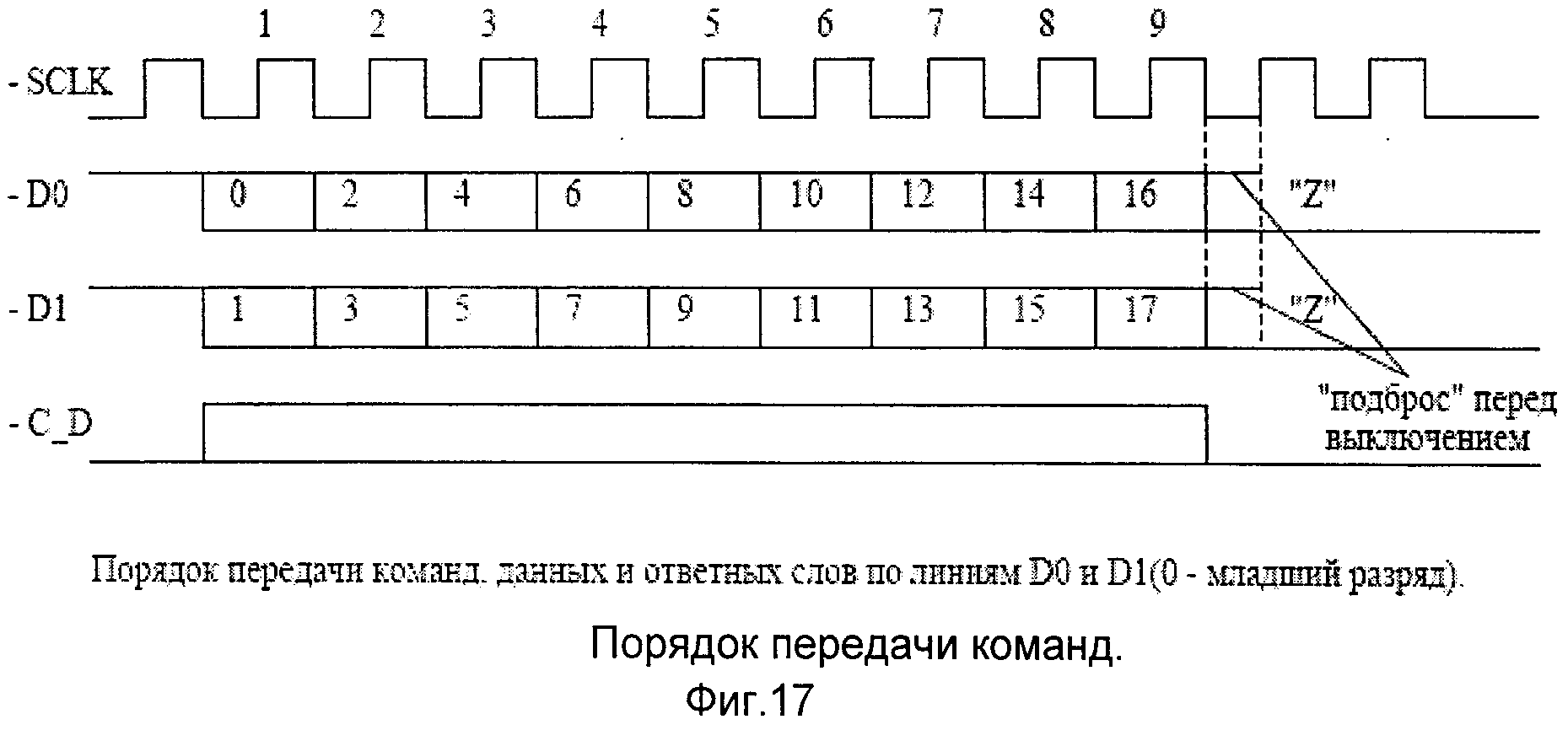

- на фиг.17 представлен порядок передачи команд;

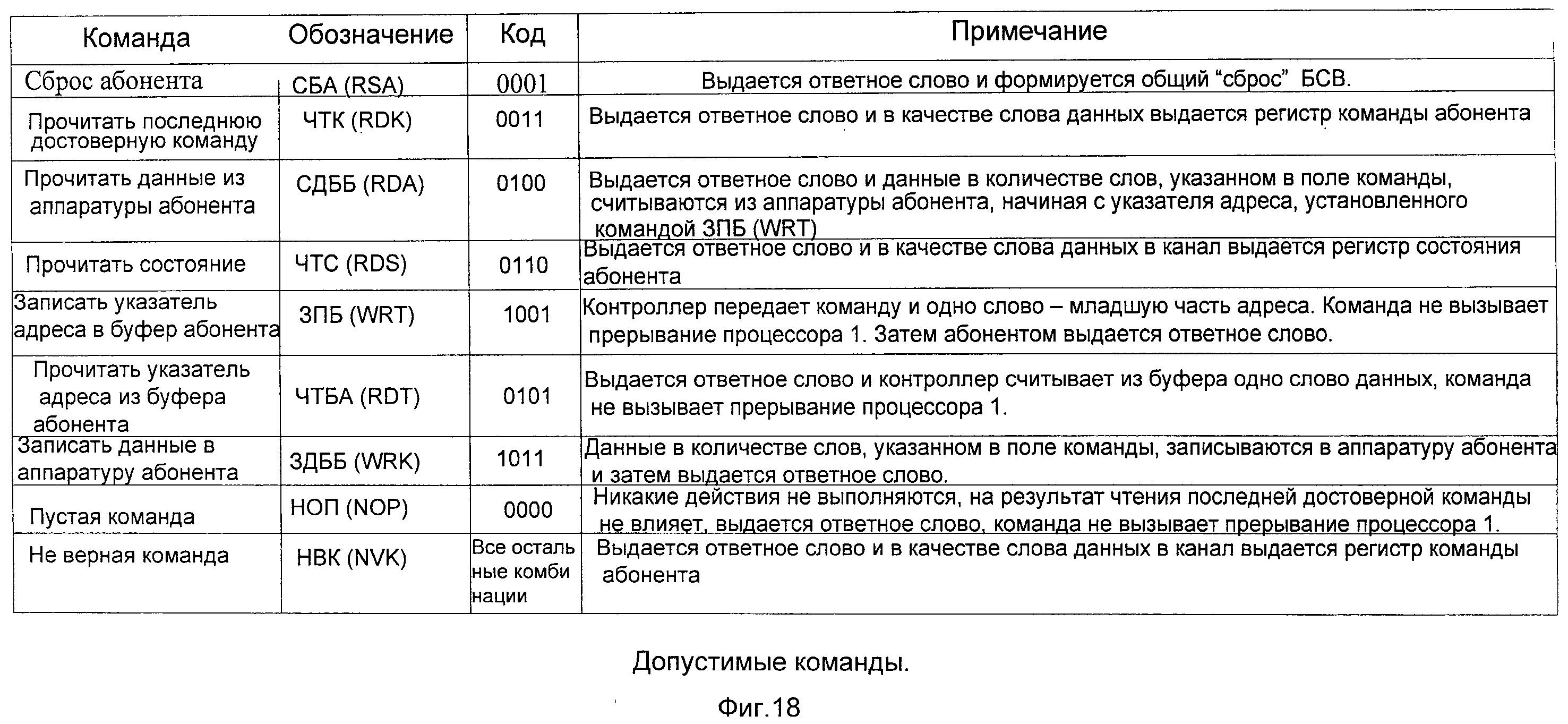

- на фиг.18 представлены допустимые команды;

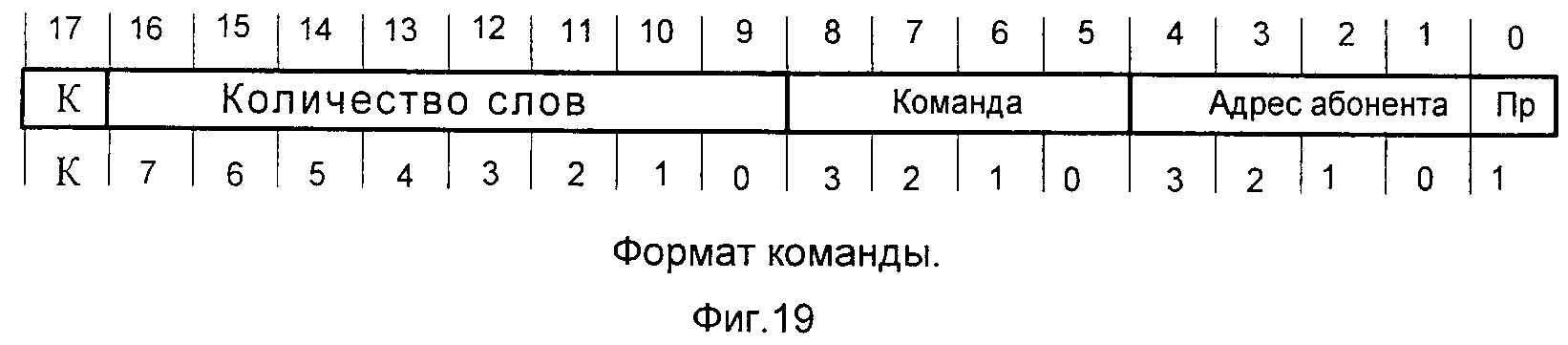

- на фиг.19 представлен формат команды;

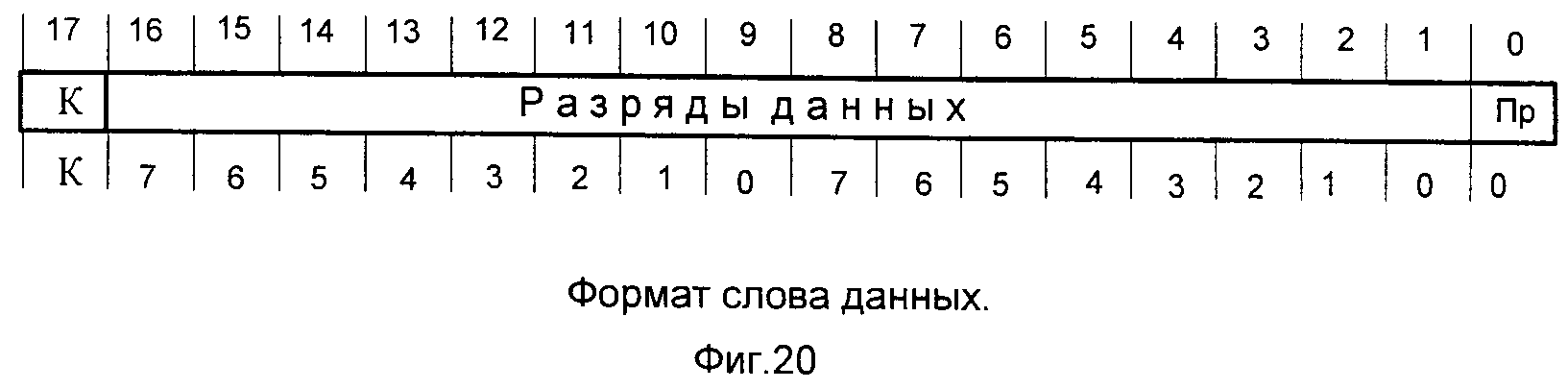

- на фиг.20 представлен формат слова данных;

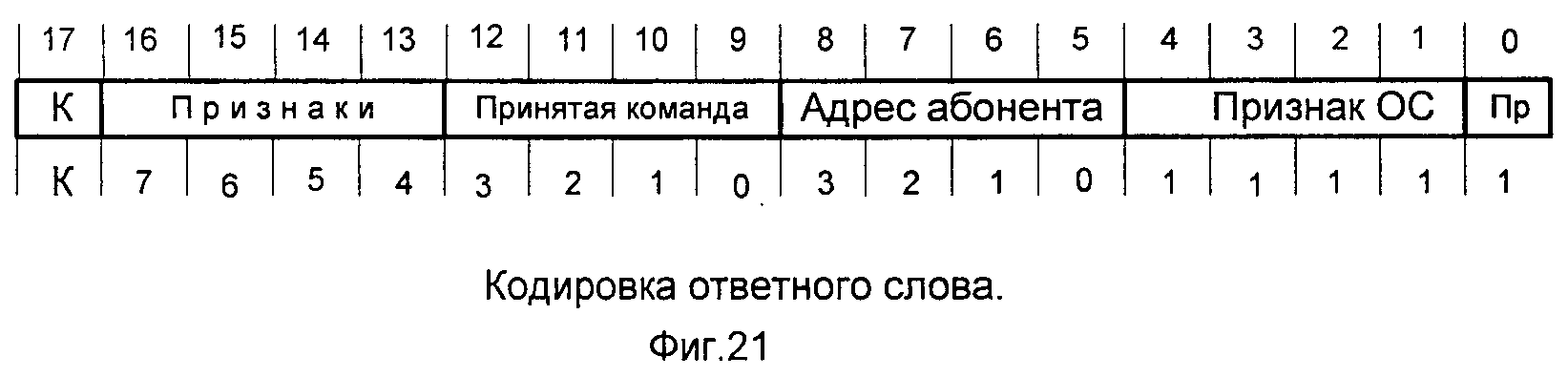

- на фиг.21 представлена кодировка ответного слова;

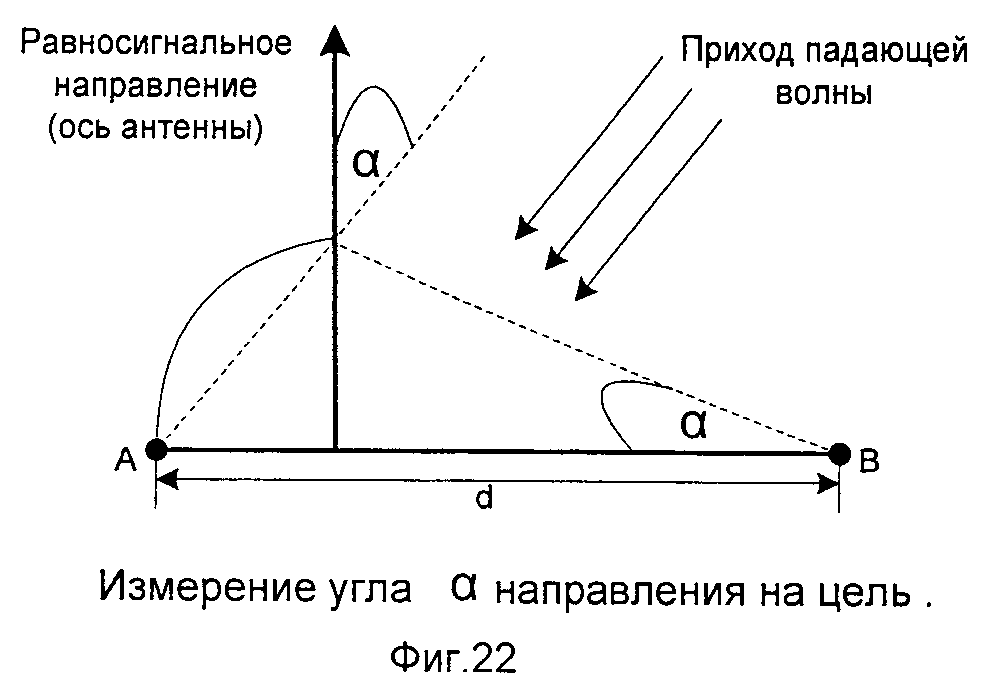

- на фиг.22 представлено измерение угла а направления на цель;

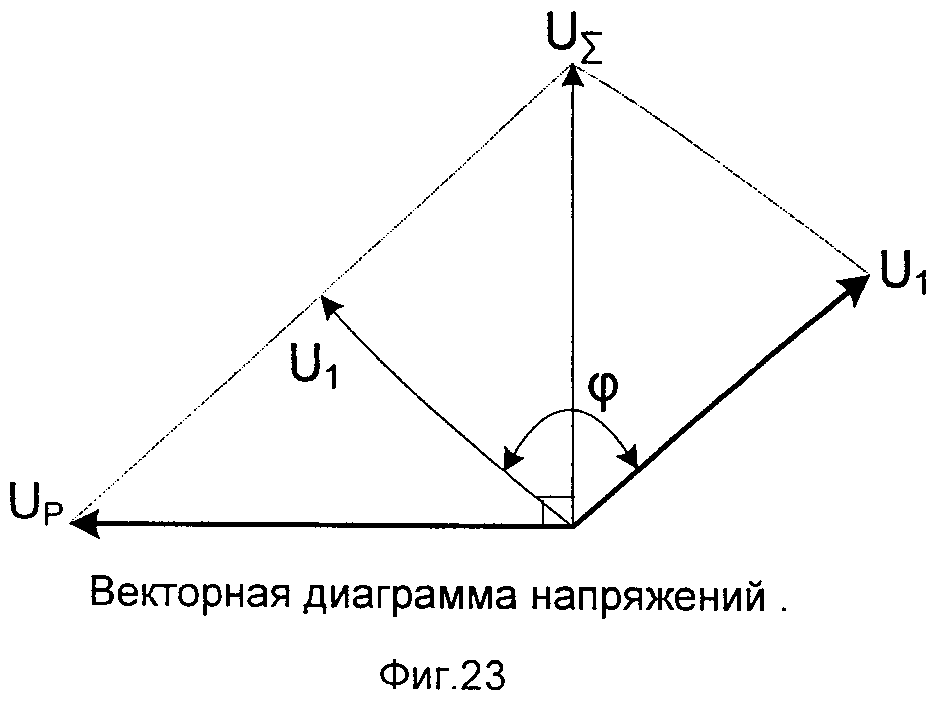

- на фиг.23 представлена векторная диаграмма напряжений.

Указанные преимущества заявляемого устройства перед прототипом достигаются за счет того, что в бортовой спецвычислитель (БСВ), содержащий процессор 1, первый 2, второй 3, третий 4 и четвертый 5 АЦП, соединенные с первым, вторым, третьим и четвертым трансформаторными входами 6, ОЗУ 7, соединенное с процессором 1 шиной данных 8, адресной шиной 9 и первым 10, вторым 11 и третьим 12 управляющими сигналами, двухпортовое ОЗУ 13, соединенное с процессором 1 шиной данных 8, адресной шиной 9 и четвертым 14, пятым 15 и шестым 16 управляющими сигналами, контроллер мультиплексного канала 17, соединенный с двухпортовым ОЗУ 13 шиной данных 18, адресной шиной 19 и первым 20, вторым 21, третьим 22 и четвертым 23 управляющими сигналами, первый 24 и второй 25 приемопередатчики мультиплексого канала, соединенные с выходами 26, 27 контроллера мультиплексого канала17 и с пятым и шестым трансформаторными входами 28, дополнительно введены ПЗУ 29, системный контроллер 30, первый 31, второй 32, третий 33 и четвертый 34 приемопередатчики RS-485 и узел сброса 35, выход 36 которого соединен с первым входом системного контроллера 30, шина данных 8 которого соединена с шиной данных процессора 1 и ПЗУ 29, адресная шина 9 которого соединена с адресной шиной процессора 1 и системного контроллера 30, второй, третий и четвертый входы которого соединены с четвертым 14, пятым 15 и шестым 16 управляющими сигналами процессора 1, первый 37 и второй 38 выходы которого соединены с первым и вторым входами ПЗУ 29, причем первая 39 группа выходов процессора 1 соединена с первой группой входов системного контроллера 30, вторая 40, третья 41, четвертая 42 и пятая 43 группы входов которого соединены с первым 2, вторым 3, третьим 4 и четвертым 5 АЦП, первые входы которых соединены с первым 44 входом бортового спецвычислителя и пятым входом системного контроллера 30, первая 45 и вторая 46 группы выходов которого соединены с первой и второй группами входов процессора 1, третья 47 группа входов процессора 1 и шестой вход системного контроллера 30 являются первой группой входов бортового спецвычислителя, вторая 48 группа входов которого соединена с шестой группой входов системного контроллера 30, третья группа выходов которого является первой 49 группой выходов бортового спецвычислителя, первый 50 и второй 51 двунаправленные входы-выходы которого соединены с первым 31 и вторым 32 приемопередатчиками RS-485, выходы 52,53 которых соединены с седьмым и восьмым входами системного контроллера 30, первый 54 и второй 55 выходы которого соединены с первым и вторым входами первого 31 приемопередатчика RS-485, первый и второй входы второго 32 приемопередатчика RS-485 соединены с третьим 56 и четвертым 57 выходами системного контроллера 30, пятый 58 выход которого соединен с первым входом четвертого 34 приемопередатчика RS-485, второй вход которого соединен со вторым 59 входом бортового спецвычислителя, третий 60 вход которого соединен со входом третьего 33 приемопередатчика RS-485, выход 61 которого соединен с девятым входом системного контроллера 30, десятый вход которого соединен с выходом 62 четвертого 34 приемопередатчика RS-485, причем четвертая 63 группа выходов системного контроллера 30 соединена со второй группой выходов бортового спецвычислителя, третья 64 группа входов которого соединена с седьмой группой входов системного контроллера 30, шестой 65 выход которого соединен с первым выходом бортового спецвычислителя, четвертый 66 вход которого соединен с одиннадцатым входом системного контроллера 30, двенадцатый вход которого соединен с пятым 67 входом бортового спецвычислителя, причем седьмой 68 выход системного контроллера 30 соединен с первым входом процессора 1, третий выход 69 которого соединен с тринадцатым входом системного контроллера 30, восьмой 70 выход которого соединен со вторым входом контроллера мультиплексного канала 17.

Системный контроллер 30 состоит из блока обработки системного контроллера 71, первого 72 счетчика, второго 73 счетчика, первого 74 FIFO, второго 75 FIFO, константы 76, группа выходов 77 которой соединена с первыми группами входов первого 74 и второго 75 FIFO, группы выходов 78,79 которых соединены с первой и второй группами входов блока обработки системного контроллера 71, первая 80 и вторая 81 группы выходов которого соединены со вторыми группами входов первого 74 и второго 75 FIFO, третьи 82,83 группы входов которых соединены с третьей и четвертой группами выходов блока обработки системного контроллера 71, первый выход которого соединен с первыми входами первого 74 и второго 75 FIFO и является седьмым 68 выходом системного контроллера 30, шина данных 8 которого соединена с шиной данных блока обработки системного контроллера 71, адресная шина которого является адресной шиной 9 системного контроллера 30, первая 45, вторая 46, третья 49 и четвертая 63 группы выходов которого соединены с пятой, шестой, седьмой и восьмой группами выходов блока обработки системного контроллера 71, второй, третий, четвертый, пятый, шестой и седьмой выходы которого соединены с первым 54, вторым 55, третьим 56, четвертым 57, пятым 58 и шестым 65 выходами системного контроллера 30, первая 39, вторая 40, третья 41, четвертая 42, пятая 43, шестая 48 и седьмая 64 группы входов которого соединены с третьей, четвертой, пятой, шестой, седьмой, восьмой и девятой группами входов блока обработки системного контроллера 71, первый вход которого является первым 36 входом системного контроллера 30 и соединен с инверсными входами первого 72 и второго 73 счетчика, прямые входы которых соединены со вторым входом блока обработки системного контроллера 71 и тринадцатым 69 входом системного контроллера 30, второй 14, третий 15, четвертый 16, пятый 44, шестой 47, седьмой 52, восьмой 53, девятый 61, десятый 62, одиннадцатый 66 и двенадцатый 67 входы которого соединены с третьим, четвертым, пятым, одиннадцатым, шестым, седьмым, восьмым, девятым, десятым, двенадцатым и тринадцатым входами блока обработки системного контроллера 71, причем выход 84 первого 72 счетчика соединен с четырнадцатым входом блока обработки системного контроллер 71, а выход второго 73 счетчика соединен с восьмым 70 выходом системного контроллера 30.

Блок обработки системного контроллера 71 состоит из первого 85 и второго 86 счетчиков, регистра 87, первого 88, второго 89 и третьего 90 дешифраторов, машины состояния 91 (МС), узла прерываний 92, узла регистров 93, контроллера RS-485 94, константы 95, первого 96 и второго 97 элементов И, элемента ИЛИ 98, выход которого соединен с первыми входами первого 96 элемента И, узла регистров 93, контроллера RS-485 94 и является первым 68 выходом блока обработки системного контроллера 71, второй 54, третий 55, четвертый 56, пятый 57 и шестой 58 выходы которого соединены с первым, вторым, третьим, четвертым и пятым выходами контроллера RS-485 94, шина данных 8 которого соединена с шиной данных узла регистров 93 и является шиной данных 8 блока обработки системного контроллера 71, адресная шина 9 которого соединена с адресной шиной регистра 87 и второго 89 дешифратора, группа выходов которого соединена с первой группой входов МС 91, вторая группа входов которого и первый вход узла прерываний 92 соединены с группой выходов третьего 90 дешифратора, группа входов которого соединена с группой выходов регистра 87, тактовый вход 69 которого соединен со вторыми входами узла регистров 93 и блока обработки системного контроллера 71, первый 36 вход которого соединен с первым входом элемента ИЛИ 98, второй вход которого соединен с шестым 47 входом блока обработки системного контроллера 71, седьмой 65 выход которого соединен с первым выходом узла регистров 93, второй 99 выход которого соединен со вторым входом контроллера RS-485 94, шестой выход которого является первым сигналом пятой 45 группы выходов блока обработки системного контроллера 71, остальные сигналы соединены с первой группой выходов узла прерываний 92, вторая 100 группа выходов которого соединена с первой группой входов узла регистров 93, первая группа выходов которого является первой 80 группой выходов блока обработки системного контроллера 71, вторая 81 группа выходов которого соединена с первой группой выходов контроллера RS-485 94, вторая 101, третья 102, четвертая 103 группы выходов которого соединены со второй, третьей и четвертой группами входов узла регистров 93, вторая группа выходов которого является восьмой 63 группой выходов блока обработки системного контроллера 71, третья 82 и четвертая 83 группы выходов которого соединены с первой и второй группами выходов МС 91, третья группа выходов которой является шестой 46 группой выходов блока обработки системного контроллера 71, седьмая 49 группа выходов которого соединена с первым и вторым выходами узла прерываний 92, первая группа входов которого является девятой 64 группой входов блока обработки системного контроллера 71, первая 78 и вторая 79 группы входов которого соединены с пятой и шестой группами входов узла регистров 93, седьмая группа входов которого соединена с первой группой входов контроллера RS-485 94, третьей группой входов МС 91 и является третьей 39 группой входов блока обработки системного контроллера 71, четвертая 40, пятая 41, шестая 42 и седьмая 43 группы входов которого соединены с восьмой, девятой, десятой и одиннадцатой группами входов узла регистров 93, двенадцатая 104 группа входов которого соединена с четвертой группой выходов МС 91, четвертая группа входов которой соединена с группой выходов 105 второго счетчика 86, группа входов которого соединена с группой выходов константы 95, причем тактовый вход второго 86 счетчика соединен с четвертым входом блока регистров 93 и с одиннадцатым 44 входом блока обработки системного контроллера 71, третий 14, четвертый 15 и пятый 16 входы которого соединены с первым, вторыми третьим входами МС 91, первый выход которой соединен с инверсным входом первого 96 элемента И, выход 106 которого соединен со вторым входом узла прерываний 92, со сбросовыми входами регистра 87 и первого 85 счетчика, с третьими входами контроллера RS-485 94 и узла регистров 93 и инверсным входом второго 97 элемента И, выход которого соединен со сбросовым входом второго 86 счетчика, причем восьмая 48 группа входов блока обработки системного контроллера 71 соединена с тринадцатой группой входов узла регистров 93, третья 107 группа выходов которого соединена с группой входов первого 85 счетчика, группа выходов которого соединена с группой входов первого 88 дешифратора, группа выходов которого соединена с пятой группой входов МС 91, второй и третий выходы которой соединены с разрешающим входом регистра 87 и с прямым входом второго 97 элемента И, четвертый и пятый выходы МС 91 соединены с разрешающим и установочным входами первого 85 счетчика, тактовый вход которого соединен с пятым, третьим и четвертым входами узла регистров 93, узла прерываний 92 и контроллера RS-485 94 соответственно и является четырнадцатым 84 входом блока обработки системного контроллера 71, двенадцатый 66 вход которого соединен с четвертым входом МС 91, шестой 108 выход которой соединен с четвертым входом узла прерываний 92, шестой вход узла регистров 93 соединен с седьмым 109 выходом контроллера RS-485 94, пятый, шестой и седьмой входы которого соединены с девятым 61, седьмым 52и восьмым 53 входами блока обработки системного контроллер71, причем четвертая 110 и пятая 111 группы выходов узла регистров 93 соединены со второй и третьей группами входов контроллера RS-485 94 и второй группой входов узла прерываний 92 соответственно.

Узел регистров блока обработки системного контроллера 93 состоит из первого 112 регистра, второго 113 регистра, третьего 114 регистра, четвертого 115 регистра, пятого 116 регистра, шестого 117 регистра, седьмого 118 регистра, восьмого 119 регистра, первой 120 группы триггеров, второго 121 триггера, группы элементов исключающее ИЛИ 122, первого 123 мультиплексора, второго 124 мультиплексора, группа выходов которого соединена с информационной группой входов восьмого 119 регистра и является шиной данных 8 узла регистров блока обработки системного контроллера 93, первая 80 группа выходов которого соединена с группой выходов первого 123 мультиплексора, группа входов которого соединена с группой выходов третьего 114 регистра, информационная группа входов которого соединена с группой выходов второго 113 регистра, информационная группа входов которого соединена с группой выходов первого 112 регистра, первая, вторая, третья и четвертая группы входов которого являются восьмой 40, девятой 41, десятой 42 и одиннадцатой 43 группами входов узла регистров блока обработки системного контроллера 93, вторая 63 группа выходов которого соединена с группой выходов пятого 116 регистра, выход которого является первым 65 выходом узла регистров блока обработки системного контроллера 93, третья 107 группа выходов которого соединена с первой группой входов второго 124 мультиплексора и группой выходов шестого 117 регистра, информационная группа входов которого соединена с информационными группами входов четвертого 115, пятого 116, седьмого 118 регистров и группой выходов восьмого 119 регистра, тактовый вход которого является вторым 69 входом узла регистров блока обработки системного контроллера 93, четвертая 110 группа выходов которого соединена со второй группой входов второго 124 мультиплексора, группой входов группы элементов исключающее ИЛИ 122 и группой выходов четвертого 115 регистра, тактовый вход которого является пятым 84 входом узла регистров блока обработки системного контроллера 93 и соединен с тактовыми входами третьего 114, пятого 116, шестого 117 и седьмого 118 регистров, первой 120 группы триггеров и второго 121 триггера, информационный вход которого является первым сигналом двенадцатой 104 группы входов, второй, третий, четвертый, пятый и шестой сигналы которой соединены с первым, вторым, третьим, четвертым и пятым входами второго 124 мультиплексора, седьмой вход которого соединен с разрешающим входом шестого 117 регистра и седьмым сигналом двенадцатой 104 группы входов узла регистров блока обработки системного контроллера 93, тринадцатый и четырнадцатый сигналы двенадцатой 104 группы входов которого соединены с разрешающим входом пятого 116 регистра и с разрешающим входом четвертого 115 регистра и восьмым входом второго 124 мультиплексора, девятый вход которого соединен с разрешающим входом седьмого 118 регистра и пятнадцатым сигналом двенадцатой 104 группы входов узла регистров блока обработки системного контроллера 93, шестнадцатый и семнадцатый сигналы двенадцатой 104 группы входов которого соединены с разрешающими входами третьего 114 и второго 113 регистров, тактовый вход которого является четвертым 44 входом узла регистров блока обработки системного контроллера 93, пятая 111 группа выходов состоит из группы выходов седьмого 118 регистра, выхода второго 121 триггера и шестого 109 входа узла регистров блока обработки системного контроллера 93 и соединена с третьей группой входов второго 124 мультиплексора, четвертая группа входов которого является второй 101 группой входов узла регистров блока обработки системного контроллера 93, второй 99 выход которого соединен с выходом группы элементов исключающее ИЛИ 122, причем первая 100, третья 102, четвертая 103, пятая 78 и шестая 79 группы входов узла регистров блока обработки системного контроллера 93 соединены с пятой, шестой, седьмой, восьмой и девятой группами входов второго 124 мультиплексора, первый и второй инверсные входы которого являются седьмой 39 группой входов узла регистров блока обработки системного контроллера 93, тринадцатая 48 группа входов которого соединена с первой 120 группой триггеров, группа выходов которой соединена с десятой группой входов второго 124 мультиплексора, причем первый 68 вход узла регистров блока обработки системного контроллера 93 соединен с инверсным входом четвертого 115 регистра, третий 106 вход узла регистров блока обработки системного контроллера 93 соединен с инверсными входами второго 113, третьего 114, пятого 116, шестого 117, седьмого 118 и восьмого 119 регистров, первой 120 группы триггеров и второго 121 триггера, восемнадцатый сигнал двенадцатой 104 группы входов соединен с прямым и инверсным входами первого 123 мультиплексора, девятнадцатый сигнал двенадцатой 104 группы входов соединен с разрешающим входом восьмого 119 регистра.

Узел прерываний 92 блока обработки системного контроллера 71 состоит первого 125 счетчика, второго 126 счетчика, третьего 127 счетчика, четвертого 128 счетчика, первого 129 дешифратора, второго 130 дешифратора, третьего 131 дешифратора, четвертого 132 дешифратора, формирователя сдвигов и одиночных импульсов 133, первого 134 триггера, второго 135 триггера, третьего 136 триггера, четвертого 137 триггера, пятого 138 триггера, шестого 139 триггера, седьмого 140 триггера, восьмого 141 триггера, девятого 142 триггера, десятого 143 триггера, одиннадцатого 144 триггера, двенадцатого 145 триггера, первого 146 элемента И, второго 147 элемента И, третьего 148 элемента И, четвертого 149 элемента И, элемента 150 ИЛИ, инверсный выход которого является третьим сигналом первой 45 группы выходов узла прерываний 92, первый и второй сигналы которой соединены с инверсными выходами десятого 143 и восьмого 141 триггеров, прямой выход которого является вторым сигналом второй 100 группы выходов узла прерываний 92, первый, третий и четвертый сигналы которой соединены с выходами шестого 139, десятого 143 и двенадцатого 145 триггеров соответственно, тактовые входы которых соединены с тактовыми входами первого 134, второго 135, третьего 136, четвертого 137, пятого 138, седьмого 140, восьмого 141, девятого 142 и одиннадцатого 144 триггеров, первого 125, второго 126, третьего 127 и четвертого 128 счетчиков и являются третьим 84 входом узла прерываний 92, первый выход INTB1 49-1 которого соединен с информационным входом третьего 127 счетчика и выходом четвертого 137 триггера, информационный вход которого соединен с первым выходом формирователя сдвигов и одиночных импульсов 133, второй выход которого соединен с информационным входом третьего 136 триггера, выход которого является первым сигналом первой группы входов формирователя сдвигов и одиночных импульсов 133, второй, третий и четвертый сигналы которой соединены с выходами седьмого 140, девятого 142 и одиннадцатого 144 триггеров, информационные входы которых являются вторым, четвертым и шестым сигналами группы выходов формирователя сдвигов и одиночных импульсов133, а информационные входы шестого 139, восьмого 141, десятого 143 и двенадцатого 145 триггеров являются первым, третьим, пятым и седьмым сигналами группы выходов формирователя сдвигов и одиночных импульсов 133 соответственно, третий выход которого соединен с информационным входом пятого 138 триггера, выход которого соединен с информационным входом четвертого 128 счетчика и является вторым INTB2 49-2 выходом узла прерываний 92, первая 64 группа входов которого соединена с информационным входом первого 125 счетчика и первым инверсным входом первого 146 элемента И и с информационным входом второго 126 счетчика и первым инверсным входом второго 147 элемента И, выход которого соединен со сбросовым входом второго 126 счетчика, группа выходов которого соединена с группой входов второго 130 дешифратора, выход которого соединен с информационным входом второго 135 триггера, выход которого соединен с первым входом формирователя сдвигов и одиночных импульсов 133, второй вход которого соединен с выходом первого 134 триггера, информационный вход которого соединен с выходом первого 129 дешифратора, группа входов которого соединена с группой выходов первого 125 счетчика, сбросовый вход которого соединен с выходом первого 146 элемента И, второй вход которого соединен со вторыми входами второго 147, третьего 148 и четвертого 149 элементов И, со сбросовыми входами первого 134, второго 135, третьего 136, шестого 139, седьмого 140, восьмого 141, девятого 142, десятого 143, одиннадцатого 144, двенадцатого 145 триггеров и является вторым 106 входом узла прерываний 92, первый SA(0) и четвертый 108 входы которого соединены с третьим и четвертым входами формирователя сдвигов и одиночных импульсов 133, причем группа выходов третьего 127 счетчика соединена с группой входов третьего 131 дешифратора, выход которого соединен с первым входом третьего 148 элемента И, выход которого соединен со сбросовыми входами третьего 127 счетчика и четвертого 137 триггера, группа выходов четвертого 128 счетчика соединена с группой входов четвертого 132 дешифратора, выход которого соединен с первым входом четвертого 149 элемента И, выход которого соединен со сбросовыми входами четвертого 128 счетчика и пятого 138 триггера, причем вторая группа входов формирователя сдвигов и одиночных импульсов 133 соединена со второй 111 группой входов узла прерываний 92, причем выходы шестого 139 и двенадцатого 145 триггеров соединены с первым и вторым входами элемента ИЛИ 150.

Контроллер RS-485 94 состоит из первого 151 счетчика, второго 152 счетчика, третьего 153 счетчика, четвертого 154 счетчика, первого 155 мультиплексора, второго 156 мультиплексора, третьего 157 мультиплексора, узла регистров 158 RS-485, MCRS 159, первой 160 константы, второй 161 константы, первого 162 триггера, второго 163 триггера, третьего 164 триггера, четвертого 165 триггера и дешифратора 166, первый выход которого соединен с установочным и сбросовым входами четвертого 165 триггера, выход 169 которого соединен с первыми входами узла регистров 158 RS-485 и MCRS 159, первый выход которой соединен с информационным входом первого 162 триггера, инверсный и прямой выходы которого соединены с шестым 58 и седьмым 109 выходами контроллера RS-485 94, первый 54 и третий 56 выходы которого соединены с первым и вторым выходами узла регистров 158 RS-485, второй вход которого соединен с выходом второго 163 триггера, вторым 55 и четвертым 57 выходами контроллера RS-485 94, пятый 57 выход которого соединен с «корпусом», первая 81, вторая 101, третья 102 и четвертая 103 группы выходов контроллера RS-485 94 соединены с первой, второй, третьей и четвертой группами входов узла регистров 158 RS-485, пятая 167 группа выходов которого соединена с первыми группами входов первого 155 и второго 156 мультиплексоров и машиной состояний MCRS 159, второй выход которой соединен со сбросовым входом первого 162 триггера, тактовый вход которого соединен с третьим входом узла регистров 158 RS-485 и является четвертым 84 входом контроллера RS-485 94, шина данных 8 которого соединена с первой группой входов узла регистров 158 RS-485, вторая группа входов которого соединена с первой 39 группой входов контроллера RS-485 94, вторая 110 группа входов которого соединена с третьей группой входов узла регистров 158 RS-485, четвертая группа входов которого соединена с первой 168 группой выходов машины состояний MCRS 159, вторая группа входов которой соединена с группой выходов первого 151 счетчика, тактовый вход которого соединен с тактовыми входами второго 152, третьего 153 и четвертого 154 счетчиков, второго 163 триггера, с четвертым входом узла регистров 158 RS-485 и является пятым 61 входом контроллера RS-485 94, первый 68 вход которого соединен с пятым входом узла регистров 158 RS-485, со сбросовыми входами первого 151 и четвертого 154 счетчиков и второго 163 триггера, с установочными входами второго 152 и третьего 153 счетчиков, группа выходов которого соединена с третьей группой входов машины состояний MCRS 159, третий и четвертый выходы которой соединены с информационным входом второго 163 триггера и установочным входом четвертого 154 счетчика, группа выходов которого соединена с группой входов дешифратора 166, второй выход которого соединен с установочным и инверсным сбросовым входами третьего 164 триггера, выход которого соединен с третьим входом машины состояний MCRS 159, причем третья 111 группа входов контроллера RS-485 94 соединена с четвертой группой входов машины состояний MCRS 159, пятый и шестой выходы которой соединены с первым и вторым входами третьего 157 мультиплексора, группа выходов которого соединена с информационной группой четвертого 154 счетчика, разрешающий вход которого соединен с седьмым выходом машины состояний MCRS 159, восьмой выход которой соединен с инверсным разрешающим входом первого 151 счетчика, девятый и десятый выходы машины состояний MCRS 159 соединены с первым и вторым входами второго 156 мультиплексора, группа выходов которого соединена с информационной группой третьего 153 счетчика, инверсный разрешающий вход которого соединен с одиннадцатым выходом машины состояний MCRS 159, двенадцатый выход которой соединен с инверсным разрешающим входом второго 152 счетчика и первым входом первого 155 мультиплексора, группа выходов которого соединена с информационной группой входов второго 152 счетчика, выход которого соединен со вторым входом машины состояний MCRS 159, тринадцатый выход которой соединен со вторым входом первого 155 мультиплексора, вторая группа входов которого соединена с группой выходов первой 160 константы и со второй группой входов второго 156 мультиплексора, причем первая и вторая группы выходов второй 161 константы соединены с первой и второй группами входов третьего 157 мультиплексора, второй 99 и третий 106 входы контроллера RS-485 94 соединены с шестым и седьмым входами узла регистров 158 RS-485, восьмой и девятый входы которого соединены с шестым 52 и седьмым 53 входами контроллера RS-485 94.

Узел регистров 158 RS-485 состоит из первого 170 регистра, второго 171 регистра, третьего 172 регистра, четвертого 173 регистра, пятого 174 регистра, шестого 175 регистра, седьмого 176 регистра, первого 177 сдвигового регистра, второго 178 сдвигового регистра, третьего 179 сдвигового регистра, четвертого 180 сдвигового регистра, первого 181 мультиплексора, второго 182 мультиплексора, первой 183 группы элементов исключающее ИЛИ, второй 184 группы элементов исключающее ИЛИ, третьей 185 группы элементов исключающее ИЛИ, четвертой 186 группы элементов исключающее ИЛИ, сумматора 187, элемента И 188, выход которого соединен со сбросовым входом первого 170 регистра, информационная группа входов которого соединена с первой 8 группой входов узла регистров 158 RS-485, первая 81 группа выходов которого соединена с группой выходов четвертого 173 регистра, информационная группа входов которого соединена с информационными группами входов второго 171 и седьмого 176 регистров и выходами первого 177 и второго 178 сдвиговых регистров и является пятой 167 группой выходов узла регистров 158 RS-485, вторая 101 группа выходов которого соединена с группой выходов шестого 175 регистра, информационная группа входов которого соединена с группой выходов сумматора 187, первая группа входов которого соединена с группой выходов пятого 174 регистра, информационная группа входов которого является четвертой 103 группой выходов узла регистров 158 RS-485 и соединена с группой выходов второго 171 регистра, информационной группой входов третьего 172 регистра и группой входов второй 184 группы элементов исключающее ИЛИ, выход которой соединен с первым инверсным входом второго 182 мультиплексора, группа выходов которого соединена с информационными группами входов третьего 179 и четвертого 180 сдвиговых регистров, выходы которых являются первым 54 и вторым 56 выходами узла регистров 158 RS-485, третья 102 группа выходов которого соединена с группой выходов седьмого 176 регистра, первой группой входов второго 182 мультиплексора и группой входов четвертой 186 группы элементов исключающее ИЛИ, выход которой соединен со вторым инверсным входом второго 182 мультиплексора, вторая группа входов которого соединена с группой выходов первого 181 мультиплексора, группа входов которого соединена с группой выходов первого 170 регистра и группой входов первой 183 группы элементов исключающее ИЛИ, выход которой соединен с третьим инверсным входом второго 182 мультиплексора, третья группа входов которого соединена с группой выходов третьего 172 регистра и группой входов третьей 185 группы элементов исключающее ИЛИ, выход которой соединен с четвертым инверсным входом второго 182 мультиплексора, четвертая группа входов которого соединена с третьей 110 группой входов узла регистров 158 RS-485, вторая 39 группа входов которого соединена с разрешающим и тактовым входами первого 170 регистра, причем первый сигнал четвертой168 группы входов соединен с разрешающим входом второго 171 регистра, второй сигнал соединен с разрешающим входом третьего 172 регистра, третий сигнал соединен с разрешающими входами первого 177 и второго 178 сдвиговых регистров, четвертый сигнал соединено разрешающим входом четвертого 173 регистра, пятый сигнал соединен с прямым и инверсным входами первого 181 мультиплексора, шестой, седьмой, восьмой и девятый сигналы соединены с первым, вторым, третьим и четвертым входами второго 182 мультиплексора, пятый вход которого соединен со вторым 55 входом узла регистров 158 RS-485, первый 169 вход которого соединен с первым инверсным входом элемента И 188, второй инверсный вход которого соединен со сбросовыми входами пятого 174 и шестого 175 регистров, сумматора 187 и является седьмым 106 входом узла регистров 158 RS-485, третий 84 вход которого соединен с тактовыми входами пятого 174, шестого 175 регистров и сумматора 187, первый вход которого соединен с питанием (3.3в), причем четвертый 61 вход узла регистров 158 RS-485 соединен с тактовыми входами второго171, третьего 172, четвертого 173 и седьмого 176 регистров, первого 177, второго 178, третьего 179 и четвертого 180 сдвиговых регистров, сбросовые входы которых соединены между собой и являются пятым 68 входом узла регистров 158 RS-485, шестой 99 вход которого соединен с пятым инверсным входом второго 182 мультиплексора, причем восьмой 52 и девятый 53 входы узла регистров 158 RS-485 соединены с информационными входами первого 177 и второго 178 сдвиговых регистров.

Бортовой спецвычислитель работает следующим образом.

Специализированная цифровая обработка сигналов (ЦОС) - мощное средство повышения эффективности функционирования современных радиолокационных станций (РЛС). К числу основных преимуществ ЦОС можно отнести получение стабильных характеристик РЛС в широком диапазоне условий эксплуатации; возможности реализации сложных, адаптивных алгоритмов обработки без ущерба для точности и других показателей эффективности; возможность модернизации аппаратуры за счет модификации программного обеспечения (ПО). Переход к программируемым цифровым устройствам принципиально изменил подход при разработке и проектировании специализированной аппаратуры ЦОС. Существенно возросла роль алгоритмов обработки, которые практически полностью определяют эффективность аппаратуры ЦОС.

Цифровой Процессор Обработки Сигналов бортового спецвычислителя спроектирован как однокристальная трехпроцессорная "система на кристалле" на базе IP-ядерной платформы «МУЛЬТИКОР» [3] (далее по тексту Процессор 1).

Процессор 1 сочетает в себе лучшие качества двух классов приборов микроконтроллеров и цифровых процессоров обработки сигналов, что особенно важно для микроминиатюрных встраиваемых применений, когда одновременно приходится решать в рамках ограниченных габаритов задачи управления и высокоточной обработки информации, включая сигналы и изображение.

Архитектура аппаратной части близка к архитектуре универсальной ЭВМ и за счет рационального распределения вычислительных ресурсов и объема памяти ее можно оптимизировать, что не исключает возможности в готовой аппаратуре изменять рабочие программы. Эти свойства позволяют получить гибкую аппаратуру, которая в процессе эксплуатации может быть перестроена под решение различных задач.

Анализ технических параметров доплеровской радиолокационной станции (РЛС) показывает, что базой при обработке радиолокационных сигналов в частотной области является быстрое преобразование Хартли. Быстрое преобразование Хартли оптимальнее в количестве операций и времени их выполнения (20%), чем преобразование Фурье [4].

Структурная схема бортового спецвычислителя представлена на фиг.1.

Бортовой спецвычислитель обеспечивает:

- программное быстрое преобразование Хартли;

- прием четырех аналоговых сигналов 6 на 14-разрядный АЦП (2, 3, 4, 5) с защитой от переполнения разрядной сетки с преобразованием сигналов в цифровой код 40, 41, 42, 43;

- прием и исполнение двух 64-радиальных векторных прерываний:

- первое - 10 Гц;

- второе - 100 Гц (начало работы);

- выдачу двух радиальных прерываний 49 по инициативе программы вычислителя;

- исполнение программ пользователя;

- проведение тестового самоконтроля при начальном включении и по внешней команде с выдачей сигнала GOTOV 65 при положительном результате самоконтроля.

Бортовой спецвычислитель (БСВ) состоит из:

Процессора 1, ПЗУ 29 (4 Мбайта), ОЗУ 7 (4 Мбайта), двухпортового ОЗУ 13 (8-132Кх18бит), мультиплексного канала обмена 17 по ГОСТ 26765.52-87, первого 24 приемопередатчика мультиплексного канал обмена, второго 25 приемопередатчика мультиплексного канал обмена, системного контроллера 30, первого 2 АЦП, второго 3 АЦП, третьего 4 АЦП и четвертого 5 АЦП, первого 31, второго 32, третьего 33 и четвертого 34 приемопередатчика RS-485 и узла сброса 35.

Процессор 1 реализован на основе ядер из библиотеки платформы «МУЛЬТИКОР»: процессорного RISC - ядра RISCore32 с архитектурой MIPS32 (для CPU) и программируемого ядра с 2SIMD (Single Instructions Multiple Data) архитектурой цифрового сигнального процессора (DSP) с плавающей/фиксированной точкой ELcore-26 (ELcore=Elvees's core).

Центральный процессор (CPU):

- Архитектура - MIPS32;

- 32-битные шины передачи адреса и данных;

- Кэш команд объемом 16 Кбайт:

- Архитектура привилегированных ресурсов в стиле ядра R4000:

- Регистры Count/Compare для прерываний реального времени;

- Отдельный вектор обработки исключений по прерываниям;

- Программируемое устройство управления памятью:

- Два режима работы - с TLB (Translation Lookaside Buffer) и FM (Fixed Mapped);

- 16 строк в режиме TLB.

- Устройство умножения и деления;

- JTAG IEEE 1149.1, встроенные средства отладки программ;

- Производительность - 120 млн. оп/сек (здесь и далее параметры производительности приведены при тактовой частоте 120 МГц);

- Оперативная память центрального процессора (CRAM) объемом 32 Кбайт;

- 5 внешних запросов прерывания, в том числе немаскируемое прерывание (NMI).

Два цифровых сигнальных сопроцессора (DSPO-DSP1), каждый из которых характеризуется следующими возможностями:

- "Гарвардская" RISC - подобная архитектура с оригинальной системой команд и преимущественно однотактным исполнением инструкций;

- 2SIMD (Single Instruction Multiple Data) организация потоков команд и данных;

- Набор инструкций, совмещающий процедуры обработки и пересылки;

- 3-ступенчатый конвейер по выполнению 32- и 64-разрядных инструкций;

- Расширенные возможности по динамическому диапазону обрабатываемых данных, позволяющие обрабатывать данные в 8/16/32-разрядных форматах с фиксированной точкой, либо в одном из форматов с плавающей точкой - 24Е8 (стандарт IEEE 754) или 32Е16 (расширенный формат). Обеспечение при этом компромиссного выбора между точностью и производительностью. Аппаратные меры повышения точности и динамического диапазона (блочная плавающая точка; режим насыщения; инструкции преобразования форматов);

- Аппаратная поддержка программных циклов;

- Программная совместимость снизу с сигнальным контроллером 1892 ВМ2Т;

- Память программ PRAM объемом 16 Кбайт;

- Двухпортовые памяти данных XRAM и YRAM объемом 96 и 32 Кбайт соответственно;

- Пиковая производительность, обеспечиваемая двумя DSP-ядрами:

- 1440 млн. оп/с 32-битных операций с плавающей точкой (IEEE 754);

- 8640 млн. оп/с 8-битных операций с фиксированной точкой;

- 3840 млн. оп/с 16-битных операций с фиксированной точкой;

- 1920 млн. оп/с 32-битных операций с фиксированной точкой. D Порт внешней памяти (MPORT):

- Шина данных - 64 разряда, шина адреса - 32 разряда;

- Поддержка асинхронной памяти типа SRAM, ROM, FLASH;

- Поддержка синхронной памяти типа SDRAM;

- Поддержка синхронной статической памяти типа SBSRAM;

- Программное конфигурирование типа блока памяти и его объема;

- Программное задание циклов ожидания;

- Формирование сигналов выборки 5 блоков внешней памяти;

- Обеспечение обслуживания 4 внешних прерываний;

- Перевод SDRAM в режим энергосбережения. Контроллер PCI (PMSC - PCI Master-Slave controller):

- Соответствует спецификации Local Bus Specification. Rev. 2.2;

- Тактовая частота - до 100 МГц;

- Разрядность - 32 разряда;

- Режимы Master и Slave;

- 2 канала DMA;

- Встроен арбитр с циклически изменяемыми приоритетами запросов. Периферийные устройства:

- 14 - канальный контроллер прямого доступа в память (DMA). 4 внешних запроса прямого доступа. Специальные режимы синхронизации. Поддержка 2-мерной и разрядно-инверсной адресации. Режим передачи Flyby, подобный реализованному BADSP-TS201: внешнее устройство ⇔ внешняя память;

- четыре линковых порта (LPORT), совместимые с ADSP21160. Имеется режим работы в качестве портов ввода-вывода общего назначения (GPIO);

- универсальный асинхронный порт (UART) типа 16550;

- 32-разрядный интервальный таймер (IT);

- 32-разрядный таймер реального времени (RTT);

32-разрядный сторожевой таймер (WDT).

Объем ОЗУ 7 составляет 4 Мбайта с организацией 8×512К×8. В качестве ОЗУ 7 используются микросхемы памяти AS7C4096 фирмы Alliance Semiconductor. Подключение ОЗУ 7 к процессору 1 позволяет достичь максимальной производительности при заданной частоте. Цикл (SCLK) 11, 12 записи-чтения равен 3SCLK. Время передачи-приема одного 64-разрядного слова данных между внешней памятью и внутренней памятью процессора 1 равно 3SCLK+N (где N - число тактов ожидания).

Объем ПЗУ 29 составляет 4 Мбайта с организацией 4×512К×16. В качестве ПЗУ 29 используются микросхемы памяти FLASH-типа Am29LV800B фирмы AMD, не требующие высокого напряжения для программировая. 4 Мбайта FLASH включают также и системное ПЗУ емкостью не менее 128Кбайт, предназначенное для организации включения БСВ и для загрузки остальной части FLASH. Темп чтения из памяти составляет 2×3SCLK+SCLK×N. Время выборки - 90 нс.

Прием четырех аналоговых сигналов на четыре 14-разрядный АЦП (2, 3, 4, 5) с защитой от переполнения разрядной сетки с преобразованием сигналов в цифровой код 40, 41, 42, 43. Дифференциальный сигнал поступает на каждое АЦП через трансформатор 6, выполняющий роль развязки по питанию. В качестве АЦП используются микросхемы AD9244 фирмы Analog Devices. Отличительными особенностями данного АЦП являются дифференциальный вход, наличие выходного сигнала превышения входного порога и низкий «Jitter» - дрожание внутренней тактовой частоты 0.3pS. В состав АЦП входит устройство выборки и хранения, позволяющие оцифровывать сигнал промежуточной частоты на низкой частоте. На устройство АЦП с приемника поступает частота 18 МГц 44, из которой путем деления на 70 формируется сигнал оцифровки. По сигналу НМ 66 (начало массива), также поступающему с приемника, БСВ начинает прием выборок.

Первый отсчет с выхода АЦП поступает через 8 тактов, т.к. АЦП имеет конвейерную организацию.

Системный контроллер (СК) 30 организует обмен данными по каналам АЦП и с устройствами ввода-вывода.

Функциональная схема системного контроллера 30 представлена на фиг.2.

В состав СК входят блок обработки СК 71, первый 72 счетчик, формирующий тактовую частоту CLK50M 84, второй 73 счетчик, формирующий тактовую частоту MCLK 70 для контроллера мультиплексного канала 17, первое 74 FIFO для приема данных с АЦП, второе 75 FIFO для приема данных из контроллера RS_485, константа 76.

Функциональная схема блока обработки системного контроллера 71 представлена на фиг.3.

В состав блока обработки СК 71 входят первый 85 счетчик, второй 86 счетчик, регистр адреса 87, машина состояний 91, узел прерываний 92, узел регистров 93, контроллер RS-485 94, первый 88, второй 89 и третий 90 дешифраторы, первый 96 элемент И, второй 97 элемент И, элемент ИЛИ 98 и константа 95.

Управление работой СК 30 со стороны процессора 1 обеспечивается программируемыми регистрами. Адресация и назначение программируемых регистров представлено на фиг.13.

Программное обеспечение обработки сигналов предназначено для цифровой обработки радиолокационного сигнала. Прием четырех аналоговых сигналов с преобразованием сигналов в цифровой код осуществляется устройством АЦП, включающим в себя четыре независимых канала АЦП. Передача данных из системного контроллера 30 в процессор 1 производится в режиме прямого доступа к памяти, т.е.происходит передача данных между внешним устройством ввода-вывода (АЦП) и внешней памятью ОЗУ7, минуя процессор 1.

В состав программного обеспечения обработки сигнала входят:

- Программа настройки контроллера DMA для приема данных в активном режиме.

- Программа настройки контроллера DMA для приема данных в полуактивном режиме.

- Программа обработки прерывания IRQ1.

- Программа обработки прерывания IRQ2.

- Программа обработки прерывания MemCh0.

- Программа выполнения Функции преобразования Хартли.

Сигнал 44 18 МГц (ADCCLK) предназначен для формирования импульсов запуска АЦП с частотой дискретизации fД=18×106/70=257,142857.

Формирование частоты дискретизации выполняется счетчиком 86 блока обработки системного контроллера 71.

Сигнал 66 MM (начало массива) - импульс положителной полярности.

БСВ формирует массивы входных данных (оцифровывает входные аналоговые сигналы), начиная с фронта импульса 66 НМ (STROB). МС 91 блока обработки СК 71 формирует семнадцатый сигнал SCLKB четвертой 104 группы выходов, разрешая прием данных с регистра АЦПА 113 на регистр АЦПВ 114. Алгоритм работы МС 91 блока обработки системного контроллера 71 представлен на фиг.8, 8а, 8б, 8в, 8г.

На БСВ выдаются четыре дифференциальных аналоговых сигнала. На первое АЦП 2 поступает суммарный сигнал, на второе АЦПЗ поступает компенсационный сигнал, на третье АЦП4 поступает сигнал, определяющий «курс», на четвертое АЦП5 поступает сигнал, определяющий «тангаж». В АЦП данные преобразуются в 14-разрядные целые числа в прямом двоичном коде АСР 1 40, АСР 2 41, АСР 3 42 и АСР4 43.

БСВ работает в 2-х режимах: полуактивном (ПР) с частотой 10 Гц (грубая оценка) и активном (АР) с частотой 100 Гц (точная оценка) режимах. Режим работы задается в команде, поступающей в контроллер RS-485 94. В ПР режиме длительность аналогового сигнала, начиная с переднего фронта импульса НМ 66 составляет 875 мкс. Расположение отсчетов во времени относительно импульса НМ (STROB) 66 представлено на фиг.12а.

В АР режиме длительность аналогового сигнала, поступающего на цифровую обработку, начиная с переднего фронта импульса НМ 66, составляет 7.1 мс. Расчет спектра может быть проведен для всего сигнала длительностью 7.1 мс, а также отдельно для двух или трех перекрывающихся отрезков сигнала (пачек), с последующей некогерентной совместной обработкой этих пачек.

С целью оптимизации обработки сигнала, сокращения возможности образования комбинационных составляющих и сокращения времени обмена данными между БСВ и центральной ЭВМ в активном режиме все входные данные разбиты на три одинаковые пачки. Расположение отсчетов во времени относительно импульса MM (STROB) 66 представлено на фиг.12б.

Длительности трех перекрывающихся пачек сигнала, начиная с фронта импульса НМ, составляет 7124,444 мск=7,1 мс.

После приема данных на входной регистр 114 МС 91 блока обработки системного контроллера 71 формирует сигнал записи fifowrb (второй сигнал третьей группы выходов) в первое 74 FIFO, по которому принятые данные записываются в FIFO 74. При записи каждого отсчета содержимое счетчика количества слов 85 блока обработки системного контроллера 71 уменьшается на единицу.

Обмен данными между внешней памятью и СК выполняется через канал прямого доступа memch0. Канал MemCh0 имеет внешний сигнал запроса передачи (DMAR0), позволяющий организовывать эффективный обмен данными с внешними устройствами. Для работы по внешним запросам необходимо сначала настроить канал DMA, а затем активизировать внешнее устройство на формирование сигналов DMARO. Для управления работой каждого канала DMA имеются следующие регистры:

- регистр управления и состояния (CSR);

- набор регистров индекса (адрес памяти) и смещения (IOR, IR, OR, Y);

- регистр начального адреса блока параметров DMA передачи (СР).

Следует отметить, что индексные регистры IR и IOR содержат физические адреса памяти.

Для эффективной передачи двумерных массивов (матриц W[m;n]) все каналы DMA используют регистр Y, в котором хранятся смещение и число строк в направления Y.

Разные типы каналов содержат разный набор регистров.

Исходное состояние регистров CSR: разряды 15:0 - нули, а состояние разрядов 31:16 не определено. Исходное состояние остальных регистров не определено.

Индексный регистр содержит адрес 32-разрядного слова в памяти (младшие два разряда адреса должны быть равны нулю).

Регистр смещения задает приращение адреса. Содержимое регистра смещения, аппаратно умноженное на 4, прибавляется к индексу после передачи каждого слова.

Программа настройки контроллера DMA для приема данных в активном/полуактивном режиме производит следующие действия:

- Настраивает контроллер DMA для передачи данных из АЦП во внешнее ОЗУ, для чего каналу DMA MemCh0 ставится в соответствие устройство АЦП - выбор устройства АЦП будет осуществляться посредством сигналов (пое1 или ncs2) ипсв1;

- Анализирует содержимое ячейки 1700_0004, ожидая завершения предыдущей операции передачи данных, (значение ячейки 1700_0004 должно быть равно «0»), после чего записывает в эту ячейку длину передаваемого массива в активном/полуактивном режиме.

Обмен по прямому доступу начинается после получения контроллером DMA запроса на прямой доступ DMARO (первый сигнал второй группы входов 46), который формирует СК 30.

Для чего в регистр управления и состояния канала MemCh0 (0×b82f0800) записать код, разрешающий обмен 8-ью словами данных по внешнему запросу и прерыванию по окончании приема 8-ми слов (0×82401). По каждому переходу сигнала DMARO из «1» в «0» DMA выполняет процедуру передачи одной пачки слов размером в 8 слов данных. В индексный регистр (О×в82а080с) записать 0×150с0000, в регистр смещения внешней памяти (0×b82f0810) записать 0×1.

После записи 8-ми слов МС 91 блока обработки системного контроллера 71 формирует сигнал DMARO запрос на передачу данных из FIFO. Передача 8-ми слов из блока обработки СК 71 во внешнюю память 7 выполняется в соответствии с временной диаграммой, представленной на фиг.14. Инициатором записи является процессор 1, получив сигнал DMARO, он начинает формировать адрес 9, выборку ОЗУ 10 и сигнал записи 12, одновременно с этим блок обработки СК 71 выполняет чтение данных из FIFO 74 и данные 78 из FIFO передает на шину данных 8 процессора 1.

Функциональная схема узла регистров блока обработки системного контроллера 93 представлена на фиг.4.

Запись в регистр количества слов 117 осуществляется из БЦВМ как в ячейку памяти по адресу 17000004-ie. В режиме ПР количество слов равно 0×ХХХХ0200, а в режиме АР - 0×ХХХХ Ое58. По сигналу OSTROB, сформированному МС 91, содержимое 107 регистра количества слов 117 переписывается в счетчик количества слов 85.

Обмен данными продолжается до тех пор, пока содержимое счетчика количества слов 85 не будет равно нулю.

Для управления режимами работы и определения состояния блока обработки СК 71 введен регистр управления и состояний (RgU) 118. Назначение разрядов регистра управления и состояний представлено на фиг.15.

Регистр управления и состояний 118 доступен процессору1 как по записи, так и по чтению по адресу 0×17000000. Чтение регистра RgU 118 выполняется как чтение ячейки памяти.

Программа выполнения преобразования Хартли производит вызов функции преобразования Хартли в активном, либо в полуактивном режиме. В функцию передается адрес внешнего ОЗУ, где находятся входные данные, считанные с 4-х АЦП и расположенные поблочно. Преобразование выполняется для заданного числа отсчетов для каждого АЦП в зависимости от установленного режима: активный/ полуактивный. Результатом преобразования является массив действительных чисел в плавающем формате.

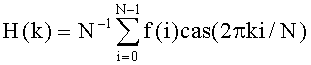

Преобразование Хартли является аналогом преобразования Фурье и может применяться для спектрального анализа, фильтрации и обработки сигналов. Обращение к преобразованию Хартли было обусловлено ситуацией, сложившейся в ряде методов обработки, использующих вещественные последовательности данных, обработку которых желательно осуществлять в области вещественных чисел. Преобразование Хартли осуществляет преобразования только в вещественной области, отображая вещественные сигналы s(t) в вещественные s(ω). Прямое и обратное преобразование Хартли взаимно симметричны [4].

На первый взгляд в формулах отсутствуют отличия от интегральных преобразований Фурье, однако на практике эти различия могут быть достаточго ощутимыми, что определяется вещественным характером функции H(k) (выигрышь в количестве операций и во времени составляет 20%).

Прежде чем приступить к вычислению преобразования Хартли необходимо выполнить нормализацию, т.е. вычесть постоянную составляющую, обеспечивающую представление отсчетов в формате с плавающей точкой.

Sni=(Sadc ni-8192)/4096,

где i=1, 2, 3 - номер пачки для АР;

n1=0..1023;

n2=0…1023;

n3=0…1023;

n=0…225 - для ПР.

Необходимо умножить отсчеты на весовую функцию для подавления боковых лепестков антенны.

В режиме АР отсчеты каждой пачки должны быть умножены на свою весовую функцию.

КАР(ni)=sin3(πni/1023),

где i=1, 2, 3 - номер пачки;

n1=0…1023;

n2=0…1023;

n3=0…1023.

В режиме ПР отсчеты каждой пачки должны быть умножены на свою весовую функцию.

KАП(n)=sin3(πn/225),

где n=0…225.

Выполнение быстрого преобразования Фурье (БПФ).

Для уменьшения количества операций при выполнении БПФ для вещественных отсчетов рекомендуется замена БПФ на быстрое преобразование Хартли(БПХ).

Дискретное преобразование Хартли Н(к) действительной функции f(i),

i=0, 1, …N-1, - определяется как сумма косинусного и синусного преобразований, т.е.:

k=0, 1, …N-1,

где casθ=cosθ+sinθ - ядро преобразования. Ядро преобразования (функция cas) является вещественным, то есть спектр Хартли действительного сигнала также является действительным. Преобразование строго симметрично: прямое и обратное преобразования Хартли одинаковы.

Преобразование Фурье F(k)=R(k)+j·X(k) можно получить с использованием ДПХ:

R(k)=(H(k)+H(N-k))/2; X(k)=-(H(k)-H(N-k))/2.

Для работы алгоритмов обнаружения и автосопровождения цели в сложных условиях помех требуется весь объем сигнальной информации (1620 16-разрядных слов). Передача полного объема данных займет около 3 мс, что значительно превышает отведенное для этих целей время 1.7-2 мс.

Основным перегружающим обмен фактором является необходимость передачи квадратурных составляющих (sin, cos) каждого замера каналов С (суммарный), К (курс), Т (тангаж) для вычисления ошибок углового сопровождения Δα и Δβ. Ошибки Δα и Δβ рассчитываются только по одному фильтру, тому, в котором находится сигнал цели, но его номер становится известен только после работы алгоритмов обнаружения цели. Расчет ошибок углового сопровождения производится алгоритмом «Фазовый дискриминатор»(ФД) [5].

Целесообразно расчитывать ошибки углового сопровождения в БСВ для каждого фильтра «Узкой гребенки». В DSP процессора 1, по накоплению данных одной полупачки, выполняется алгоритм БПХ. Сразу за этим алгоритмом нужно просчитать алгоритм ФД для той же полупачки. После просчета третьей полупачки необходимо усреднить Δα и Δβ по каждому фильтру. Избыточность данных окупается сокращением обмена между БСВ и БЦВМ в 9 раз (162 ошибки вместо 1485 квадратур).

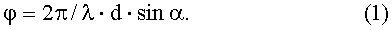

ФД предназначен для расчета сигналов ошибок сопровождения по углам (угловых рассогласований Δα и Δβ между равносигнальным направлением на цель по каналам курса и тангажа. Полученные в приемнике после выполнения алгоритма БПХ квадратурные составляющие из центрального частотного фильтра (то есть, из того, где находится максимум принимаемого сигнала) передаются на вход вычислительного алгоритма «ФД». Алгоритм ФД определяет сигналы ошибок углового сопровождения по углам между линией визирования (осью антенны) и напрвлением на цель по каналам К и Т. Формулы для вычисления угловых рассогласований Δα и Δβ для обоих каналов аналогичны. Для измерения угла α направления на цель используется моноимпульсный амплитудно-фазовый метод. Рассмотрим картину в одной плоскости, например тангажа (фиг.22). Две идентичные антенны А и В, имеющие одинаковые узкие диаграммы направленности (θ0,5=3÷4°), разнесены на расстояние d, где d - база. Фокальные оси антенн параллельны в пространстве и перпендикулярны к базе d. Поэтому падающая волна от далекой цели придет на обе антенны под одним углом α. Угол α - пеленг цели, равный углу между осью антенны и направлением на цель. Пеленг цели вызывает возникновение фаз φ между сигналами, принимаемыми антеннами А и В. Разность фаз φ принимаемых колебаний антеннами А и В будет равна:

Для малых углов можно считать: sinα~α (угол α в радианах). Для того чтобы значение α оставалось однозначно, необходимо выполнение условия sinα<<λ/2d. В данном случае это условие выполняется, так как диаграммы направленности (ДН) антенн А и В достаточно узкие.

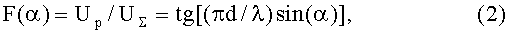

В СВЧ устройствах антенной системы образуются суммарный и разностный сигналы. Векторная диаграмма напряжений приведена на фиг.23. На антенны А и В принимаются сигналы с амплитудами U1 и разностью фаз между ними φ. Тогда согласно фиг.23 суммарный сигнал UΣ=2U1 cos(φ/2), а разностный сигнал Up=2U1sin(φ/2). Пелегационная характеристика будет иметь вид:

или

По определению, пеленгационная характеристика - это зависимость напряжения на выходе ФД от угла α, где α - угол между равносигнальным направлением и направлением на цель (пеленг цели - фиг.22).

В цифровой реализации фазового дискриминатора выходом алгоритма ФД являются ошибки углового сопровождения Δα и Δβ, на основе которых следящая система вырабатывает команды управления антенной для установки линии визирования на цель.

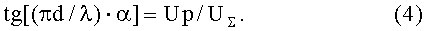

Для малых углов (α=2-2.5°) можно считать: sinα~α (угол α в радианах). Тогда формула (2) принимает вид:

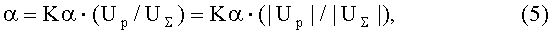

Из формулы (4) следует, что угол α пропорционален отношению Up/UΣ с коэффициентом пропорциональности Кα. Этот коэффициент называется крутизной пеленгационной характеристики по каналу тангажа (Т). Выражение для угла α можно записать в виде:

где Up и UΣ - разностный и суммарный векторы, а их модули |Up| и |UΣ|.

Угол пеленга цели α есть не что иное, как величина Δα=α.

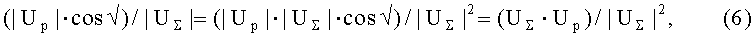

Для того чтобы в аппаратуре не приходилось вычислять квадратные корни, отношение модулей разностного и суммарного векторов можно выразить через скалярное произведение этих векторов:

где √ - угол между векторами UΣ и Up, а (UΣ·Up) - скалярное произведение векторов.

Разностный и суммарный векторы сдвинуты по фазе на 90°. Чтобы скалярное произведение векторов зависело только от значений модулей этих векторов и не зависело от угла √ между ними, нужно, чтобы разностный и суммарный векторы были коллинеальными (то есть лежали на одной прямой) и равнонаправленными.

На практике в приемном тракте существуют паразитные сдвиги фазы α0 и β0 (углы расфазировки α0 и β0) в каналах курса и тангажа, которые необходимо скомпенсировать. Для компенсации углов расфазировки α0 и β0 выполняются повороты полученных разностных векторов на углы α0 и β0. Заранее неизвестно, отрицательные или положительные эти углы расфазировок, поэтому, например, для разностного сигнала в канале тангажа компенсация осуществляется умножением вектора TCOS+j TSIN на экспоненту exp(j α0). Аналогичным образом выполняется компенсация в канале курса. Таким образом, до вычисления скалярного произведения разностного и суммарного векторов необходимо выполнить умножение соответствующего разностного вектора на экспоненту exp(j α0) или exp(j β0).

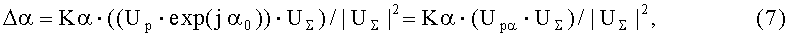

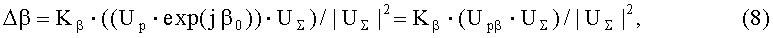

Выражение (5) для вычисления сигнала ошибки Δα принимает вид:

где Кα - крутизна пеленгационной характеристики по каналу тангажа, а Upα=Up·exp(j α0) - разностный вектор в канале тангажа, довернутый на угол расфазировки α0 для достижения коллинеарности и равнонаправленности с суммарным вектором UΣ.

Соответственно, для канала курса выражение (5) для вычисления сигнала ошибки Δβ принимает вид:

где Кβ - крутизна пеленгационной характеристики по каналу курса, а

Upβ=Up·exp(j β0) - разностный вектор в канале, довернутый на угол расфазировки β0 для достижения коллинеарности и равнонаправленности с суммарным вектором UΣ.

Крутизны Кα и Кβ используются для масштабирования сигналов ошибки, их значения близки к 1. Если углы расфазировки α0 и β0 по каналам равны нулю, то формулы (7) и (8) вырождаются в формулу для пеленгационной характеристики (2).

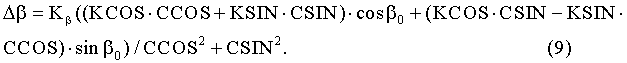

Раскрывая формулы (7) и (8) и выражая скалярное произведение через квадратурные составляющие векторов (компоненты векторов), мы получим следующие выражения для вычисления угловых рассогласований Δα и Δβ для обоих каналов:

Δα=Kα·((TCOS-CCOS+TSIN-CSIN)·cosα0+(TCOS-CSIN-TSIN-CCOS)·sinα0)/CCOS2+CSIN2;

Здесь обозначено: Кα и Кβ - крутизны пеленгационных характеристик по каналам тангажа и курса; TCOS, TSIN и KCOS, KSIN - квадратурные составляющие разностных векторов по каналам тангажа и курса соответственно; sinα0, cosα0 и sinβ0, cosβ0-sin и cos углов расфазировки α0 и β0 по каналам; CCOS2+CSIN2 - квадрат модуля суммарного сигнала (вектора).

В режиме ПР существует только один замер/поэтому вычисление по формулам (9) Δα и Δβ являются результатом работы алгоритма «фазовый дискриминатор».

В режиме АР производится три замера. По каждому замеру вычисляются величины Δα и Δβ по формулам (9). Выходом алгоритма «фазовый дискриминатор» являются усредненные значения угловых рассогласований по трем замерам..

По источнику прерывания все прерывания делятся на две группы: внутренние и внешние. Внутренние прерывания возникают внутри процессора 1, а внешние - в устройствах ввода-вывода.

Функциональная схема узла прерываний представлена на фиг.5.

Алгоритм работы узла прерываний представлен на фиг.9, 9а, 9б.

Прерывание IRQ1 формируется СК для задания полуактивного режима работы программы преобразования Хартли и.соответственно, задания полуактивного режима передачи данных из АЦП во внешнее ОЗУ. По этому прерыванию процессор 1 передает управление на программу обработки прерывания IRQ1, которая выполняет следующие действия:

- Запускает программу настройки контроллера DMA для приема данных в полуактивном режиме.

- Устанавливает признак «полуактивный режим» для программы преобразования Хартли.

По сигналам ADCCLK 44 или STROB 66, поступающим из приемника, СК формирует запрос на прямой доступ DMAR0. Канал MemCh0, получив внешний сигнал запроса передачи DMARO, начинает передачу данных из АЦП во внешнее ОЗУ. По концу обмена канал MemCh0 формирует прерывание от канала DMA MemCh0. По этому прерыванию процессор 1 передает управление на программу обработки прерывания MemCh0, которая выполняет следующие действия для приема очередного массива:

- Запускает программу настройки контроллера DMA для приема данных в активном/полуактивном режимах, в зависимости от того какой признак установлен для программы преобразования Хартли.

- Записывает значение длины массива (для активного/полуактивного режима) в ячейку 1777_0004.

СК 30 по внешним сигналам 10 Гц и 100 Гц (третья группа входов 64) формирует прерывания IRQ1 и IRQ2 (первая группа выходов 45).

Внешние прерывания имеют входные фильтры для защиты отложного срабатывания от помех. Первый сигнал 10 Гц первой 64 группы входов узла прерываний 92 поступает на информационный вход фильтра, состоящего из счетчика 126, дешифратора 130 и триггера 135, формирует сигнал FINT5-79, по которому формирователь сдвигов и одиночных импульсов 133 устанавливает триггер tgint5 143, формируя сигнал прерывания IRQ1 (первый сигнал первой группы выходов 45). Второй сигнал 100 Гц первой 64 группы входов узла прерываний 92 поступает на информационный вход фильтра, состоящего из счетчика 125, дешифратора 129 и триггера 134, формирует сигнал FINT4-79, по которому формирователь сдвигов и одиночных импульсов 133 устанавливает триггер tgint4 141, формируя сигнал прерывания IRQ2 (второй сигнал первой группы выходов 45). При появлении этих прерываний в регистре управления и состояний 118 устанавливаются в «1» двенадцатый и одиннадцатый разряды соответственно. Сброс каждого триггера возможен при записи «1» в восьмой и седьмой разряды регистра управления и состояний 118. Все прерывания могут быть замаскированы с помощью регистра маски (RgU(20), RgU(19)).

При записи в двадцать третий и двадцать четвертый разряды регистра управления и состояний 118 узла регистров блока обработки системного контроллера 93 «1» формируется адрес регистра RgU 118, который хранится в регистре адреса 87 блока обработки системного контроллера 93 и по сигналу sA(0) с дешифратора 90 разрешает запись (SWE) 108, формирователь сдвигов и одиночных импульсов 133 формирует выход один и выход два, устанавливая триггеры 137 и 138 «1». Сбросы этих триггеров выполнятся через 800 не, формируясь на счетчике 127 и дешифраторе 131 и счетчике 128 и дешифраторе 132 соответственно.

В узле регистров блока обработки системного контроллера 93 предусмотрены регистр выходных разовых команд 116 и группа триггеров входных разовых команд 120.

Программа поддержки канала связи RS-485 предназначена для организации обмена данными между БСВ и БЦВМ. Обмен производится в режиме прямого доступа к памяти, т.е. происходит передача данных между внешним устройством и внешней памятью. В состав программы поддержки канала связи RS-485 входят: программа обработки прерывания IRQO и программа обработки прерывания MemCh1.

Двунаправленный высокоскоростной интерфейс RS-485 предназначен для обмена информацией между БЦВМ и абонентами. Он представляет собой интерфейс, состоящий из приемников 33, 34, приемопередатчиков 31, 32 и линий передачи информации (ЛПИ) 50, 51, 59, 60. Передача информации происходит со скоростью не менее 10 Мбит/с. Инициатором обмена всегда является БЦВМ (далее контроллер). БВС по каналу RS-485 функционирует в режиме пассивного устройства (далее абонент). Абонент выполняет команды контроллера. Команды адресуются конкретному абоненту, «чужие» команды абонентом не воспринимаются. БВС присвоен двоичный адрес абонента - 0010.

Контроллер обмена RS-485 94 (абонент) с каналом RS-485 обеспечивает обмен данными, поступающими из БЦВМ.

Состав линий связи:

- SCLK (60)- сигнал синхронизации;

- C_D (59) - признак команда/данные;

- D0, D1 (50, 51) - линии приемопередачи данных.

SCLK - сигнал предназначен для синхронизации передаваемых данных. Источником синхронизации является контроллер, находящийся в БЦВМ. Частота сигнала - 6 МГц или 6.25 МГц.

C_D - однонаправленная линия с третьим состоянием, предназначенная для идентификации команд контроллера. При передаче данных и ответного слова абонента линия находится в состоянии "0". При отсутствии обменов в канале линия подтянута к "0".

D0, D1 - двунаправленные линии с третьим состоянием, предназначенные для обмена данными в параллельно-последовательном виде. В пассивном состоянии линии подтянуты к "1". Порядок передачи информации полициям D0, D1 представлен на фиг.17. Внутри контроллера данные инвертируются.

На фиг.18 представлены все допустимые команды, обязательные для исполнения абонентом. Любая другая команда абонентом игнорируется, но абонент обязан выдать контроллеру ответное слово с признаком «некорректная команда».

Обмен осуществляется словами по 18 бит (Пр+16 информационных бит+К). Минимальная посылка - два слова (включая команду), максимальная - 256 слов. Количество слов обмена задается контроллером в 9-16 разрядах команды. Выдача в линию битов происходит, начиная с младших разрядов. «К» - это контрольный разряд по модулю 2 (дополнение до нечетного числа единиц). Младший разряд слова «Пр» - признак команды, равен «1» если слово - команда или ответное слово, «0» - данные.

Перед выдачей в ЛПИ команды контроллер выставляет сигнал C_D=1, после выдачи - C_D=0.

Выполнение команды «Запись».

Контроллер последовательно выставляет C_D=1, выдает в ЛПИ команду записи, устанавливает признак данных C_D=0 и передает данные. Абонент, получив данные, не позднее, чем через 8 тактов, формирует и выдает ответное слово в ЛПИ.

Выполнение команды «Чтение».

Контроллер последовательно выставляет C_D=1, выдает в ЛПИ команду чтения, устанавливает C_D=0 и ожидает прихода данных. Абонент, получив команду, формирует и выдает ответное слово в ЛПИ (не позднее, чем через 8 тактов) и передает запрошенные данные.

Контроллер считает, что обмен заканчивается аварийно по таймауту при отсутствии ответного слова от абонента в течение 8 тактов после передачи команды и указанного числа слов данных.

Нормальным окончанием обмена контроллер считает прием (передачу) всех данных, наличие в положенное время ответного слова, отсутствие признаков ошибок в ответном слове и собственном слове состояния.

Описания форматов команд представлены на фиг.19-21.

Формат команд при выдаче в линию (начиная с младших разрядов) команды имеют формат (18-разрядное слово), представленный на фиг.19. Количество слов данных для передачи от 1 до 255. Коды команд представлены на фиг.18. Каждому абоненту присвоен уникальный двоичный адрес. Формат данных при выдаче в линию (начиная с младших разрядов) имеет формат (18-разрядное слово), представленный на фиг.20.

Формат ответного слова при выдаче в линию (начиная с младших разрядов) представлен на фиг.21,

где: Адрес абонента - уникальный двоичный адрес абонента;

Признак ОС=1111 и (Пр=1);

Принятая команда - код принятой команды;

Признаки - набор информационных признаков:

- 14р - некорректная команда;

- 15р - абонент занят (формируется программно);

- 16р - ошибка по четности в словах данных.

Началом ответного слова считается первая комбинация …01 в контроллере после передачи данных или перед приемом данных.

Действия абонента по получению команды.

По команде 0001 «сброс абонента» выполняется общий "сброс" и перезапуск программного обеспечения БСВ. Количество слов в этой команде не имеет значения.

По команде 0011 «прочитать последнюю достоверную команду» абонент передает контроллеру в качестве слова данных последнюю полученную достоверную команду (т.е. команду, которая соответствует фиг.18 и не имеет ошибок по четности командного слова или данных). Количество слов в этой команде не имеет значения.

По команде 0110 «прочитать состояние» абонент в качестве слова данных передает контроллеру свое слово состояния. Слово состояния абонента формируется программно в регистре состояния. Количество слов в этой команде не имеет значения.

По команде 1001 «записать данные без выдачи в аппаратуру» абоненту передается два слова данных. Первое слово - старшая, второе - младшая часть полного 32-разрядного физического адреса ОЗУ, начиная с которого располагается информационный массив для выполнения команд «прочитать данные из аппаратуры абонента» и «записать данные в аппаратуру абонента без записи в буфер». Полученное значение сохраняется в регистре указателя адреса. Если число слов отлично от двух, то содержимое указателя адреса не изменяется, и передается ответное слово с установленным признаком «некорректная команда». При выполнении абонентом команд 0100 «прочитать данные из аппаратуры абонента» и 1011 «записать данные в аппаратуру абонента без записи в буфер» производится чтение регистра указателя адреса с его последующим сбросом.

По команде 0101 «прочитать содержимое буфера абонента» контроллер читает два слова данных - содержимое регистра указателя адреса. Данная команда не приводит к сбросу регистра указателя.

По команде 0100 «прочитать данные из аппаратуры абонента» абонент передает контроллеру массив информации, начиная с адреса, на который установлен указатель. При поступлении следующей команды 0100 без предварительной установки регистра указателя адреса (т.е. значение регистра указателя адреса после сброса равно 0), программный указатель адреса остается установленным на ячейку ОЗУ, следующую за последним переданным информационным словом.

По команде 1011 «записать данные в аппаратуру абонента без записи в буфер» абонент принимает от контроллера указанное количество слов и записывает их в ячейки ОЗУ, начиная с адреса, на который установлен указатель. При поступлении следующей команды 1011 без предварительной установки регистра указателя адреса (т.е. значение регистра указателя адреса после сброса равно 0), программный указатель адреса остается установленным на ячейку ОЗУ, следующую за последним принятым информационным словом.

Действия абонента при сбоях обмена.

При получении абонентом недопустимой команды команда игнорируется и устанавливается признак «некорректная команда» в 14-ом разряде регистра состояния.

При обнаружении абонентом ошибки контроля по нечету при приеме команды команда игнорируется и ответное слово не выставляется во избежание возможных коллизий в ЛПИ.

Абонент должен фиксировать ошибку контроля по нечету при приеме данных в 16-ом разряде регистра ответного слова.

Если контроллер обнаруживает ошибки во время приема большого массива данных, он выдает сигнал C_D=1 в течение двух тактов SCLK, что означает сброс оконечного устройства БСВ, которое должно сформировать прерывание и установить признак аварийного прекращения обмена с абонентом.

Все команды, полученные абонентом во время информационного обмена, игнорируются, и ответное слово на новую команду не посылается.

Обмен по каналу RS-485 должен быть синхронизирован по времени относительно сигнала 100 Гц (второй сигнал третьей группы входов 64).

Функциональная схема контроллера RS-485 представлена на фиг.7. Функциональная схема узла регистров RS-485 представлена на фиг.6.

Алгоритм работы контроллера RS-485 представлен на фиг.10, 10а, 10б, 10в, 10г, 10д, 10е.

Обмен данными между внешней памятью и контроллером RS-485 94 выполняется через канал прямого доступа memch1. Канал MemCh1 имеет внешний сигнал запроса передачи (DMAR1), позволяющий организовывать эффективный обмен данными с внешними устройствами. Для работы по внешним запросам необходимо сначала настроить канал DMA, а затем активизировать внешнее устройство на формирование сигналов DMAR1 (второй сигнал второй 46 группы выходов СК 30). Для управления работой каждого канала DMA имеются следующие регистры:

- регистр управления и состояния (CSR); (0×b82f08000:0×82401);

- набор регистров индекса (адрес памяти) и смещения (IOR, IR, OR, Y); (0×b82f080c: 0×150c0000; 0×b82f0810:0×1);

- регистр начального адреса блока параметров DMA передачи (СР).

После приема команды записи ЗДББ или команды чтения СДББ контроллер RS-485 94 устанавливает сигнал прерывания IRQO в процессор 1, если данное прерывание не замаскировано (15 разряд СК 93) находится в «1») и одновременно устанавливает в «1» 14 разряд RgU. Процессор 1 прерывается, считывает содержимое регистра команд 171 узла регистров RS-485 158 по адресу 1700000816 и настраивает канал прямого доступа на прием количества слов, заданных в команде. Затем процессор 1 формирует разрешение на прямой доступ, записав «1» в 26 разряд RgU.

При появлении бита готовности (RgU(26)=«1» контроллер RS-485 устанавливает сигнал запроса передачи DMAR1 процессору 1. Канал MemCh1, получив внешний сигнал запроса передачи DMAR1, начинает обмен данными с внешним устройством. По концу обмена формируется прерывание от канала DMA MemCh1. По этому прерыванию управление передается на программу обработки прерывания MemCh1, которая производит: сброс прерывания от RS-485 записью в RgU(25)=«1», сброс признака «Готовность DMA» записью в RgU(26)=«0».

После приема данных на сдвиговые регистры 177 и 178 узла регистров RS-485 158 при выполнении команды записи, если есть разрешение на прямой доступ, формируется сигнал запроса на прямой доступ DMAR1 (второй сигнал второй 46 группы выходов СК 30), по которому процессор 1 обеспечивает прием данных из СК во внешнюю память в соответствии с фиг.14. После приема заданного в команде количества слов контроллер RS-485 94 формирует передачу в БЦВМ ответного слова, а процессор 1 прерывается по окончании обмена.

При выполнении команды чтения СДББ, если есть разрешение на прямой доступ, блок обработки СК 71 формирует сигнал запроса на прямой доступ DMAR1, по которому процессор 1 обеспечивает передачу данных из внешней памяти в регистр данных контроллера RS-485 94 в соответствии с фиг.16. Одновременно с этим контроллер RS-485 94 передает в БЦВМ ответное слово, затем переписывает содержимое регистра данных в сдвиговый регистр, формируя новый запрос на прямой доступ. После передачи заданного в команде количества слов процессор 1 прерывается по окончании обмена.

Запись в RgU и в регистр данных осуществляется из процессора 1, как в ячейки памяти по адресам 1700000016 и 1700000C16 соответственно.

Чтение из RgU и регистра команд осуществляется в процессор 1, как чтение из ячеек памяти по адресам 1700000016 и 1700000816 соответственно.

БСВ является оконечным устройством (ОУ) с адресом задаваемым перемычками на плате. Адрес ОУ определяется в системе. ОУ поддерживает следующие форматы обмена по МКО в соответствии с ГОСТ 26765.52-87:

- Формат 1 - прием данных от контроллера канала;

- Формат 2 - передача данных в контроллер канала;

- Формат 4 - прием команд управления от контроллера канала.

ОУ поддерживает обмен данными с контроллером канала по нерезервируемой линии передачи данных с характеристиками в соответствии с ГОСТ 26765.52-87. Схема подключения ОУ БСВ к линии передачи данных - с трансформаторным ответвителем 28. В состав канала обмена МКО входят двухпортовое ОЗУ 13, контроллер МКО 17, реализованный на ПЛИС, микросхема [6] и приемопередатчики 24, 25, осуществляющие электрофизическое сопряжение канала.

Источники информации

1. Авторское свидетельство SU 1569847 A1, G06F 15/332, 1990 г.

2. Устройство цифровой обработки радиолокационных сигналов на основе процессора 1879 ВМ1. Электроника, Наука, Технология, Бизнес, 3/2003.

3. ЦПОС-02 микросхема 1892 ВМ5Я ГУПНПЦ ЭЛВИС, Руководство пользователя.

4. Злобин С.Л, Стальной А.Я. "Двумерное быстрое преобразование Хартли в цифровой обработке изображений". Доклады 6-ой Международной конференции "Цифровая обработка сигналов и ее применение". Том 2, с.114-116. Труды РНТОРЭС им. А.С. Попова. М., Россия, 2004 г.

5. Ю.П. Гришин, В.П. Ипатов, Ю.М. Казаринов Радиотехнические системы, «Фазовый дискриминатор». М.: Высшая школа, 1990 г.

6. Микросхема XC95288XL-10PQ208I фирмы Xilinx.