Результат интеллектуальной деятельности: ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "ИСКЛЮЧАЮЩЕЕ ИЛИ" С МНОГОЗНАЧНЫМ ВНУТРЕННИМ ПРЕДСТАВЛЕНИЕМ СИГНАЛОВ

Вид РИД

Изобретение

Изобретение относится к области вычислительной техники, автоматики и может использоваться в различных цифровых структурах и системах автоматического управления, передачи информации и т.п.

В различных вычислительных и управляющих системах широко используются логические элементы «Исключающее ИЛИ» (ЛЭ), реализованные на основе эмиттерно-связанной логики [1-16], работающие по законам булевой алгебры и имеющие по выходу два логических состояния «0» и «1», характеризующихся низким и высоким потенциалами.

В работе [17], а также монографиях соавтора настоящей заявки [18-19] показано, что булева алгебра является частным случаем более общей линейной алгебры, практическая реализация которой в структуре вычислительных и логических устройств автоматики нового поколения требует создания специальной элементной базы, реализуемой на основе логики с многозначным внутренним представлением сигналов, в которой эквивалентом стандартного логического сигнала является квант тока I0. Заявляемое устройство «Исключающее ИЛИ» относится к этому типу логических элементов.

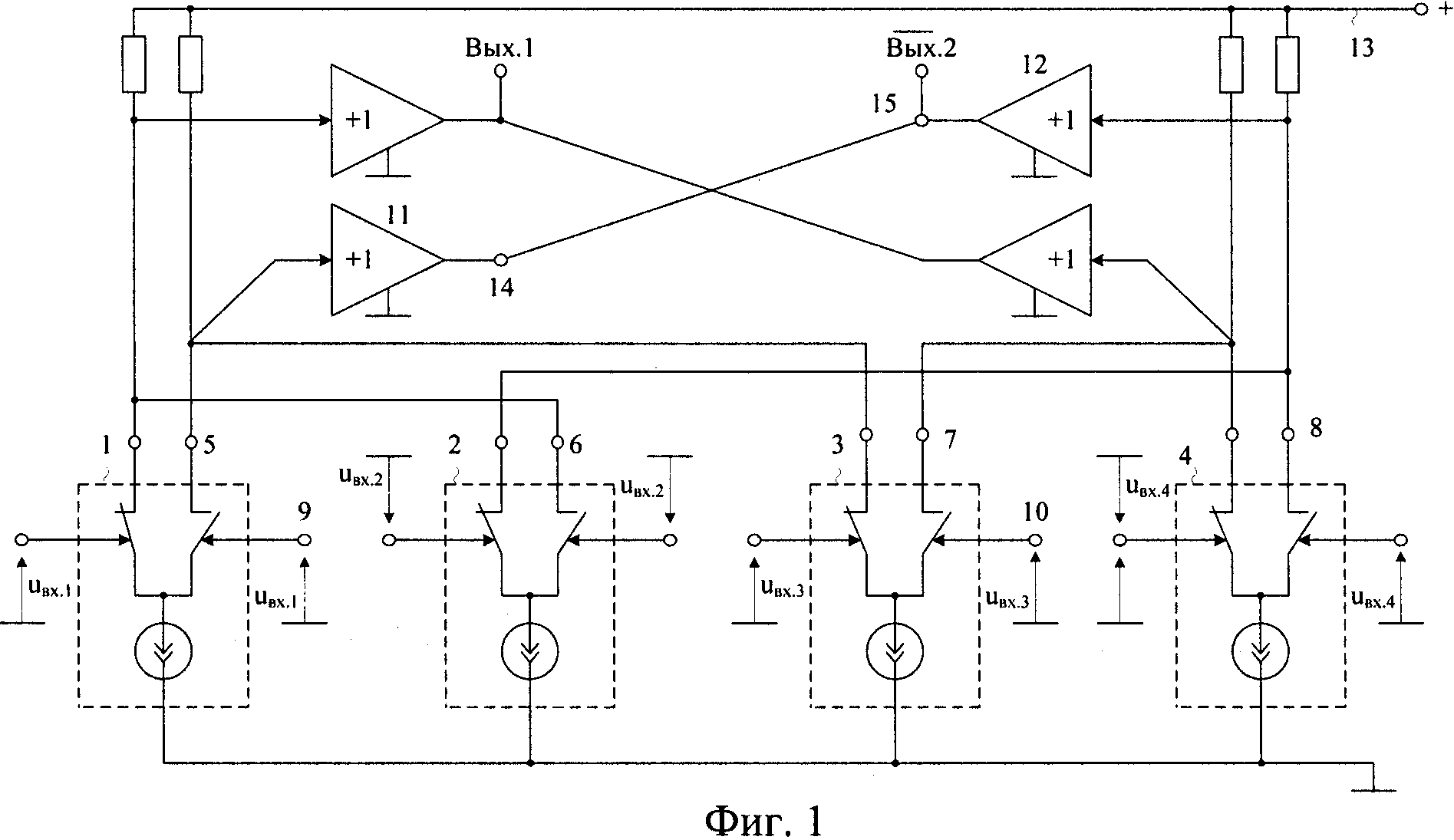

Ближайшим прототипом заявляемого устройства является логический элемент «Исключающее ИЛИ», представленный в патенте US 5.315.176, fig.1. Он содержит первый 1, второй 2, третий 3 и четвертый 4 коммутаторы квантов тока I0 с первым 5, вторым 6, третьим 7 и четвертым 8 соответствующими токовыми выходами, первый 9 и второй 10 источники входных логических сигналов, управляющих состоянием соответствующих коммутаторов квантов тока I0 (1, 2, 3, 4), первый 11 и второй 12 повторители выходных сигналов, согласованные с шиной источника питания 13, выходы которых 14 и 15 соединены друг с другом и являются выходом устройства.

Существенный недостаток известного логического элемента «Исключающее ИЛИ» состоит в том, что он, используя потенциальные двоичные сигналы, обладает усложненной структурой связей, нелинейностью рабочих режимов элементов и критичностью параметров структуры ЛЭ и входных сигналов, что в конечном итоге приводит к снижению его быстродействия.

Основная задача предлагаемого изобретения состоит в создании логического элемента «Исключающее ИЛИ», в котором внутреннее преобразование информации производится в многозначной токовой форме сигналов, определяемое состоянием входных потенциальных двоичных сигналов. В конечном итоге это позволяет повысить быстродействие и создать элементную базу вычислительных устройств, работающих на принципах многозначной линейной алгебры [18-19].

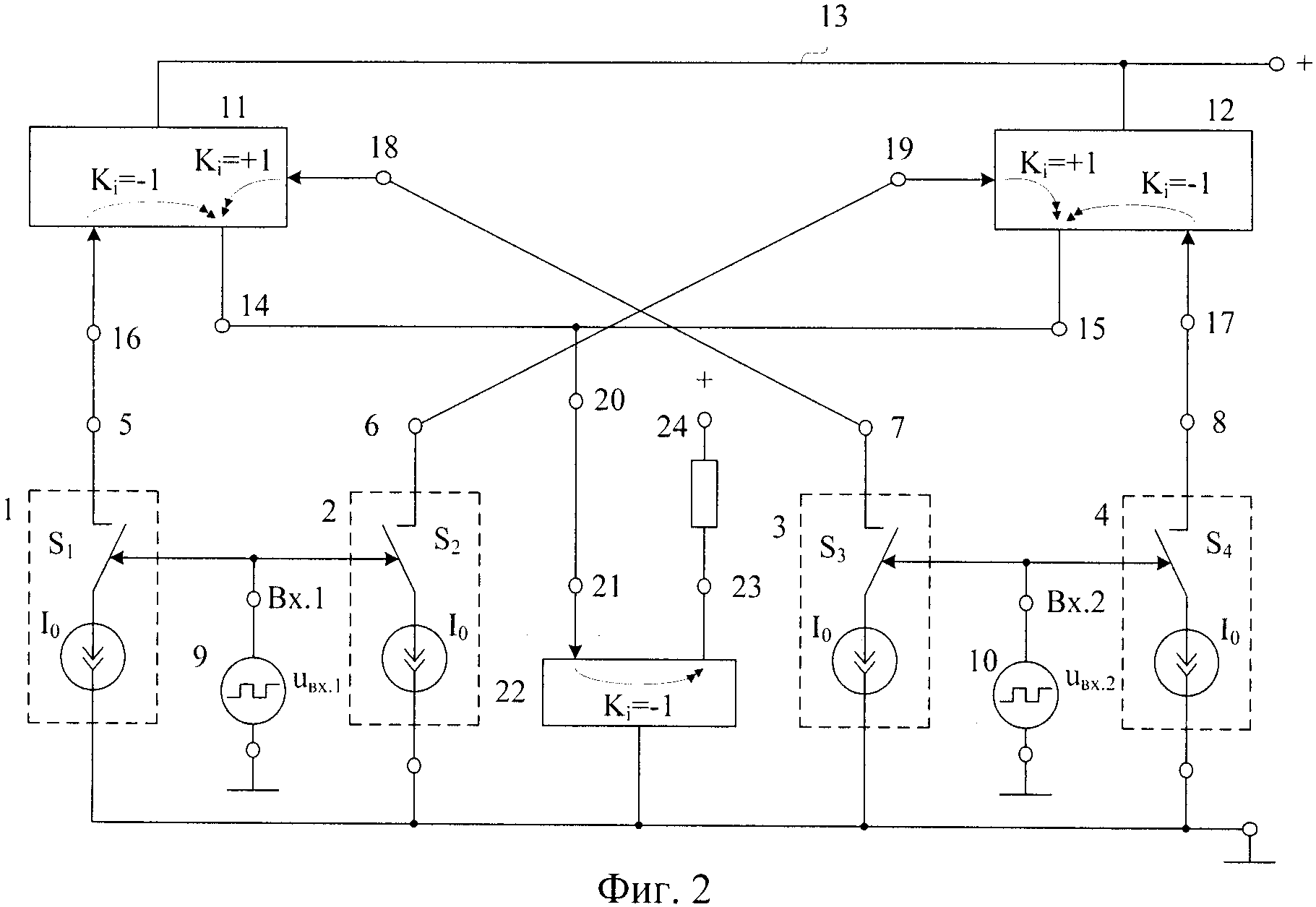

Поставленная задача решается тем, что в логическом элементе «Исключающее ИЛИ» с многозначным внутренним представлением сигналов (фиг.1), содержащем первый 1, второй 2, третий 3 и четвертый 4 коммутаторы квантов тока I0 с первым 5, вторым 6, третьим 7 и четвертым 8 соответствующими токовыми выходами, первый 9 и второй 10 источники входных логических сигналов, управляющих состоянием соответствующих коммутаторов квантов тока I0 (1, 2, 3, 4), первый 11 и второй 12 повторители выходных сигналов, согласованные с шиной источника питания 13, выходы которых 14 и 15 соединены друг с другом, предусмотрены новые элементы и связи - в качестве первого 11 и второго 12 повторителей сигнала используются токовые зеркала, каждое из которых имеет инвертирующий (18, 19) и неинвертирующий (16, 17) токовые входы, инвертирующий токовый вход 16 первого 11 токового зеркала соединен с токовым выходом 5 первого 1 коммутатора кванта тока I0, неинвертирующий вход 18 первого 11 токового зеркала соединен с токовым выходом 7 третьего 3 коммутатора кванта тока I0, инвертирующий вход 17 второго 12 токового зеркала соединен с токовым выходом 8 четвертого 4 коммутатора кванта тока I0, неинвертирующий вход 19 второго 12 токового зеркала соединен с токовым выходом 6 второго 2 коммутатора кванта тока I0, объединенные токовые выходы 14, 15 первого 11 и второго 12 токовых зеркал соединены с токовым выходом 20 устройства, причем первый источник входного логического сигнала 9 связан с управляющими входами первого 1 и второго 2 входных коммутаторов кванта тока I0, а второй источник входного логического сигнала 10 связан с управляющими входами третьего 3 и четвертого 4 входных коммутаторов кванта тока I0, а первый 1 и второй 2, а также третий 3 и четвертый 4 входные коммутаторы квантов тока I0 попарно синфазны.

Схема логического элемента «Исключающее ИЛИ»-прототипа показана на фиг.1. На фиг.2 представлена схема заявляемого устройства в соответствии с п.1-4 формулы изобретения.

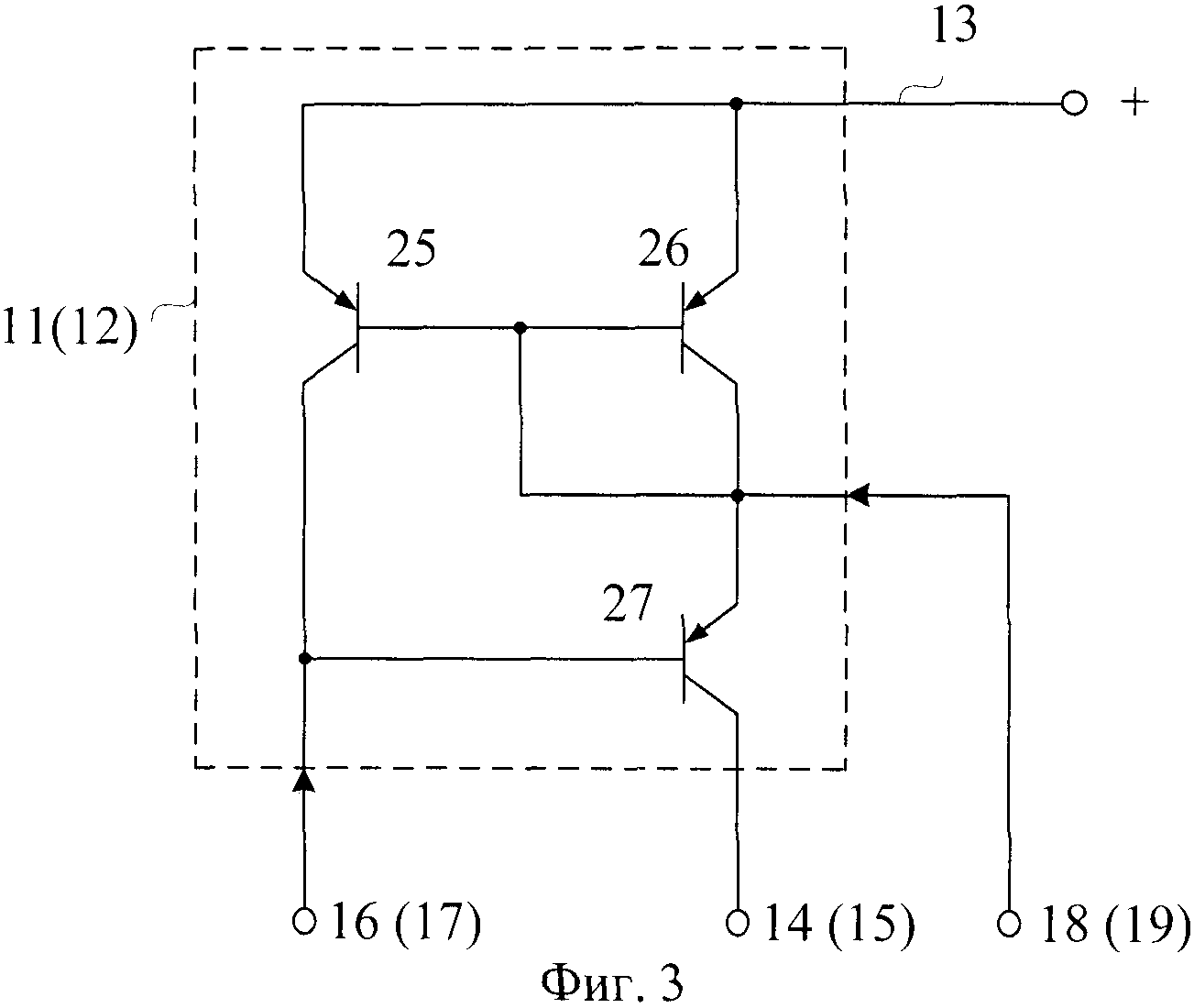

На фиг.3 показаны схемы первого 11 и второго 12 повторителей сигнала в виде токовых зеркал, которые используются в схеме фиг.2 в соответствии с п.3 и 4 формулы изобретения

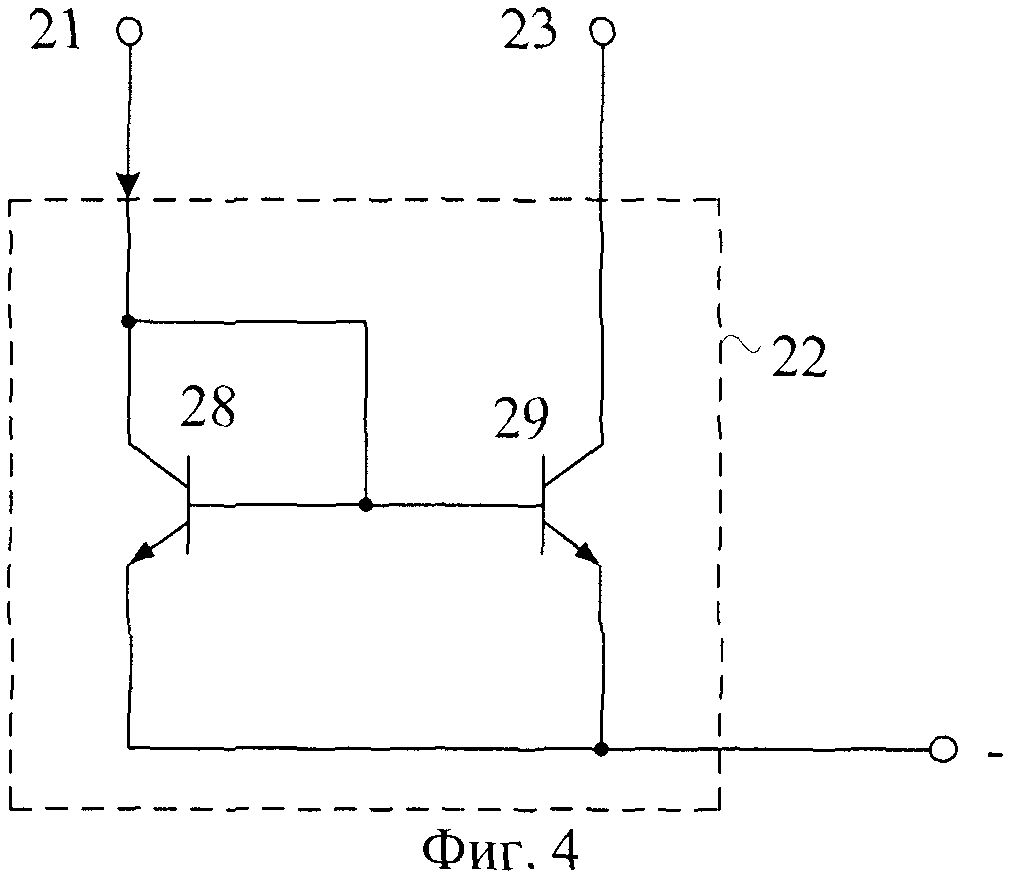

На фиг.4 приведена схема вспомогательного токового зеркала 22, которое используется в схеме фиг.2 по п.2 формулы изобретения.

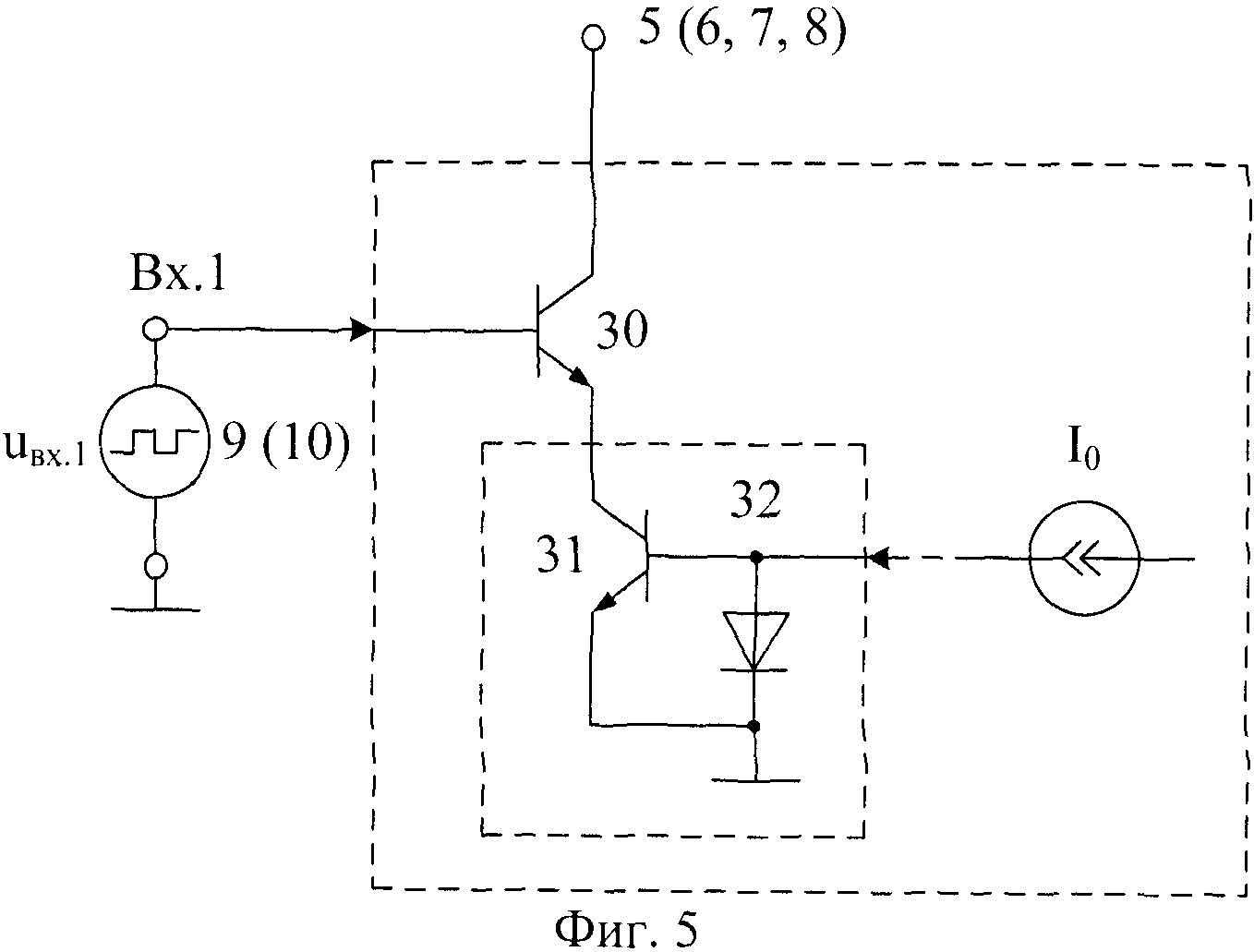

На фиг.5 приведена одна из возможных схем первого 1 (второго 2, третьего 3, четвертого 4) входных коммутаторов кванта тока I0.

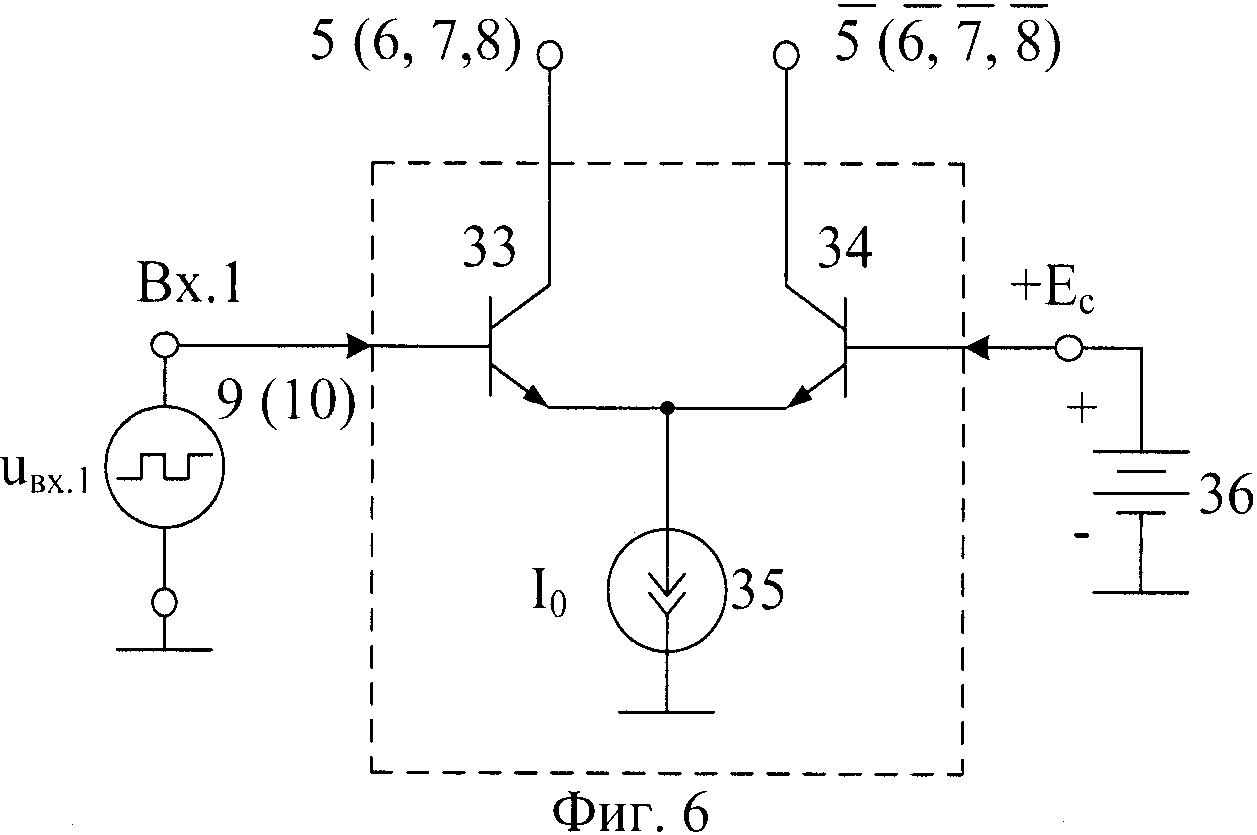

На фиг.6 приведена схема первого 1 (второго 2, третьего 3, четвертого 4) входных коммутаторов кванта тока I0 на основе дифференциальных усилителей.

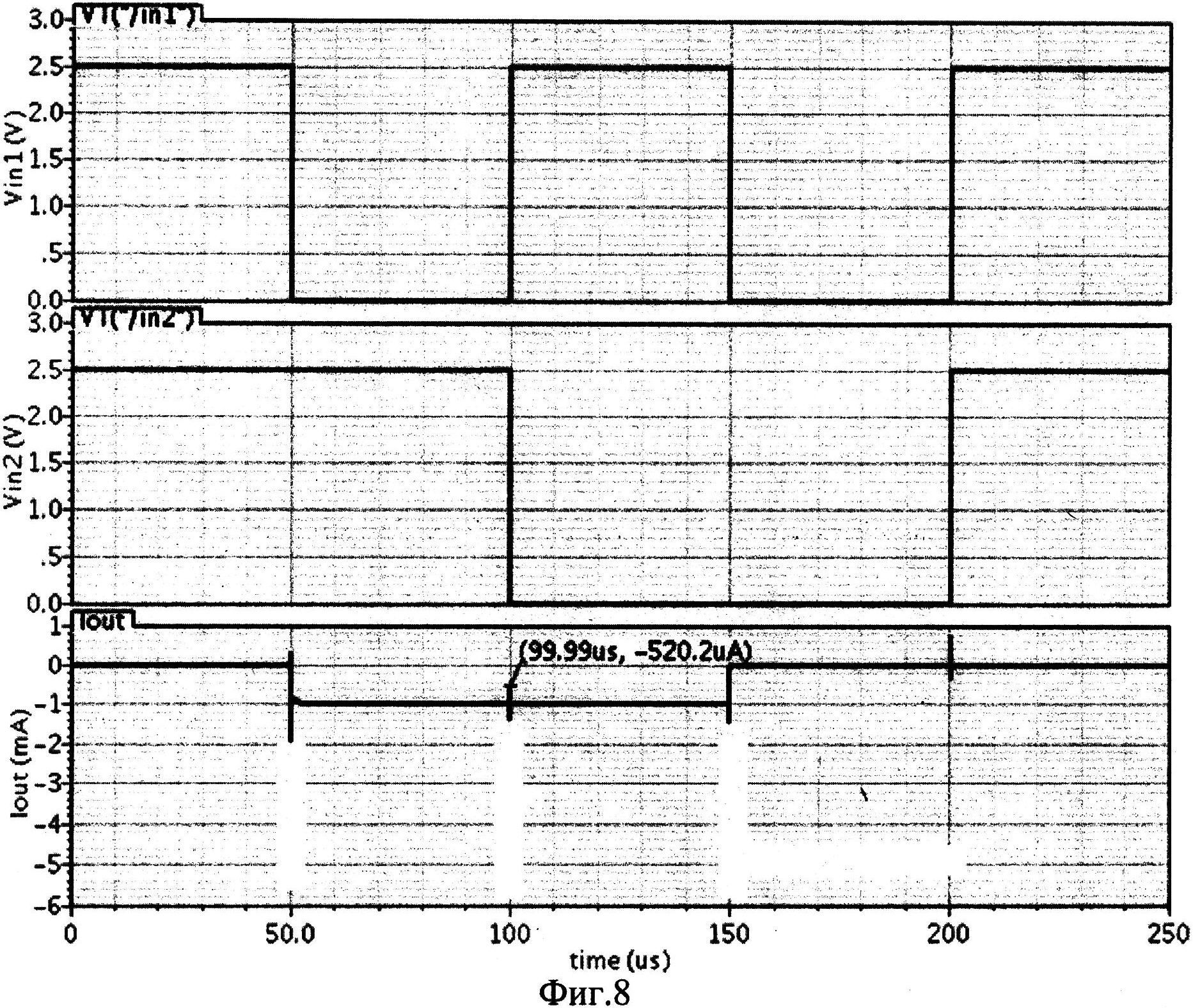

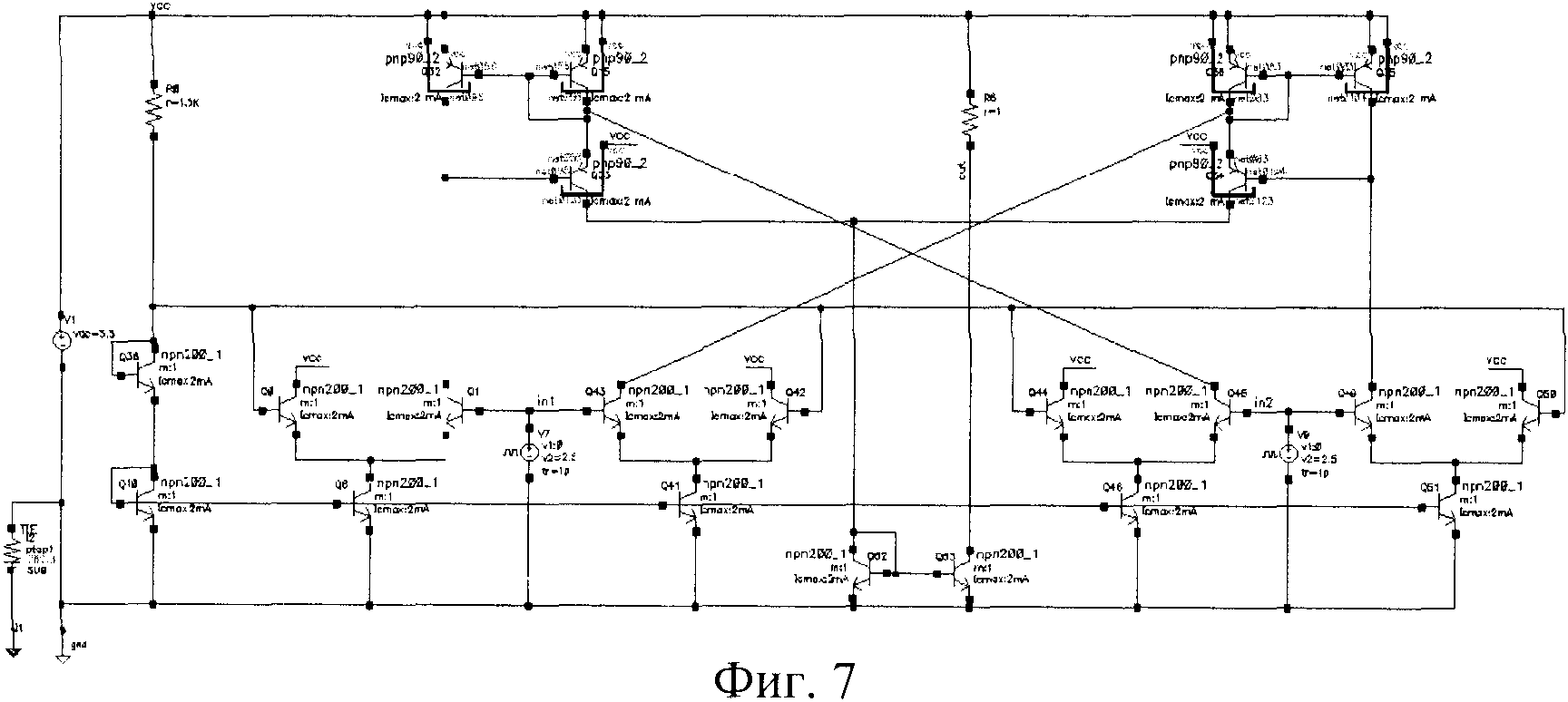

На фиг.7 показана схема неинвертирующего элемента «Исключающее ИЛИ» в среде компьютерного моделирования Cadence на моделях SiGe транзисторов.

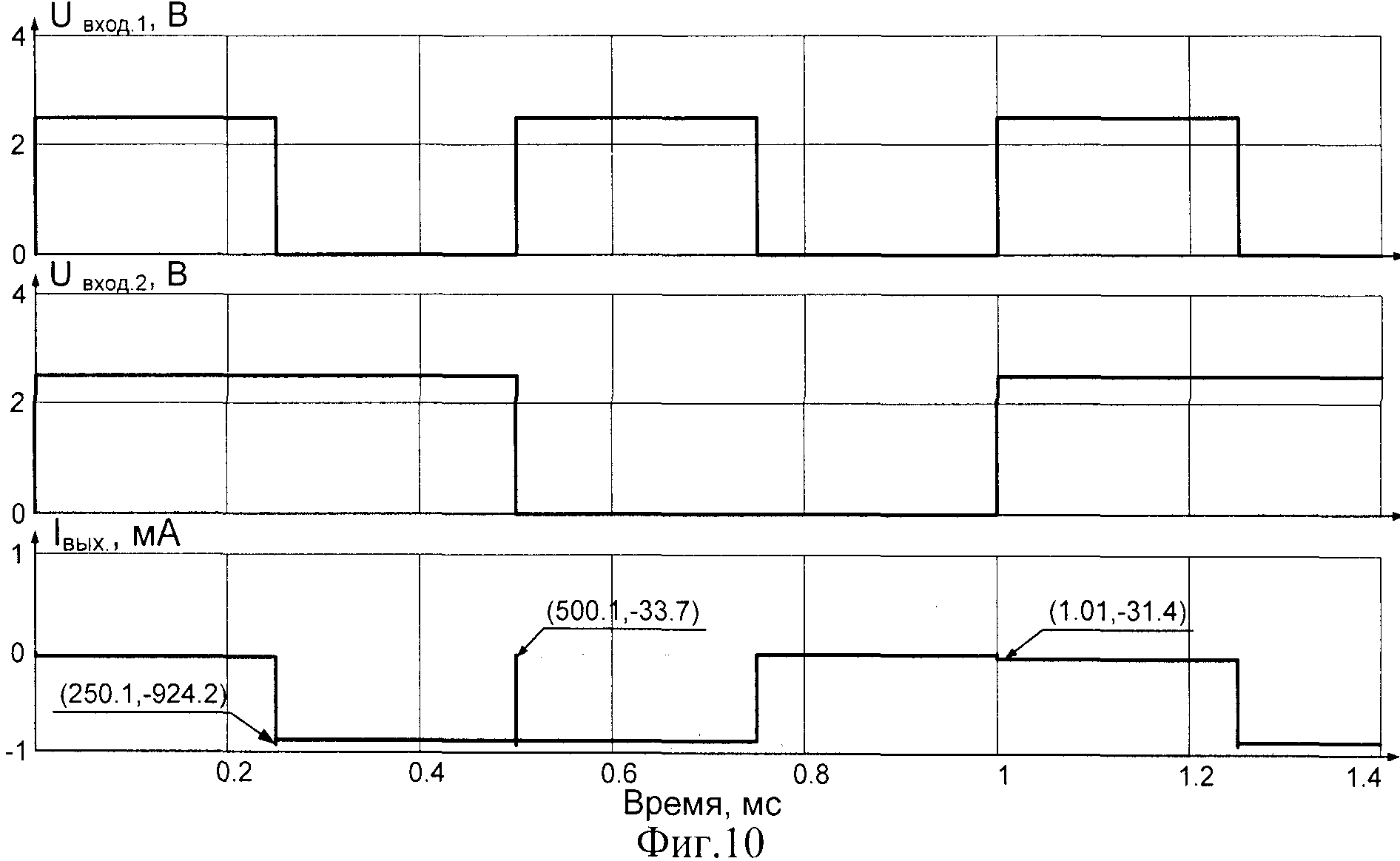

На фиг.8 представлена осциллограмма входных напряжений и выходного тока устройства (частота источника напряжения v1=10 кГц, частота источника напряжения v2=5кГц).

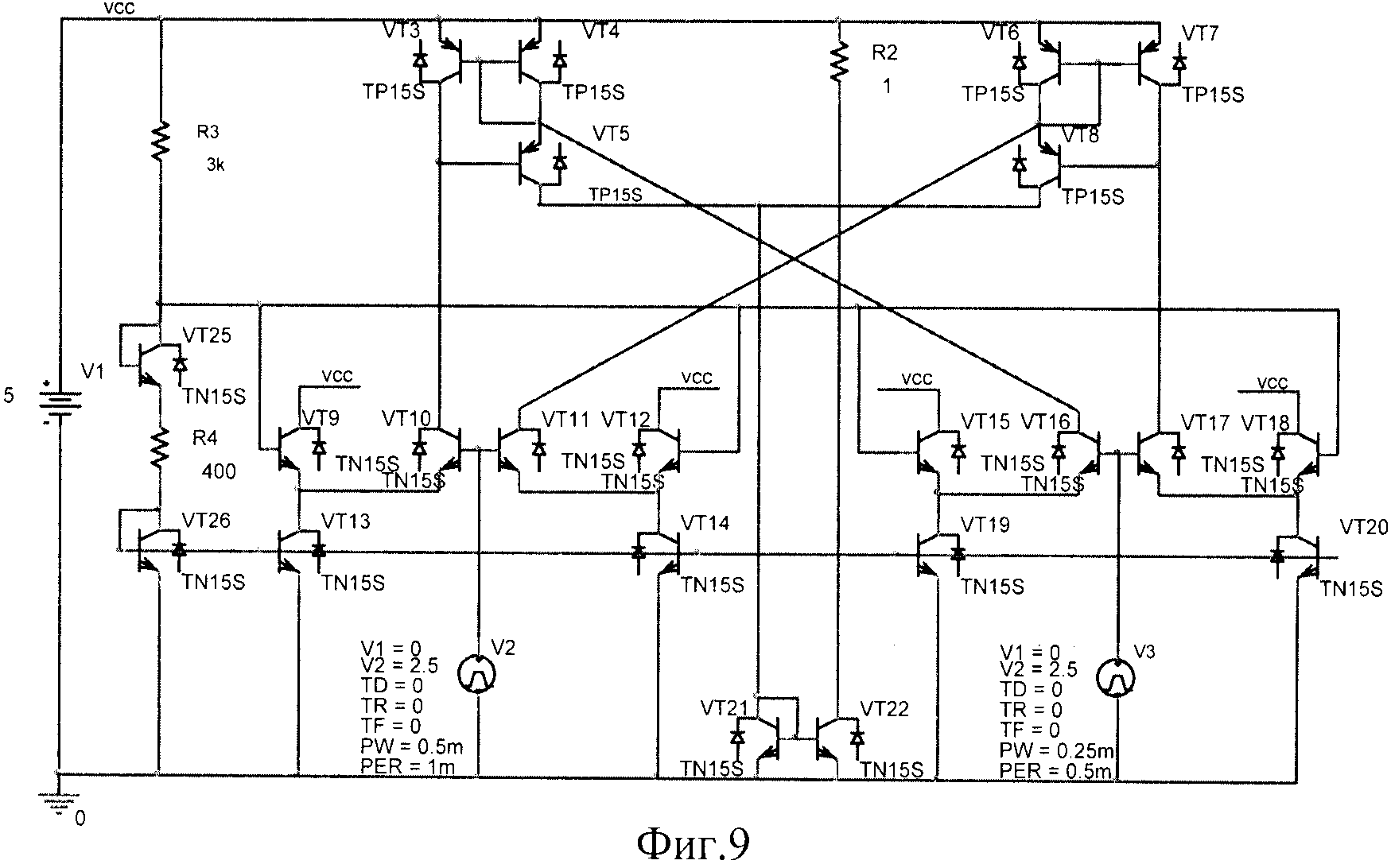

На фиг.9 показана схема «Исключающее ИЛИ» в среде PSpise на моделях интегральных транзисторов ФГУП НПП «Пульсар».

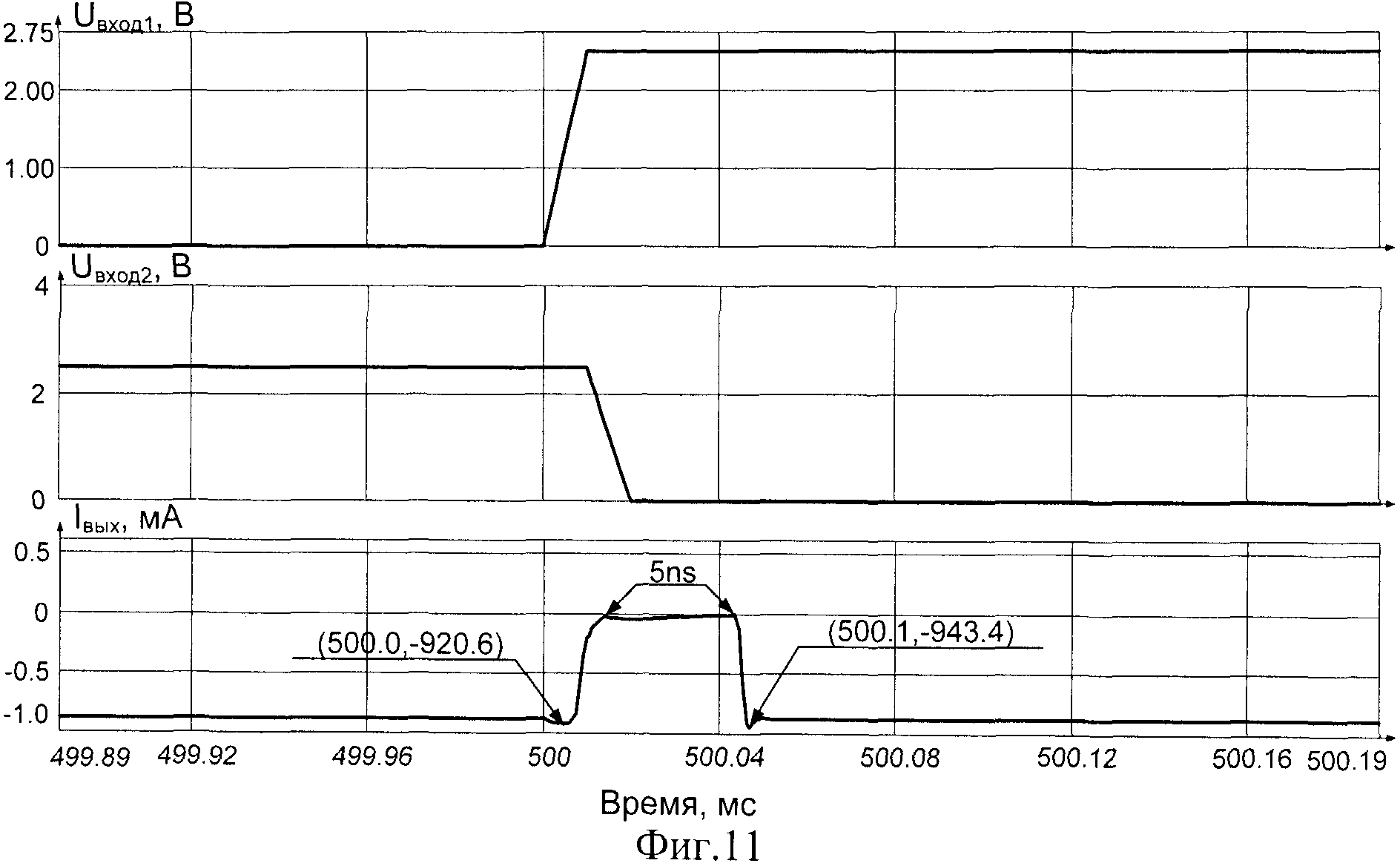

На фиг.10 приведена временная характеристика устройства фиг.9, а на фиг.11 - его временная характеристика в зоне фронтов входных импульсов напряжения в увеличенном масштабе.

Логический элемент исключающее «ИЛИ» с многозначным внутренним представлением сигналов фиг.2 содержит первый 1, второй 2, третий 3 и четвертый 4 коммутаторы квантов тока I0 с первым 5, вторым 6, третьим 7 и четвертым 8 соответствующими токовыми выходами, первый 9 и второй 10 источники входных логических сигналов, управляющих состоянием соответствующих коммутаторов квантов тока I0 (1, 2, 3, 4), первый 11 и второй 12 повторители выходных сигналов, согласованные с шиной источника питания 13, выходы которых 14 и 15 соединены друг с другом. В качестве первого 11 и второго 12 повторителей сигнала используются токовые зеркала, каждое из которых имеет инвертирующий (16, 17) и неинвертирующий (18, 19) токовые входы, инвертирующий токовый вход 16 первого 11 токового зеркала соединен с токовым выходом 5 первого 1 коммутатора кванта тока I0, неинвертирующий вход 18 первого 11 токового зеркала соединен с токовым выходом 7 третьего 3 коммутатора кванта тока I0, инвертирующий вход 17 второго 12 токового зеркала соединен с токовым выходом 8 четвертого 4 коммутатора кванта тока I0, неинвертирующий вход 19 второго 12 токового зеркала соединен с токовым выходом 6 второго 2 коммутатора кванта тока I0, объединенные токовые выходы 14, 15 первого 11 и второго 12 токовых зеркал соединены с токовым выходом 20 устройства, причем первый 9 источник входного логического сигнала связан с управляющими входами первого 1 и второго 2 входных коммутаторов кванта тока I0, а второй 10 источник входного логического сигнала связан с управляющими входами третьего 3 и четвертого 4 входных коммутаторов кванта тока I0, а первый 1 и второй 2, а также третий 3 и четвертый 4 входные коммутаторы квантов тока I0 попарно синфазны.

Кроме этого, на фиг.2, в соответствии п.2 формулы изобретения, токовый выход устройства 20 соединен со входом 21 вспомогательного токового зеркала 22, токовый выход которого 23 является дополнительным токовым выходом устройства.

На фиг.3, в соответствии п.3 формулы изобретения, первое 11 токовое зеркало содержит первый 25 и второй 26 входные транзисторы, эмиттеры которых соединены с шиной источника питания 13, базы объединены и подключены к эмиттеру выходного транзистора 27 и коллектору второго 26 входного транзистора, коллектор первого 25 входного транзистора соединен с базой выходного транзистора 27 и связан с инвертирующим входом 16 первого 11 токового зеркала, база второго 26 входного транзистора подключена к неинвертирующему входу 18 первого 11 токового зеркала, а коллектор выходного транзистора 27 связан с выходом 14 первого 11 токового зеркала.

На фиг.3, в соответствии п.4 формулы изобретения, второе 12 токовое зеркало содержит первый 25 и второй 26 входные транзисторы, эмиттеры которых соединены с шиной источника питания 13, базы объединены и подключены к эмиттеру выходного транзистора 27 и коллектору второго 26 входного транзистора, коллектор первого 25 входного транзистора соединен с базой выходного транзистора 27 и связан с инвертирующим входом 17 второго 12 токового зеркала, база второго 26 входного транзистора подключена к неинвертирующему входу 19 второго 12 токового зеркала, а коллектор выходного транзистора 27 связан с выходом 15 второго 12 токового зеркала.

На фиг.9 каждый из входных коммутаторов 1, 2, 3, 4 кванта тока I0, управляемых источниками входных логических напряжений 9, 10, выполнен в виде дифференциальных каскадов на транзисторах, эмиттеры которых связаны с источниками квантов тока I0.

На фиг.7 показана схема ЛЭ фиг.2 для случая, когда в качестве входных коммутаторов 1, 2, 3, 4 квантов тока I0 используются дифференциальные каскады фиг.6.

Рассмотрим работу предлагаемой схемы ЛЭ фиг.2.

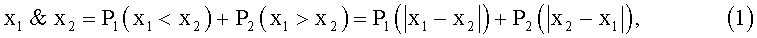

Синтез логической функции «Исключающее ИЛИ» («логическая неравнозначность», «сумма по модулю 2») производится на основе представления ее в линейной алгебре. Это представление в предикатной форме имеет следующий вид:

где Pi(х1, х2) - предикат [18, 19];

x1, x2 - входные логические сигналы.

Реализация предикатов выражения (1) производится с помощью токовых зеркал 11 и 12. Входной сигнал x1 в форме кванта тока I0 с выходов 5 и 6 коммутаторов тока 1 и 2 поступает на входы 16 и 19, а входной сигнала x2 с выходов 7 и 8 коммутаторов 3 и 4 в форме кванта тока I0 поступает на входы 17 и 18. В токовых зеркалах производится вычитание входных токов на инвертирующих входах 16, 19 из входных токов на неинвертирующих входах 18, 19 соответственно. Результат вычитания в виде квантов тока снимается с выходов 14 и 15 токовых зеркал 11 и 12 соответственно. При этом квант тока на выходе 14 имеет место, только если ток I0 на входе 16 есть, а на входе 18 отсутствует, что соответствует логическим значениям x1=1, x2=0. При других сочетаниях значений квантов тока на входах 16 и 18 ток на выходе 14 отсутствует. Аналогично на выходе 15 токового зеркала 12 квант тока имеет место только в том случае, если ток I0 на входе 17 имеется, а на входе 19 отсутствует, что соответствует логическим значениям x1=0, x2=1. При других сочетаниях значений токов на входах 17 и 19 ток на выходе 15 отсутствует. Кванты токов I0 с выходов 14 и 15 поступают на вход токового зеркала 22, с выхода которого снимается дополнительный выходной токовый сигнал.

Как видно из приведенного описания, реализация логической функции «Исключающее ИЛИ» здесь производится формированием алгебраической суммы квантов тока I0 и выделением определенных значений этой суммы токов. Все элементы приведенной схемы работают в активном режиме, предполагающем отсутствие насыщения в процессе переключений, что повышает общее быстродействие схемы. Кроме того, использование многозначного внутреннего представления сигналов повышает информативность линий связи, что уменьшает их количество. Использование стабильных значений квантов тока I0, а также определение выходного сигнала разностью этих токов обеспечивает малую зависимость функционирования схемы от внешних дестабилизирующих факторов (девиация питающего напряжения, радиационное и температурное воздействия, синфазная помеха и др.).

Отличием логического элемента «Исключающее ИЛИ» с использованием схемы фиг.6 является реализация входных коммутаторов квантов тока I0 в виде дифференциальных каскадов на элементах 33, 34. 35. Вариант такой реализации приведен на фиг.7. Здесь дифференциальный каскад производит коммутацию кванта тока I0. При этом источник тока 35 при любом состоянии входного логического сигнала не выходит из активного режима, что повышает быстродействие схемы.

Показанные на фиг.8, 10 и 11 результаты моделирования подтверждают указанные свойства заявляемых схем. Следует отметить, что кратковременные импульсы на выходе ЛЭ, возникающие в момент переключения входных сигналов (фиг.10 и 11), характерные и для других известных логических элементов, определяются различными временами переключения входных коммутаторов квантов тока 1, 2, 3, 4 и могут быть устранены в реальных схемах средствами технологии.

Таким образом, рассмотренные схемотехнические решения логического элемента «Исключающее ИЛИ» характеризуются многозначным состоянием внутренних сигналов и двоичным представлением сигнала на его токовом выходе и могут быть положены в основу вычислительных и управляющих устройств, использующих многозначную линейную алгебру, частным случаем которой является булева алгебра.

Литература

1. Патентная заявка US 2007/0018694.

2. Патент US 6.414.519.

3. Патент US 6.566.912.

4. Патент US 6.700.413.

5. Патентная заявка US 2004/0263210.

6. Патент US 6.680.625.

7. Патент SU 1621164.

8. Патент JP 10098374.

9. Патент US 6.573.758.

10. Патент US 5.155.387.

11. Патент US 4.713.790.

12. Патент US 4.713.790.

13. Патент US 5.608.741.

14. Патент US 4.158.210.

15. Патент US 4.185.210, fig.2.

16. Патент US 3.040.192, fig.1.

17. Малюгин В.Д. Реализация булевых функций арифметическими полиномами // Автоматика и телемеханика, 1982. №4. С.84-93.

18. Чернов И.И. Основы теории логического синтеза цифровых структур над полем вещественных чисел // Монография. - Таганрог: ТРТУ, 2001. - 147 с.

19. Чернов Н.И. Линейный синтез цифровых структур АСОИУ // Учебное пособие. - Таганрог: ТРТУ, 2004 г. - 118 с.