Результат интеллектуальной деятельности: Способ косвенного измерения отказоустойчивости облучаемых испытательных цифровых микросхем, построенных различными способами постоянного поэлементного резервирования, и функциональная структура испытательной микросхемы, предназначенной для реализации этого способа

Вид РИД

Изобретение

Область техники, к которой относится изобретение

Изобретение относится к области цифровой вычислительной техники и электроники, а именно к выбору способов построения цифровых микросхем, отказоустойчивых к облучению, и более точно относится к способу косвенного измерения отказоустойчивости испытательных резервированных цифровых микросхем при их облучении с целью получения экспериментальных оценок отказоустойчивости, которую могут обеспечить различные способы постоянного поэлементного резервирования цифровых микросхем. Предлагаемый способ косвенного измерения должен позволить получить экспериментальные оценки отказоустойчивости, которые могут обеспечить различные способы поэлементного резервирования микросхем при их облучении, сравнить эти экспериментальные оценки с теоретическими оценками и выбрать подходящий способ постоянного резервирования цифровых микросхем. Изобретение может найти применение для выбора подходящего способа постоянного поэлементного резервирования микросхем при создании цифровых микросхем, отказоустойчивых к облучению.

Уровень техники

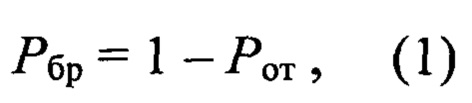

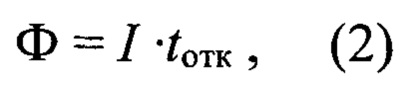

Под отказоустойчивостью микросхемы понимается ее способность выполнять заданные функции и выдавать верные результаты при отказах - постоянных и временных (т.е. при сбоях). Понятие отказоустойчивости нередко путают с надежностью и радиационной стойкостью. В книге Александрова П.А., Жука В.И. и Литвинова В.Л. «Способы построения отказоустойчивых цифровых микросхем и оценки вероятностей их отказа, вызванного облучением» (М.: Издательский дом «ПоРог», 2019) дан терминологический обзор понятия «отказоустойчивость» и отмечается, что для оценки отказоустойчивости микросхемы в отечественной литературе и за рубежом используют вероятность отказа микросхемы. Отказоустойчивость микросхемы тем выше, чем ниже вероятность ее отказа. Отказоустойчивостью микросхемы можно считать вероятность ее безотказной работы:

где Рот - вероятность отказа микросхемы.

В работах Александрова П.А., Жука В.И., Литвинова В.Л. и др., обзор которых дан в указанной выше книге этих авторов, предложены и теоретически исследованы различные способы постоянного поэлементного резервирования микросхем (структурное дублирование, квадрирование, девятикратное резервирование одиночных транзисторов).

В этих работах приведены математические формулы отказоустойчивости облучаемых микросхем, являющиеся теоретическими оценками вероятности отказа микросхемы при ее резервировании указанными способами и без ее резервирования. Эти теоретические оценки отказоустойчивости позволяют предварительно выбрать подходящий способ резервирования без разработки и создания конкретных сложных микросхем.

Однако, учитывая большую стоимость разработки и изготовления сложных цифровых микросхем, для большей обоснованности выбора способа поэлементного резервирования для построения цифровых микросхем, отказоустойчивых к облучению, необходимо получить экспериментальные оценки отказоустойчивости, которые могут быть обеспечены различными способами постоянного поэлементного резервирования цифровых микросхем.

Для получения этих экспериментальных оценок необходимо провести испытания различных способов постоянного поэлементного резервирования облучаемых цифровых микросхем, а не испытания конкретных микросхем, созданных для разных применений и имеющих структуру, не позволяющую обнаруживать подавляющее число отказов. Например, если конкретная цифровая микросхема представляет собой арифметическое устройство, то о его отказе можно будет судить по неверному результату на его выходе, но при этом нельзя обнаружить отказы в его элементах и измерить время до первого отказа, который может произойти задолго до получения результата арифметической операции. А без этого невозможно будет вычислить отказоустойчивость цифровой микросхемы.

Предлагаемое изобретение посвящено проблеме создания технических средств для проведения этих испытаний указанных способов резервирования микросхем. Эти средства представляют собой способ косвенного измерения отказоустойчивости испытательных цифровых микросхем, построенных различными способами постоянного поэлементного резервирования, и функциональную структуру испытательной микросхемы, которая может быть реализована любым испытываемым способом постоянного поэлементного резервирования. Здесь под испытательной микросхемой понимается микросхема, единственной функцией которой является обеспечение испытания способа косвенного измерения отказоустойчивости микросхем при заданном способе их постоянного поэлементного резервирования. Для обеспечения указанного испытания функциональная структура испытательной микросхемы должна позволять обнаруживать все отказы в ней в процессе ее работы.

Известны способы постоянного резервирования цифровых микросхем, отказоустойчивых к облучению и ориентированных на построение логических устройств, а не устройств памяти (см., книгу Александрова П.А., Жука В.И. и Литвинова В.Л. «Способы построения отказоустойчивых цифровых микросхем и оценки вероятностей их отказа, вызванного облучением», М.: Издательский Дом «ПоРог», 2019, -116 с; Патент РФ №2475820 от 10.08.2010, МПК G06F 11/18, Александров П.А., Жук В.И., Литвинов В.Л. «Способ постоянного поэлементного дублирования в дискретных электронных системах (Варианты)» и следующие статьи этих авторов и др.:

- «Отказоустойчивость покомпонентно дублированной микросхемы при облучении» // Наш- и микросистемная техника, 2015, №3, С. 10-17,

- «Сравнительные оценки отказоустойчивости мажоритарно резервированных и покомпонентно дублированных микросхем при облучении» // Нано- и микросистемная техника, 2016, №3, С. 176-185,

- «О построении дублированных логических элементов для повышения отказоустойчивости микросхем при облучении» // Нано- и микросистемная техника, 2016, №4, С. 239 -250,

- «О квадрировании транзисторов в нано- и микроцифровых интегральных схемах при облучении» // Нано- и микросистемная техника, 2018, №2, С. 111-118,

- «О применении транзисторной квадратной матрицы для резервирования цифровых интегральных схем при облучении» // Нано- и микросистемная техника, 2018, №9, С. 561-568).

Однако способы экспериментальной оценки теоретически исследованных способов построения на основе постоянного поэлементного резервирования цифровых микросхем, отказоустойчивых к облучению, и, более точно, способы измерения отказоустойчивости этих микросхем при их облучении, обеспечиваемой различными способами резервирования микросхем, не известны.

Хотя способы измерения отказоустойчивости микросхем к облучению не предлагались, однако очевидный способ измерения отказоустойчивости облучаемых микросхем, включает в себя способ вычисления их отказоустойчивости по измеренному начальному отрезку времени облучения до ее отказа, и представлен в указанных выше теоретических работах.

Поэтому прототипом предлагаемого способа является обобщенный способ измерения отказоустойчивости облучаемых микросхем, представленный в книге Александрова П.А., Жука В.И. и Литвинова В.Л. «Способы построения отказоустойчивых цифровых микросхем и оценки вероятностей их отказа, вызванного облучением» (М.: Издательский дом «ПоРог», 2019). Здесь под обобщенным способом измерения отказоустойчивости облучаемых микросхем понимается способ, общий для микросхем, построенных различными способами постоянного поэлементного резервирования.

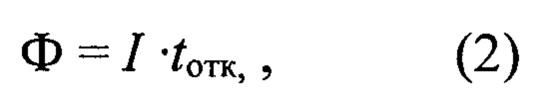

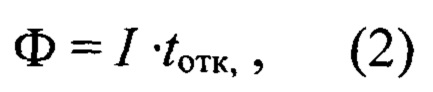

Способ-прототип состоит в том, что во время облучения микросхемы измеряют начальный отрезок времени облучения микросхемы до ее отказа, позволяющий оценить вероятность отказа микросхемы, затем вычисляют флюенс, при котором произошел отказ микросхемы, по формуле:

где Ф - флюенс, или иначе говоря, число частиц, попавших в 1 см2 микросхемы за время облучения до ее отказа,

I - интенсивность облучения,

tотк - начальный отрезок времени облучения микросхемы до ее отказа, позволяющий оценить вероятность отказа микросхемы,

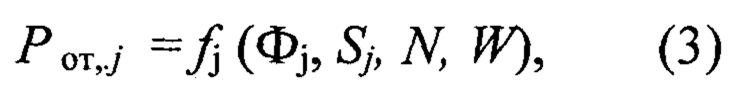

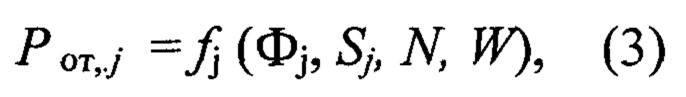

а затем по вычисленному флюенсу и заданными характеристикам микросхемы, указанным ниже, вычисляют отказоустойчивость микросхемы по соответствующей способу ее построения формуле вероятности отказа микросхемы:

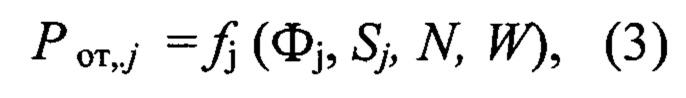

где j - идентификатор способа построения микросхемы,

Рот,j - вероятность отказа микросхемы, характеризующая ее отказоустойчивость,

ƒj, Фj и Sj - формула, флюенс и площадь микросхемы, соответствующие j-му способу построения микросхемы,

N - число условных одинаковых компонентов, в частности, логических элементов, в микросхеме,

W - вероятность повреждения единицы площади микросхемы при попадании в нее частицы.

В способе-прототипе в качестве соответствующей способу построения цифровой микросхемы формуле (3) могут быть использованы конкретные известные или пока неизвестные математические формулы вероятности отказа микросхем. В качестве известных формул вероятности отказа могут быть использованы конкретные формулы для нерезервированной, структурно дублированной, квадрированной и 9-кратно резервированной микросхемы, эквивалентные представленным в указанной выше книге Александрова П.А., Жука В.И. и Литвинова В.Л. «Способы построения отказоустойчивых цифровых микросхем и оценки вероятностей их отказа, вызванного облучением» - М.: Издательский Дом «ПоРог», 2019.

Так, в качестве формулы (3) могут быть использованы следующие формулы вероятности отказа микросхем, взятые из этой книги:

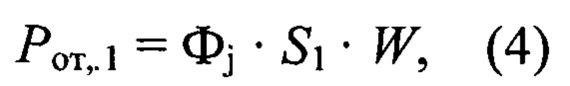

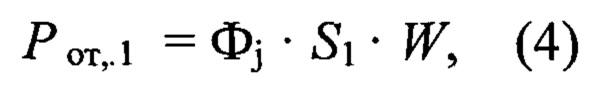

1) для нерезервированной микросхемы:

где все величины определены выше;

формула (4) соответствует формуле (4.2-11) на С.29 указанной книги;

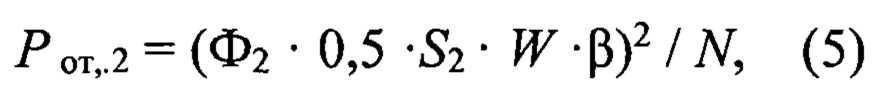

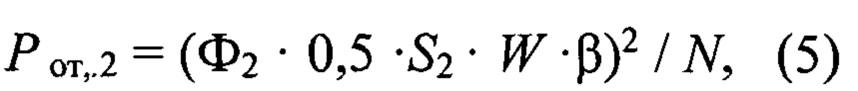

2) для структурно дублированной микросхемы:

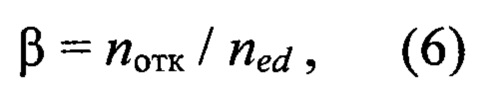

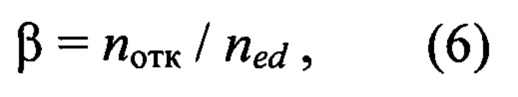

где β - относительная вероятность отказа дублированного элемента при попадании частицы в его нерезервированный компонент,

где nотк - среднее число нерезевированных компонентов дублирующего элемента,

ned - среднее число компонентов в дублирующем элемента, остальные величины определены выше;

формула (5) соответствует в указанной книге формуле (5.3-11) на С.44, в которую надо подставить формулу (5.3-1) на С.41; формула (6) соответствует в указанной книге формуле (5.3-2) на С.42;

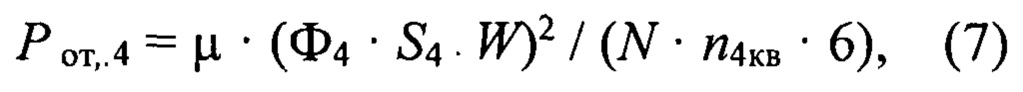

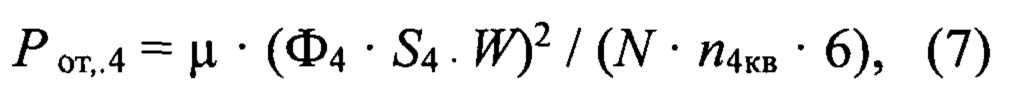

3) для квадрированной микросхемы:

где: n4кв - среднее число квадрированных транзисторов в одном квадрированном логическом элементе;

μ - относительная вероятность попадания частицы в отказывающую пару одиночных транзисторов;

остальные величины определены выше;

формула (7) соответствует в указанной книге формуле (8.4-10) на С.81, в которой

Gmax=6, sот⋅4⋅Nкв=S4;

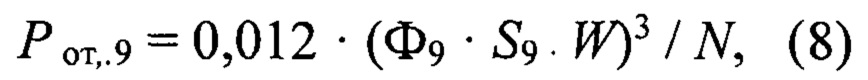

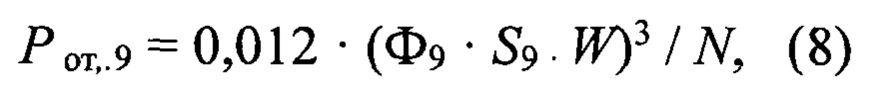

4) для 9-кратно резервированной микросхемы:

где все величины определены выше;

формула (8) соответствует в указанной книге формуле (9-34) на С.97, в которой согласно (9-32) sот ⋅ Nот-9 согласно (9-39) N9=N.

Недостаток способа-прототипа состоит в том, что начальный отрезок времени облучения микросхемы до ее отказа, позволяющий оценить вероятность отказа микросхемы, или, другими словами, начальный отрезок времени облучения микросхемы до ее отказа, полученный с вероятностью отказа микросхемы, можно измерить только при облучении большого числа идентичных микросхем, которые после их отказов не годятся к использованию. Но как уменьшить число испытуемых идентичных микросхем до одной, не известно.

Другой недостаток способа-прототипа заключается в том, что даже при уменьшении числа испытуемых идентичных микросхем до одной, не известно, как измерять начальный отрезок времени облучения микросхемы до ее отказа и как распознавать ее отказ.

Для реализации способа-прототипа требуются испытательные микросхемы, предназначенные для испытаний способов постоянного поэлементного резервирования микросхем и облегчающие обнаружение отказов микросхемы и измерение отрезков времени, в том числе - между отказами. Однако испытательные микросхемы такого назначения и их функциональные структуры не известны и не имеют аналогов.

Раскрытие сущности изобретения

Проблемой, решаемой предлагаемым изобретением, является разработка способа косвенного измерения отказоустойчивости облучаемых испытательных цифровых микросхем, построенных различными способами постоянного поэлементного резервирования, и функциональной структуры испытательных микросхем, инвариантной к используемым способам их резервирования, позволяющей обнаруживать в них отказы и предназначенной для реализации предлагаемого способа косвенного измерения.

Предлагаемые способ и функциональная структура направлены на достижение технического результата, состоящего в создании средств проведения испытаний способов построения цифровых микросхем на основе постоянного поэлементного резервирования с целью получения экспериментальных оценок их отказоустойчивости к облучению.

Достижение этого технического результата оказалось возможным благодаря тому, что оценки отказоустойчивости облучаемых микросхем «по площадям», использованные в прототипе, основаны на том факте, что облучение действует на «площадь» микросхемы независимо от ее функционального содержания. Это позволило создать для испытаний способов постоянного резервирования микросхем простую функциональную структуру испытательной микросхемы, специально предназначенную и приспособленную для измерения ее отказоустойчивости в процессе ее облучения и позволяющую просто обнаруживать отказы испытательной микросхемы в процессе ее облучения.

Для достижения этого технического результата предложен способ косвенного измерения отказоустойчивости облучаемых цифровых микросхем, построенных различными способами постоянного поэлементного резервирования, заключающийся в том, что это косвенное измерение отказоустойчивости проводят на микросхемах, построенных различными способами их постоянного резервирования или без резервирования, во время их облучения, и при этом измеряют начальный отрезок времени облучения микросхемы до ее отказа, позволяющий оценить вероятность отказа микросхемы, затем вычисляют флюенс, при котором произошел отказ микросхемы, по формуле:

где Ф - флюенс,

I -интенсивность облучения,

tотк - начальный отрезок времени облучения микросхемы до ее отказа, позволяющий оценить вероятность отказа микросхемы,

а затем по вычисленному флюенсу и заданным характеристикам микросхемы вычисляют отказоустойчивость микросхемы по соответствующей способу ее построения формуле вероятности отказа микросхемы:

где j - идентификатор способа построения микросхемы,

Рот,j - вероятность отказа микросхемы, характеризующая ее отказоустойчивость,

ƒj, Фj и Sj - формула, флюенс и площадь микросхемы, соответствующие j-му способу построения микросхемы,

N - число условных одинаковых компонентов, в частности, логических элементов, в микросхеме,

W - вероятность повреждения единицы площади микросхемы при попадании в нее частицы,

и при этом выполняют следующие действия:

измерение начального отрезка времени облучения микросхемы до ее отказа производят на облучаемой испытательной микросхеме, соединенной с необлучаемой вычислительной системой управления измерением, с помощью которой производят измерение времени облучения, вычисление флюенса, вычисление отказоустойчивости микросхемы, проверку результатов работы микросхемы, фиксацию ее отказов и формируют управляющие сигналы циклов ее работы и работы микросхемы, время облучения микросхемы измеряют по числу циклов ее работы, умноженному на длительность цикла работы указанной вычислительной системы, в каждом цикле из указанной вычислительной системы передают на вход микросхемы контрольные эталоны, а в эту систему передают коды результатов работы микросхемы и в этой системе в каждом цикле фиксируют отказ микросхемы при несовпадением ее кода результата с входным эталоном, а в качестве указанного начального отрезка времени работы микросхемы до ее отказа измеряют средний отрезок времени облучения микросхемы от момента облучения, принятого за начальный, до ее последнего отказа в заданном числе соседних циклов ее работы.

Это позволяет решить проблему создания способа косвенного измерения отказоустойчивости облучаемых микросхем при использовании одной испытуемой испытательной микросхемы для каждого испытуемого способа постоянного поэлементного резервирования микросхем и при этом обеспечить простые способы измерения отрезков времени облучения испытательной микросхемы и способ обнаружения ее отказов.

Достижению этого технического результата способствует то, что измеряют отрезок времени облучения микросхемы от момента начала измерения времени облучения микросхемы по сигналу устройства управления затвором облучения, подаваемого в необлучаемую вычислительную систему управления измерением, до цикла работы микросхемы, в котором будет обнаружен первый отказ микросхемы, характеризуемый фактом ошибки в коде, являющемся результатом работы микросхемы, при сравнении этого кода с эталоном, соответствующим моменту начала измерения времени облучения.

Это позволяет обнаружить первый отказ в микросхеме при ее облучении и в дальнейшем использовать момент этого первого отказа при измерении среднего отрезка времени облучения микросхемы до ее отказа.

Достижению указанного технического результата способствует также то, что за момент облучения, принятый за начальный момент измерения среднего отрезка времени облучения микросхемы, принимают начальный момент начала измерения времени облучения по сигналу устройства управления затвором облучения, подаваемому в необлучаемую вычислительную систему управления измерением.

Это позволяет по желанию испытателя использовать отрезок времени до первого отказа микросхемы при измерении среднего отрезка времени облучения микросхемы до ее отказа.

Достижению технического результата способствует и то, что за момент облучения, принятый за начальный момент измерения среднего отрезка времени облучения микросхемы, принимают момент первого отказа микросхемы после начала измерения в необлучаемой вычислительной системе управления измерением.

Это позволяет по желанию испытателя в дальнейшем использовать момент этого первого отказа при измерении среднего отрезка времени облучения микросхемы до ее отказа.

Технический результат достигается также благодаря тому, что измеряют отрезок времени облучения микросхемы от момента предыдущего ее отказа до момента следующего ее отказа по числу циклов работы микросхемы, прошедших от момента предыдущего отказа до цикла ее работы, в котором будет обнаружена ошибка в коде, являющемся результатом работы микросхемы, при сравнении этого кода с эталоном, соответствующим коду результата при предыдущем отказе микросхемы.

Это позволяет решить задачу измерения длительности среднего отрезка времени облучения микросхемы до ее отказа.

Для достижения технического результата предложена функциональная структура испытательной микросхемы, реализуемая различными способами ее постоянного поэлементного резервирования и без ее резервирования; эта функциональная структура содержит входной и выходной n-разрядные двоичные регистры, узел управления приемом контрольных эталонов во входной регистр от необлучаемой вычислительной системы управления измерением и узел управления приемом кода результата в выходной регистр по сигналу указанной вычислительной системы управления измерением, причем между одноименными i-ми (i=1, 2, …, n) разрядами входного и выходного регистров установлена последовательная цепочка одинаковых одновходовых комбинационных логических элементов.

Это позволяет создать простую функциональную структуру, общую для испытательных микросхем, служащих для реализации предлагаемого способа косвенного измерения отказоустойчивости облучаемых испытательных микросхем, обеспечивающих обнаружение в них отказов и построенных различными способами постоянного поэлементного резервирования.

Краткое описание чертежей

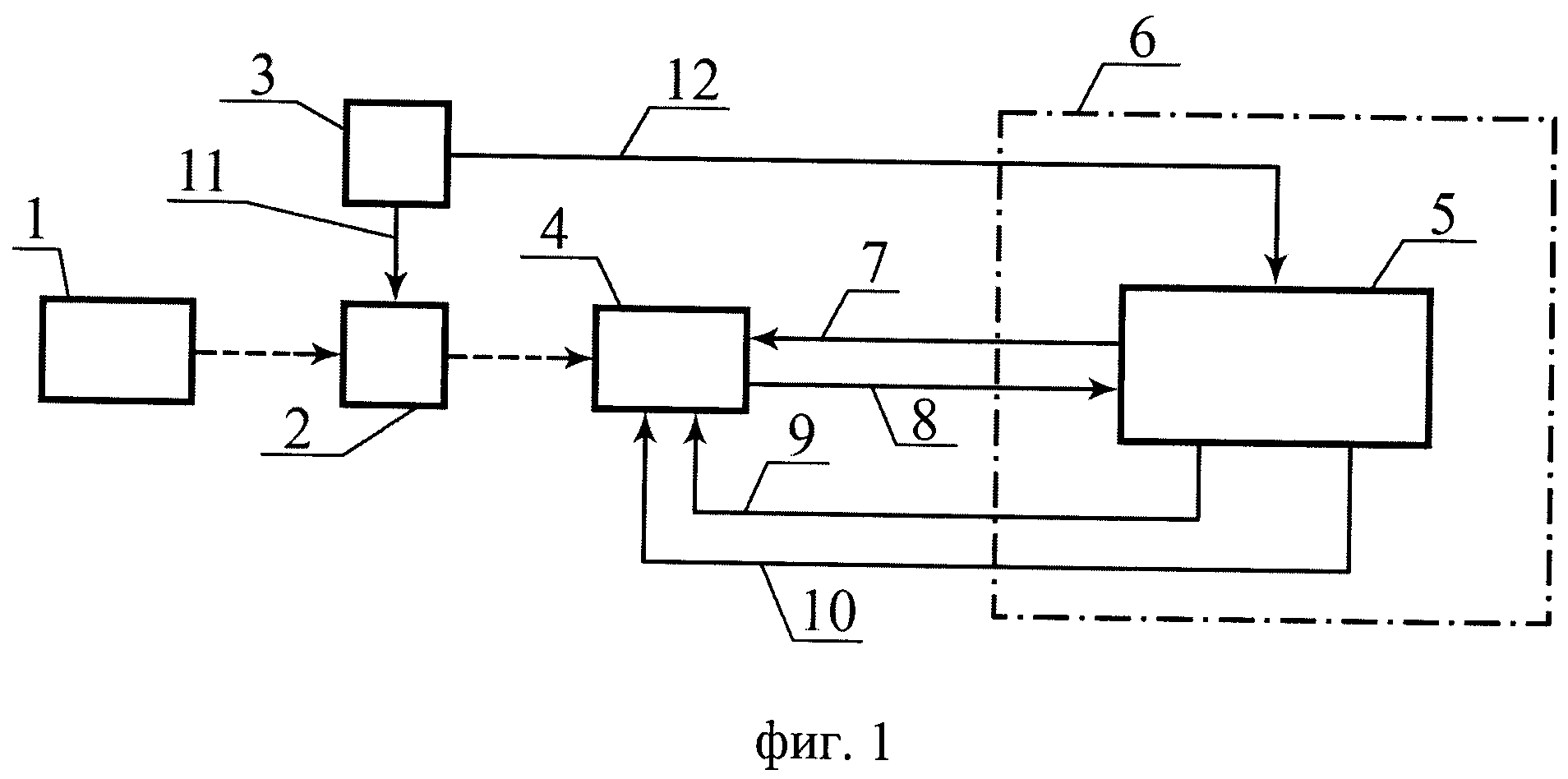

На фиг. 1 показана схема испытательной системы для косвенного измерения отказоустойчивости облучаемых испытательных цифровых микросхем, построенных различными способами постоянного резервирования.

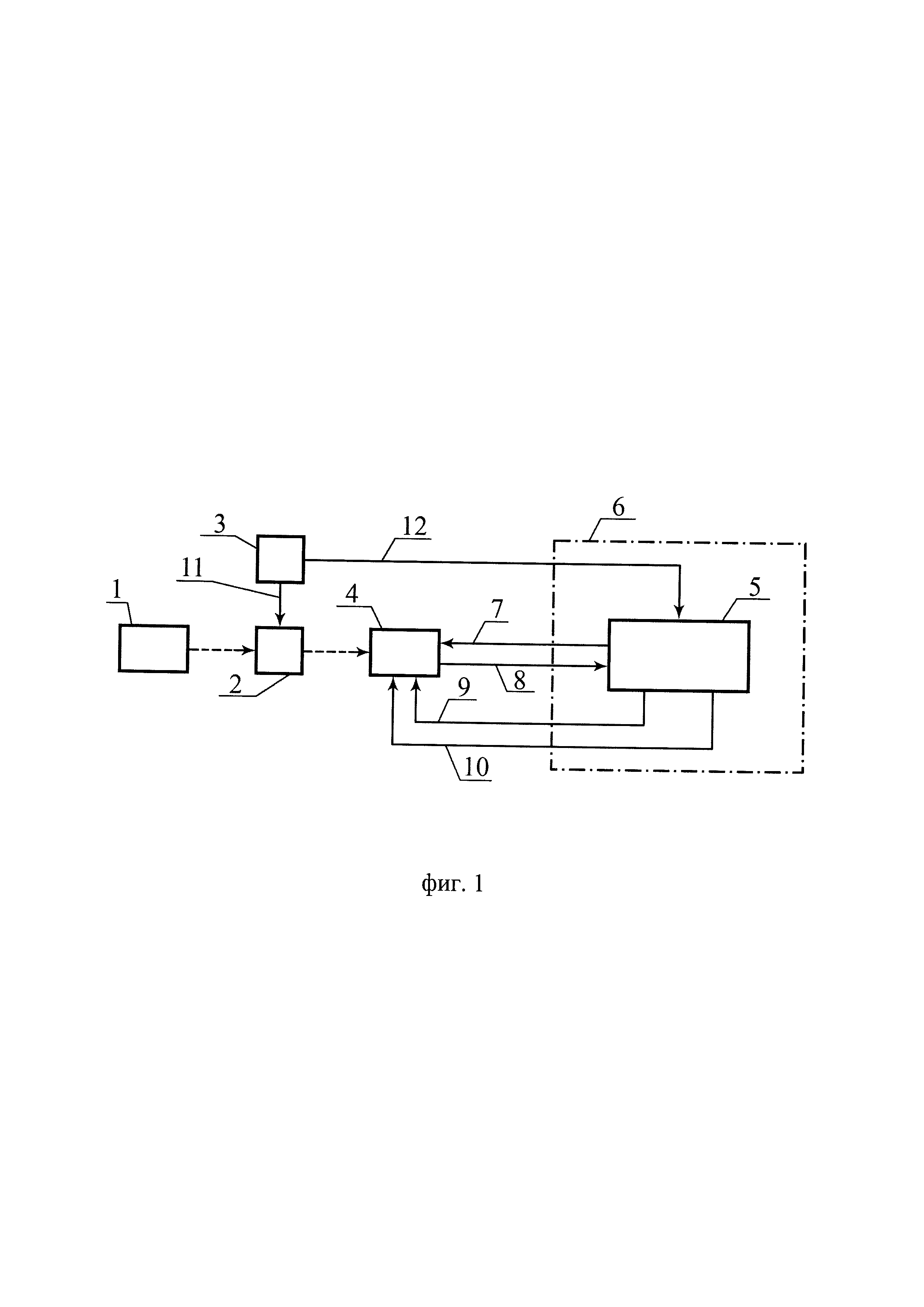

На фиг. 2 показана функциональная структура испытательной цифровой микросхемы для косвенного измерения ее отказоустойчивости при облучении, реализуемая различными способами ее постоянного поэлементного резервирования и без ее резервирования.

Осуществление изобретения

Состав испытательной системы

Испытательная система (фиг. 1) для косвенного измерения отказоустойчивости облучаемых испытательных цифровых микросхем, построенных различными способами постоянного резервирования, содержит источник 1 радиационного излучения, построенный, например, на основе атомного реактора, затвор 2 облучения, устройство 3 управления затвором 2 облучения, испытательная цифровая микросхема 4, установленная в качестве облучаемого образца, и удаленная необлучаемая вычислительная система 5 управления измерением, установленная в необлучаемом помещении 6. Соединение 7 служит для передачи n-разрядного двоичного кода контрольного эталона из вычислительной системы 5 в микросхему 4. Соединение 8 служит для передачи n-разрядного двоичного кода результата работы микросхемы 4 в вычислительную систему 5. Соединение 9 служит для подачи управляющего сигнала приема контрольных эталонов в микросхему 4, а соединение 10 служит для подачи управляющего сигнала приема кода результата работы микросхемы в ее выходной регистр (на фиг. 1 не показан). Соединение 11 служит для подачи устройством 3 сигналов управления («открыть», «закрыть») затвором 2 облучения, а соединение 12 служит для подачи управляющего сигнала начала измерений в вычислительную систему 5.

Функциональная структура испытательной цифровой микросхемы 5, реализуемая различными способами ее постоянного поэлементного резервирования и без ее резервирования (фиг. 2) содержит входной n-разрядный двоичный регистр 13, выходной n-разрядный двоичный регистр 14, узел 15 управления приемом «-разрядного двоичного кода контрольного эталона во входной регистр 13, узел 16 управления приемом кода результата работы микросхемы 4 в выходной регистр 14. Кроме того, в микросхеме 5 между одноименными i-ми (i=1, 2, …, n) двоичными разрядами входного регистра 13 и выходного регистра 14 установлена последовательная цепочка одинаковых одновходовых комбинационных логических элементов 17. Набор этих цепочек представляет n-разрядную двоичную комбинационную логическую схему 18, т.е. логическую схему, не содержащую элементов памяти.

Работа испытательной системы (фиг. 1) для косвенного измерения отказоустойчивости облучаемых испытательных микросхем рассматривается ниже в три этапа: сначала рассматривается совместная работа вычислительной системы 5 и микросхемы 4 (фиг. 2), затем рассматривается измерение отрезков времени и после этого рассматривается вычисление отказоустойчивости микросхемы 4.

Совместная работа вычислительной системы 5 и микросхемы 4

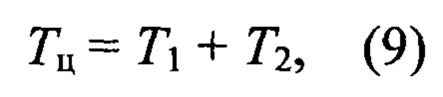

Начиная с момента своего включения вычислительная система 5 с постоянной частотой синхронно формирует пары управляющих сигналов начала и конца циклов работы микросхемы 4. Период этой частоты является длительностью Tц цикла работы вычислительной системы 5:

где Т1 - длительность времени между сигналами начала и конца цикла работы микросхемы 4,

Т2 - длительность обработки кода результата работы микросхемы 4, полученного в одном цикле ее работы.

Эта обработка кода результата работы микросхемы 4, полученного в одном цикле ее работы, осуществляется вычислительной системой 5, которая измеряет время работы микросхемы 4 по числу указанных циклов работы вычислительной системы 5, равному числу циклов работы микросхемы 4. Из формулы (9) видно, что цикл работы микросхемы 4 является частью цикла работы вычислительной системы 5.

Время облучения микросхемы 4 вычисляют умножением измеренного числа циклов работы вычислительной системы 5 на длительность Тц этого цикла.

Вычислительная система 5 передает в микросхему 4 управляющие сигналы начала цикла по соединению 9, и управляющие сигналы конца цикла работы микросхемы 4 - по соединению 10. Каждый цикл работы микросхемы 4 определен парой сигналов начала и конца цикла ее работы.

Сигналы начала цикла поступают в узел 15 управления приемом контрольных эталонов во входной регистр 13 микросхемы 4, а сигналы конца цикла работы микросхемы 4 поступают в узел 16 управления приемом кода результата работы микросхемы 4 в выходной регистр 14. В узлах 15 и 16 формируются управляющие сигналы приема кодов во входной регистр 13 и в выходной регистр 14 соответственно.

В начале каждого цикла по сигналу начала цикла, подаваемому в узел 15 из вычислительной системы 5, происходит прием контрольного эталона во входной регистр 13. Затем в результате переходного процесса в последовательных цепочках одинаковых комбинационных логических элементов 17 на входе выходного регистра 14 формируется код результата работы микросхемы 4 в течение одного цикла. И в конце цикла работы микросхемы 4 этот код принимают в выходной регистр 14. Потенциальные выходные сигналы регистра 14 передают в вычислительную систему 5 по соединению 8. Длительность цикла работы микросхемы 4 в основном определяется длительностью переходного процесса в последовательных цепочках одинаковых логических элементов 17, число которых в цепочке может быть очень большим.

Отказом микросхемы 4 считается отказ в ней одного или более логических элементов. Отказ микросхемы 4 фиксируется по несовпадению кода во входном регистре 13 с кодом в выходном регистре 14. Это несовпадение проверяется в вычислительной системе 5. Если в каком-либо цикле эти коды совпадают между собой, то в этом цикле отказа микросхемы не произошло. В следующем цикле можно сохранить прежний эталон во входном регистре 13, например, не подавая сигнал начала цикла в узел 15, и проверить несовпадение входного и выходного кодов микросхемы 4 в вычислительной системе 5.

Если в некотором цикле вычислительная система 5 обнаруживает отказ микросхемы, то в следующем цикле она в качестве эталона передает во входной регистр 14 ошибочный выходной код, полученный в предыдущем цикле. Если в этом следующем цикле выходной код микросхемы 4 совпадет с ошибочным входным кодом, то это означает, что в этом следующем цикле не было отказа. Если же в этом следующем цикле ошибочный входной код не совпадет с выходным кодом микросхемы 4, то это означает, что в этом следующем цикле произошел отказ, что будет зафиксировано вычислительной системой 5.

Однако возможен случай, когда выходной код микросхемы 4 совпадает с ошибочным входным кодом, но при этом произошел необнаруженный отказ микросхемы.

Это возможно, если необнаруженный отказ произошел в тех же цепочках логических элементов, т.е. в тех же разрядах комбинационной схемы 18, в которых он был раньше, но в других логических элементах. Однако вероятность того, что отказ микросхемы произошел в том же разряде n-разрядной комбинационной схемы 18 составит 1/n и будет незначительной при больших значениях n. Так при n=50 эта вероятность будет 0,02.

Рассмотрим теперь работу испытательной системы для косвенного измерения отказоустойчивости облучаемых испытательных цифровых микросхем, включая измерение времени работы микросхемы 4.

Измерение времени облучения

Перед началом работы устанавливают нужный режим источника 1 радиационного излучения с заданной постоянной интенсивностью I. Затем открывают затвор 2 по сигналу устройства 3 управления затвором 2, передаваемому по соединению 11. Затем в момент времени, регулируемый испытателем, по сигналу устройства 3, который подается по соединению 12, включают начало измерения в вычислительной системе 5 управления измерением. Момент начала измерения обозначим t0.

Поскольку время открытия механического затвора 2 достаточно большое (порядка нескольких секунд) и неопределенное, то момент начала облучения может не совпадать с моментом начала измерения в вычислительной системе 5. В связи с этим испытателю предоставлена возможность вести одновременно два вида (типа) измерения времени работы микросхемы 4.

В первом виде измерения за момент облучения, принятый за начальный, принимают момент начала измерения t0=0. Во втором виде измерения за момент облучения, принятый за начальный, принимают момент фиксации первого отказа микросхемы после момента начала измерений t0.

Как говорилось выше, время облучения микросхемы 4 измеряют числом циклов, умноженным на длительность цикла работы вычислительной системы 5 управления измерением.

Время облучения до момента первого отказа микросхемы измеряют от момента начала измерений t0=0 до цикла работы микросхемы 4, в котором будет обнаружен первый отказ микросхемы 4, характеризуемый фактом ошибки в ее выходном коде при сравнении его с входным контрольным эталоном (во входном регистре 13) микросхемы 4, соответствующим моменту начала измерения t0=0.

По окончании заданного числа циклов в вычислительной системе 5 вычисляют условный начальный отрезок времени tотк облучения микросхемы 4 до ее отказа, позволяющий оценить вероятность отказа микросхемы 4. В качестве этого указанного начального отрезка времени работы микросхемы 4 до ее отказа вычисляют средний начальный отрезок времени облучения микросхемы от момента облучения, принятого за начальный, до ее последнего отказа в заданном числе соседних циклов ее работы.

Пусть, например, после момента tн облучения, принятого за начальный, в заданном числе циклов произойдут отказы микросхемы 4 в моменты t1, t2 и t3. Тогда средний начальный отрезок времени облучения микросхемы 4 будет tотк=(t1+t2+t3)/3.

Для вычисления, например, времени t3 сначала измеряют отрезок времени Λ23=t3-t2 от момента t2 предыдущего отказа микросхемы 4 до момента t3 следующего ее отказа, после чего вычисляют момент t3 следующего ее отказа: t3=t2+Λ23.

Для получения величин, аналогичных величине Λ23 измеряют отрезок времени облучения микросхемы 4 от момента предыдущего ее отказа до момента следующего ее отказа по числу циклов работы микросхемы 4, прошедших от момента предыдущего отказа до цикла ее работы, в котором будет обнаружена ошибка в выходном коде микросхемы 4 при сравнении этого кода с эталоном, соответствующим выходному коду результата при предыдущем отказе микросхемы 4.

Оценим приблизительно длительность цикла Tц по формуле (4). Длительность Т1 времени между сигналами начала и конца цикла микросхемы 4 оценим приблизительно по времени переходного процесса в комбинационной схеме 18, пренебрегая временем приема кодов во входной регистр 13 и в выходной регистр 14 микросхемы 2. Примем, что число двоичных разрядов в каждом из этих регистров и в комбинационной схеме 18 будет n=50. Тогда, если число логических элементов в схеме 18 равно 100000, то длина цепочки логических элементов в одном двоичном разряде схемы 18 будет равно 2000. При задержке на логический элемент (вентиль) 1 нсек, длительность Т1 переходного процесса в схеме 18 будет 2000 нсек, т.е. 2 мксек. Примем, например, что длительность обработки кода результата работы микросхемы 4 в одном цикле Т2=1 мксек, что вполне реально при тактовой частоте 50 мгц вычислительной системы 5. В этом случае длительность цикла составит 3 мксек, а частота циклов составит 0.33 мгц.

Вычисление экспериментальной оценки отказоустойчивости

По окончании измерения среднего отрезка времени tотк облучения микросхемы 4 до ее отказа в вычислительной системе 5 вычисляют флюенс, при котором произошел отказ микросхемы, по формуле:

где Ф - флюенс,

I - постоянная интенсивность облучения,

tотк - начальный отрезок времени облучения микросхемы до ее отказа, позволяющий оценить вероятность отказа микросхемы,

а затем по вычисленному флюенсу и заданным характеристикам микросхемы, указанным ниже, вычисляют отказоустойчивость микросхемы по соответствующей способу ее построения формуле вероятности отказа микросхемы:

где j - идентификатор способа построения микросхемы,

Pот,j - вероятность отказа микросхемы, характеризующая ее отказоустойчивость,

ƒj, Фj и Sj - формула, флюенс и площадь микросхемы, соответствующие j-му способу построения микросхемы,

N - число условных одинаковых компонентов, в частности, логических элементов, в микросхеме,

W - вероятность повреждения единицы площади микросхемы при попадании в нее частицы.

В качестве формулы (3) вычислительная система 5 вычисляет вероятность отказа микросхемы 4 по одной из формул, соответствующих способу построения микросхемы 4, в частности, по одной из следующих формул:

1) для нерезервированной микросхемы 4 по формуле

где все величины определены выше;

2) для структурно дублированной микросхемы 4 по формуле:

где β - относительная вероятность отказа дублированного элемента при попадании частицы в его нерезервированный компонент:

где nотк - среднее число нерезервированных компонентов дублирующего элемента,

ned - среднее число компонентов в дублирующем элемента, остальные величины определены выше;

3) для квадрированной микросхемы по формуле:

где n4кв - среднее число квадрированных транзисторов в одном квадрированном логическом элементе,

μ - относительная вероятность попадания частицы в отказывающую пару одиночных транзисторов,

остальные величины определены выше;

4) для 9-кратно резервированной микросхемы по формуле:

где все величины определены выше.

В дальнейшем при появлении более точных теоретических оценок отказоустойчивости микросхем при облучении и при теоретической оценке отказоустойчивости других способов поэлементного резервирования в качестве формулы (3) могут быть использованы другие формулы.