Результат интеллектуальной деятельности: Триггерный сумматор по модулю два на полевых транзисторах

Вид РИД

Изобретение

Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Оно, в частности, может быть использовано в блоках вычислительной техники, содержащих сумматоры чисел, цифровые компараторы, преобразователи кода Грея в двоичный позиционный.

Известен логический элемент Исключающее ИЛИ - сумматор по модулю два [1 Опадчий Ю.Ф., Глудкин О.П., Гуров А.И. Аналоговая и цифровая электроника. - М.: Горячая линия - Телеком, 2003, стр. 606, рис.18.2, а], содержащий пять логических элементов И-НЕ. При выполнении элементов И-НЕ на полевых транзисторах [1, стр. 665, рис. 19.29, а] сумматор по модулю два содержит 15 транзисторов и источник питающего постоянного напряжения.

Недостатком его является малая нагрузочная способность. Выходом сумматора по модулю два является выход последнего логического элемента И-НЕ. Электрический ток внешней нагрузки в нем формирует только один полевой транзистор. Если бы такой ток формировали несколько транзисторов, то это повысило бы максимальную силу тока внешней нагрузки и повысило бы нагрузочную способность сумматора по модулю два.

Наиболее близким по технической сущности и достигаемому результату является выбранный в качестве прототипа элемент Исключающее ИЛИ – сумматор по модулю два. [2 Шило В.Л. Популярные цифровые микросхемы.- Челябинск: Металлургия, 1989. Стр.56, рис. 1.35, а], содержащий четыре логических элемента И-НЕ. При использовании элементов И-НЕ на полевых транзисторах [1, стр.665, рис. 19.29, а] сумматор по модулю два включает в себя 12 транзисторов и источник питающего постоянного напряжения. Недостатком его является малая нагрузочная способность. Выходом сумматора по модулю два является выход последнего логического элемента И-НЕ. Электрический ток внешней нагрузки в нем формирует только один полевой транзистор. Если бы такой ток формировали два транзистора, то это повысило бы максимальную силу тока внешней нагрузки и повысило бы нагрузочную способность сумматора по модулю два.

Задача, на решение которой направленно изобретение, состоит в повышении нагрузочной способности сумматора по модулю два на полевых транзисторах.

Это достигается тем, что в триггерный сумматор по модулю два на полевых транзисторах, содержащий источник питающего постоянного напряжения, общая шина (минусовой вывод) которого заземлена, последовательно соединенные первый и второй полевые транзисторы с индуцированными каналами n-типа, два вывода двух затворов этих двух транзисторов относительно «земли» образуют первый и второй входы сумматора, подложки полевых транзисторов соединены с их истоками, исток второго транзистора заземлен, третий полевой транзистор с индуцированным каналом n-типа, подложка которого соединена с его истоком, введены три дополнительных полевых транзистора и шесть резисторов, затвор третьего полевого транзистора соединен с первым входом сумматора, последовательно между собой включены первый дополнительный полевой транзистор с индуцированным n каналом и первый резистор, сток первого дополнительного транзистора подключен к стоку третьего транзистора, затвор – ко второму входу сумматора, подложка – к его истоку, свободный вывод первого резистора заземлен, общий вывод его и истока первого дополнительного транзистора соединен с истоком третьего транзистора, последовательно между собой включены второй резистор, второй дополнительный полевой транзистор с индуцированным каналом n-типа и третий резистор, свободный вывод второго резистора подключен к выходу источника питающего постоянного напряжения, общий вывод второго резистора и стока второго дополнительного транзистора подсоединен к общему выводу стоков третьего и первого дополнительного транзисторов, подложка второго дополнительного транзистора соединена с его истоком, последовательно включены четвертый резистор, третий дополнительный полевой транзистор с индуцированным р-каналом и пятый резистор, свободный вывод четвертого резистора подключен к общему выводу второго резистора и выхода источника питающего постоянного напряжения, подложка третьего дополнительного транзистора подсоединена к его истоку и их общий вывод соединен со стоком первого транзистора, затвор третьего дополнительного транзистора подключен к общему выводу второго резистора, стоков третьего, первого дополнительного и второго дополнительного транзисторов, общий вывод пятого резистора и стока третьего дополнительного транзистора подсоединен к затвору второго дополнительного транзистора, свободный вывод пятого резистора соединен со свободным выводом третьего резистора, и их общий вывод образует относительно «земли» выход сумматора по модулю два, шестой резистор включен между «землей» и общим выводом четвертого резистора, истока и подложки третьего дополнительного транзистора и стока первого транзистора.

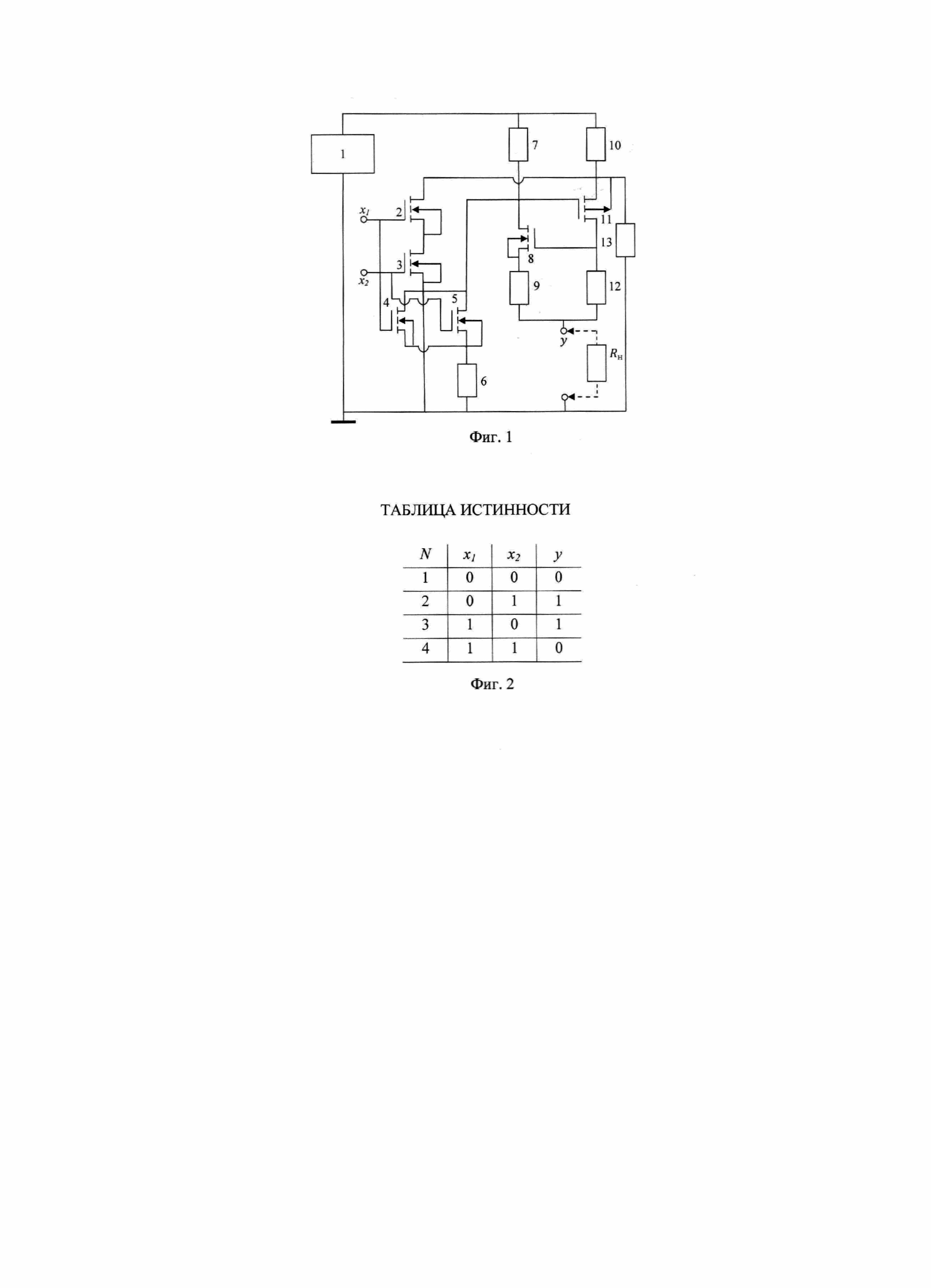

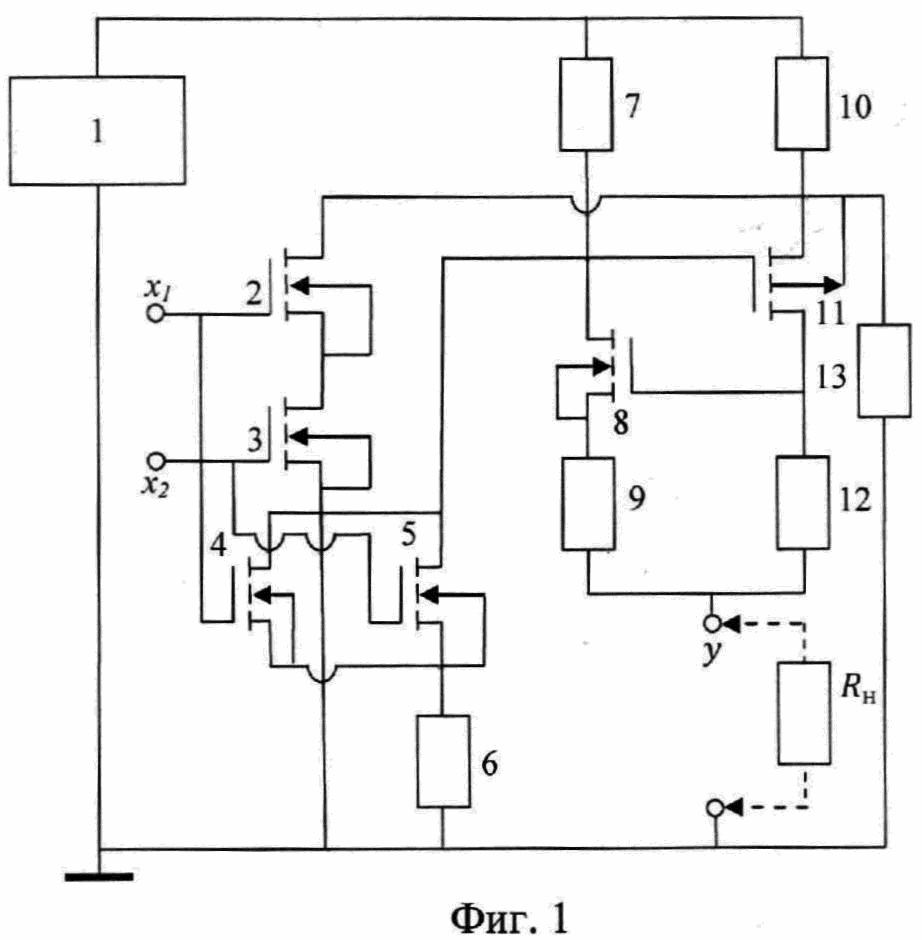

Сущность изобретения поясняется схемой триггерного сумматора по модулю два на полевых транзисторах (фиг.1) и его таблицей истинности (фиг.2).

В триггерном сумматоре по модулю два на полевых транзисторах общая шина (минусовой вывод) источника 1 питающего постоянного напряжения заземлена. Последовательно между собой включены полевые транзисторы 2 и 3 с индуцированными каналами n-типа. Подложки этих транзисторов подключены к их истокам, а выводы затворов образуют относительного «земли» два входа х1 и х2 сумматора по модулю два. Общий вывод истока и подложки транзистора 3 заземлен. Параллельно между собой включены полевые транзисторы 4 и 5 с индуцированными каналами n-типа. Подложки этих транзисторов подсоединены к их истокам. Затвор транзистора 4 подключен к первому входу х1 сумматора, а затвор транзистора 5 – ко второму входу х2. Общий вывод истоков транзисторов 4 и 5 соединен с одним из выводов резистора 6, другой вывод этого резистора заземлен.

Последовательно включены резистор 7, полевой транзистор 8 с индуцированным каналом n-типа и резистор 9. Свободный вывод резистора 7 подключен к выходу (плюсовой вывод) источника 1 питающего постоянного напряжения. Общий вывод этого резистора и стока транзистора 8 подсоединен к общему выводу стоков параллельно включенных транзисторов 4 и 5. Подложка транзистора 8 соединена с его истоком.

Последовательно включены резистор 10, полевой транзистор 11 с индуцированным каналом р-типа и резистор 12. Свободный вывод резистора 10 подключен к общему выводу резистора 7 и выхода источника 1. Затвор транзистора 11 подсоединен к общему выводу резистора 7 и стоков транзисторов 4, 5 и 8. Подложка транзистора 11 соединена с его истоком и их общий вывод с резистором 10 подключен к стоку транзистора 2. Общий вывод стока транзистора 11 и резистора 12 подключен к затвору транзистора 8. Свободный вывод резистора 12 соединен со свободным выводом резистора 9 и их общий вывод образует относительно «земли» выход сумматора по модулю два y. Резистор 13 включен между «землей» и общим выводом резистора 10, истока и подложки транзистора 11 и стока транзистора 2. На фиг.1 также приведен подключенный к выходу сумматора резистор Rн, который условно отображает внешнюю нагрузку сумматора. Часть схемы на фиг.1 на транзисторах 8, 11 и резисторах 7, 9, 10 и 12 является триггером на транзисторах противоположного типа проводимости.

Триггерный сумматор по модулю два на полевых транзисторах работает следующим образом. В цифровой электронике используются входные и выходные электрический сигналы с низким и высоким уровнем напряжения. Низкий уровень – уровень логического нуля соответствует значениям напряжения в районе нуля (ближе к нулю), высокий уровень – уровень логической единицы соответствует значениям напряжения в районе единиц вольт (нередко в районе четырех вольт). Работа сумматоров по модулю два отображается известной таблицей истинности (фиг.2), где N-номер строки по порядку х1 и х2 – условное отображение входных сигналов и y – условное отображение выходного сигнала. В соответствии с первыми тремя строками таблицы истинности (фиг.2) на затворы одного из полевых транзисторов 2, 3 или обоих поступает низкий уровень напряжения – уровень логического нуля и сила электрического тока через последовательно включенные транзисторы 2, 3 в худшем случае настолько мала, что не оказывает влияние на последующую схему.

В соответствии с первой строкой таблицы истинности (фиг.2) на затворы транзисторов 4 и 5 подаются низкие уровни напряжения, и возможная сила электрического тока этих параллельно включенных транзисторов тоже весьма мала. Электрический ток через резисторы 10 и 13 создает на резисторе 10 напряжение, которое минусом приложено к истоку транзистора 11 с индуцированным каналом р-типа, а плюсом через резистор 7 к его затвору. Значением сопротивления резистора 13 можно обеспечить уверенный перевод транзистора 11 в непроводящее электрический ток состояние. Тогда напряжение на затворе транзистора 8 обеспечивает его непроводящий электрический ток состояние. В итоге на внешней нагрузке низкий уровень напряжения – уровень логического нуля.

В соответствии со 2-й и 3-й строками таблицы истинности (фиг.2) на затвор одного из двух параллельно включенных транзисторов 4, 5 подается высокий уровень напряжения. Тогда сила электрического тока одного из транзисторов имеет повышенное значение и создает на резисторе 7 высокий уровень напряжения, который с учетом напряжения на резисторе 10 за счет электрического тока через резистор 13 поддерживает проводящий электрический ток состояние транзистора 11. Напряжение на резисторе 12 за счет тока стока транзистора 11 обеспечивает проводящее электрический ток состояние транзистора 8. Сумма силы токов транзисторов 8 и 11 создает на внешней нагрузке высокий уровень напряжения – уровень логической единицы.

При четвертой строке таблицы истинности (фиг.2) оба транзистора 4, 5 проводят электрический ток и за счет напряжения на резисторе 7 обеспечивают проводящее ток состояние транзистора 11, если бы в схеме отсутствовали полевые транзисторы 2 и 3. При наличии этих транзисторов на их затворы тоже подаются высокие уровни напряжения, и они проводят электрический ток. На резистор 10 замыкаются электрические токи последовательно включенных транзисторов 2, 3 и через резистор 13. Возрастание силы этих токов приводит к уменьшению силы тока транзистора 11 и может закрыть этот транзистор (его не проводящее ток состояние). В последнем случае должно выполняться неравенство  , где R7 и R10 – сопротивление резисторов 7 и 10, I23 – сила электрического тока через последовательно включенные транзисторы 2 и 3, I45 – сумма силы токов параллельно включенных 4 и 5 транзисторов, I13 – сила тока через резистор 13 и Uпор 11 – пороговое напряжение полевого транзистора 11. Непроводящее электрический ток состояние транзистора 11 вызывает непроводящее ток состояние транзистора 8. Тогда на выходе сумматора по модулю 2 (на его внешней нагрузке) имеем уровень логического нуля.

, где R7 и R10 – сопротивление резисторов 7 и 10, I23 – сила электрического тока через последовательно включенные транзисторы 2 и 3, I45 – сумма силы токов параллельно включенных 4 и 5 транзисторов, I13 – сила тока через резистор 13 и Uпор 11 – пороговое напряжение полевого транзистора 11. Непроводящее электрический ток состояние транзистора 11 вызывает непроводящее ток состояние транзистора 8. Тогда на выходе сумматора по модулю 2 (на его внешней нагрузке) имеем уровень логического нуля.

Таким образом, сила электрического тока на внешней нагрузке триггерного сумматора по модулю два на полевых транзисторах определяется силой тока не одного транзистора, а суммой силы токов двух транзисторов, что повышает его нагрузочную способность.

Триггерный сумматор по модулю два на полевых транзисторах, содержащий источник питающего постоянного напряжения, общая шина (минусовой вывод) которого заземлена, последовательно соединенные первый и второй полевые транзисторы с индуцированными каналами n-типа, два вывода двух затворов этих двух транзисторов относительно «земли» образуют первый и второй входы сумматора, подложки полевых транзисторов соединены с их истоками, исток второго транзистора заземлен, третий полевой транзистор с индуцированным каналом n-типа, подложка которого соединена с его истоком, отличающийся тем, что в него введены три дополнительных полевых транзистора и шесть резисторов, затвор третьего полевого транзистора соединен с первым входом сумматора, последовательно между собой включены первый дополнительный полевой транзистор с индуцированным n каналом и первый резистор, сток первого дополнительного транзистора подключен к стоку третьего транзистора, затвор – ко второму входу сумматора, подложка – к его истоку, свободный вывод первого резистора заземлен, общий вывод его и истока первого дополнительного транзистора соединен с истоком третьего транзистора, последовательно между собой включены второй резистор, второй дополнительный полевой транзистор с индуцированным каналом n-типа и третий резистор, свободный вывод второго резистора подключен к выходу источника питающего постоянного напряжения, общий вывод второго резистора и стока второго дополнительного транзистора подсоединен к общему выводу стоков третьего и первого дополнительного транзисторов, подложка второго дополнительного транзистора соединена с его истоком, последовательно включены четвертый резистор, третий дополнительный полевой транзистор с индуцированным р-каналом и пятый резистор, свободный вывод четвертого резистора подключен к общему выводу второго резистора и выхода источника питающего постоянного напряжения, подложка третьего дополнительного транзистора подсоединена к его истоку и их общий вывод соединен со стоком первого транзистора, затвор третьего дополнительного транзистора подключен к общему выводу второго резистора, стоков третьего, первого дополнительного и второго дополнительного транзисторов, общий вывод пятого резистора и стока третьего дополнительного транзистора подсоединен к затвору второго дополнительного транзистора, свободный вывод пятого резистора соединен со свободным выводом третьего резистора, и их общий вывод образует относительно «земли» выход сумматора по модулю два, шестой резистор включен между «землей» и общим выводом четвертого резистора, истока и подложки третьего дополнительного транзистора и стока первого транзистора.