Результат интеллектуальной деятельности: СОСТАВНОЙ ТРАНЗИСТОР НА ОСНОВЕ КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ

Вид РИД

Изобретение

Изобретение относится к области микроэлектроники и может быть использовано в качестве активного элемента (трехполюсника) в различных аналоговых устройствах (операционных усилителях, усилителях мощности, драйверах линий связи и т.п.), допускающих работу в условиях воздействия проникающей радиации и низких температур.

В современной микроэлектронике находят применение так называемые отставные транзисторы (СТ), которые содержат несколько элементарных транзисторов, в том числе с разными принципами работы [1-9]. Такое схемотехническое решение рекомендуется использовать в том случае, когда элементарные транзисторы не позволяют самостоятельно обеспечить то или иное требуемое качество, например, большое усиление по току (схема Дарлингтона, схема Линна, схема Шиклая), более широкий частотный диапазон (каскодные СТ, СТ с компенсацией емкости коллектор-база), повышенное выходное сопротивление (каскодные СТ), улучшенный коэффициент ослабления входных синфазных сигналов (СТ со «следящим» питанием), повышенные рабочие напряжения (последовательное включение элементарных транзисторов), повышенный уровень максимального тока стока (параллельное включение нескольких элементарных транзисторов) и т.п. [7-9]. Данные схемотехнические приемы [1-9,11,12] являются основой современной микросхемотехники [7].

Для решения задач космического приборостроения (низкие температуры, проникающая радиация) перспективно использование полевых транзисторов с управляющим pn-переходом (JFet) [10], которые также обеспечивают низкий уровень шумов. Однако, в активном режиме, JFet обладают «не удобной» полярностью напряжений между затвором и истоком, которая противоположна по знаку напряжению между стоком и истоком. Указанные выше особенности JFet транзисторов не позволяют применять в аналоговой микроэлектронике известные схемотехнические решения СТ [7], которые эффективны для КМОП и биполярных транзисторов.

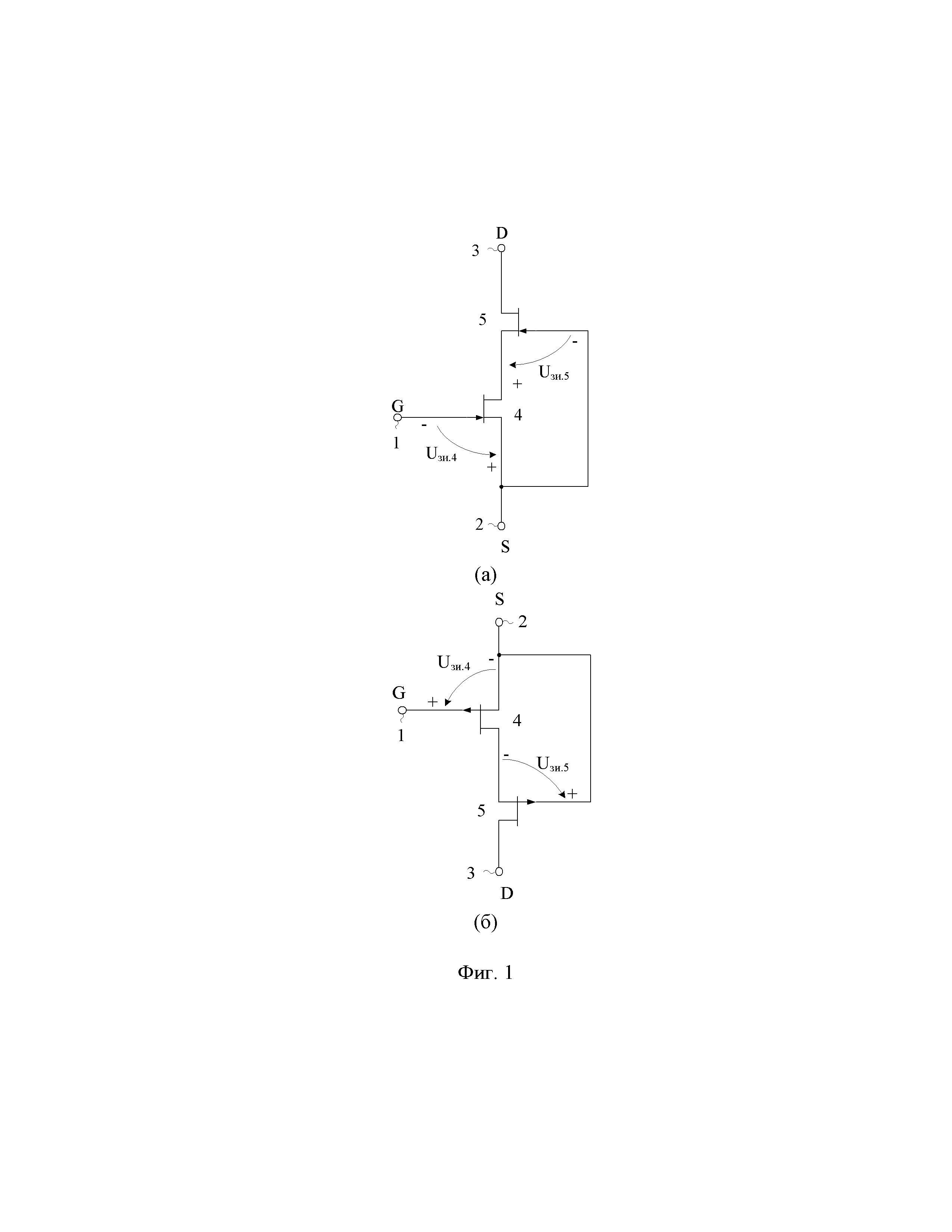

Ближайшим прототипом заявляемого устройства является составной транзистор (фиг. 1), представленный в патенте US 5065043, fig. 1A, fig. 2A, 1991 г. Он содержит затвор 1, исток 2 и сток 3 устройства, первый 4 полевой транзистор, затвор которого подключен к затвору 1 устройства, второй 5 полевой транзистор, сток которого соединен со стоком 3 устройства.

Основная задача предполагаемого изобретения состоит в создании составного транзистора (трехполюсника) на комплементарных (CJFet) транзисторах, который по своим стоко-затворным (UGS) характеристикам подобен КМОП полевому транзистоу, т.е. имеет характерную зону закрытого состояния при напряжении затвор-исток не превышающем пороговое напряжение (Uп), а при напряжении UGS на эквивалентном затворе 1 устройства, превышающем Uп, переходит в активный режим и может использоваться в задачах аналогового усиления сигналов при управлении по цепи затвора 1. При этом относительно эквивалентного вывода стока 3 устройства сигнал в заявляемом СТ не инвертируется.

Поставленная задача достигается тем, что в схеме составного транзистора-прототипа фиг. 1, содержащего затвор 1, исток 2 и сток 3 устройства, первый 4 полевой транзистор, затвор которого подключен к затвору 1 устройства, второй 5 полевой транзистор, сток которого соединен со стоком 3 устройства, предусмотрены новые элементы и связи между ними – первый 4 полевой транзистор и второй 5 полевой транзистор имеют разные типы каналов (p и n), сток первого 4 полевого транзистора соединен с истоком 2 устройства, его исток соединен с истоком второго 5 полевого транзистора, а затвор второго 5 полевого транзисторов соединен с истоком 2 устройства.

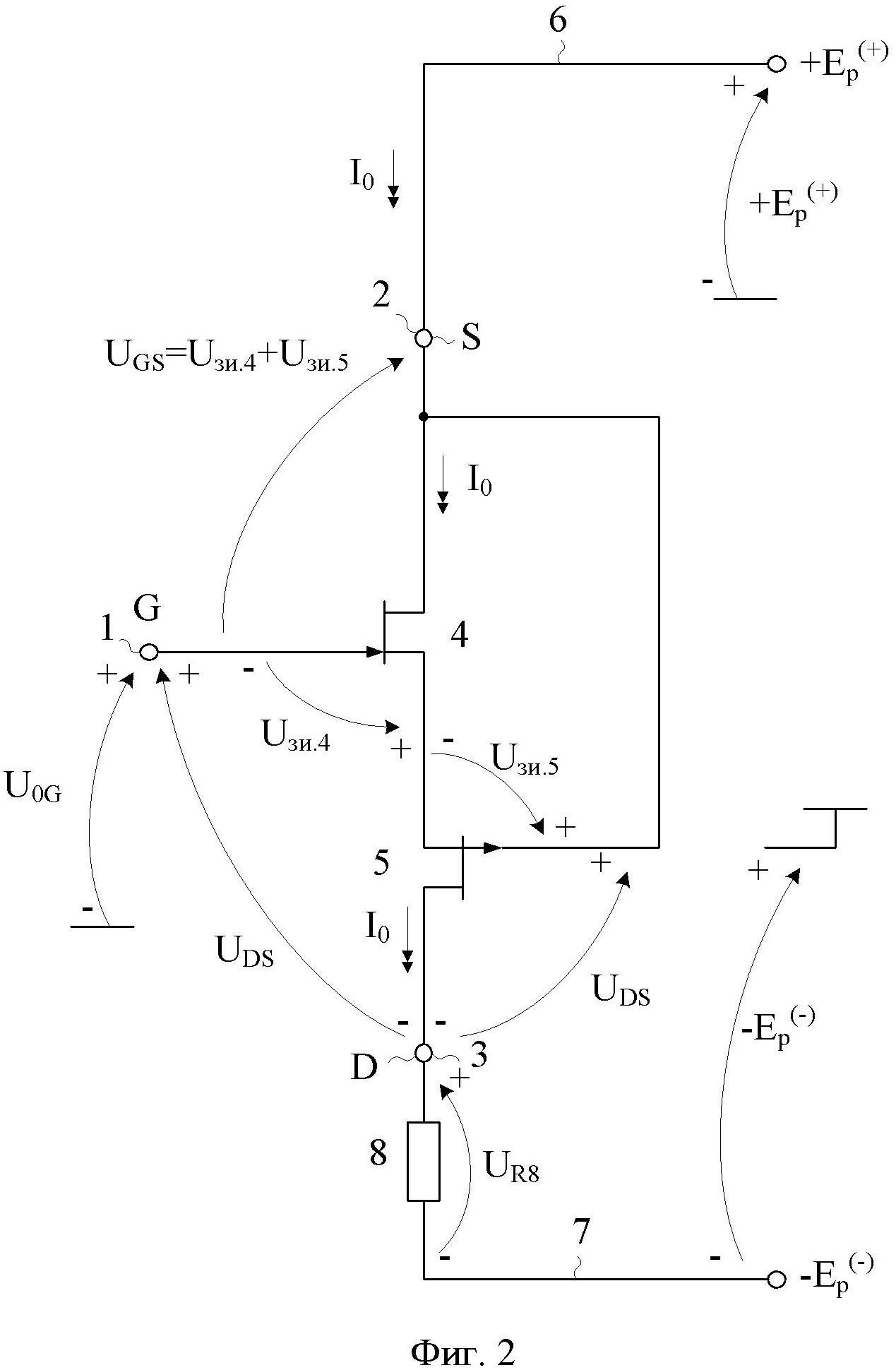

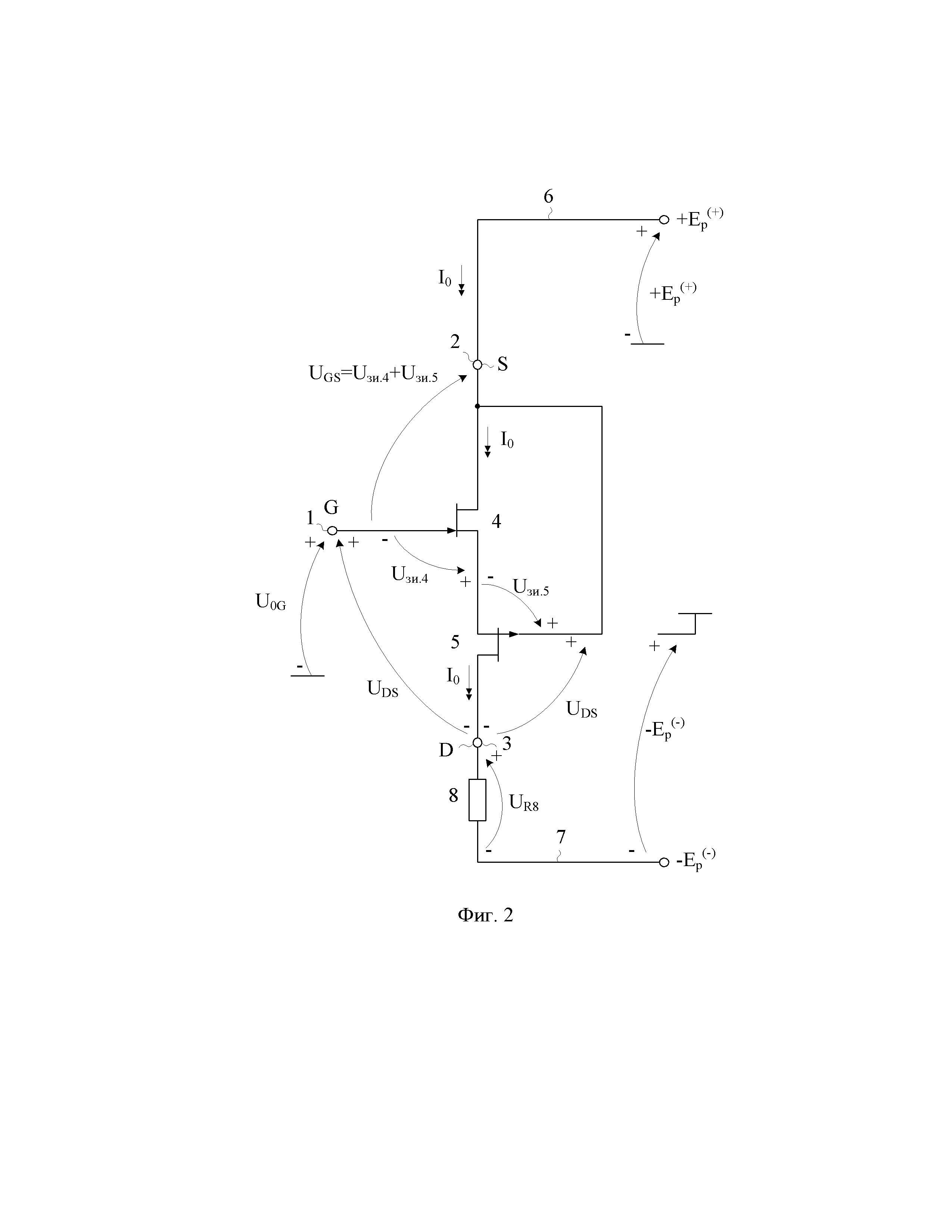

На чертеже фиг. 1 представлена схема составного транзистора-прототипа, а на чертеже фиг. 2 – заявляемая схема СТ в соответствии с п. 1 и п. 2 формулы изобретения.

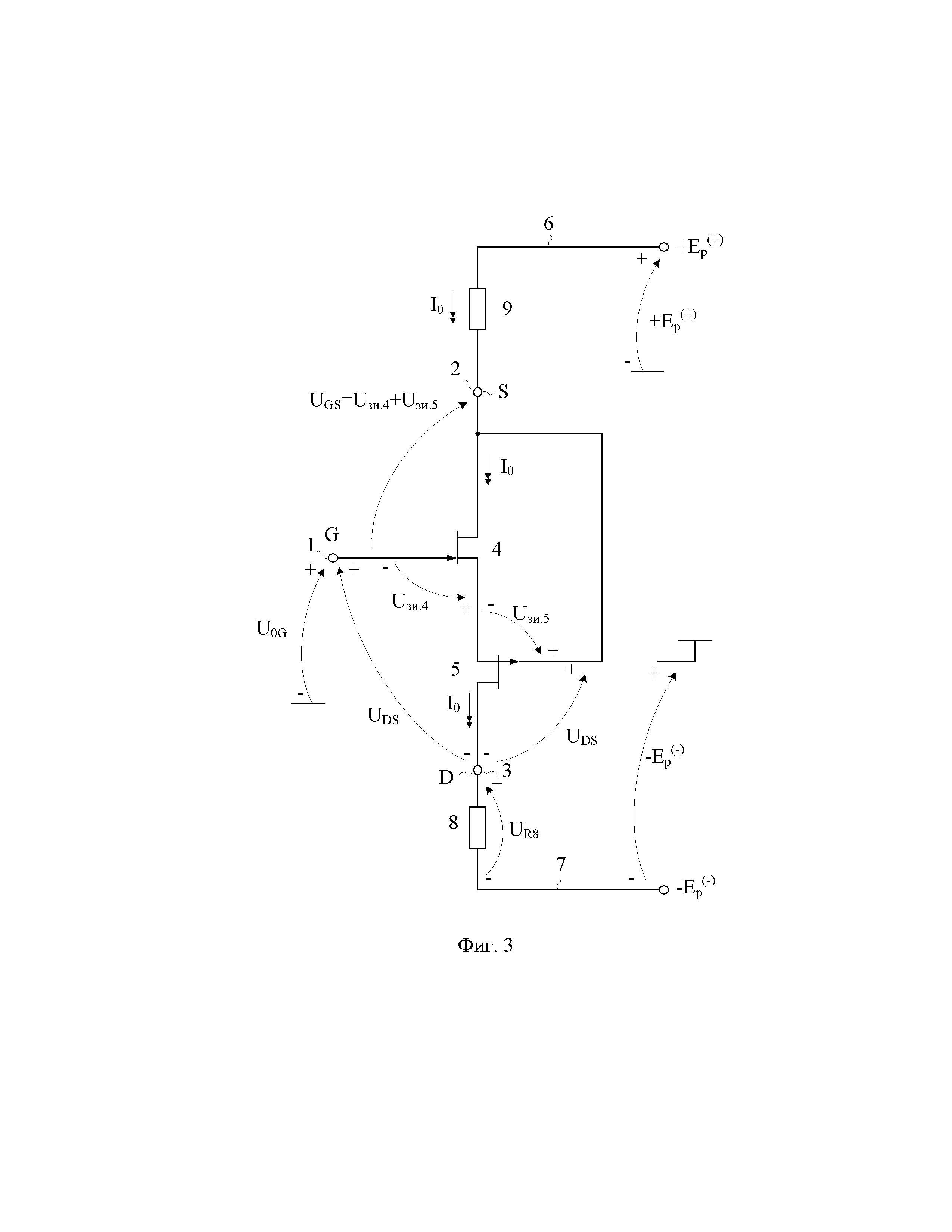

На чертеже фиг. 3 показана схема составного транзистора в соответствии с п. 3 формулы изобретения. Здесь в схему введен второй 9 двухполюсник нагрузки, первый 4 полевой транзистор имеет n-канал, а второй 5 полевой транзистор – p-канал.

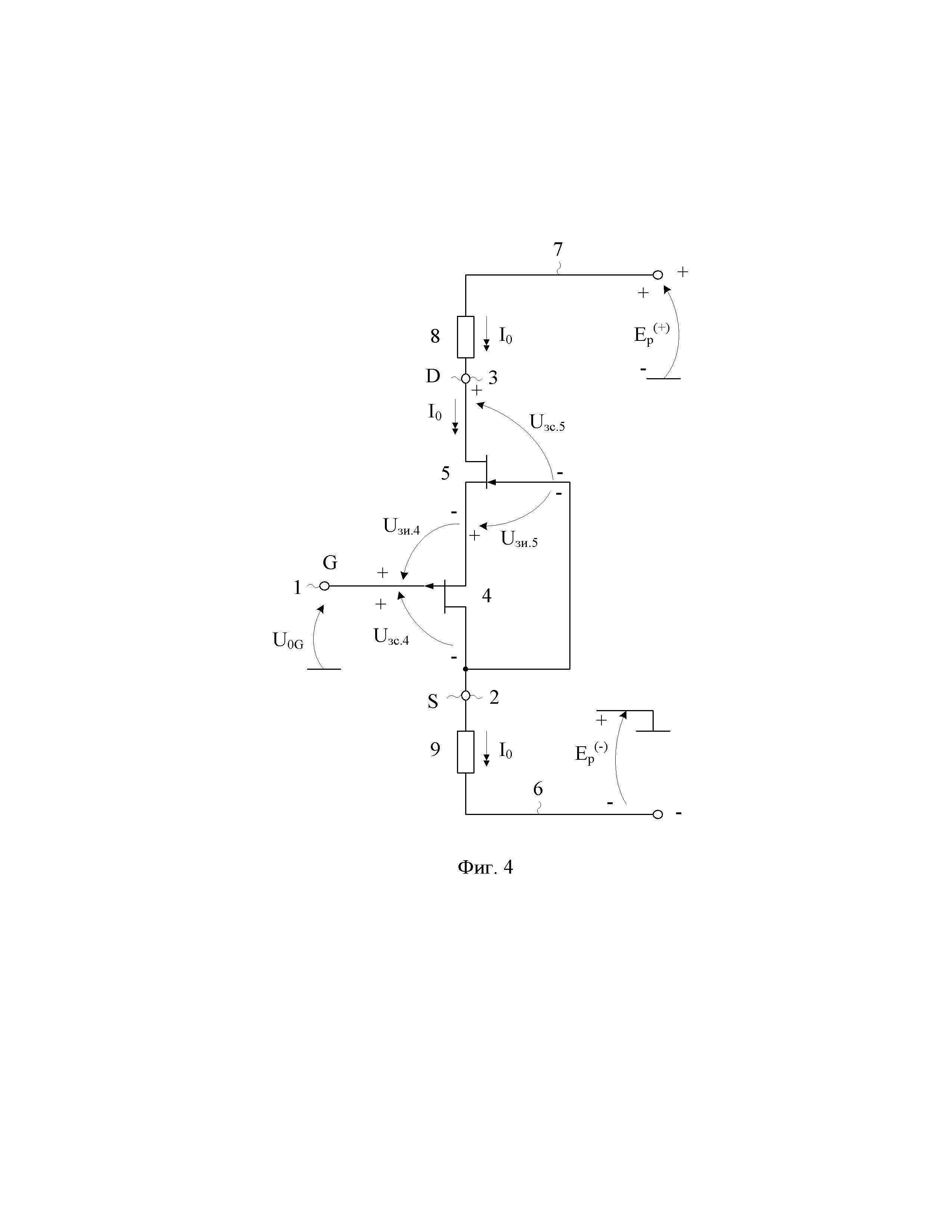

На чертеже фиг. 4 приведена заявляемая схема составного транзистора, которая также соответствует п. 3 формулы изобретения для случая, когда первый (4) полевой транзистор имеет p-канал, а второй (5) полевой транзистор – n-канал.

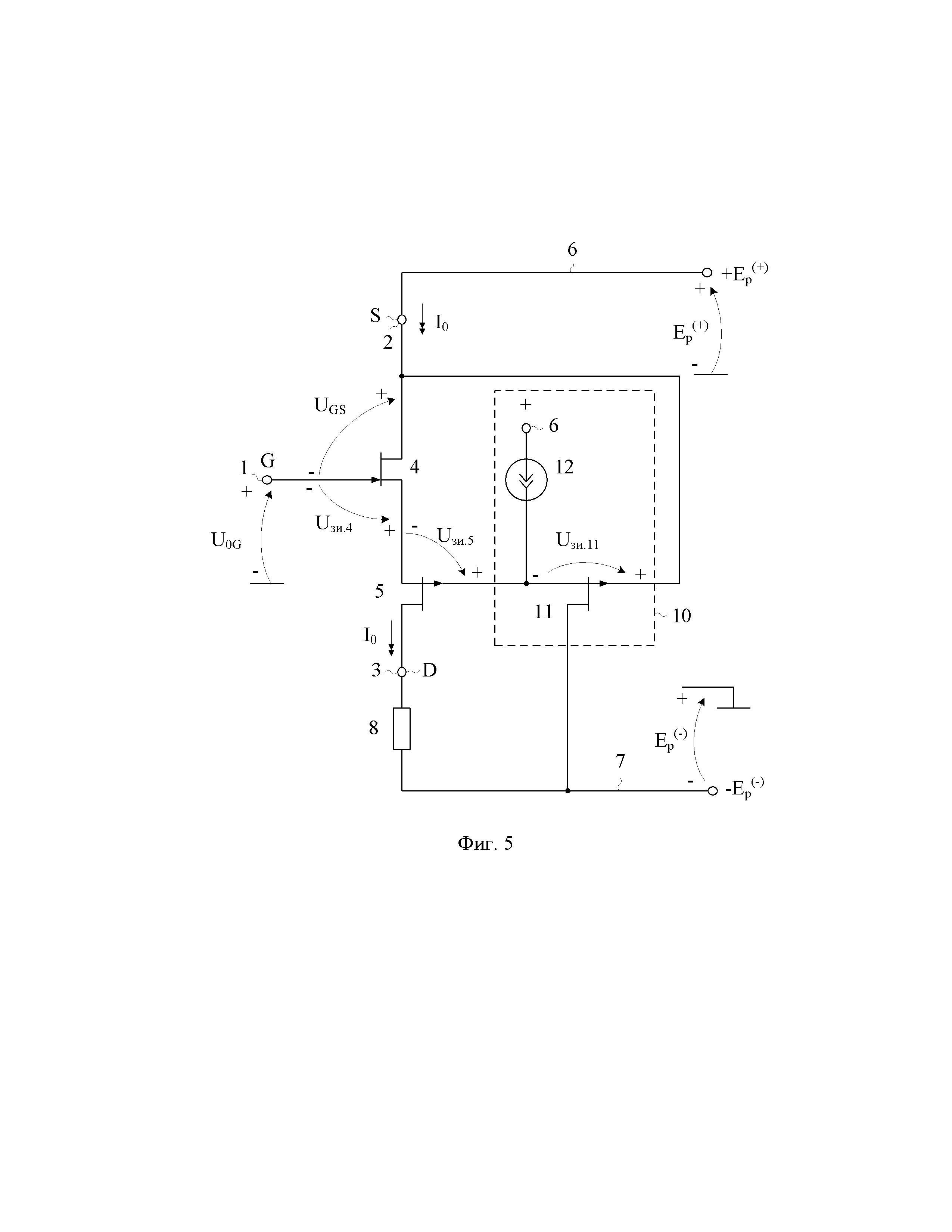

На чертеже фиг. 5 представлена схема составного транзистора в соответствии с п. 4 и п. 5 формулы изобретения.

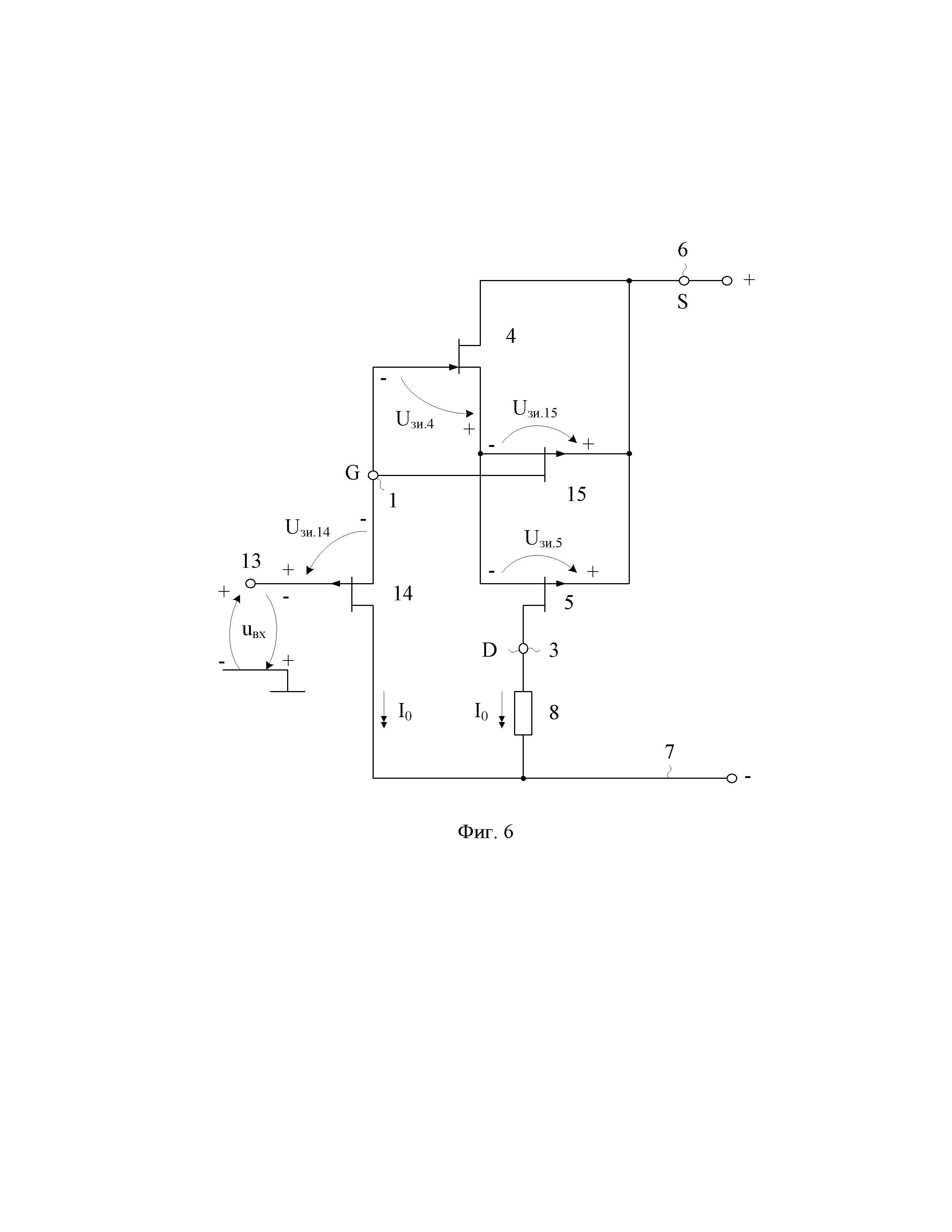

На чертеже фиг. 6 показана схема составного транзистора в соответствии с п. 6 формулы изобретения.

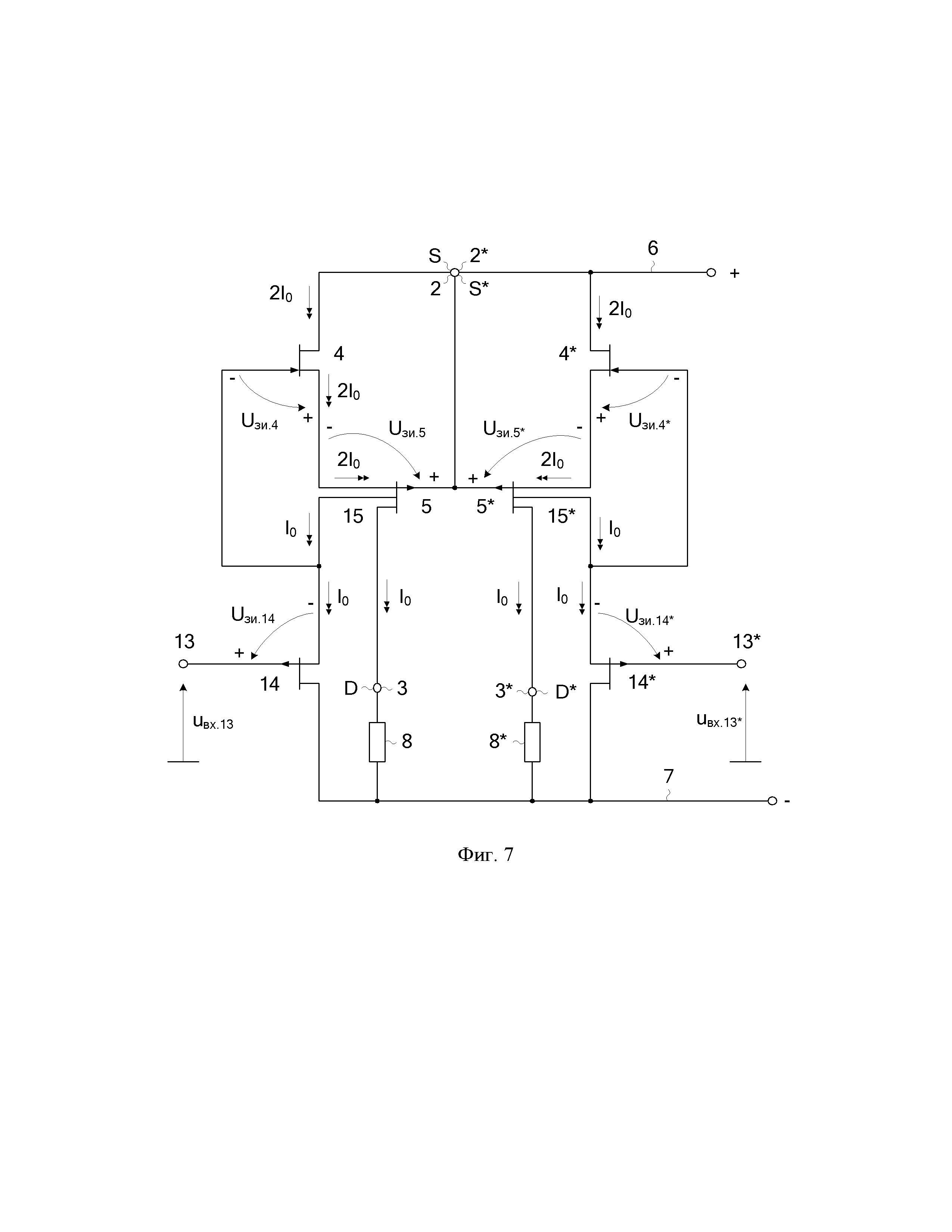

На чертеже фиг. 7 приведен пример построения дифференциального каскада на основе двух составных транзисторов фиг. 6.

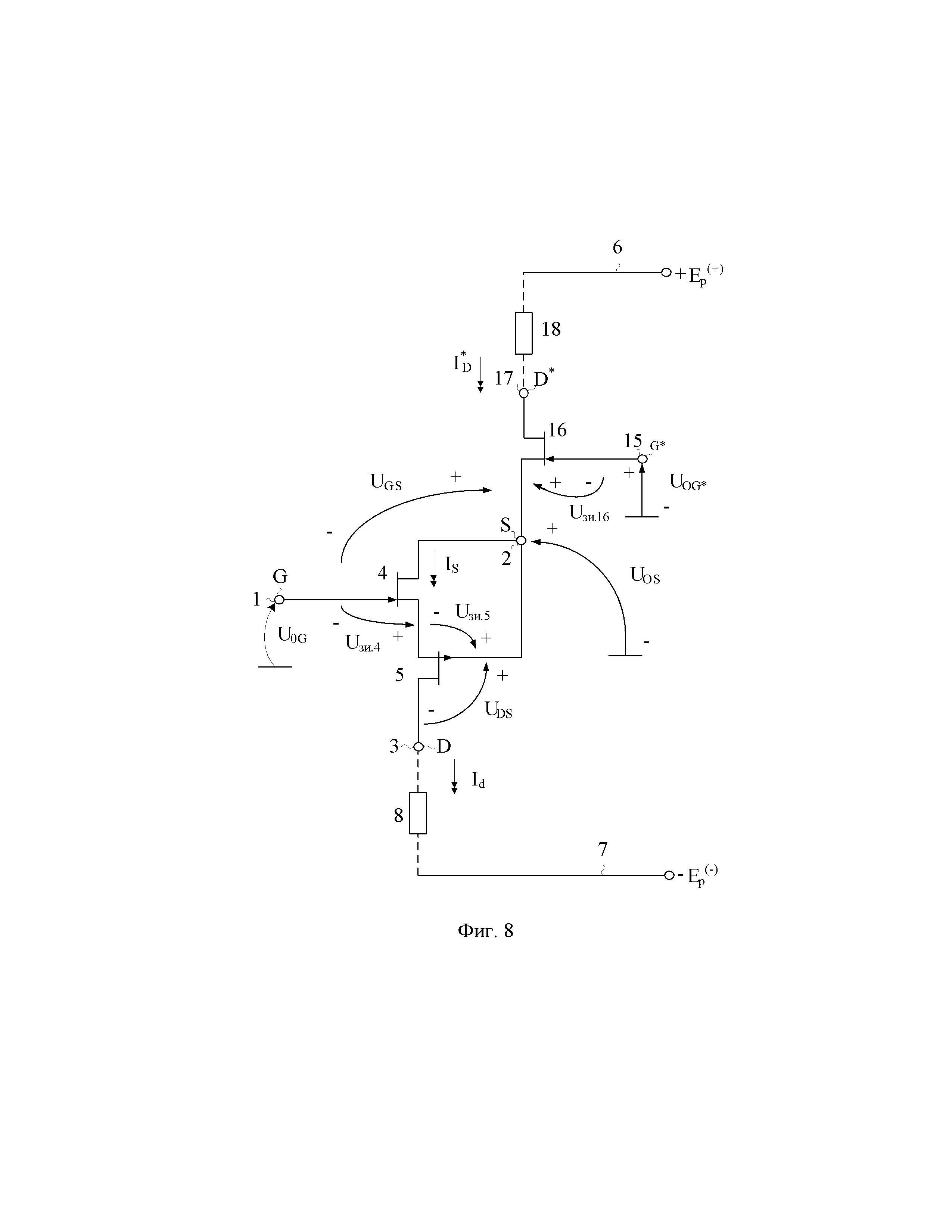

На чертеже фиг. 8 приведена схема заявляемого составного транзистора в соответствии с п. 7 формулы изобретения.

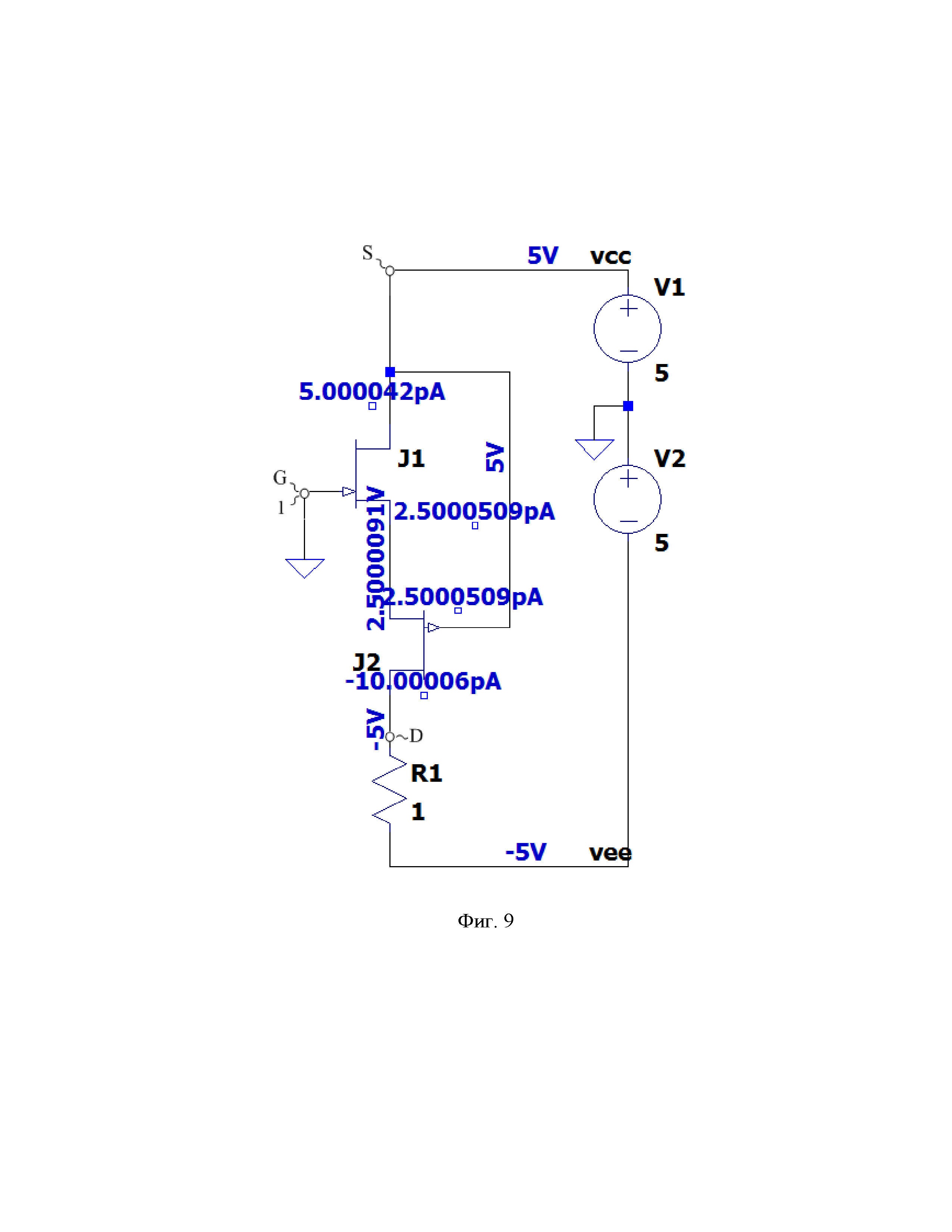

На чертеже фиг. 9 показан статический режим составного транзистора фиг. 2 в среде компьютерного моделирования LTSpice при нулевом (относительно общей шины) напряжении U0G на затворе 1 устройства (в соответствии с п. 1 формулы изобретения) и температуре окружающий среды 27°C.

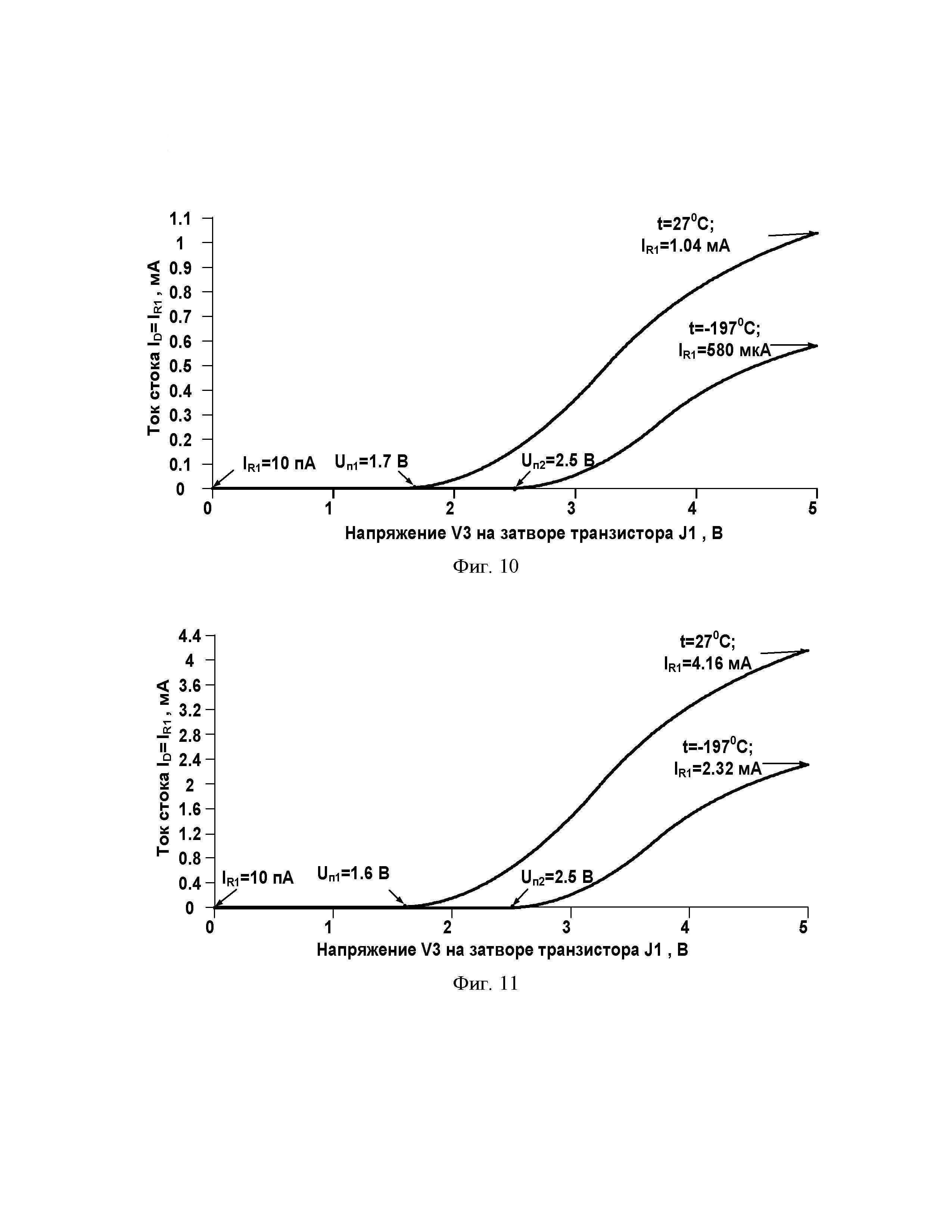

На чертеже фиг. 10 представлены стоко-затворные характеристики составного транзистора фиг. 9 в среде LTSpice при t=27°C, t=-197°C и напряжениях питания Eп= ±5В.

На чертеже фиг. 11 показаны стоко-затворные характеристики составного транзистора фиг. 9 в среде LTSpice при t=27°C, t=-197°C, при напряжениях питания Eп= ±5В и четырех параллельно включенных JFet транзисторах в структуре J1 и J2.

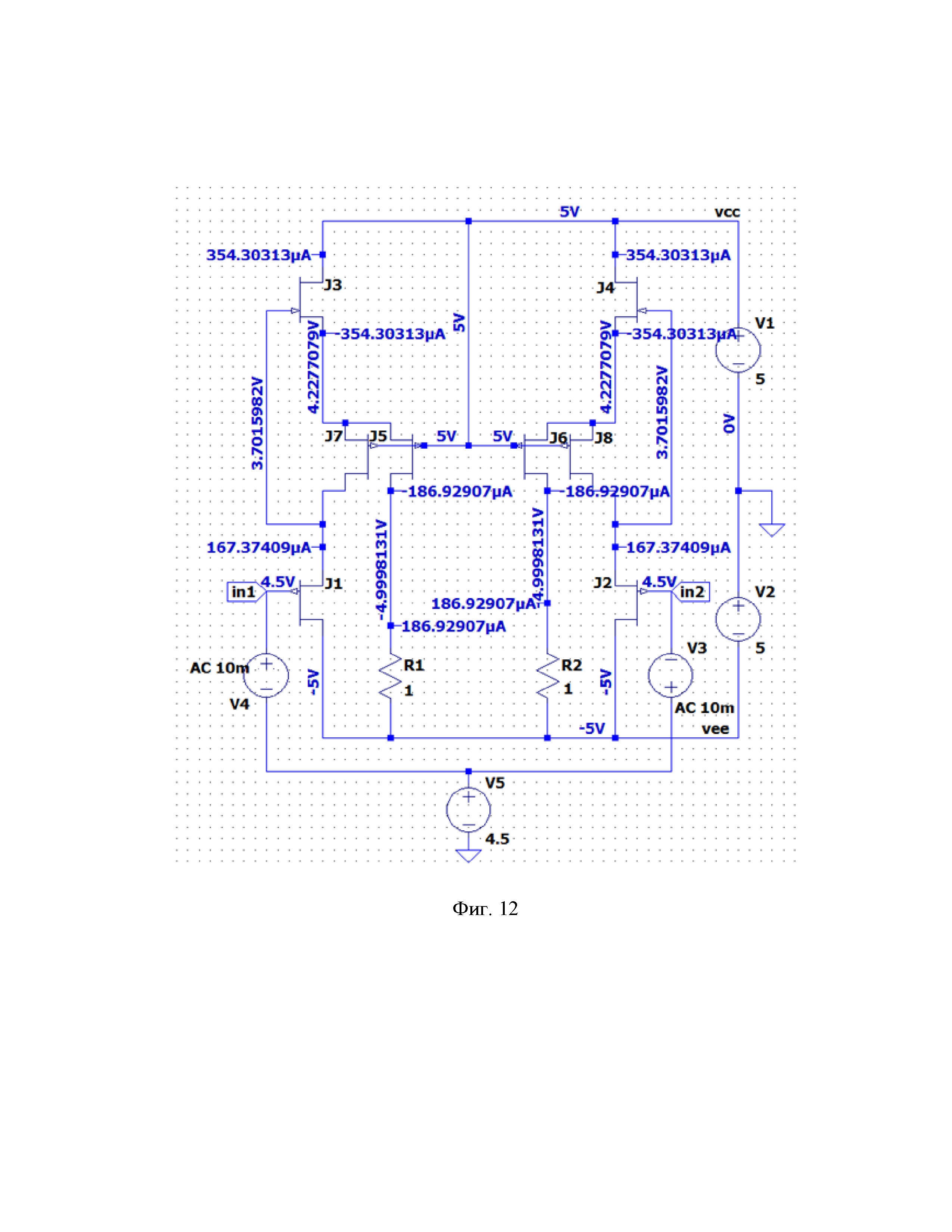

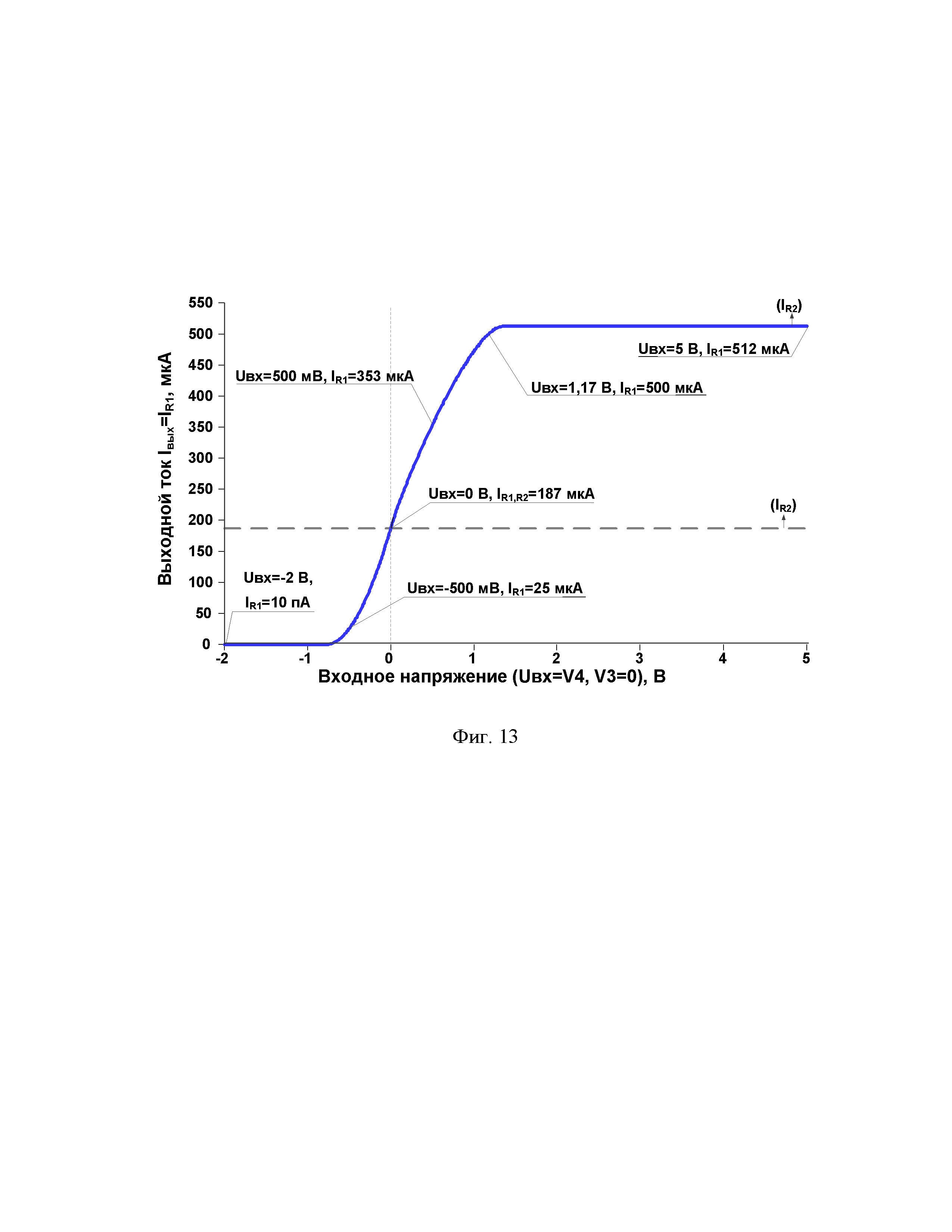

На чертеже фиг. 12 приведен статический режим дифференциального каскада фиг. 7 на основе двух составных транзисторов фиг. 6 при смещении входов ДК (in.1, in.2) относительно общей шины на величину V5=4,5В и температуре -197 °C.

На чертеже фиг. 13 показана проходная характеристика дифференциального каскада фиг. 12 (Iвых.=f(Uвх)) при температуре -197°C.

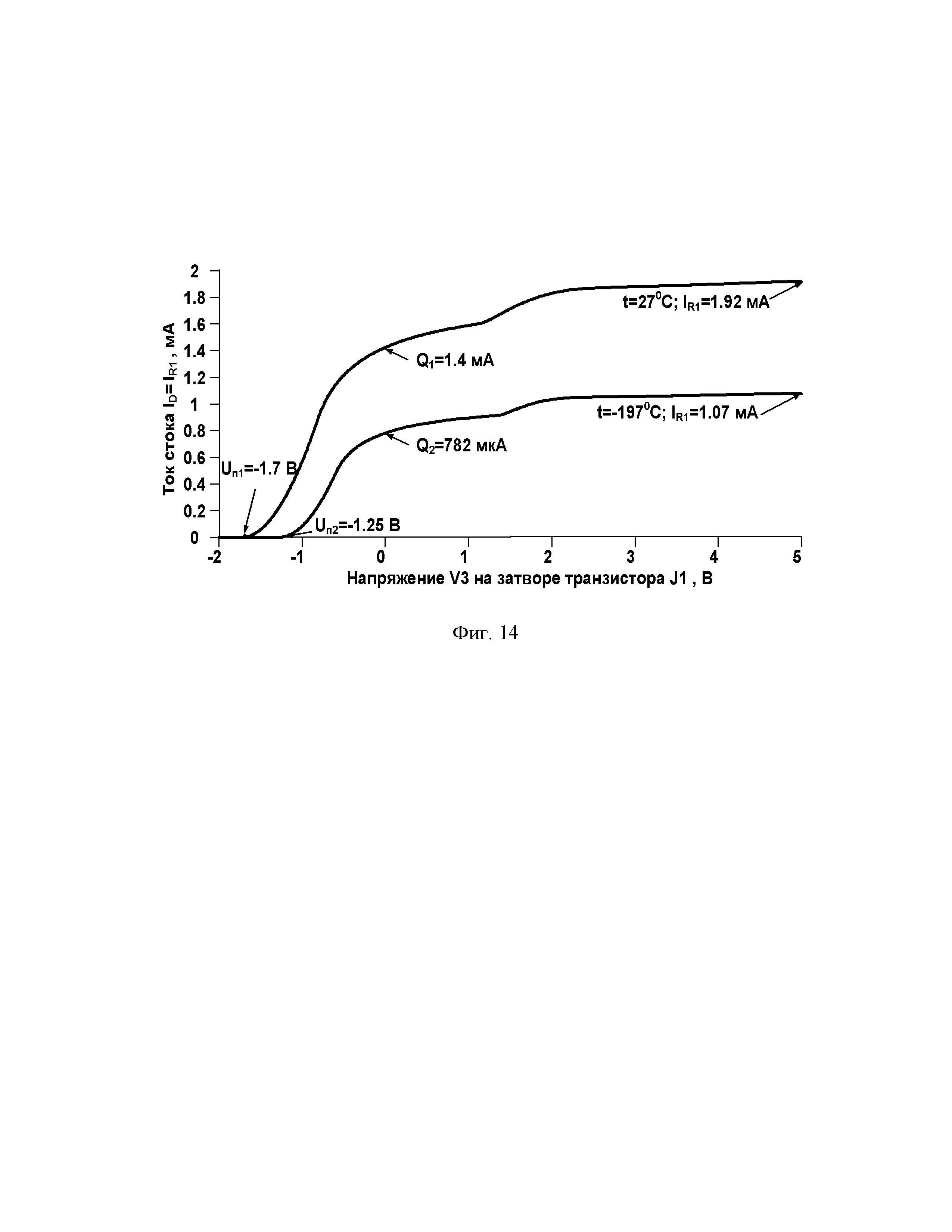

На чертеже фиг. 14 представлены стоко-затворные характеристики составного транзистора фиг. 8 в среде LTSpice при t=27°C, t=-197°C и напряжениях питания Eп=±5В.

Составной транзистор на основе комплементарных полевых транзисторов с управляющим p-n переходом фиг. 2, содержит затвор 1, исток 2 и сток 3 устройства, первый 4 полевой транзистор, затвор которого подключен к затвору 1 устройства, второй 5 полевой транзистор, сток которого соединен со стоком 3 устройства. Первый 4 полевой транзистор и второй 5 полевой транзистор имеют разные типы каналов. Сток первого 4 полевого транзистора соединен с истоком 2 устройства, его исток связан с истоком второго 5 полевого транзистора, а затвор второго 5 полевого транзисторов соединен с истоком 2 устройства. Таким образом, СТ фиг. 2 является трехполюсником, к выводам которого (затвору 1, истоку 2 и стоку 3 устройства) могут подключатся различные пассивные элементы (резисторы, конденсаторы и т.п.), которые совместно с СТ образуют конкретную электронную схему на основе заявляемого СТ.

На чертеже фиг. 2, в соответствии с п. 2 формулы изобретения, исток 2 устройства непосредственно связан с первой 6 шиной источника питания, а сток 3 устройства соединен со второй 7 шиной источника питания через первый 8 двухполюсник нагрузки.

На чертеже фиг. 3, в соответствии с п. 3 формулы изобретения, исток 2 устройства связан с первой 6 шиной источника питания через второй 9 двухполюсник нагрузки, причем первый 4 полевой транзистор имеет n-канал, а второй 5 полевой транзистор – p-канал.

На чертеже фиг. 4 представлена схема СТ, которая также соответствует п. 3 формулы изобретения для случая, когда первый 4 полевой транзистор имеет p-канал, а второй 5 полевой транзистор – n-канал.

На чертеже фиг. 5, в соответствии с п. 4 формулы изобретения, затвор второго 5 полевого транзистора соединен с истоком 2 устройства через цепь согласования потенциалов 10.

На чертеже фиг. 5, в соответствии с п. 5 формулы изобретения, цепь согласования потенциалов 10 содержит первый 11 дополнительный полевой транзистор и первый 12 дополнительный токостабилизирующий двухполюсник, причем затвор первого 11 дополнительного полевого транзистора соединен с истоком 2 устройства, его исток подключен к затвору второго 5 полевого транзистора и через первый 12 дополнительный токостабилизирующий двухполюсник связан с первой 6 шиной источника питания, а сток первого 11 дополнительного полевого транзистора связан со второй 7 шиной источника питания.

На чертеже фиг. 6 в соответствии с п. 6 формулы изобретения, заявляемый СТ снабжен первым дополнительным затвором 13, который соединен с затвором первого 14 вспомогательного полевого транзистора, причем исток первого 14 вспомогательного полевого транзистора соединен с затвором 1 устройства и стоком второго 15 вспомогательного полевого транзистора, сток первого 14 вспомогательного полевого транзистора связан со второй 7 шиной источника питания, исток второго 15 вспомогательного полевого транзистора подключён к истоку второго 5 полевого транзистора, а его затвор соединен с затвором второго 5 полевого транзистора.

На чертеже фиг. 7, в качестве примера, приведена схема включения заявляемого СТ фиг. 6 по п. 6 формулы изобретения в структуре дифференциального каскада, усиливающего разность двух входных напряжений uвх.13 и uвх.13*, смещенных относительно общей шины на V5=4,5В.

На чертеже фиг. 8, показан составной транзистор в соответствии с п. 7 формулы изобретения, который снабжен вторым 15 дополнительным затвором. Этот затвор соединен с затвором третьего 16 вспомогательного полевого транзистора, исток которого соединен с истоком 2 устройства, а его сток связан с дополнительным 17 стоком устройства. В данной схеме включения СТ сток 3 устройства связан со второй 7 шиной источника питания через первый 8 двухполюсник нагрузки, а дополнительный сток 17 устройства связан с первой 6 шиной источника питания через второй 18 дополнительный двухполюсник нагрузки. В частных случаях в качестве двухполюсников нагрузки 8 и 18 могут использоваться входы токовых зеркал, обеспечивающие дальнейшее преобразования сигналов в схеме ДК фиг. 8.

Работу предлагаемого составного транзистора фиг. 2 поясняют его стоко-затворные характеристики, представленные на чертежах фиг. 10, фиг. 11. Данные графики показывают, что СТ фиг. 2 по своим стоко-затворным характеристикам подобен КМОП полевому транзистору с индуцированным каналом. Он имеет характерную зону закрытого состояния при напряжении на затворе U0G, не превышающем пороговое напряжение (Uп), а при напряжении на эквивалентном затворе 1 устройства, превышающем Uп, переходит в активный режим. Таким образом, СТ фиг. 2 может использоваться в задачах аналогового усиления сигналов при управлении напряжением на эквивалентном затворе 1 устройства относительно общей шины. При этом относительно эквивалентного вывода стока 3 СТ (высокоинпедансного токового выхода) сигнал в заявляемом устройстве не инвертируется, что является его существенным преимуществом.

Введение второго 9 двухполюсника нагрузки (резистора) в схему включения заявляемого СТ фиг. 3 значительно расширяет его функциональные возможности. Схема СТ фиг. 3 работоспособна при сопротивлениях второго 9 двухполюсника нагрузки (резистора), не превышающих сумму сопротивлений истоков первого 4 и второго 5 полевых транзисторов.

Для управления величиной порогового напряжения Uп заявляемого СТ может использоваться цепь согласования потенциалов 10 (фиг. 5). При её применении можно изменять численные значения порогового напряжения Uп в широких пределах.

Введение в схему фиг. 6 первого 14 и второго 15 вспомогательных полевых транзисторов (в соответствии с п. 6 формулы изобретения) позволяет создавать на базе заявляемого СТ неинвертирующие преобразователи «входное напряжение-ток стока 3 устройства». При этом, управление СТ осуществляется по дополнительному затвору 13, имеющее высокой входное сопротивление.

Пример включения схемы СТ фиг. 6 в структуре дифференциального каскада на основе двух СТ фиг. 6 представлен на чертеже фиг. 7, а его характеристики приведены на чертеже фиг. 14.

Анализ статического режима СТ в схеме фиг. 9 показывает, что при нулевом напряжении U0G на затворе 1 устройства (J1, фиг. 9), транзисторы J1 и J2 заперты. Увеличение управляющего входного напряжения U0G на затворе 1 (J1) устройства (фиг. 10) выше порогового уровня Uп1≈1,8В приводит к переходу транзисторов J1 и J2 в активный режим, который может использоваться в различных усилительных схемах.

Воздействие криогенных температур несколько увеличивает пороговое напряжение (фиг. 10).

При параллельном включении четырех JFet транзисторов в структуре J1 и J2 фиг. 9 (или изменении ширины их каналов) пороговое напряжение Uп практически не изменяется (фиг. 11). Однако при этом возрастают максимальные токи СТ. Такое схемотехническое решение позволяет использовать заявляемое устройство при больших заданных токах нагрузки.

Существует более 20 других вариантов практического применения заявляемого СТ фиг. 2.

Так, на чертеже фиг. 8 представлен составной транзистор, соответствующий п. 7 формулы изобретения, в котором предусмотрены второй 15 дополнительный затвор (G*) и дополнительный сток 17 (D*) устройства. Структура СТ фиг. 8 позволяет управлять токами стоков ID и ID* и токами в первом 8 и втором 18 дополнительном двухполюсниках нагрузки не только путем изменения напряжения U0G, но и за счет управления величиной U0G* на дополнительном затворе 15, при этом обеспечивается высокие входные сопротивления.

По существу схема фиг. 8 является дифференциальным каскадом (ДК), усиливающим (относительно первого 8 и второго 18 дополнительного двухполюсников нагрузки), разность напряжений U0G и U0G* и подавляющим их синфазную составляющую. При этом, статический режим такого ДК (когда U0G=U0G*=0), устанавливается за счет геометрической размеров канала применяемых полевых транзисторов, то есть конструктивно-технологическим путем.

Графики фиг. 14 показывают, что рабочая точка по току (Q1) СТ фиг. 8 для JFet ОАО «Интеграл» (г. Минск) лежит в приделах нескольких сотен микроампер, а СТ фиг. 8 подобен КМОП транзистору со встроенным каналом, у которого ток стока не равен нулю при нулевом напряжении за затворе. В этой схеме ДК входное дифференциальное напряжение может принимать как положительное, так и отрицательное значение отновительно общей шины питания. При этом, каких-либо дополнительных устройств смещения статического режима ДК не требуется, что является его важным достоинством.

Компьютерное моделирование характеристик, рассмотренных СТ выполнялось в среде САПР LTSpice XVII (Analog Device, США) на моделях СJFet транзисторов (ОАО «Интеграл» (г. Минск), АО «НПП» Пульсар» (г. Москва), учитывающих влияние низких температур и проникающей радиации [10].

Таким образом, заявляемый СТ существенно расширяет представления разработчиков аналоговых CJFet микросхем о методах построения усилительных трехполюсников (составных транзисторов), которые, в отличие от известных JFet СТ, характеризуются новыми качествами и позволяют создавать нетрадиционные CJFet аналоговые микросхемы с улучшенными параметрами.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 5.065.043, 1991 г. прототип

2. Патент US 5.422.563, 1995 г.

3. Патент EP 0 854 570, 2001 г.

4. Патент US 4.291.316, 1980 г.

5. Патент US 4.422.563, 1995 г.

6. Патент US 5.008.565, 1991 г.

7. Схемотехника биполярно-полевых аналоговых микросхем. Часть 6. Составные схемы включения биполярных и полевых транзисторов / О.В. Дворников // Chip News #6(99) Аналоговая схемотехника, 2005г., С. 42-49. Fig. 6, Fig. 7, Fig. 8, Fig. 12, Fig. 13, Fig. 14.

8. Основы микросхемотехники: учеб. пособие для студ. вузов / А.Г. Алексеенко. 3-е изд. М.: ЛБЗ; М.: Физматлит; М. : ЮНИМЕДИАСТАЙЛ, 2002. 448с. Fig. 2.26, Fig. 2.27

9. Элементная база радиационно-стойких информационно-измерительных систем: монография / Н.Н. Прокопенко, О.В. Дворников, С.Г. Крутчинский; под общ. ред. д.т.н. проф. Н.Н. Прокопенко; ФГБОУ ВПО «Южно-Рос. гос. ун-т экономики и сервиса». - Шахты: ФГБОУ ВПО «ЮРГУЭС», 2011. - 208 с.

10. O. V. Dvornikov, V. L. Dziatlau, N. N. Prokopenko, K. O. Petrosiants, N. V. Kozhukhov and V. A. Tchekhovski. The accounting of the simultaneous exposure of the low temperatures and the penetrating radiation at the circuit simulation of the BiJFET analog interfaces of the sensors // 2017 International Siberian Conference on Control and Communications (SIBCON), Astana, Kazakhstan, 2017, pp. 1-6. DOI: 10.1109/SIBCON.2017.7998507

11. Патент RU 2519563, 2014 г.

12. Патент RU 2536672, 2014 г.