Результат интеллектуальной деятельности: Триггерный синхронный D триггер

Вид РИД

Изобретение

Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Оно, в частности, может быть применено в блоках вычислительной техники, выполненных с использованием D триггеров.

Известен синхронный D триггер. [1-Манаев Е.И. Основы радиоэлектроники. − М.: Радио и связь, 1985, с. 355, рис. 14.42], содержащий с учётом [1, c. 353, рис. 14.40] пять логических элементов.

Недостатком его является большое число используемых транзисторов, что усложняет и удорожает устройство. В частности, в каждом двухвходовом транзисторно-транзисторном логическом элементе И-НЕ [1, с. 340, рис. 14.22, б] имеется четыре транзистора, и один диод, тогда в обсуждаемом синхронном D триггере содержится большое число транзисторов (двадцать), что приводит к его усложнению и удорожанию.

Наиболее близким по технической сущности и достигаемому результату является выбранный в качестве прототипа триггер с дополнительной симметрией [Гольденберг Л.М., Импульсные и цифровые устройства. − М.: Связь, 1973, стр. 275, рис. 4.18, в], содержащий два транзистора, четыре резистора и три источника постоянных питающих напряжений.

Недостаток его заключается в том, что у него малая нагрузочная способность, т.к. относительно небольшая часть электрического тока, потребляемого от источника постоянного питающего напряжения, образует электрический ток внешней нагрузки. Это объясняется тем, что одну внешнюю нагрузку в рассматриваемой схеме можно подключать к коллектору или к эмиттеру только одного из двух имеющихся транзисторов. Если бы в формировании электрического тока внешней нагрузки участвовали оба имеющихся транзистора, то это повысило бы нагрузочную способность триггера.

Задача, на решение которой направлено изобретение, состоит в упрощении и удишевлении триггерного синхронного D триггера.

Это достигается тем, что в триггерный синхронный D триггер, содержащий источник питающего постоянного напряжения, общая шина которого заземлена, последовательно соединённые первый резистор, первый транзистор (n-p-n) и второй резистор, свободный вывод первого резистора соединён с выходом источника питающего постоянного напряжения, другой вывод этого резистора соединён с коллектором первого транзистора, также имеются последовательно соединённые третий резистор, второй транзистор (p-n-p) и четвёртый резистор, свободный вывод третьего резистора подключен к общему выводу выхода источника питающего постоянного напряжения и первого резистора, другой вывод третьего резистора соединён с эмиттером второго транзистора, а база соединена с общим выводом первого резистора и коллектора первого транзистора, база первого транзистора подключена к общему выводу коллектора второго транзистора и четвёртого резистора, свободный вывод последнего резистора подключён к свободному выводу второго резистора, введены пять дополнительных транзисторов и четыре дополнительных резистора, один из выводов первого дополнительного резистора подсоединён к выходу источника питающего постоянного напряжения, а другой - к эмиттеру первого дополнительного транзистора (p-n-p), база которого соединена с базой второго дополнительного транзистора (n-p-n), вывод эмиттера этого второго дополнительного транзистора образует вход D относительно «земли» синхронного триггера, последовательно между собой включены третий дополнительный транзистор (n-p-n), второй дополнительный резистор и четвертый дополнительный транзистор (n-p-n), база третьего дополнительного транзистора соединена с коллектором второго дополнительного транзистора, а коллектор - с общим выводом первого резистора и коллектора первого транзистора, эмиттер четвертого дополнительного транзистора заземлён, а вывод его базы образует относительно «земли» вход синхронизации (вход С) синхронного триггера, также последовательно между собой включены пятый дополнительный транзистор (n-p-n) и третий дополнительный резистор, база пятого дополнительного транзистора соединена с коллектором первого дополнительного транзистора, а его коллектор - с общим выводом третьего резистора и эмиттера второго транзистора, свободный выводом третьего дополнительного резистора подключен к общему выводу второго дополнительного резистора и коллектора четвёртого дополнительного транзистора, четвёртый дополнительный резистор включен между «землей» и общим выводом второго и четвёртого резисторов, общий вывод второго, четвёртого и четвёртого дополнительного резисторов образует относительно «земли» выход (Q) синхронного триггера.

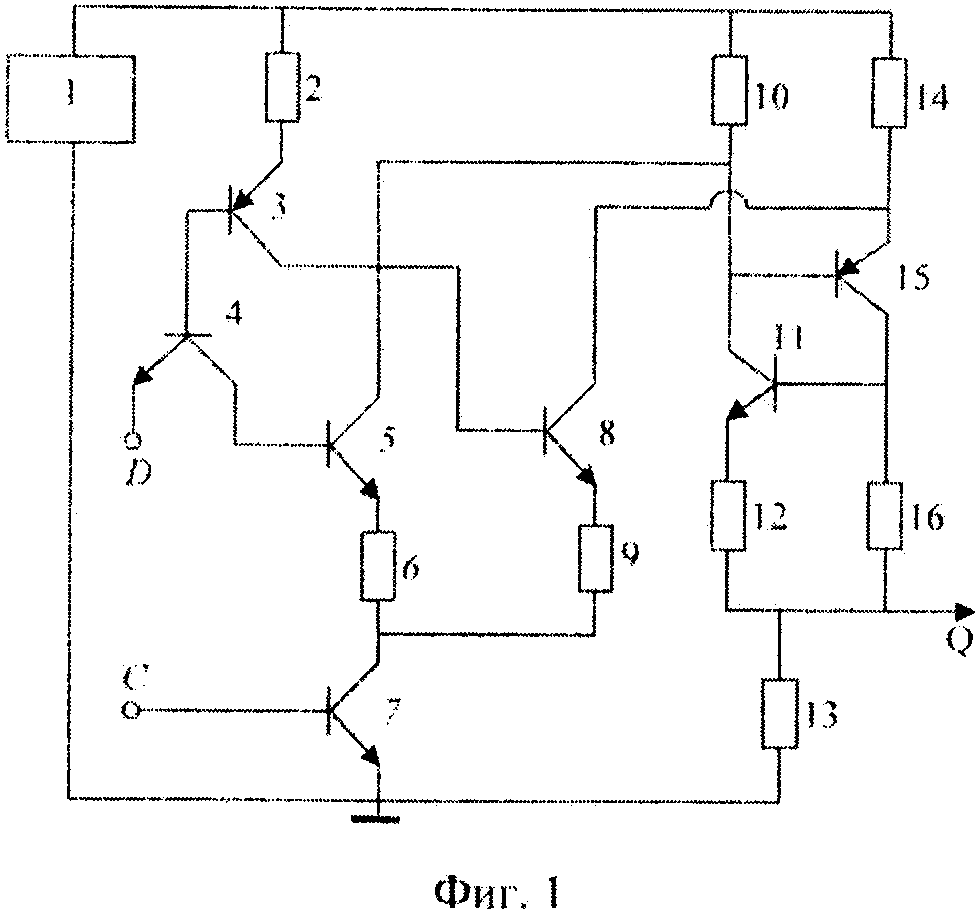

Сущность изобретения поясняется чертежом (фиг. 1).

В триггерном синхронном D триггере общая шина источника 1 питающего постоянного напряжения заземлена. Один из выводов резистора 2 подсоединён к выходу источника 1 , а другой - к эмиттеру p-n-p транзистора 3, база которого соединена с базой n-p-n транзистора 4, а эмиттер последнего транзистора образует вход D относительно «земли» синхронного триггера. Последовательно между собой включены n-p-n транзистор 5, резистор 6 и n-p-n транзистор 7. База транзистора 5 соединена с коллектором транзистора 4, а эмиттер транзистора 7 заземлён. Вывод базы последнего транзистора образует относительно «земли» вход синхронизации С синхронного триггера. Также последовательно включены n-p-n транзистора 8 и резистор 9. База транзистора 8 подсоединена к коллектору транзистора 3, а свободный резистора 9 - к общему выводу резистора 6 и коллектора транзистора 7. Последовательно между собой включены резистор 10, n-p-n транзистор 11, резисторы 12 и 13. Свободный вывод резистора 10 подсоединён к общему выводу резистора 2 и выхода источника 1. Общий вывод резистора 10 и коллектора транзистора 11 соединён с коллектором транзистора 5, а свободный вывод резистора 13 заземлён. И, наконец, последовательно включены резистор 14, p-n-p транзистор 15 и резистор 16. Свободный вывод резистора 14 подсоединён к общему выводу резисторов 2, 10 и выхода источника 1. Общий вывод резистора 14 и эмиттера транзистора 15 подключен к коллектору транзистора 8. База транзистора 15 соединена с общим выводом резистора 10, коллектора транзистора 5 и коллектора транзистора 11. Общий вывод коллектора транзистора 15 и резистора 16 подсоединён к базе транзистора 11. Свободный вывод резистора 16 соединён с общим выводом резисторов 12, 13 и общий вывод этих резисторов 12, 13 и 16 образует выход Q относительно «земли» синхронного триггера. Часть приведённой на фиг. 1 схемы на транзисторах 11, 15 и резисторах 10, 12, 14 и 16 является триггером на транзисторах противоположного типа проводимости.

Триггерный синхронный D триггер работает следующим образом. В цифровой электронике используются входные и выходные электрические сигналы низкого и высокого уровней. Низкий уровень − уровень логического нуля соответствует значениям напряжения в районе нуля или в районе ближе к нулю, высокий уровень − уровень логической единицы соответствует значениям напряжения в районе единиц вольт (нередко в районе четырех вольт).

|

Работа синхронного D триггера отображается известной табл.1, где N − номер строки по порядку,  − условное отображение входного сигнала в данный момент времени

− условное отображение входного сигнала в данный момент времени  и

и  − условное отображение выходного сигнала триггера в последующее время (состояние на выходе). Приведённая табл. 1 справедлива только при наличии сигнала синхронизации С-1 (импульса синхронизации). При его отсутствии табл. 1 не справедлива, состояние D триггера не изменяется, оно останется неизменным вне зависимости от сигнала на входе D (0 или 1), кратко говоря, триггер в этом случае не работает, а по сути в нём хранится имевшаяся ранее информация (0 или 1 на выходе Q).

− условное отображение выходного сигнала триггера в последующее время (состояние на выходе). Приведённая табл. 1 справедлива только при наличии сигнала синхронизации С-1 (импульса синхронизации). При его отсутствии табл. 1 не справедлива, состояние D триггера не изменяется, оно останется неизменным вне зависимости от сигнала на входе D (0 или 1), кратко говоря, триггер в этом случае не работает, а по сути в нём хранится имевшаяся ранее информация (0 или 1 на выходе Q).

Триггер на транзисторах 11, 15 противоположного типа проводимости имеет два состояния равновесия. В первом (условно) состоянии оба транзистора закрыты и не проводят электрический ток. Тогда в том числе на резисторах 10 и 16 нулевые значения напряжения. Они прикладываются к базам транзисторов 11, 15 меньше пороговых напряжений транзисторов по абсолютной величине и в итоге поддерживают эти транзисторы в закрытом состоянии. Во втором (условно) состоянии транзисторы 11 и 15 открыты, их электрические токи создают напряжения в том числе на резисторах 10 и 16 больше по значениям пороговых напряжений транзисторов по абсолютной величине и поддерживают транзисторы 11, 15 в открытом состоянии. Триггер на транзисторах противоположного типа проводимости, как и другие распространённые триггеры, переходит из первого состояния во второе и наоборот, когда управляющие входные напряжения по своим значениям превышают значения напряжений соответствующих порогов срабатывания триггера.

При наличии сигнала синхронизации С-1 транзистор 7 открыт и проводит электрический ток. В соответствии с первой строкой табл. 1 высокий уровень напряжения на входе D предопределяет пониженные значения и напряжения, и силы электрического тока базы транзистора 3. Последнее вызывает пониженные значения силы электрических токов коллектора транзистора 3, базы и коллектора транзистора 8. Ток транзистора 8 создает на резисторе 14 соответственно пониженное значение напряжения, которое меньше напряжения порога срабатывания триггера на транзисторах 11, 15 противоположного типа проводимости и не влияет на его состояние. Электрический ток транзистора 8 замыкается на «землю» через открытый транзистор 7. Базо-коллекторный p-n переход транзистора 4 открыт и через него на базу транзистора 5 поступает высокий уровень напряжения со входа D. Это определяет повышенные значения силы электрических токов базы и коллектора транзистора 5, что вызывает повышенное значение напряжения на резисторе 10. Последнее больше значения порогового напряжения срабатывания триггера на транзисторах 11, 15 и переводит его во второе состояние. Тогда электрические токи транзисторов 11 и 15 создают на выходе Q повышенное значение напряжения - уровень логической единицы. Электрический ток транзистора 5 замыкается на «землю» через открытый транзистор 7.

В соответствии со второй строкой табл. 1 низкий уровень напряжения на входе D предопределяет низкий уровень напряжения на базе транзистора 4 относительно «земли», т.к. базо-эмиттерный p-n переход транзистора 4 открыт. Это вызывает высокий уровень напряжения между выходом источника 1 и базами транзисторов 3 и 4, а также низкий уровень напряжения между базой и «землей» транзистора 5. Последнее приводит к пониженным значениям силы тока транзистора 5 и напряжения на резисторе 10. Значение напряжения на резисторе 10 меньше значения порогового напряжения срабатывания триггера на транзисторах 11, 15 противоположного типа проводимости и не влияет на его состояние. Повышенное значение напряжения между выходом источника 1 и общим выводом баз транзисторов 4 и 3 определяет повышенное значение сил электрических токов базы транзистора 3, коллектора этого транзистора, базы и коллектора транзистора 8. Электрический ток транзистора 8 замыкается через открытый транзистор 7, его повышенное значение создает на резисторе 14 повышенное значение напряжения. Оно превышает значение напряжения порога срабатывания триггера на транзисторах 11, 15 и переводит его в первое состояние. Тогда нулевые значения силы электрических токов транзисторов 11, 15 создают на выходе Q синхронного триггера напряжение уровня логического нуля.

При отсутствии сигнала синхронизации С-0 транзистор 7 закрыт и тем самым разорвана цепь прохождения электрического тока и транзистора 5, и транзистора 8 при любых значениях сигналов на входе D. Тогда на резисторах 10, 16 не могут появится напряжения по значениям превышающие пороговые напряжения срабатывания триггера на транзисторах 11, 15. В итоге состояние этого триггера не изменяется и соответственно не изменяется напряжение на выходе Q синхронного D триггера.

Таким образом, рассмотренная схема упрощает и удишевляет синхронный D триггер. В ней семь транзисторов, а, в частности, в приведенном выше аналоге имеется двадцать транзисторов.

Триггерный синхронный D триггер, содержащий источник питающего постоянного напряжения, общая шина которого заземлена, последовательно соединённые первый резистор, первый транзистор (n-p-n) и второй резистор, свободный вывод первого резистора соединён с выходом источника питающего постоянного напряжения, другой вывод этого резистора соединён с коллектором первого транзистора, также имеются последовательно соединённые третий резистор, второй транзистор (p-n-p) и четвёртый резистор, свободный вывод третьего резистора подключен к общему выводу выхода источника питающего постоянного напряжения и первого резистора, другой вывод третьего резистора соединён с эмиттером второго транзистора, а база соединена с общим выводом первого резистора и коллектора первого транзистора, база первого транзистора подключена к общему выводу коллектора второго транзистора и четвёртого резистора, свободный вывод последнего резистора подключён к свободному выводу второго резистора, отличающийся тем, что в него введены пять дополнительных транзисторов и четыре дополнительных резистора, один из выводов первого дополнительного резистора подсоединён к выходу источника питающего постоянного напряжения, а другой - к эмиттеру первого дополнительного транзистора (p-n-p), база которого соединена с базой второго дополнительного транзистора (n-p-n), вывод эмиттера этого второго дополнительного транзистора образует вход D относительно «земли» синхронного триггера, последовательно между собой включены третий дополнительный транзистор (n-p-n), второй дополнительный резистор и четвертый дополнительный транзистор (n-p-n), база третьего дополнительного транзистора соединена с коллектором второго дополнительного транзистора, а коллектор - с общим выводом первого резистора и коллектора первого транзистора, эмиттер четвертого дополнительного транзистора заземлён, а вывод его базы образует относительно «земли» вход синхронизации (вход С) синхронного триггера, также последовательно между собой включены пятый дополнительный транзистор (n-p-n) и третий дополнительный резистор, база пятого дополнительного транзистора соединена с коллектором первого дополнительного транзистора, а его коллектор - с общим выводом третьего резистора и эмиттера второго транзистора, свободный вывод третьего дополнительного резистора подключен к общему выводу второго дополнительного резистора и коллектора четвёртого дополнительного транзистора, четвёртый дополнительный резистор включен между «землей» и общим выводом второго и четвёртого резисторов, общий вывод второго, четвёртого и четвёртого дополнительного резисторов образует относительно «земли» выход (Q) синхронного триггера.