Результат интеллектуальной деятельности: ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО

Вид РИД

Изобретение

Изобретение относится к вычислительной технике и может быть использовано для вычисления систем логических функций в программируемых логических интегральных схемах (ПЛИС).

Известно программируемое логическое устройство, содержащее первую, вторую и третью группы D-триггеров количеством по m⋅2n (n - число входных переменных, m - число выходных функций), третью группу D-триггеров количеством 2(n-1)m, группу m(n-1) элементов И, счетчик, группу m⋅2n элементов И с тремя состояниями на выходе, дешифратор, группу m(n-1) элементов ИЛИ, вторую группу m⋅2n элементов И с тремя состояниями на выходе и m блоков вычисления функций, каждый блок вычисления функций содержит группу 4⋅2n элементов И с тремя состояниями на выходе, два D-триггера, Т-триггер, RS-триггер фиксации импульса, пять элементов ИЛИ, три элемента И, четыре инвертора, n групп элементов 2⋅2 НЕ-И-ИЛИ (в каждую i-ю группу входит 2n-1 элементов, i=1,n), элемент задержки, дополнительную группу элементов И с тремя состояниями на выходе (патент РФ №2146840 от 20.03.2000, кл. G11C 17/00, G06F 7/00).

Недостатком известного устройства являются высокие аппаратурные затраты, выраженные в количестве транзисторов, на реализацию логической функции в программируемых логических интегральных схемах (ПЛИС).

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является программируемое логическое устройство, содержащее группу из четырех инверторов четырех переменных, четыре группы передающих транзисторов по 2i, i=1,2,3,4 транзисторов в группе, группу из шестнадцати инверторов настройки, выходной инвертор, входы четырех переменных, шестнадцать входов настройки и выход устройства,

причем затвор каждого четного транзистора i-й группы из четырех групп передающих транзисторов подключен к i-му входу из четырех входов переменных, которые также подключены ко входам соответствующих четырех инверторов четырех переменных, затвор каждого нечетного транзистора i-й группы из четырех групп передающих транзисторов подключен к выходам соответствующих четырех инверторов четырех переменных, истоки транзисторов четвертой группы передающих транзисторов подключены к выходам соответствующих инверторов группы из шестнадцати инверторов настройки, входы которых подключены к соответствующим из шестнадцати входов настройки, стоки четных и нечетных шестнадцати передающих транзисторов четвертой группы объединены в восемь пар и подключены к истокам соответствующих восьми передающих транзисторов третьей группы, стоки четных и нечетных передающих транзисторов, в которой объединены в четыре пары и подключены к истокам соответствующих передающих транзисторов второй группы, стоки четных и нечетных передающих транзисторов в которой объединены в две пары и подключены к истокам соответствующих передающих транзисторов первой группы, стоки которых объединены и подключены ко входу выходного инвертора, выход которого подключен к выходу устройства (Строганов А., Цыбин С. Программируемая коммутация в ПЛИС: взгляд изнутри// Компоненты и технологии. - 2010. - №11. С. 56-62 Рис. 9,12 [Электронный ресурс]. - URL: http://www.kit-e.ru/articles/plis/2010_11_56.php 12.11.12 г). Данное устройство принято за прототип.

Признаки прототипа, совпадающие с существенными признаками заявляемого изобретения, - содержит группу из четырех инверторов четырех переменных, четыре группы передающих транзисторов по 2i, i=1,2,3,4 транзисторов в группе, группу из шестнадцати инверторов настройки, выходной инвертор, входы четырех переменных, шестнадцать входов настройки и выход устройства, причем затвор каждого четного транзистора i-й группы из четырех групп передающих транзисторов подключен к i-му входу из четырех входов переменных, которые также подключены ко входам соответствующих четырех инверторов четырех переменных, затвор каждого нечетного транзистора i-й группы из четырех групп передающих транзисторов подключен к выходам соответствующих четырех инверторов четырех переменных, истоки транзисторов четвертой группы передающих транзисторов подключены к выходам соответствующих инверторов группы из шестнадцати инверторов настройки, входы которых подключены к соответствующим из шестнадцати входов настройки, стоки четных и нечетных шестнадцати передающих транзисторов четвертой группы объединены в восемь пар и подключены к истокам соответствующих восьми передающих транзисторов третьей группы, стоки четных и нечетных передающих транзисторов, в которой объединены в четыре пары и подключены к истокам соответствующих передающих транзисторов второй группы, стоки четных и нечетных передающих транзисторов, в которой объединены в две пары и подключены к истокам соответствующих передающих транзисторов первой группы, стоки которых объединены и подключены ко входу выходного инвертора, выход которого подключен к выходу устройства.

Недостатком известного устройства, принятого за прототип, является невозможность реализации второй логической функции на неактивной половине групп передающих транзисторов. Это обусловлено следующими обстоятельствами. Технические средства прототипа ориентированы на реализацию в зависимости от настройки одной конкретной логической функции n переменных в совершенной дизъюнктивной нормальной форме (СДНФ). В связи с этим одна из двух половин четырех групп передающих транзисторов по 2i, i=1,2,3,4 транзисторов в группе на любом наборе переменных, подаваемых на входы переменных, всегда неактивна по старшей переменной, подаваемой на первый вход.

Задачей изобретения является реализация второй логической функции на неактивной половине четырех групп передающих транзисторов по 2i, i=1,2,3,4 транзисторов в группе.

Поставленная задача была решена за счет того, что в заявляемое устройство, содержащее группу из четырех инверторов четырех переменных, четыре группы передающих транзисторов по 2i, i=1,2,3,4 транзисторов в группе, группу из шестнадцати инверторов настройки, выходной инвертор, входы четырех переменных, шестнадцать входов настройки и выход устройства,

причем затвор каждого четного транзистора i-й группы из четырех групп передающих транзисторов подключен к i-му входу из четырех входов переменных, которые также подключены ко входам соответствующих четырех инверторов четырех переменных, затвор каждого нечетного транзистора i-й группы из четырех групп передающих транзисторов подключен к выходам соответствующих четырех инверторов четырех переменных, истоки транзисторов четвертой группы передающих транзисторов подключены к выходам соответствующих инверторов группы из шестнадцати инверторов настройки, входы которых подключены к соответствующим из шестнадцати входов настройки, стоки четных и нечетных шестнадцати передающих транзисторов четвертой группы объединены в восемь пар и подключены к истокам соответствующих восьми передающих транзисторов третьей группы, стоки четных и нечетных передающих транзисторов, в которой объединены в четыре пары и подключены к истокам соответствующих передающих транзисторов второй группы, стоки четных и нечетных передающих транзисторов, в которой объединены в две пары и подключены к истокам соответствующих передающих транзисторов первой группы, стоки которых объединены и подключены ко входу выходного инвертора, выход которого подключен к выходу устройства,

согласно изобретению дополнительно введены два дублирующих передающих транзистора первой группы, первая группа транзисторов отключения настройки, вторая группа транзисторов отключения настройки, вторая группа входов настройки, второй выходной инвертор, второй выход устройства, причем второй выход устройства подключен в выходу второго выходного инвертора, вход которого подключен к стокам двух дублирующих передающих транзисторов первой группы, исток первого из них подключен к истоку второго передающего транзистора первой группы передающих транзисторов, исток второго из них подключен к истоку первого передающего транзистора первой группы передающих транзисторов, затвор первого дублирующего передающего транзистора первой группы подключен к затвору первого передающего транзистора первой группы передающих транзисторов, затвор второго дублирующего передающего транзистора первой группы подключен к затвору второго передающего транзистора первой группы передающих транзисторов, истоки транзисторов первой группы транзисторов отключения настройки подключены ко входам соответствующих из шестнадцати входов настройки, а стоки транзисторов первой группы транзисторов отключения настройки подключены к стокам соответствующих из шестнадцати транзисторов второй группы транзисторов отключения настройки, истоки которых подключены к соответствующим входам второй группы входов настройки, затворы первой половины транзисторов из шестнадцати транзисторов второй группы транзисторов отключения настройки и второй половины из первой группы транзисторов отключения настройки подключены к выходу первого инвертора переменных, затворы второй половины транзисторов из шестнадцати транзисторов второй группы транзисторов отключения настройки и первой половины из первой группы транзисторов отключения настройки подключены к первому входу переменных.

Признаки заявляемого технического решения, отличительные от прототипа, - дополнительно введены два дублирующих передающих транзистора первой группы, первая группа транзисторов отключения настройки, вторая группа транзисторов отключения настройки, вторая группа входов настройки, второй выходной инвертор, второй выход устройства, второй выход устройства подключен в выходу второго выходного инвертора, вход которого подключен к стокам двух дублирующих передающих транзисторов первой группы, исток первого из них подключен к истоку второго передающего транзистора первой группы передающих транзисторов, исток второго из них подключен к истоку первого передающего транзистора первой группы передающих транзисторов, затвор первого дублирующего передающего транзистора первой группы подключен к затвору первого передающего транзистора первой группы передающих транзисторов, затвор второго дублирующего передающего транзистора первой группы подключен к затвору второго передающего транзистора первой группы передающих транзисторов, истоки транзисторов первой группы транзисторов отключения настройки подключены ко входам соответствующих из шестнадцати входов настройки, а стоки транзисторов первой группы транзисторов отключения настройки подключены к стокам соответствующих из шестнадцати транзисторов второй группы транзисторов отключения настройки, истоки которых подключены к соответствующим входам второй группы входов настройки, затворы первой половины транзисторов из шестнадцати транзисторов второй группы транзисторов отключения настройки и второй половины из первой группы транзисторов отключения настройки подключены к выходу первого инвертора переменных, затворы второй половины транзисторов из шестнадцати транзисторов второй группы транзисторов отключения настройки и первой половины из первой группы транзисторов отключения настройки подключены к первому входу переменных.

Отличительные признаки в сочетании с известными позволяют обеспечить повышение достоверности функционирования путем контроля правильности вычисления заданной логической функции в процессе работы за счет использования второй, незадействованной на данном наборе входных переменных половине передающих транзисторов.

Введение двух дублирующих передающих транзисторов первой группы и соответствующих связей позволяет использовать неактивную половину - второй, третьей и четвертой групп передающих транзисторов, для вычисления второй логической функции.

Введение первой и второй групп транзисторов отключения настройки и соответствующих связей позволяет подключать как входы настройки, так и дополнительные входы настройки к каждой из половин четырех групп передающих транзисторов к каждой из половин группы из шестнадцати инверторов настройки одновременно.

Введение второй группы входов настройки и соответствующих связей позволяет настраивать устройство на реализацию второй логической функции.

Введение второго выходного инвертора, соответствующего второго выхода устройства и соответствующих им связей позволяет формировать на нем значение второй логической функции, по сигналам, передаваемым со второй половины - второй, третьей и четвертой групп передающих транзисторов через соответствующий транзистор из двух дублирующих передающих транзисторов первой группы.

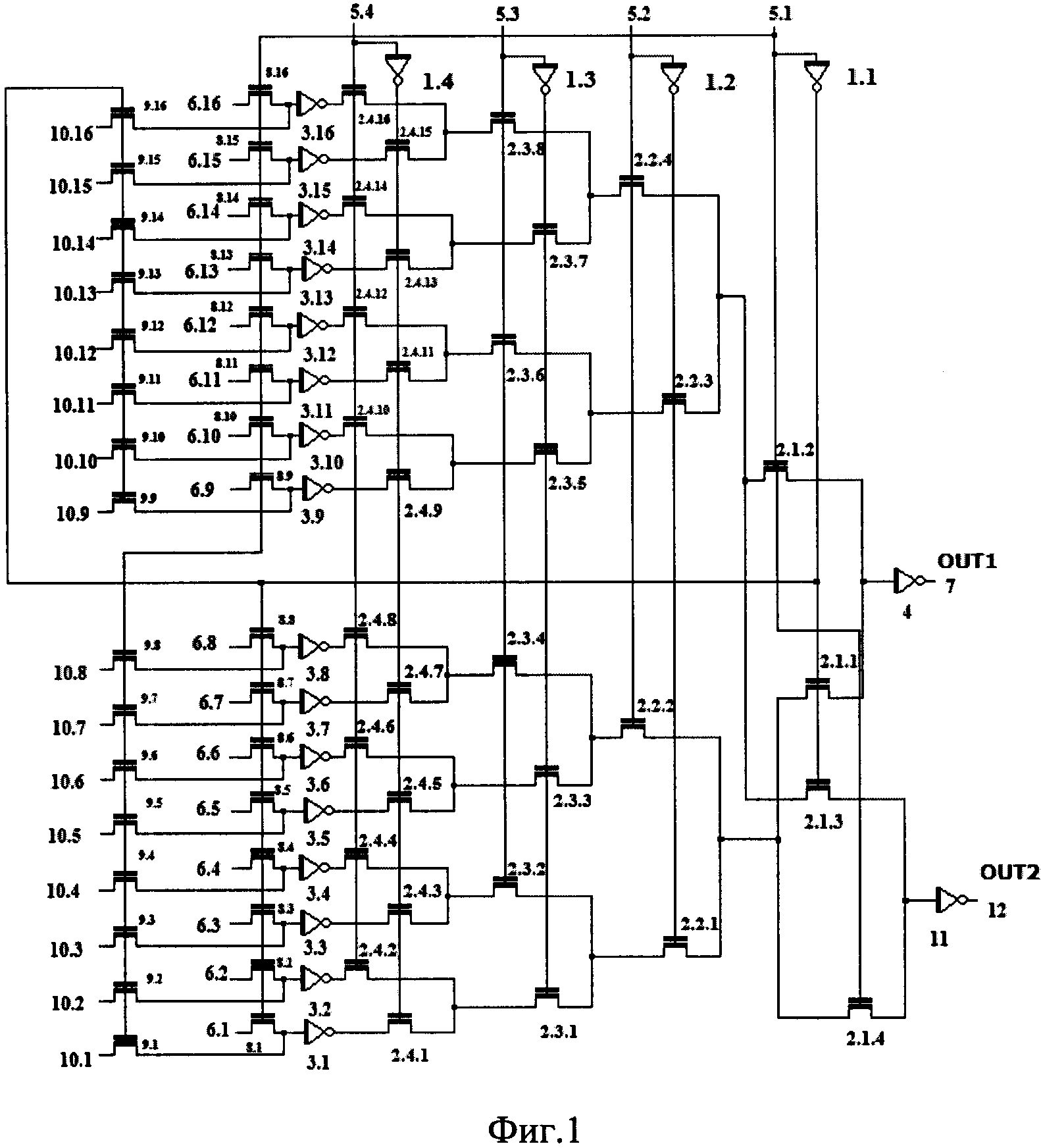

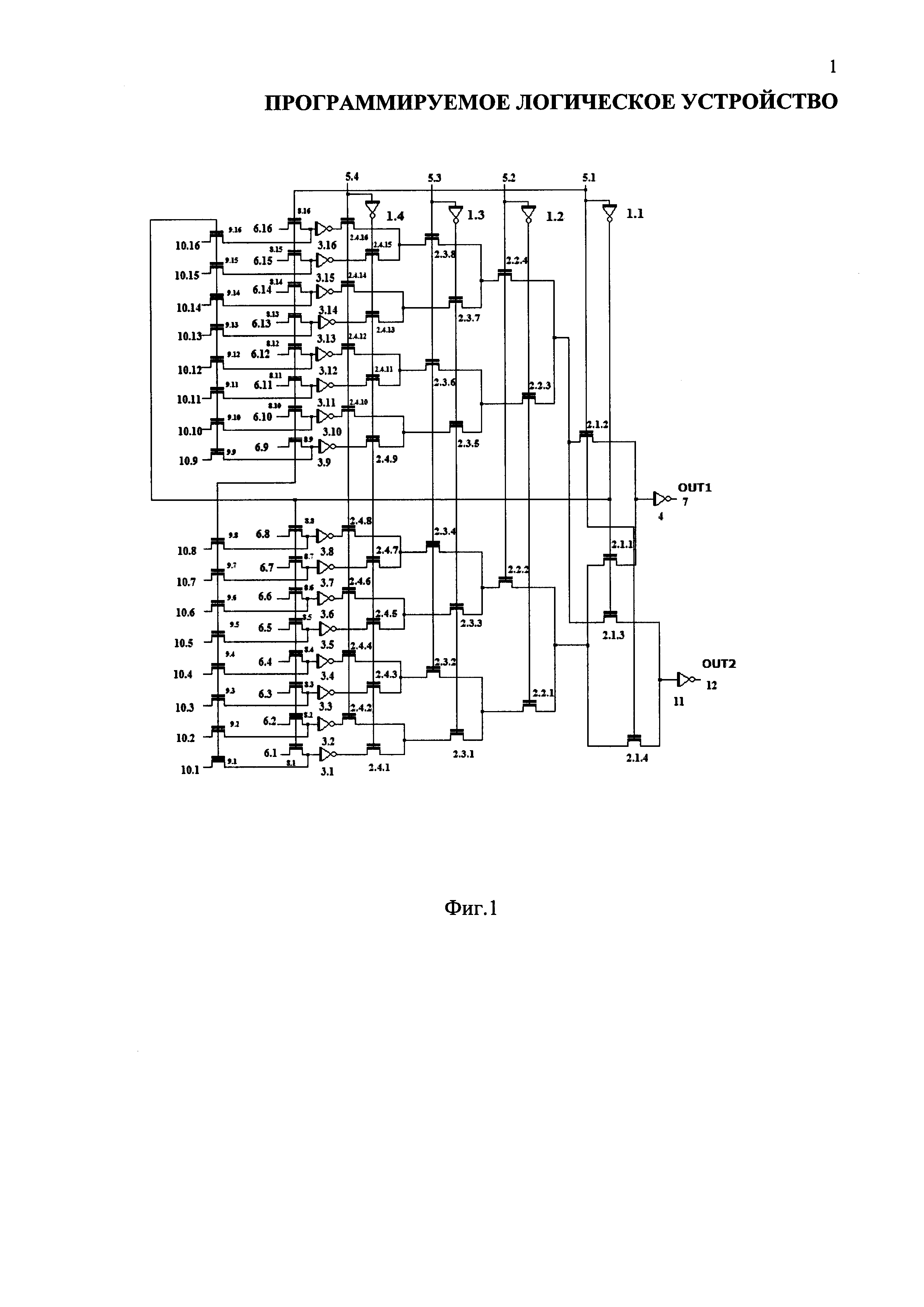

На фиг. 1 изображена схема электрическая принципиальная программируемого логического устройства.

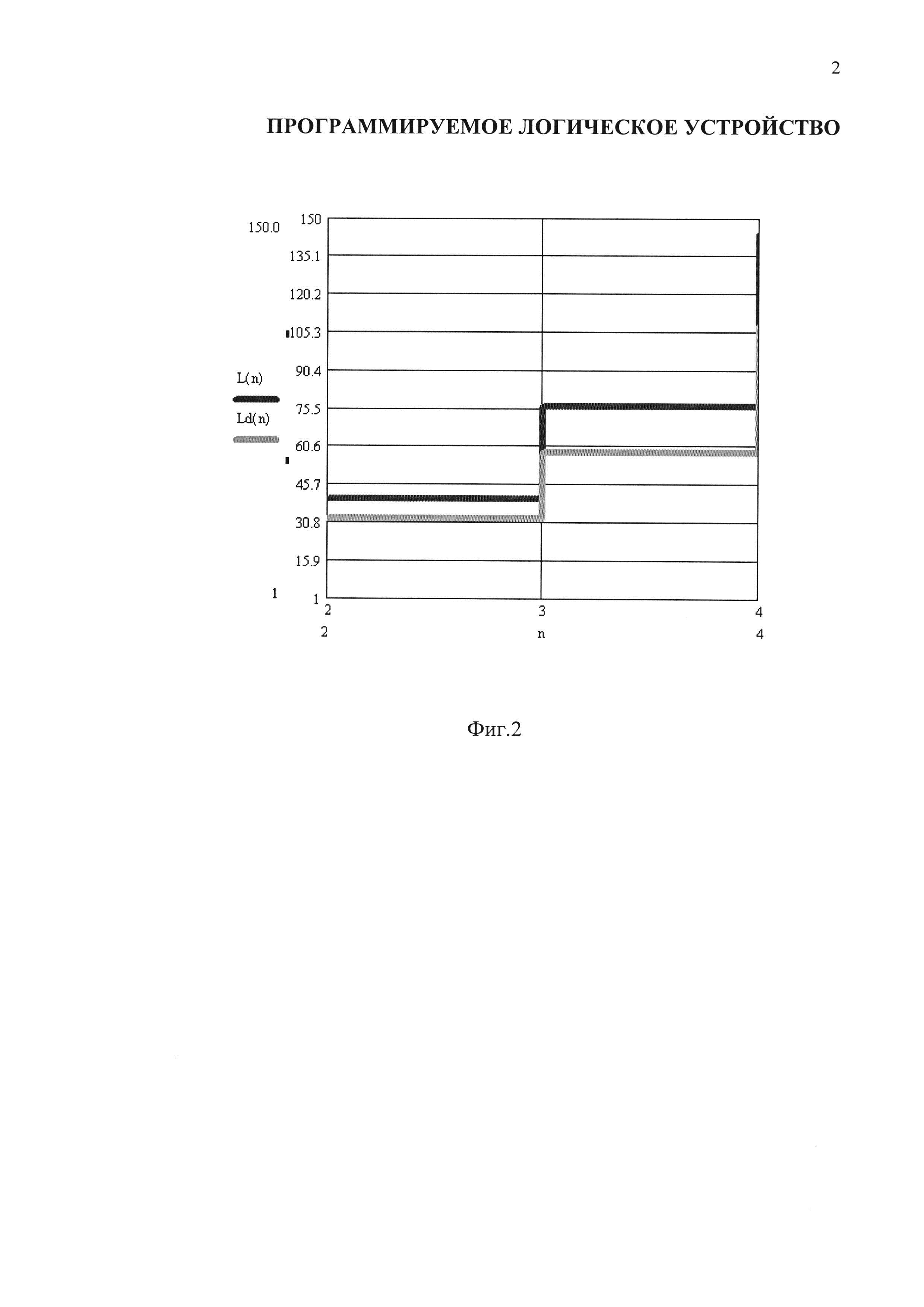

На фиг. 2 изображены графики изменения сложности реализации двух функций при использовании прототипа L(n) и предлагаемого устройства Ld(n) при n=4.

Программируемое логическое устройство (фиг. 1) содержит группу из четырех инверторов четырех переменных 1.1, 1.2, 1.3, 1.4, четыре группы 2 передающих транзисторов 2.1, 2.2, 2.3, 2.4 по 2i, i=1,2,3,4 транзисторов в группе; группу 3 из шестнадцати инверторов настройки 3.1, 3.2, 3.3, 3.4, 3.5, 3.6, 3.7, 3.8, 3.9, 3.10, 3.11, 3.12, 3.13, 3.14, 3.15, 3.16, выходной инвертор 4, входы четырех переменных 5, шестнадцать входов 6 настройки 6.1, 6.2, 6.3, 6.4, 6.5, 6.6, 6.7. 6.8, 6.9, 6.10, 6.11, 6.12, 6.13, 6.14,6.14, 6.15, 6.16; выход устройства 7, два дублирующих передающих транзистора первой группы 2.1.3, 2.1.4; первую группу транзисторов отключения настройки 8: 8.1, 8.2, 8.3, 8.4, 8.5, 8.6, 8.7, 8.8, 8.9, 8.10, 8.11, 8.12, 8.13, 8.14, 8.15, 8.16; вторую группу транзисторов отключения настройки 9: 9.1, 9.2, 9.3, 9.4, 9.5, 9.6, 9.7, 9.8, 9.9, 9.10, 9.11, 9.12, 9.13, 9.14, 9.15, 9.16; вторую группу входов настройки 10: 10.1, 10.2, 10.3, 10.4, 10.5, 10.6, 10.7. 10.8, 10.9, 10.10, 10.11, 10.12, 10.13, 10.14, 10.14, 10.15, 10.16; второй выходной инвертор 11, второй выход устройства 12.

Затвор каждого четного транзистора i-й группы из четырех групп передающих транзисторов 2 подключен к i-му входу из четырех входов переменных 5, которые также подключены ко входам соответствующих четырех инверторов четырех переменных 1.1, 1.2, 1.3,1.4.

Затвор каждого нечетного транзистора i-й группы из четырех групп передающих транзисторов 2 подключен к выходам соответствующих четырех инверторов четырех переменных 1.1, 1.2, 1.3, 1.4.

Истоки транзисторов четвертой группы передающих транзисторов 2.4.1, 2.4.2, 2.4.3, 2.4.4, 2.4.5, 2.4.6, 2.4.7, 2.4.8, 2.4.9, 2.4.10, 2.4.11, 2.4.12, 2.4.13, 2.4.14, 2.4.15, 2.4.16 подключены к выходам соответствующих инверторов группы 3 из шестнадцати инверторов настройки 3.1, 3.2, 3.3, 3.4, 3.5, 3.6, 3.7, 3.8, 3.9, 3.10, 3.11, 3.12, 3.13, 3.14, 3.15, 3.16, входы которых подключены к соответствующим из шестнадцати входов 6 настройки 6.1, 6.2, 6.3, 6.4, 6.5, 6.6, 6.7. 6.8, 6.9, 6.10, 6.11, 6.12, 6.13, 6.14,6.14, 6.15, 6.16.

Стоки четных и нечетных шестнадцати передающих транзисторов четвертой группы 2.4: 2.4.1, 2.4.2, 2.4.3, 2.4.4, 2.4.5, 2.4.6, 2.4.7, 2.4.8, 2.4.9, 2.4.10, 2.4.11, 2.4.12, 2.4.13, 2.4.14, 2.4.15, 2.4.16 объединены в восемь пар и подключены к истокам соответствующих восьми передающих транзисторов третьей группы 2.3: 2.3.1, 2.3.2, 2.3.3, 2.3.4, 2.3.5, 2.3.6, 2.3.7, 2.3.8.

Стоки четных и нечетных передающих транзисторов, в которой объединены в четыре пары и подключены к истокам соответствующих передающих транзисторов второй группы 2.2: 2.2.1, 2.2.2, 2.2.3, 2.2.4.

Стоки четных и нечетных передающих транзисторов, в которой объединены в две пары и подключены к истокам соответствующих передающих транзисторов первой группы 2.1: 2.1.1, 2.1.2, стоки которых объединены и подключены ко входу выходного инвертора 4, выход которого подключен к выходу устройства 7.

Второй выход устройства 12 подключен в выходу второго выходного инвертора 11, вход которого подключен к стокам двух дублирующих передающих транзисторов первой группы 2.1.3, 2.1.4, исток первого 2.1.3 из них подключен к истоку второго 2.1.2 передающего транзистора первой группы передающих транзисторов 2.1, исток второго 2.1.4 из них подключен к истоку первого 2.1.1 передающего транзистора первой группы передающих транзисторов 2.1.

Затвор первого дублирующего передающего транзистора первой группы 2.1.3 подключен к затвору первого 2.1.1 передающего транзистора первой группы передающих транзисторов 2.1.

Затвор второго дублирующего передающего транзистора первой группы 2.1.4 подключен к затвору второго 2.1.2 передающего транзистора первой группы передающих транзисторов 2.1.

Истоки транзисторов первой группы транзисторов отключения настройки 8: 8.1, 8.2, 8.3, 8.4, 8.5, 8.6, 8.7, 8.8, 8.9, 8.10, 8.11, 8.12, 8.13, 8.14, 8.15, 8.16, подключены ко входам соответствующих из шестнадцати входов 6 настройки 6.1, 6.2, 6.3, 6.4, 6.5, 6.6, 6.7. 6.8, 6.9, 6.10, 6.11, 6.12, 6.13, 6.14,6.14, 6.15,6.16.

Стоки транзисторов первой группы транзисторов отключения настройки 8 подключены к стокам соответствующих из шестнадцати транзисторов второй группы транзисторов отключения настройки 9: 9.1, 9.2, 9.3, 9.4, 9.5, 9.6, 9.7, 9.8, 9.9, 9.10, 9.11, 9.12, 9.13, 9.14, 9.15, 9.16, истоки которых подключены к соответствующим входам второй группы входов настройки 10: 10.1, 10.2, 10.3, 10.4, 10.5, 10.6, 10.7. 10.8, 10.9, 10.10, 10.11, 10.12, 10.13, 10.14,10.14, 10.15,10.16.

Затворы первой половины транзисторов из шестнадцати транзисторов второй группы транзисторов отключения настройки 9.1, 9.2, 9.3, 9.4, 9.5, 9.6, 9.7, 9.8 и второй половины из первой группы транзисторов отключения настройки 8.9, 8.10, 8.11, 8.12, 8.13, 8.14, 8.15, 8.16 подключены к выходу первого инвертора переменных 1.1.

Затворы второй половины транзисторов из шестнадцати транзисторов второй группы транзисторов отключения настройки 9.9, 9.10, 9.11, 9.12, 9.13, 9.14, 9.15, 9.16 и первой половины из первой группы транзисторов отключения настройки 8.1, 8.2, 8.3, 8.4, 8.5, 8.6, 8.7, 8.8 подключены к первому входу переменных 5.1.

Программируемое логическое устройство работает в следующих режимах:

1) программирования;

2) вычислений с контролем правильности результата.

1. Режим программирования

При этом с помощью внешних по отношению к устройству технических средств на шестнадцати входах настройки 6:6.1….6.16 устанавливаются логические уровни, соответствующие логической функции четырех переменных, которую необходимо вычислять (таблице истинности заданной логической функции n переменных, содержащей 16 строк).

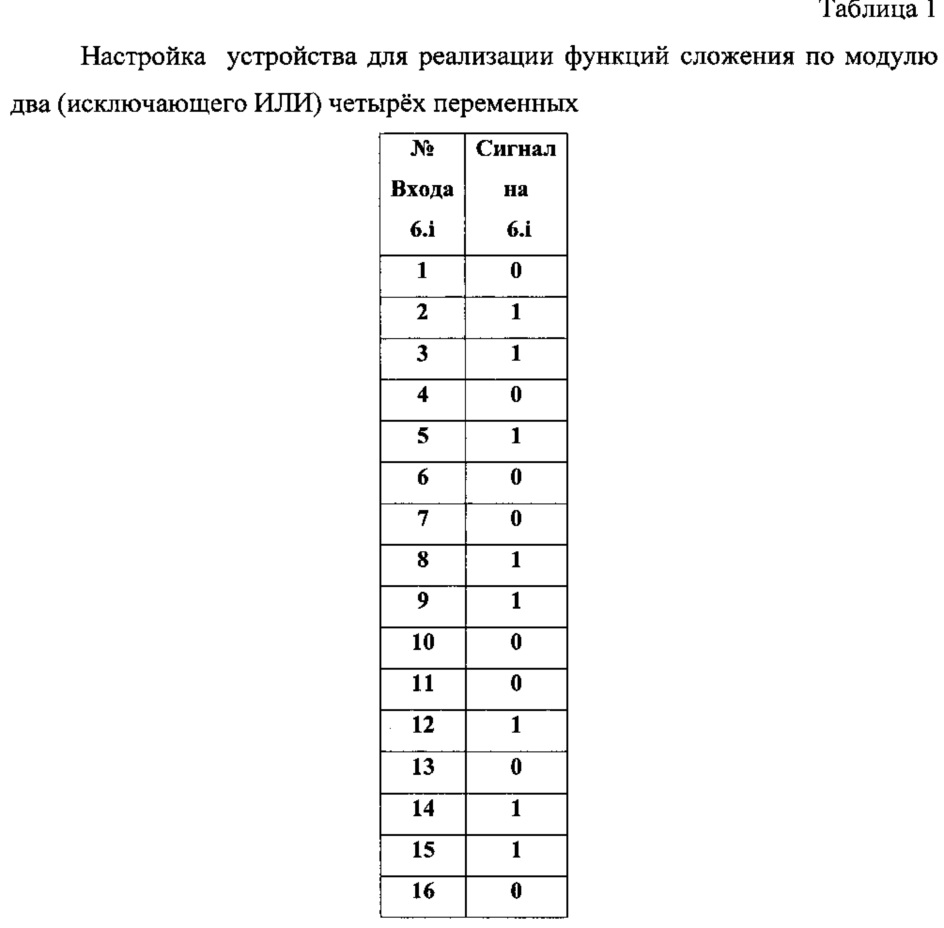

Так, для реализации функции сложения по модулю два (исключающего ИЛИ) четырех переменных (n=4)  , где xi - сигнал на входах переменных 5.1, 5.2, 5.3.5.4 - на настроечных входах 6(6.1…6.16) устанавливаются следующие логические уровни (Строганов А., Цыбин С. Программируемая коммутация в ПЛИС: взгляд изнутри// Компоненты и технологии. - 2010. - №11. С. 56-62 Рис. 9 [Электронный ресурс]. - URL: http://www.kit-e.ru/articles/plis/2010_11_56.php Дата обращения 12.01.13 г) - табл. 1:

, где xi - сигнал на входах переменных 5.1, 5.2, 5.3.5.4 - на настроечных входах 6(6.1…6.16) устанавливаются следующие логические уровни (Строганов А., Цыбин С. Программируемая коммутация в ПЛИС: взгляд изнутри// Компоненты и технологии. - 2010. - №11. С. 56-62 Рис. 9 [Электронный ресурс]. - URL: http://www.kit-e.ru/articles/plis/2010_11_56.php Дата обращения 12.01.13 г) - табл. 1:

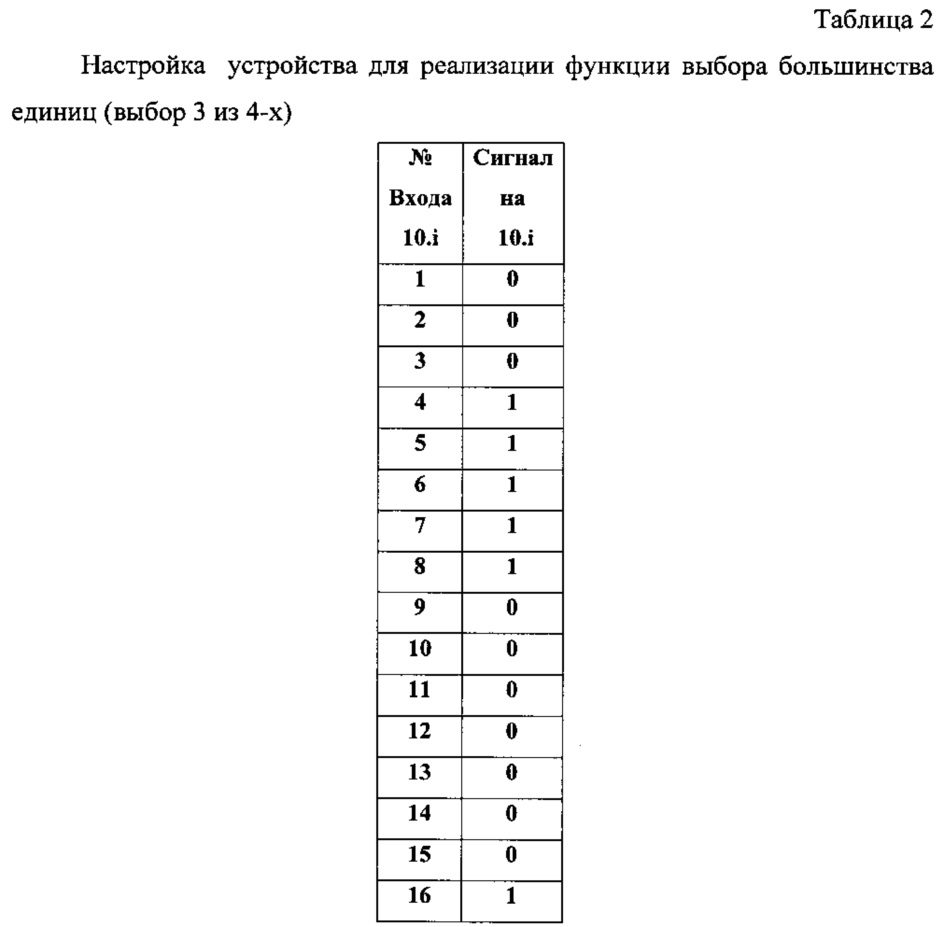

Для настройки устройства на вычисление второй логической функции с помощью внешних по отношению к устройству технических средств на шестнадцати входах второй группы входов настройки 10:10.1…10.16 устанавливаются логические уровни, соответствующие логической функции четырех переменных, которую необходимо вычислять (таблице истинности заданной логической функции n переменных, содержащей 16 строк).

Так, например, для реализации функции выбора большинства единиц (выбор 3 из 4-х) на второй группе входов настройки 10.1…10.16 устанавливаются следующие сигналы - табл. 2:

То есть здесь таблица истинности записывается «наоборот» - старшими разрядами вперед, чтобы использовать неактивную часть четырех групп передающих транзисторов 2.

2. Режим вычислений

В этом режиме на входы переменных 5.1, 5.2, 5.3, 5.4 поступают значения входных переменных. Допустим, старшая переменная 5.1 равна нулю. Тогда активированы затворы транзисторов 2.1.1 и 2.1.3. Поэтому значения первой логической функции поступают со входов настройки 6.1, 6.2, 6.3, 6.4, 6.5, 6.6, 6.7, 6.8 через активированные по своим затворам транзисторы отключения настройки 8.1, 8.2, 8.3, 8.4, 8.5, 8.6, 8.7, 8.8 через инверторы настройки 3.1, 3.2, 3.3, 3.4, 3.5, 3.6, 3.7, 3.8, через транзисторы нижней половины группы передающих транзисторов 2:2.1.1; 2.2.1, 2.2.2; 2.3.1, 2.3.2, 2.3.3, 2.3.4; 2.4.1, 2.4.2, 2.4.3, 2.4.4, 2.4.5, 2.4.6, 2.4.7, 2.4.8; через выходной инвертор 4 на выход 7 устройства.

В то же время значения второй логической функции (записанной старшими разрядами вперед) поступают со второй группы входов настройки 10.16, 10.15, 10.14, 10.13, 10.12, 10.11, 10.10, 10.9 через активированные по своим затворам транзисторы отключения настройки 9.16, 9.15, 9.14, 9.13, 9.12, 9.11, 9.10, 9.9 через инверторы настройки 3.16, 3.15, 3.14, 3.13, 3.12, 3.11, 3.10, 3.9, через транзисторы верхней половины группы передающих транзисторов 2: 2.1.3; 2.2.3, 2.2.4; 2.3.5, 2.3.6, 2.3.7, 2.3.8; 2.4.9, 2.4.10, 2.4.11, 2.4.12, 2.4.13, 2.4.14, 2.4.15, 2.4.16; через второй выходной инвертор 11 на второй выход 11 устройства.

Аналогично выполняются вычисления в случае, если старшая переменная 5.1 равна единице, только теперь для вычисления первой функции используется верхняя половина группы передающих транзисторов 2:2.2.3, 2.2.4; 2.3.5, 2.3.6, 2.3.7, 2.3.8; 2.4.9, 2.4.10, 2.4.11, 2.4.12, 2.4.13, 2.4.14, 2.4.15, 2.4.16 и транзистор 2.1.2.

Для вычисления второй логической функции используется нижняя половина группы передающих транзисторов 2:2.2.1, 2.2.2; 2.3.1, 2.3.2, 2.3.3, 2.3.4; 2.4.1, 2.4.2, 2.4.3, 2.4.4, 2.4.5, 2.4.6, 2.4.7, 2.4.8 и транзистор 2.1.4.

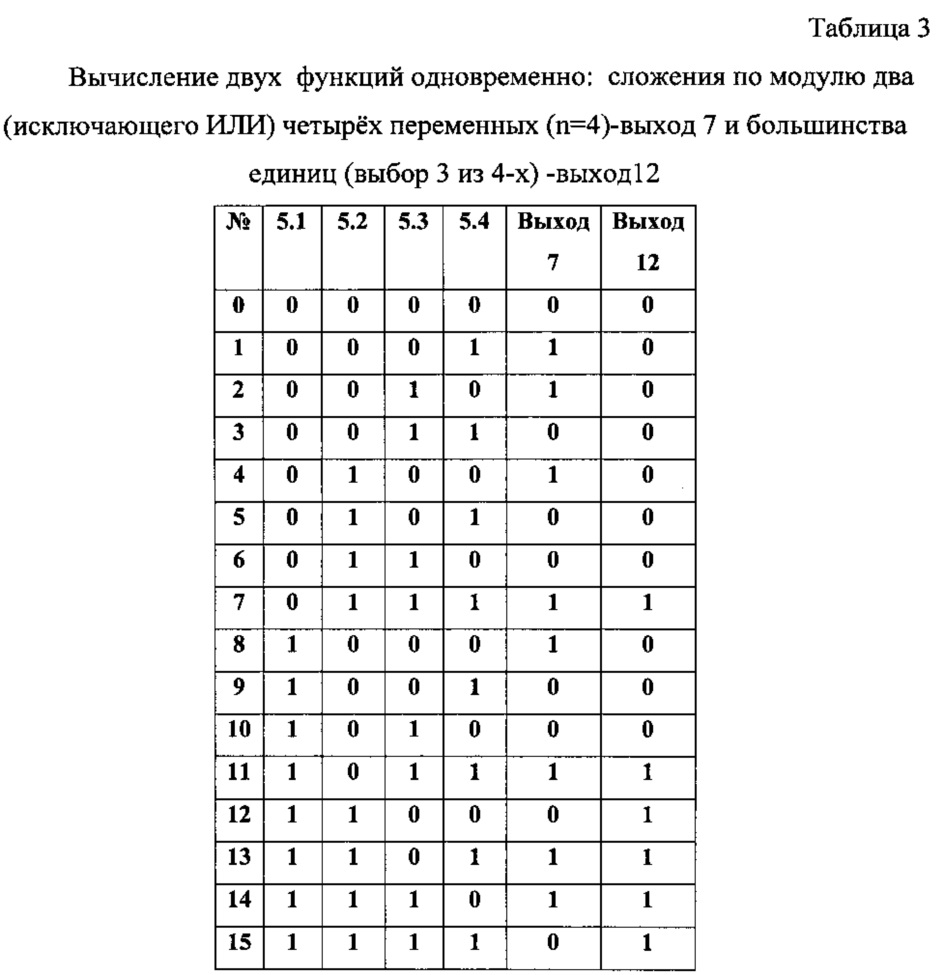

Вычисление двух функций одновременно описывается табл. 3:

Оценка технико-экономической эффективности

Таким образом, в отличие от прототипа, в котором одна половина (в зависимости от значения старшей переменной) передающих транзисторов четырех групп передающих транзисторов 2 постоянно «простаивает», в предлагаемом устройстве она использована для реализации второй функции, зависящей от тех же переменных. То есть реализуется вторая логическая функция на неактивной половине четырех групп передающих транзисторов 2, что увеличивает функциональность устройства.

Для этого используется дополнительная пара транзисторов 2.1.3, 2.1.4 и соответствующий дополнительный инвертор 11, а также и дополнительный выход 12.

Вторая функция от тех же переменных настраивается второй группой настроечных входов 10.

Используются две группы отключающих транзисторов 8 и 9, обеспечивающих подключение настроек сразу двух функций, но по разным половинам передающих транзисторов четырех групп передающих транзисторов 2. Все это, несмотря на дополнительные затраты, приводит к уменьшению своего рода «удельной» сложности реализации каждой из логических функций.

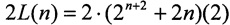

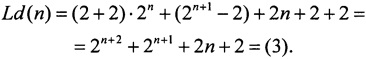

Так, сложность в количестве транзисторов программируемого логического устройства-прототипа в зависимости от числа переменных п (n=1,2,3,4) оценивается как

.

.

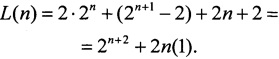

Для вычисления двух функций необходимо использовать два устройства-прототипа, тогда при п=4 получим удвоенную сложность:

.

.

При n=4 получим:

.

.

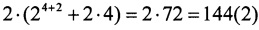

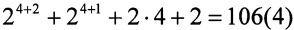

В случае совмещения реализации двух функций одновременно в предлагаемом программируемом логическом устройстве его сложность оценивается как

При n=4 получим:

.

.

То есть выигрыш в сложности при использовании предлагаемого устройства более 26%, задержка увеличивается всего на один транзистор.

Так, например, можно вычислять и сумму, и перенос при реализации в предлагаемом программируемом логическом устройстве всего полного сумматора.

Таким образом, в прототипе удельные затраты на реализацию одной логической функции равны (для n=4) 144/2=72,

В предлагаемом устройстве они меньше и равны (для n=4) 106/2=53.

Диаграммы сложности известного устройства L(n) и предлагаемого Ld(n) при реализации двух логических функций в зависимости от n=1…4 представлены на фиг. 2.

Достижение технического результата изобретения подтверждается приведенными оценками.

Программируемое логическое устройство, содержащее группу из четырех инверторов четырех переменных, четыре группы передающих транзисторов по 2, i=1, 2, 3, 4 транзисторов в группе, группу из шестнадцати инверторов настройки, выходной инвертор, входы четырех переменных, шестнадцать входов настройки и выход устройства, причем затвор каждого четного транзистора i-й группы из четырех групп передающих транзисторов подключен к i-му входу из четырех входов переменных, которые также подключены ко входам соответствующих четырех инверторов четырех переменных, затвор каждого нечетного транзистора i-й группы из четырех групп передающих транзисторов подключен к выходам соответствующих четырех инверторов четырех переменных, истоки транзисторов четвертой группы передающих транзисторов подключены к выходам соответствующих инверторов группы из шестнадцати инверторов настройки, входы которых подключены к соответствующим из шестнадцати входов настройки, стоки четных и нечетных шестнадцати передающих транзисторов четвертой группы объединены в восемь пар и подключены к истокам соответствующих восьми передающих транзисторов третьей группы, стоки четных и нечетных передающих транзисторов, в которой объединены в четыре пары и подключены к истокам соответствующих передающих транзисторов второй группы, стоки четных и нечетных передающих транзисторов, в которой объединены в две пары и подключены к истокам соответствующих передающих транзисторов первой группы, стоки которых объединены и подключены ко входу выходного инвертора, выход которого подключен к выходу устройства, отличающееся тем, что в него дополнительно введены два дублирующих передающих транзистора первой группы, первая группа транзисторов отключения настройки, вторая группа транзисторов отключения настройки, вторая группа входов настройки, второй выходной инвертор, второй выход устройства, причем второй выход устройства подключен в выходу второго выходного инвертора, вход которого подключен к стокам двух дублирующих передающих транзисторов первой группы, исток первого из них подключен к истоку второго передающего транзистора первой группы передающих транзисторов, исток второго из них подключен к истоку первого передающего транзистора первой группы передающих транзисторов, затвор первого дублирующего передающего транзистора первой группы подключен к затвору первого передающего транзистора первой группы передающих транзисторов, затвор второго дублирующего передающего транзистора первой группы подключен к затвору второго передающего транзистора первой группы передающих транзисторов, истоки транзисторов первой группы транзисторов отключения настройки подключены ко входам соответствующих из шестнадцати входов настройки, а стоки транзисторов первой группы транзисторов отключения настройки подключены к стокам соответствующих из шестнадцати транзисторов второй группы транзисторов отключения настройки, истоки которых подключены к соответствующим входам второй группы входов настройки, затворы первой половины транзисторов из шестнадцати транзисторов второй группы транзисторов отключения настройки и второй половины из первой группы транзисторов отключения настройки подключены к выходу первого инвертора переменных, затворы второй половины транзисторов из шестнадцати транзисторов второй группы транзисторов отключения настройки и первой половины из первой группы транзисторов отключения настройки подключены к первому входу переменных.