Результат интеллектуальной деятельности: МАЖОРИТАРНОЕ УСТРОЙСТВО

Вид РИД

Изобретение

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении отказо- и сбоеустойчивых, радиационно-стойких резервированных самосинхронных схем.

Известно мажоритарное устройство, содержащее первый элемент И, элемент ИЛИ, элемент НЕ, элемент "равнозначность", второй элемент И (авторское свидетельство СССР №711576, опубл. 25.01.1980 г.).

Недостатком известного устройства является невозможность его использования в самосинхронных схемах.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является мажоритарное устройство для трех парафазных сигналов с парафазным выходом, содержащее два блока транзисторов р-проводимости, два блока транзисторов n-проводимости, три неинверсных информационных входа, три инверсных информационных входа, инверсный выход, неинверсный выход, вход подключения шины «+» питания, вход подключения шины «Ноль вольт», причем неинверсные информационные входы подключены к соответствующим входам первого блока транзисторов р-проводимости и первого блока транзисторов n-проводимости, инверсные информационные входы подключены к соответствующим входам второго блока транзисторов р-проводимости и второго блока транзисторов n-проводимости, токовые входы первого блока транзисторов р-проводимости и первого блока транзисторов n-проводимости объединены и подключены ко входу подключения шины «+» питания, токовые выходы второго блока транзисторов р-проводимости и второго блока транзисторов n-проводимости объединены и подключены ко входу подключения шины «Ноль вольт», токовый выход первого блока транзисторов р-проводимости подключен к токовому входу первого блока транзисторов n-проводимости и является инверсным выходом устройства, токовый выход второго блока транзисторов р-проводимости подключен к токовому входу второго блока транзисторов n-проводимости и является неинверсным выходом устройства.

Каждый блок транзисторов р-проводимости содержит пять транзисторов р-проводимости, три информационных входа, токовый вход, токовый выход, причем первый информационный вход блока подключен к затворам первого транзистора р-проводимости, второй информационный вход блока подключен к затворам второго и четвертого транзисторов р-проводимости, третий информационный вход блока подключен к затворам третьего и пятого транзисторов р-проводимости, стоки первого и четвертого транзисторов группы транзисторов р-проводимости объединены и подключены к токовому выходу блока, истоки второго, третьего и пятого транзисторов группы транзисторов р-проводимости объединены и подключены к токовому входу блока, стоки второго и третьего транзисторов группы транзисторов р-проводимости объединены и подключены к истоку первого транзистора группы транзисторов р-проводимости, сток пятого транзистора группы транзисторов р-проводимости подключен к истоку четвертого транзистора группы транзисторов р-проводимости.

Каждый блок транзисторов n-проводимости содержит пять транзисторов n-проводимости, три информационных входа, токовый вход, токовый выход, причем первый информационный вход блока подключен к затворам первого транзистора n-проводимости, второй информационный вход блока подключен к затворам второго и четвертого транзисторов n-проводимости, третий информационный вход блока подключен к затворам третьего и пятого транзисторов n-проводимости, стоки первого и четвертого транзисторов группы транзисторов n-проводимости объединены и подключены к токовому выходу блока, истоки второго, третьего и пятого транзисторов группы транзисторов n-проводимости объединены и подключены к токовому входу блока, стоки второго и третьего транзисторов группы транзисторов n-проводимости объединены и подключены к истоку первого транзистора группы транзисторов n-проводимости, сток пятого транзистора группы транзисторов n-проводимости подключен к истоку четвертого транзистора группы транзисторов n-проводимости (Ю.А. Степченков, А.Н. Денисов, Ю.Г. Дьяченко, Ф.И. Гринфельд, О.П. Филимоненко, Н.В. Морозов, Д.Ю. Степченков. Библиотека элементов для проектирования самосинхронных полузаказных микросхем серий 5503/5507 и 5508/5509. -М.: ИПИ РАН, 2014. - 296 с.- С. 150, 151). Данное устройство принято за прототип.

Признаки прототипа, совпадающие с существенными признаками заявляемого изобретения, - два блока транзисторов p-проводимости; два блока транзисторов n-проводимости; три неинверсных информационных входа; три инверсных информационных входа; инверсный выход; неинверсный выход; вход подключения шины «+» питания; вход подключения шины «Ноль вольт»; неинверсные информационные входы подключены к соответствующим входам первого блока транзисторов р-проводимости и первого блока транзисторов n-проводимости; инверсные информационные входы подключены к соответствующим входам второго блока транзисторов р-проводимости и второго блока транзисторов n-проводимости; токовые входы первого блока транзисторов р-проводимости и второго блока транзисторов р-проводимости объединены и подключены ко входу подключения шины «+» питания; токовый выход первого блока транзисторов р-проводимости подключен к токовому входу первого блока транзисторов n-проводимости и является инверсным выходом устройства; токовый выход второго блока транзисторов р-проводимости подключен к токовому входу второго блока транзисторов n-проводимости и является неинверсным выходом устройства;

каждый блок транзисторов р-проводимости содержит пять транзисторов р-проводимости, три информационных входа, токовый вход, токовый выход; первый информационный вход блока подключен к затвору первого транзистора р-проводимости; второй информационный вход блока подключен к затворам второго и четвертого транзисторов р-проводимости; третий информационный вход блока подключен к затворам третьего и пятого транзисторов р-проводимости; стоки первого и четвертого транзисторов группы транзисторов р-проводимости объединены и подключены к токовому выходу блока; истоки второго, третьего и пятого транзисторов группы транзисторов р-проводимости объединены и подключены к токовому входу блока; стоки второго и третьего транзисторов группы транзисторов р-проводимости объединены и подключены к истоку первого транзистора группы транзисторов р-проводимости; сток пятого транзистора группы транзисторов р-проводимости подключен к истоку четвертого транзистора группы транзисторов р-проводимости;

каждый блок транзисторов n-проводимости содержит пять транзисторов n-проводимости, три информационных входа, токовый вход, токовый выход; первый информационный вход блока подключен к затвору первого транзистора n-проводимости; второй информационный вход блока подключен к затворам второго и четвертого транзисторов n-проводимости; третий информационный вход блока подключен к затворам третьего и пятого транзисторов n-проводимости; стоки первого и четвертого транзисторов группы транзисторов n-проводимости объединены и подключены к токовому выходу блока; истоки второго, третьего и пятого транзисторов группы транзисторов n-проводимости объединены и подключены к токовому входу блока; стоки второго и третьего транзисторов группы транзисторов n-проводимости объединены и подключены к истоку первого транзистора группы транзисторов n-проводимости; сток пятого транзистора группы транзисторов n-проводимости подключен к истоку четвертого транзистора группы транзисторов n-проводимости.

Недостатком известного устройства, принятого за прототип, является невозможность реализации фазы гашения парафазных сигналов, поступающих с таких резервированных триггеров, выходы которой не могут принимать одинаковые значения.

Это обусловлено следующими обстоятельствами. Технические средства прототипа позволяют реализовать фазу гашения в случае, когда инверсные и неинверсные информационные входы принимают одинаковое - нулевое значение, что имеет место при резервировании комбинационных самосинхронных схем и части триггеров. Тогда на инверсном выходе и неинверсном выходах формируются одинаковые - единичные сигналы. В случае резервирования некоторых триггеров, парафазные выходы которых не могут принимать одинаковые значения, фаза гашения в прототипе не может быть реализована, так как в прототипе нет средств реализации фазы гашения в случае, когда инверсные и неинверсные информационные входы принимают инверсные значения. Это сужает область применения известного устройства для создания резервированных таких самосинхронных схем с памятью, выходы которой не могут принимать одинаковые значения.

Задачей изобретения является реализация фазы гашения в случае, когда инверсные и неинверсные информационные входы принимают инверсные значения.

Поставленная задача была решена за счет того, что в заявляемое устройство, содержащее два блока транзисторов р-проводимости, два блока транзисторов n-проводимости, три неинверсных информационных входа, три инверсных информационных входа, инверсный выход, неинверсный выход, вход подключения шины «+» питания, вход подключения шины «Ноль вольт», причем неинверсные информационные входы подключены к соответствующим входам первого блока транзисторов р-проводимости и первого блока транзисторов n-проводимости, инверсные информационные входы подключены к соответствующим входам второго блока транзисторов р-проводимости и второго блока транзисторов n-проводимости, токовые входы первого блока транзисторов р-проводимости и второго блока транзисторов р- проводимости объединены и подключены ко входу подключения шины «+» питания,

токовый выход первого блока транзисторов р-проводимости подключен к токовому входу первого блока транзисторов n-проводимости и является инверсным выходом устройства, токовый выход второго блока транзисторов р-проводимости подключен к токовому входу второго блока транзисторов n-проводимости и является неинверсным выходом устройства;

каждый блок транзисторов р-проводимости содержит пять транзисторов р-проводимости, три информационных входа, токовый вход, токовый выход, причем первый информационный вход блока подключен к затвору первого транзистора р-проводимости, второй информационный вход блока подключен к затворам второго и четвертого транзисторов р-проводимости, третий информационный вход блока подключен к затворам третьего и пятого транзисторов р-проводимости, стоки первого и четвертого транзисторов группы транзисторов р-проводимости объединены и подключены к токовому выходу блока, истоки второго, третьего и пятого транзисторов группы транзисторов р-проводимости объединены и подключены к токовому входу блока, стоки второго и третьего транзисторов группы транзисторов р-проводимости объединены и подключены к истоку первого транзистора группы транзисторов р-проводимости, сток пятого транзистора группы транзисторов р-проводимости подключен к истоку четвертого транзистора группы транзисторов р-проводимости;

каждый блок транзисторов n-проводимости содержит пять транзисторов n-проводимости, три информационных входа, токовый вход, токовый выход, причем первый информационный вход блока подключен к затвору первого транзистора n-проводимости, второй информационный вход блока подключен к затворам второго и четвертого транзисторов n-проводимости, третий информационный вход блока подключен к затворам третьего и пятого транзисторов n-проводимости, стоки первого и четвертого транзисторов группы транзисторов n-проводимости объединены и подключены к токовому выходу блока, истоки второго, третьего и пятого транзисторов группы транзисторов n-проводимости объединены и подключены к токовому входу блока, стоки второго и третьего транзисторов группы транзисторов n-проводимости объединены и подключены к истоку первого транзистора группы транзисторов n-проводимости, сток пятого транзистора группы транзисторов n-проводимости подключен к истоку четвертого транзистора группы транзисторов n-проводимости, согласно изобретению дополнительно введены два блока транзисторов р-проводимости и два блока транзисторов n-проводимости, три входа разрешения, причем токовый выход первого блока транзисторов n-проводимости подключен к токовому входу третьего блока транзисторов n-проводимости, токовый выход второго блока транзисторов n-проводимости подключен к токовому входу четвертого блока транзисторов n-проводимости, токовые выходы третьего и четвертого блоков транзисторов n-проводимости объединены и подключены ко входу подключения шины «Ноль вольт», токовые входы третьего и четвертого блоков транзисторов р-проводимости подключены ко входу подключения шины «+» питания, токовый выход третьего блока транзисторов р-проводимости подключен к инверсному выходу устройства, токовый выход четвертого блока транзисторов р-проводимости подключен к неинверсному выходу устройства, первые информационные входы третьего и четвертого блоков транзисторов р-проводимости, третьего и четвертого блоков транзисторов n-проводимости подключены к первому входу разрешения, вторые информационные входы третьего и четвертого блоков транзисторов р-проводимости, третьего и четвертого блоков транзисторов n-проводимости подключены ко второму входу разрешения, третьи информационные входы третьего и четвертого блоков транзисторов р-проводимости, третьего и четвертого блоков транзисторов n-проводимости подключены к третьему входу разрешения.

Признаки заявляемого технического решения, отличительные от прототипа - два блока транзисторов р-проводимости и два блока транзисторов n-проводимости; три входа разрешения; токовый выход первого блока транзисторов n-проводимости подключен к токовому входу третьего блока транзисторов n-проводимости; токовый выход второго блока транзисторов n-проводимости подключен к токовому входу четвертого блока транзисторов n-проводимости; токовые выходы третьего и четвертого блоков транзисторов n-проводимости объединены и подключены ко входу подключения шины «Ноль вольт»; токовые входы третьего и четвертого блоков транзисторов р-проводимости подключены ко входу подключения шины «+» питания; токовый выход третьего блока транзисторов р-проводимости подключен к инверсному выходу устройства; токовый выход четвертого блока транзисторов р-проводимости подключен к неинверсному выходу устройства; первые информационные входы третьего и четвертого блоков транзисторов р-проводимости, третьего и четвертого блоков транзисторов n-проводимости подключены к первому входу разрешения; вторые информационные входы третьего и четвертого блоков транзисторов р-проводимости, третьего и четвертого блоков транзисторов n-проводимости подключены ко второму входу разрешения; третьи информационные входы третьего и четвертого блоков транзисторов р-проводимости, третьего и четвертого блоков транзисторов n-проводимости подключены к третьему входу разрешения.

Отличительные признаки в сочетании с известными позволяют в случае резервирования таких триггеров, парафазные выходы которых не могут принимать одинаковые значения, реализовать фазу гашения за счет того, что троированный сигнал разрешения в случае его снятия через третий и четвертый блоки транзисторов n-проводимости обеспечивает отключение от шины «Ноль вольт» по токовым выходам первого и второго блоков транзисторов n-проводимости, а через третий и четвертый блоки транзисторов р-проводимости - принудительное подключение на инверсный и неинверсный выходы шины «+» питания, что приводит к появлению на этих выходах одинакового единичного логического уровня, то есть реализуется фаза гашения.

В случае подачи разрешающего сигнала через третий и четвертый блоки транзисторов n-проводимости обеспечивается подключение шины «Ноль вольт» по токовым выходам первого и второго блоков транзисторов n-проводимости, а через третий и четвертый блоки транзисторов р-проводимости отключается связь на инверсный и неинверсный выходы шины «+» питания, что обеспечивает возможность реализации гашения за счет гашения по трем неинверсным информационным входам, трем инверсным информационным входам в случае, если они принимают одинаковые нулевые значения.

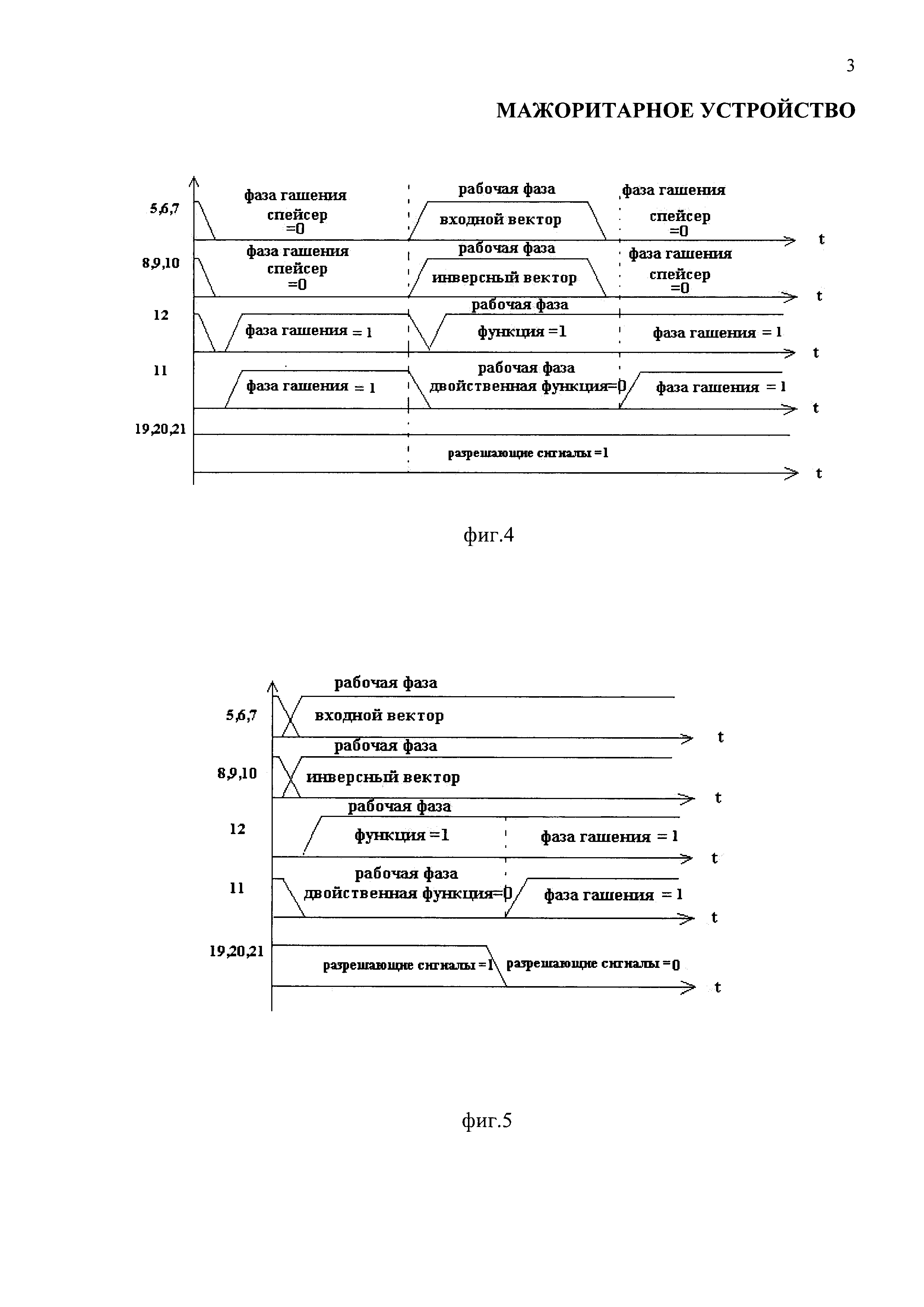

На фиг. 1 изображена схема электрическая структурная предлагаемого мажоритарного устройства.

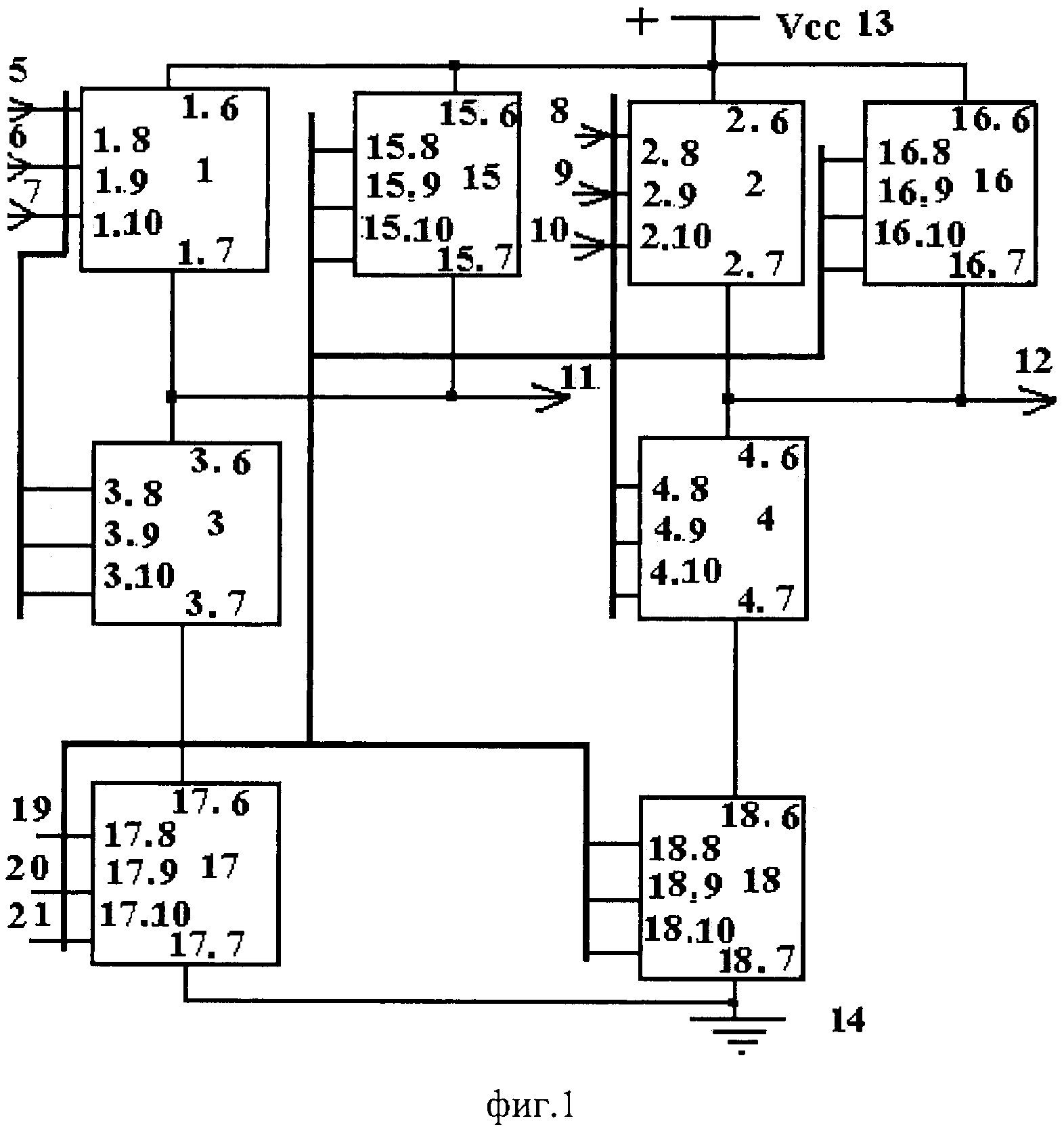

На фиг. 2 изображена схема электрическая функциональная i-го блока транзисторов р-проводимости предлагаемого мажоритарного устройства.

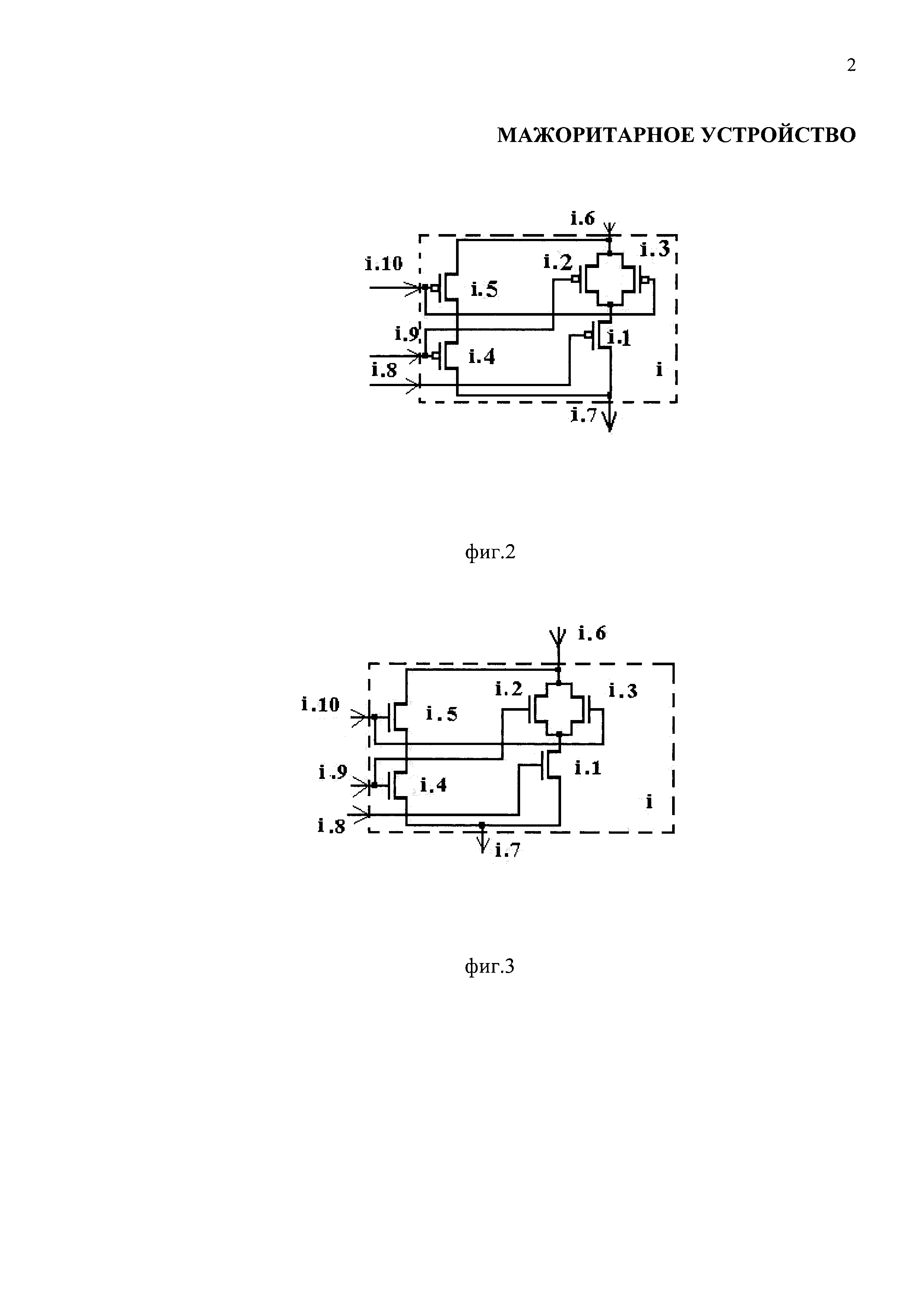

На фиг. 3 изображена схема электрическая функциональная i-го блока транзисторов n-проводимости предлагаемого мажоритарного устройства.

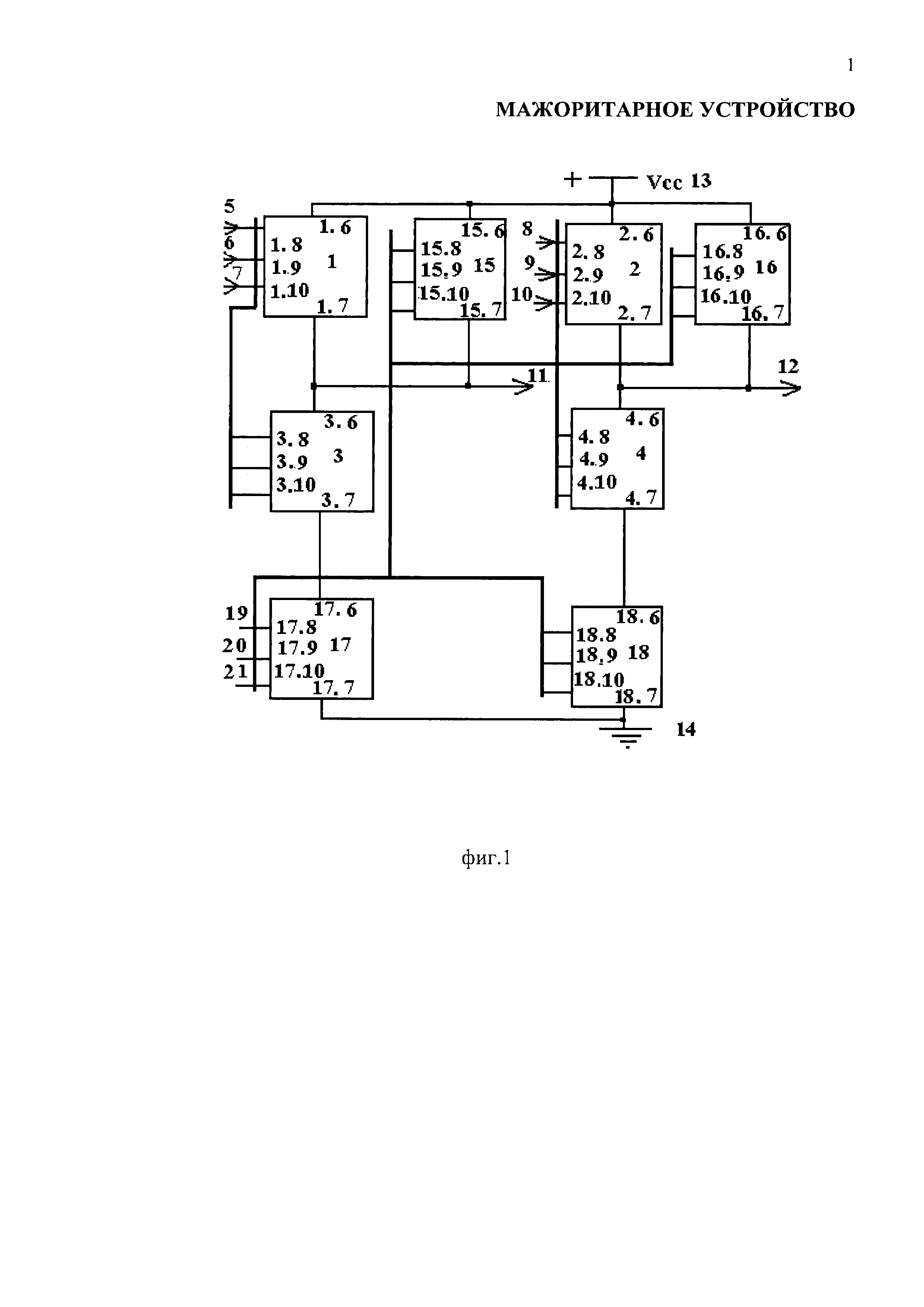

На фиг. 4 изображена временная диаграмма работы предлагаемого мажоритарного устройства.

На фиг. 5 изображена временная диаграмма работы предлагаемого мажоритарного устройства.

Мажоритарное устройство (фиг. 1) содержит первый 1 и второй 2 блоки транзисторов р-проводимости, первый 3 и второй 4 блоки транзисторов n-проводимости, три неинверсных информационных входа 5, 6, 7, три инверсных информационных входа 8, 9,10, инверсный выход 11, неинверсный выход 12, вход подключения шины «+» питания 13, вход подключения шины «Ноль вольт» 14, третий 15 и четвертый 16 блоки транзисторов р-проводимости, третий 17 и четвертый 18 блоки транзисторов n-проводимости, первый 19, второй 20 и третий 21 входы разрешения.

Неинверсные информационные входы 5, 6, 7 подключены к соответствующим входам 1.8, 1.9, 1.10 первого блока транзисторов р-проводимости 1 и соответствующим входам 3.8, 3.9, 3.10 первого блока транзисторов n-проводимости 3.

Инверсные информационные входы 8, 9, 10 подключены к соответствующим входам 2.8, 2.9, 2.10 второго блока транзисторов р-проводимости 2 и соответствующим входам 4.8, 4.9, 4.10 второго блока транзисторов n-проводимости 4.

Токовый вход 1.6 первого блока транзисторов р-проводимости 1 и токовый вход 2.6 второго блока транзисторов р-проводимости 2 объединены и подключены к входу подключения шины «+» питания 13.

Токовый вход 3.6 первого блока транзисторов n-проводимости 3 является инверсным выходом устройства 11.

Токовый вход 4.6 второго блока транзисторов n-проводимости 4 является неинверсным выходом устройства 12.

Токовый выход 1.7 первого блока транзисторов р-проводимости 1 подключен к токовому входу 3.6 первого блока транзисторов n-проводимости 3.

Токовый выход 2.7 второго блока транзисторов р-проводимости 2 подключен к токовому входу 4.6 второго блока транзисторов n-проводимости 4.

Токовые выходы 17.7 третьего 17 и 18.7 четвертого 18 блоков транзисторов n-проводимости объединены и подключены ко входу подключения шины «Ноль вольт» 14.

Токовые входы 15.6 третьего 15 и 16.6 четвертого 16 блоков транзисторов р-проводимости подключены ко входу подключения шины «+» питания 13.

Токовый выход 15.7 третьего 15 блока транзисторов р-проводимости подключен к инверсному выходу 11 устройства.

Токовый выход 16.7 четвертого 16 блока транзисторов р-проводимости подключен к неинверсному выходу 12 устройства.

Токовые выходы 3.7 и 4.7 первого 3 и второго 4 блоков транзисторов n-проводимости подключены к токовым входам 17.6 и 18.6 третьего 17 и четвертого 18 блоков транзисторов n-проводимости, соответственно.

Первые информационные входы 15.8,16.8,17.8,18.8 третьего 15 и четвертого 16 блоков транзисторов р-проводимости, третьего 17 и четвертого 18 блоков транзисторов n-проводимости подключены к первому входу разрешения 19.

Вторые информационные входы 15.9,16.9,17.9,18.9 третьего 15 и четвертого 16 блоков транзисторов р-проводимости, третьего 17 и четвертого 18 блоков транзисторов n-проводимости подключены ко второму входу разрешения 20.

Третьи информационные входы 15.10,16.10,17.10,18.10 третьего 15 и четвертого 16 блоков транзисторов р-проводимости, третьего 17 и четвертого 18 блоков транзисторов n-проводимости подключены к третьему входу разрешения 21.

Каждый i-й (i=1…4) блок транзисторов р-проводимости (фиг. 2) содержит пять транзисторов р-проводимости i.l, i.2, i.3, i.4, i.5, токовый вход i.6, токовый выход i.7, три информационных входа i.8, i.9, i.10.

Первый информационный вход i.8 блока i подключен к затвору первого транзистора р-проводимости i.l, второй информационный вход i.9 блока i подключен к затворам второго i.2 и четвертого i.4 транзисторов р-проводимости.

Третий информационный вход i.10 блока подключен к затворам третьего i.3 и пятого i.5 транзисторов р-проводимости.

Стоки первого i.l и четвертого i.4 транзисторов группы транзисторов р-проводимости объединены и подключены к токовому выходу i.7 блока.

Истоки второго i.2, третьего i.3 и пятого i.5 транзисторов группы транзисторов р-проводимости объединены и подключены к токовому входу i.6 блока.

Стоки второго i.2 и третьего i.3 транзисторов группы транзисторов р-проводимости объединены и подключены к истоку первого транзистора i.1 группы транзисторов р-проводимости.

Сток пятого транзистора i.5 группы транзисторов р-проводимости подключен к истоку четвертого i.4 транзистора группы транзисторов р-проводимости.

Каждый i-й (i=1…4) блок транзисторов n-проводимости (фиг. 3) содержит пять транзисторов n-проводимости i.l, i.2, i.3, i.4, i.5, три информационных входа i.8, i.9, i.l0, токовый вход i.6, токовый выход i.7.

Первый информационный вход i.8 блока i подключен к затвору первого транзистора n-проводимости i.1, второй информационный вход i.9 блока i подключен к затворам второго i.2 и четвертого i.4 транзисторов n-проводимости.

Третий информационный вход i.l0 блока подключен к затворам третьего i.3 и пятого i.5 транзисторов n-проводимости.

Стоки первого i.l и четвертого i.4 транзисторов группы транзисторов n-проводимости объединены и подключены к токовому выходу i.7 блока.

Истоки второго i.2, третьего i.3 и пятого i.5 транзисторов группы транзисторов n-проводимости объединены и подключены к токовому входу i.6 блока.

Стоки второго i.2 и третьего i.3 транзисторов группы транзисторов n-проводимости объединены и подключены к истоку первого транзистора i.l группы транзисторов n-проводимости.

Сток пятого транзистора i.5 группы транзисторов n-проводимости подключен к истоку четвертого i.4 транзистора группы транзисторов n-проводимости.

Устройство работает следующим образом.

1. Работа устройства при резервировании самосинхронных схем (комбинационных и триггеров), имеющих парафазные выходы

В этом случае на неинверсные 5, 6, 7 и инверсные 8, 9, 10 информационные входы поступают сигналы с трех каналов одновыходных самосинхронных схем, которые могут принимают взаимно инверсные значения в рабочей фазе и одинаковые нулевые значения в фазе гашения (фиг. 1), и устройство работает аналогично прототипу.

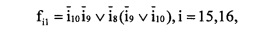

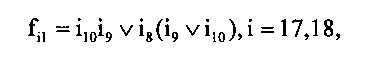

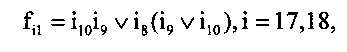

При этом на трех входах разрешения 19, 20, 21 должны быть установлены логические единицы, в результате чего третий 15 и четвертый 16 блоки транзисторов р-проводимости (фиг. 2) вычисляют инверсную мажоритарную функцию вида:

равную в этом случае нулю, то есть размыкают связь со входа «+» питания 13 на инверсный 11 и неинверсный выходы 12.

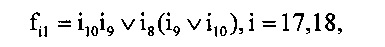

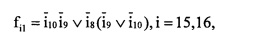

Третий и четвертый блоки транзисторов n-проводимости 17, 18 (фиг. 1,3) вычисляют неинверсную мажоритарную функцию вида:

равную в этом случае единице, то есть подключают вход подключения шины «Ноль вольт» к выходам 3.7 и 4.7 первого и второго блоков транзисторов n-проводимости 3, 4.

В рабочей фазе обеспечивается мажоритирование сигналов с трех каналов самосинхронной схемы для реализации пассивной отказоустойчивости, парирующей как отказы, так и сбои в одном из трех каналов внешней по отношению к устройству самосинхронной комбинационной схемы.

Например, при наличии логических нулей на инверсных информационных входах 10 и 9, или 8 и 9, или 8 и 10 i-го блока (наборы 000, 001, 010, 100) активируются соответствующие затворы транзисторов р-проводимости и образуется цепочка (цепочки) открытых транзисторов, что обеспечивает протекание тока с токового входа 2.6 на токовый выход 2.7 второго блока транзисторов р-проводимости 2.

В то же время такая ситуация не позволяет активировать ни один путь с токового входа 4.6 на токовый выход 4.7 второго блока транзисторов n-проводимости 4 (фиг. 1, 2, 4).

Все это обеспечивает появление на неинверсном выходе 12 логической единицы за счет протекания тока со входа подключения шины «+» питания 13 (фиг. 1, 4)

Тогда, поскольку в описанном выше примере на инверсных входах 8, 9,10 имеется большинство единиц (наборы 111, 110, 101, 011), в первом блоке транзисторов р-проводимости 1 (фиг. 1,2) не образуется ни одной цепочки с токового входа 1.6 на токовый выход 1.7, но зато такие цепочки образуются в первом блоке транзисторов n-проводимости 3 (фиг. 1, 3, 4):

Все это обеспечивает появление на инверсном выходе 11 логического нуля, то есть вычисляется мажоритированное значение логической функции, равное единице (выход 12) и двойственное мажоритированное значение, равное нулю (выход 11) - фиг. 1, 2, 3, 4.

В случае поступления на инверсные информационные входы 8, 9, 10 наборов 111, 110, 101, 011, а на неинверсные информационные входы 5, 6, 7 - соответствующих наборов 000, 001, 010, 100, образуются цепочки с токового входа 4.6 на токовый выход 4.7 первого блока транзисторов n-проводимости 4 (фиг. 1, 3) и токового входа 1.6 на токовый выход 1.7 первого блока транзисторов р-проводимости 1 (фиг. 1, 2).

Это обеспечивает появление на неинверсном выходе 12 логического нуля, а на инверсном - единицы.

В фазе гашения на неинверсные информационные входы 5, 6, 7; на инверсные информационные входы 8, 9, 10 поступает одинаковая информация, например все нули, поэтому на инверсном выходе 11 и неинверсном выходе 12 устанавливаются одинаковые единичные логические уровни (фиг. 4).

2. Работа устройства при резервировании триггеров, выходы которых не могут принимать одинаковые значения

В этом случае на три входа разрешения 19, 20, 21 поступают сигналы разрешения работы с трех каналов внешнего триггера, единичное значение которых фиксирует рабочую фазу, а нулевое - фазу гашения (фиг. 1, 2, 3, 4).

2.1. Рабочая фаза при резервировании триггеров, выходы которых не могут принимать одинаковые значения

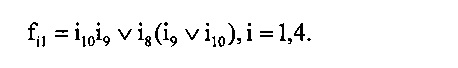

Если на трех входах разрешения 19, 20, 21 установлено большинство логических единиц, то, поскольку третий 15 и четвертый 16 блоки транзисторов р-проводимости (фиг. 2) вычисляют инверсную мажоритарную функцию вида

равную нулю, размыкается связь со входа «+» питания 13 на инверсный 11 и неинверсный 12 выходы.

Третий и четвертый блоки транзисторов n-проводимости 17, 18 (фиг. 1, 3) вычисляют неинверсную мажоритарную функцию вида:

равную в этом случае единице, то есть подключают вход подключения шины «Ноль вольт» к выходам 3.7 и 4.7 первого и второго блоков транзисторов n-проводимости 3, 4. Реализуется рабочая фаза (фиг. 5).

2.2. Фаза гашения при резервировании триггеров, выходы которых не могут принимать одинаковые значения.

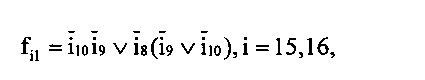

Если на трех входах разрешения 19, 20, 21 установлено большинство логических нулей, то, поскольку третий 15 и четвертый 16 блоки транзисторов р-проводимости (фиг. 2) вычисляют инверсную мажоритарную функцию вида

равную единице, замыкается связь со входа «+» питания 13 на инверсный 11 и неинверсный 12 выходы, что переводит их в одинаковое единичное значение, реализуя так называемый спейсер (фиг. 5).

При этом третий и четвертый блоки транзисторов n-проводимости 17, 18 (фиг. 1, 3) вычисляют неинверсную мажоритарную функцию вида:

равную в этом случае нулю, то есть отключают вход подключения шины «Ноль вольт» к выходам 3.7 и 4.7 первого и второго блоков транзисторов n-проводимости 3,4. Таким образом, реализуется фаза гашения.

То есть предлагаемое устройство может быть использовано как при резервировании таких самосинхронных схем, когда инверсные и неинверсные информационные входы принимают в фазе гашения одинаковое нулевое значение, так и в случае резервирования таких триггеров, у которых парафазные выходы не могут принимать одинаковые значения, но фаза гашения реализуется путем отключения от шины «Ноль вольт» и навязывания на выходы инверсный 11 и неинверсный 12 логической единицы с использованием мажоритирования сигналов разрешения, поступающих с трех каналов триггера.

Таким образом, достижение технического результата изобретения подтверждается.