Результат интеллектуальной деятельности: БИПОЛЯРНО-ПОЛЕВОЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ

Вид РИД

Изобретение

Изобретение относится к области радиотехники и автоматики и может быть использовано в измерительной технике в качестве прецизионного устройства усиления сигналов различных сенсоров.

В современной радиоэлектронной аппаратуре находят применение операционные усилители (ОУ) на полевых и биполярных транзисторах, которые содержат отрицательную обратную связь по синфазному сигналу [1-5].

Для работы в условиях космического пространства, в экспериментальной физике необходимы радиационно-стойкие ОУ с повышенным коэффициентом усиления и малым напряжением смещения нуля (Uсм). Опыт проектирования устройств данного класса показывает, что решение этих задач возможно с использованием биполярно-полевого технологического процесса [6], обеспечивающего формирование p-канальных полевых и высококачественных n-p-n биполярных транзисторов с радиационной стойкостью до 1 Мрад и потоком нейтронов до 1013 н/см2.

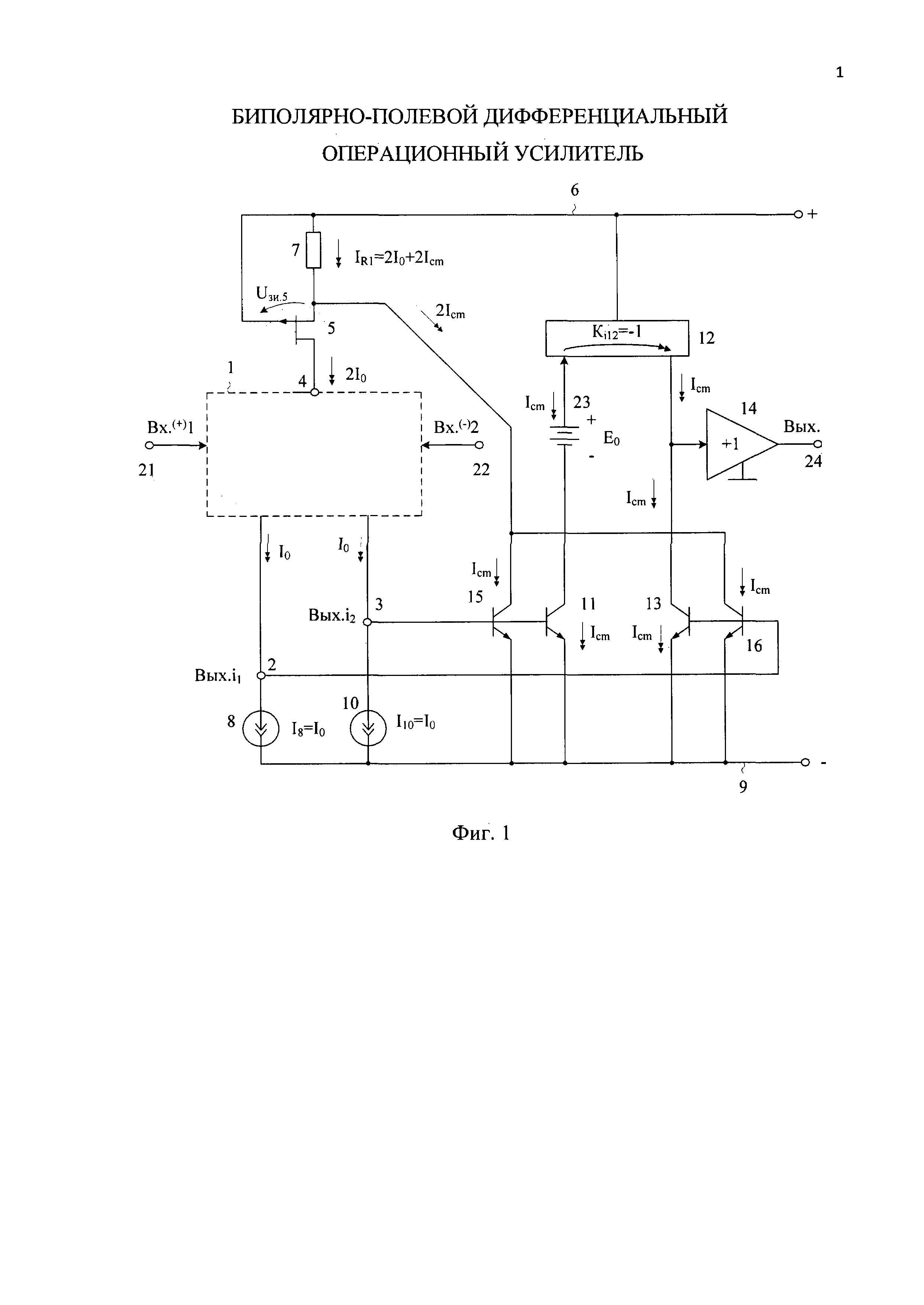

Ближайшим прототипом (фиг. 1) заявляемого устройства является операционный усилитель по патенту RU 2571579 (заявка 2014145403/08, положительное решение от 09.07.15), фиг. 4. Он содержит (фиг. 1) входной дифференциальный каскад 1 с первым 2 и вторым 3 противофазными токовыми выходами, первый 4 токовый вход для установления статического режима по току транзисторов входного дифференциального каскада 1, подключенный к стоку первого 5 полевого транзистора с управляющим p-n переходом, затвор которого связан с первой 6 шиной источника питания, а исток подключен к первой 6 шине источника питания через первый 7 вспомогательный токостабилизирующий двухполюсник, первый 8 токостабилизирующий двухполюсник, включенный между первым 2 токовым выходом входного дифференциального каскада 1 и второй 9 шиной источника питания, второй 10 токостабилизирующий двухполюсник, включенный между вторым 3 токовым выходом входного дифференциального каскада 1 и второй 9 шиной источника питания, первый 11 выходной транзистор, эмиттер которого подключен ко второй 9 шине источника питания, а коллектор связан со входом токового зеркала 12, второй 13 выходной транзистор, эмиттер которого подключен ко второй 9 шине источника питания, а коллектор связан с выходом токового зеркала 12 и входом буферного усилителя 14, первый 15 и второй 16 вспомогательные транзисторы, коллекторы которых объединены и подключены к истоку первого 5 полевого транзистора с управляющим р-n переходом, а эмиттеры соединены со второй 9 шиной источника питания, причем база первого 15 вспомогательного транзистора соединена с базой первого 11 выходного транзистора, а база второго 16 вспомогательного транзистора соединена с базой второго 13 выходного транзистора.

Существенный недостаток известного ОУ состоит в том, что он имеет сравнительно небольшой разомкнутый коэффициент усиления по напряжению (Kу). В конечном итоге это снижает прецизионность известного ОУ при работе в схемах с отрицательной обратной связью. Кроме этого, ОУ с известной архитектурой не могут работать в структуре достаточно нового подкласса активных элементов [8] - мультидифференциальных операционных усилителях, для которых входной дифференциальный каскад 1 (ДК) должен иметь два токовых входа для установления его статического режима [6].

Основная задача предлагаемого изобретения состоит в повышении разомкнутого коэффициента усиления по напряжению ОУ при сохранении высоких показателей по стабильности напряжения смещения нуля. Дополнительная задача - расширение функциональных возможностей ОУ - создание необходимых условий для построения на его основе мультидифференциальных операционных усилителей (МОУ), имеющих ряд неоспоримых преимуществ в сравнении с классическими ОУ [8].

Поставленные задачи достигаются тем, что в операционном усилителе фиг. 1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 противофазными токовыми выходами, первый 4 токовый вход для установления статического режима по току транзисторов входного дифференциального каскада 1, подключенный к стоку первого 5 полевого транзистора с управляющим p-n переходом, затвор которого связан с первой 6 шиной источника питания, а исток подключен к первой 6 шине источника питания через первый 7 вспомогательный токостабилизирующий двухполюсник, первый 8 токостабилизирующий двухполюсник, включенный между первым 2 токовым выходом входного дифференциального каскада 1 и второй 9 шиной источника питания, второй 10 токостабилизирующий двухполюсник, включенный между вторым 3 токовым выходом входного дифференциального каскада 1 и второй 9 шиной источника питания, первый 11 выходной транзистор, эмиттер которого подключен ко второй 9 шине источника питания, а коллектор связан со входом токового зеркала 12, второй 13 выходной транзистор, эмиттер которого подключен ко второй 9 шине источника питания, а коллектор связан с выходом токового зеркала 12 и входом буферного усилителя 14, первый 15 и второй 16 вспомогательные транзисторы, коллекторы которых объединены и подключены к истоку первого 5 полевого транзистора с управляющим p-n переходом, а эмиттеры соединены со второй 9 шиной источника питания, причем база первого 15 вспомогательного транзистора соединена с базой первого 11 выходного транзистора, а база второго 16 вспомогательного транзистора соединена с базой второго 13 выходного транзистора, предусмотрены новые элементы и связи - в схему введены первый 17 и второй 18 дополнительные транзисторы, коллекторы которых связаны с первой 6 шиной источника питания, база первого 17 дополнительного транзистора подключена к первому 2 токовому выходу входного дифференциального каскада 1, эмиттер первого 17 дополнительного транзистора связан со второй 9 шиной источника питания через второй 19 вспомогательный токостабилизирующий двухполюсник и соединен с объединенными базами второго 13 выходного транзистора и второго 16 вспомогательного транзистора, база второго 18 дополнительного транзистора подключена ко второму 3 токовому выходу входного дифференциального каскада 1, эмиттер второго 18 дополнительного транзистора связан со второй 9 шиной источника питания через третий 20 вспомогательный токостабилизирующий двухполюсник и соединен с объединенными базами первого 11 выходного транзистора и первого 15 вспомогательного транзистора.

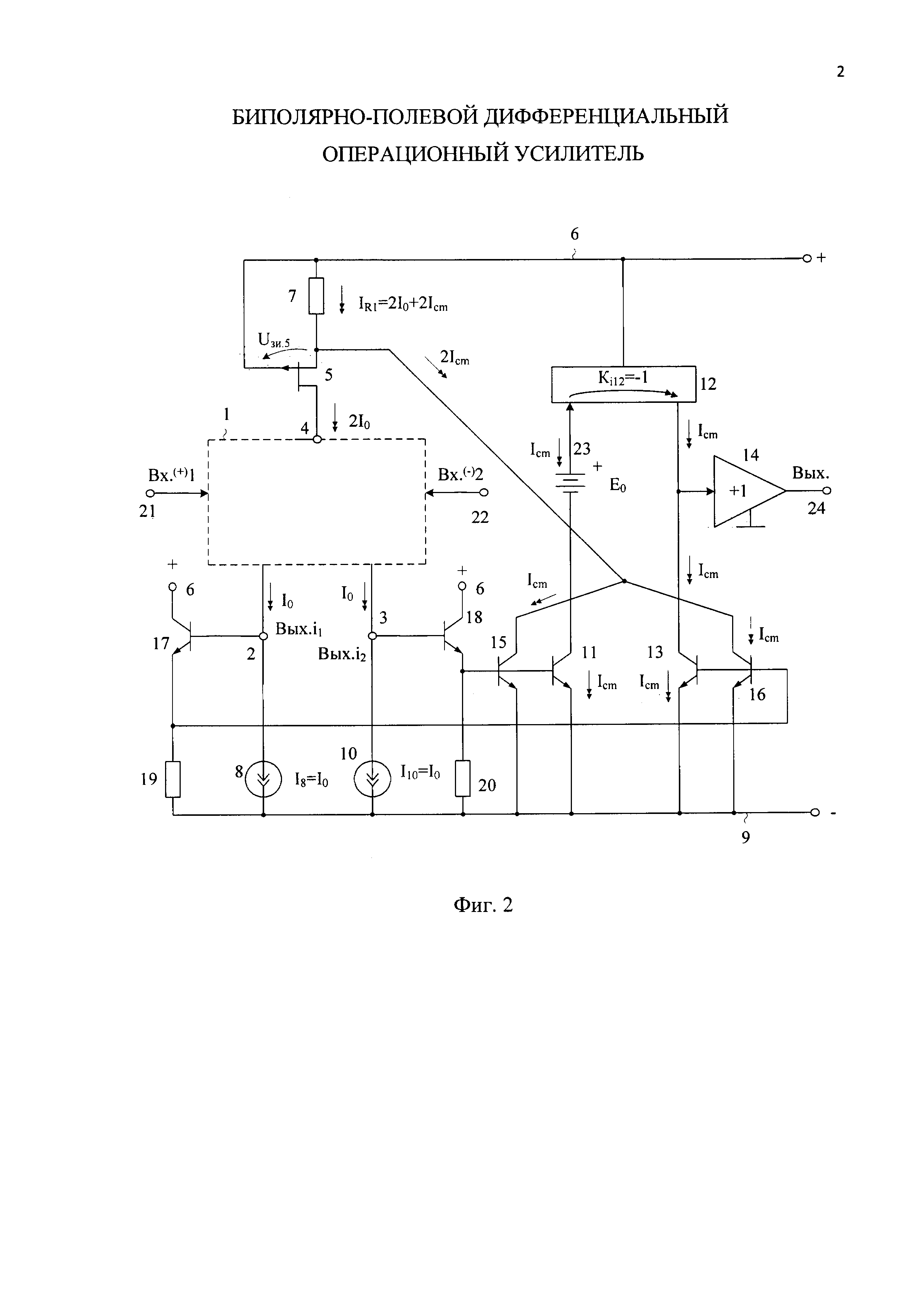

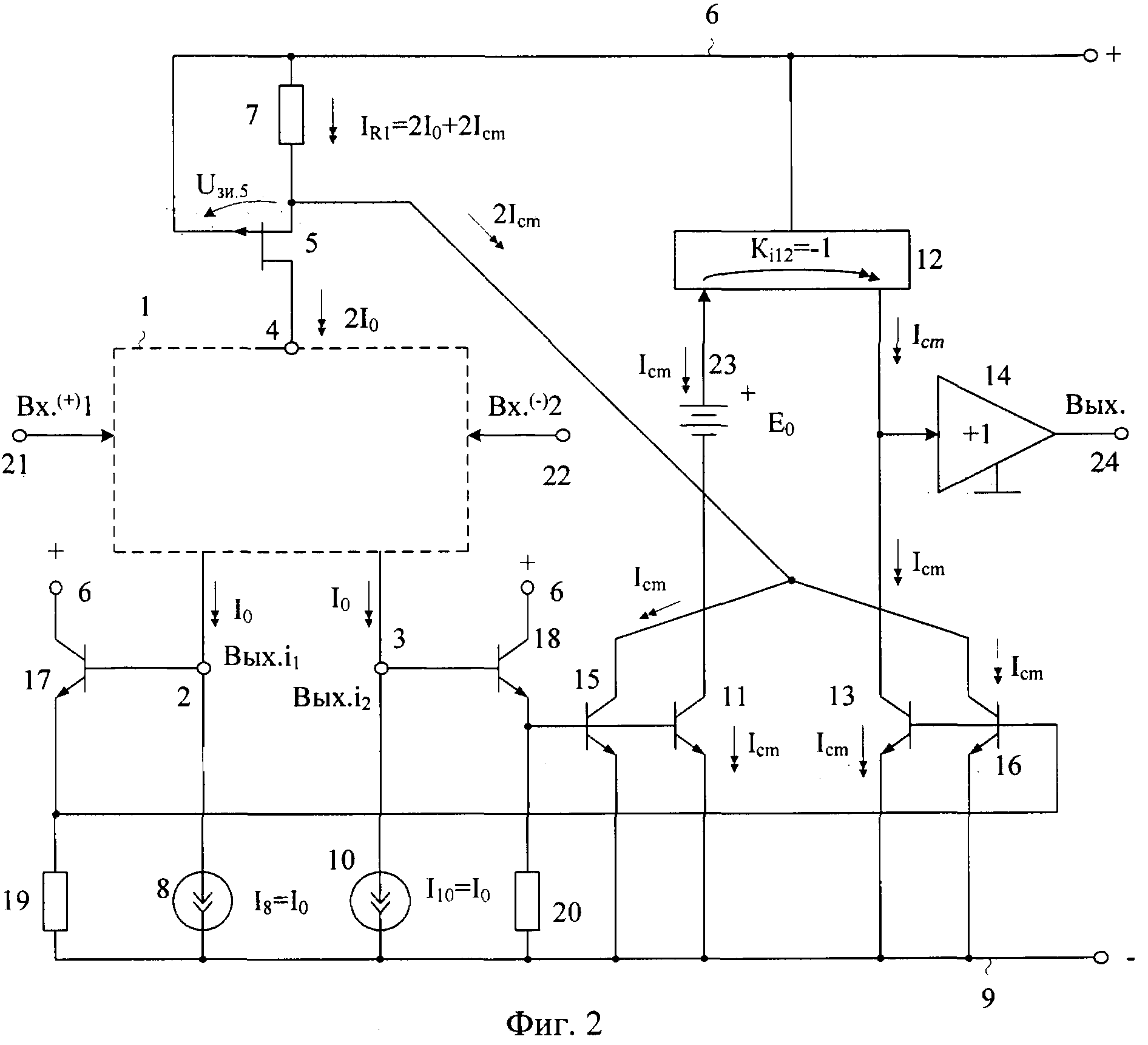

На чертеже фиг. 1 показана схема ОУ-прототипа, а на чертеже фиг. 2 - схема заявляемого ОУ в соответствии с п. 1 формулы изобретения.

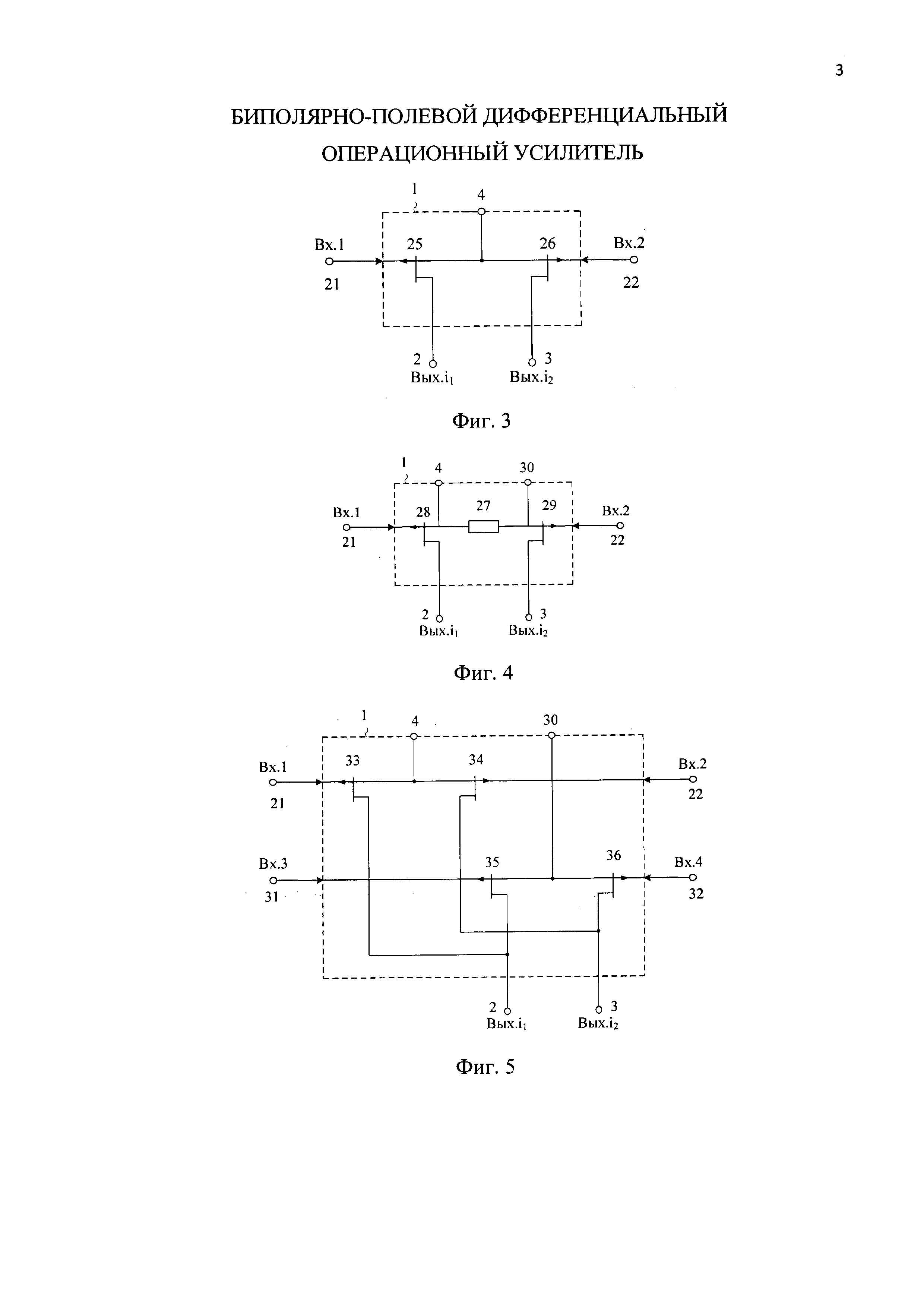

На чертежах фиг. 3, фиг. 4, фиг. 5 показаны варианты выполнения входного дифференциального каскада 1 на полевых транзисторах (фиг. 3 - классическая схема ДК, фиг. 4 - схема ДК с местной отрицательной обратной связью, фиг. 5 - входной дифференциальный каскад 1 с двумя токовыми входами (4 и 30) для установления его статического режима). На основе схемы фиг. 5 и фиг. 2 реализуются мультидифференциальные ОУ [8].

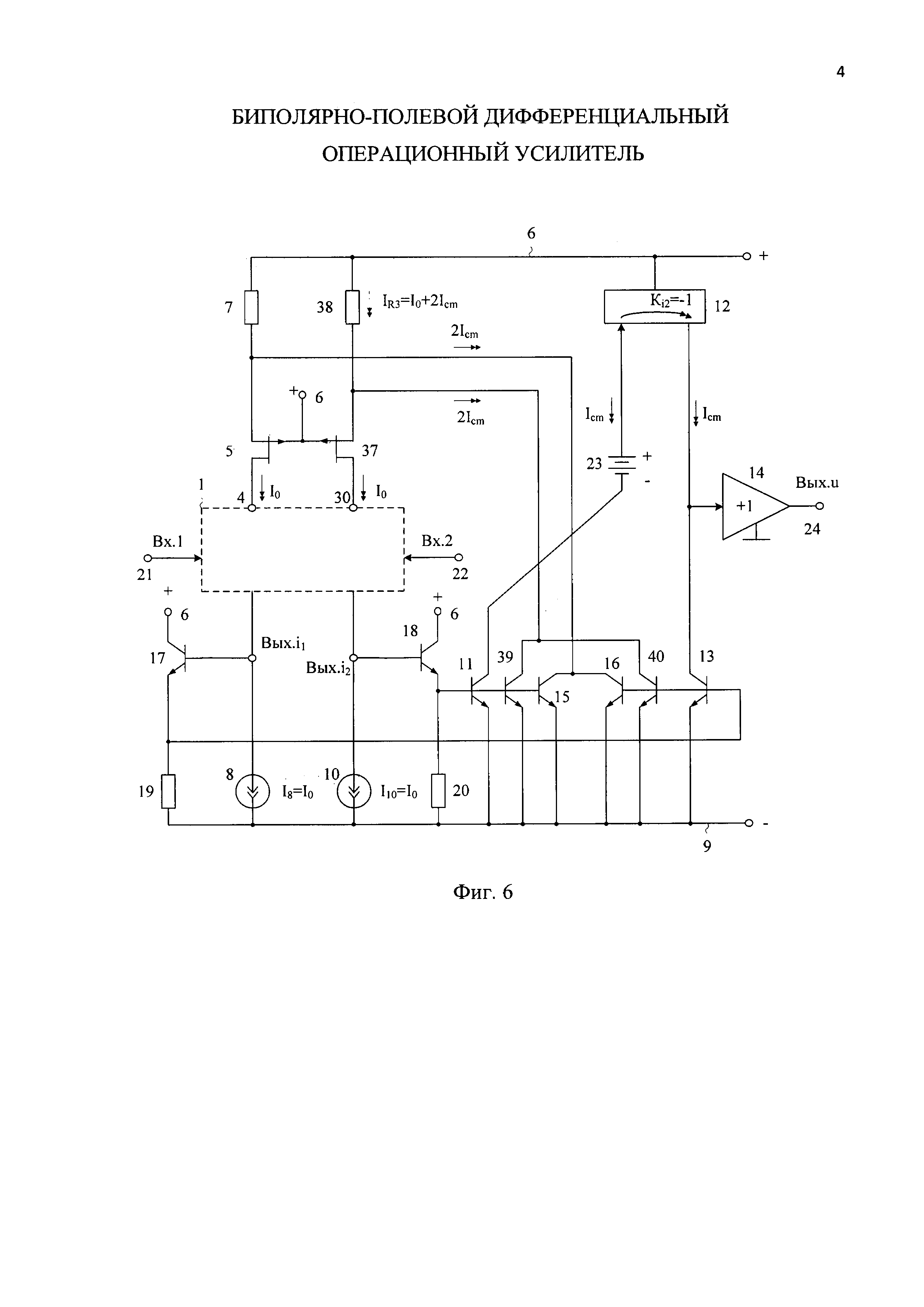

На чертеже фиг. 6 показана схема заявляемого устройства в соответствии с п. 2 формулы изобретения.

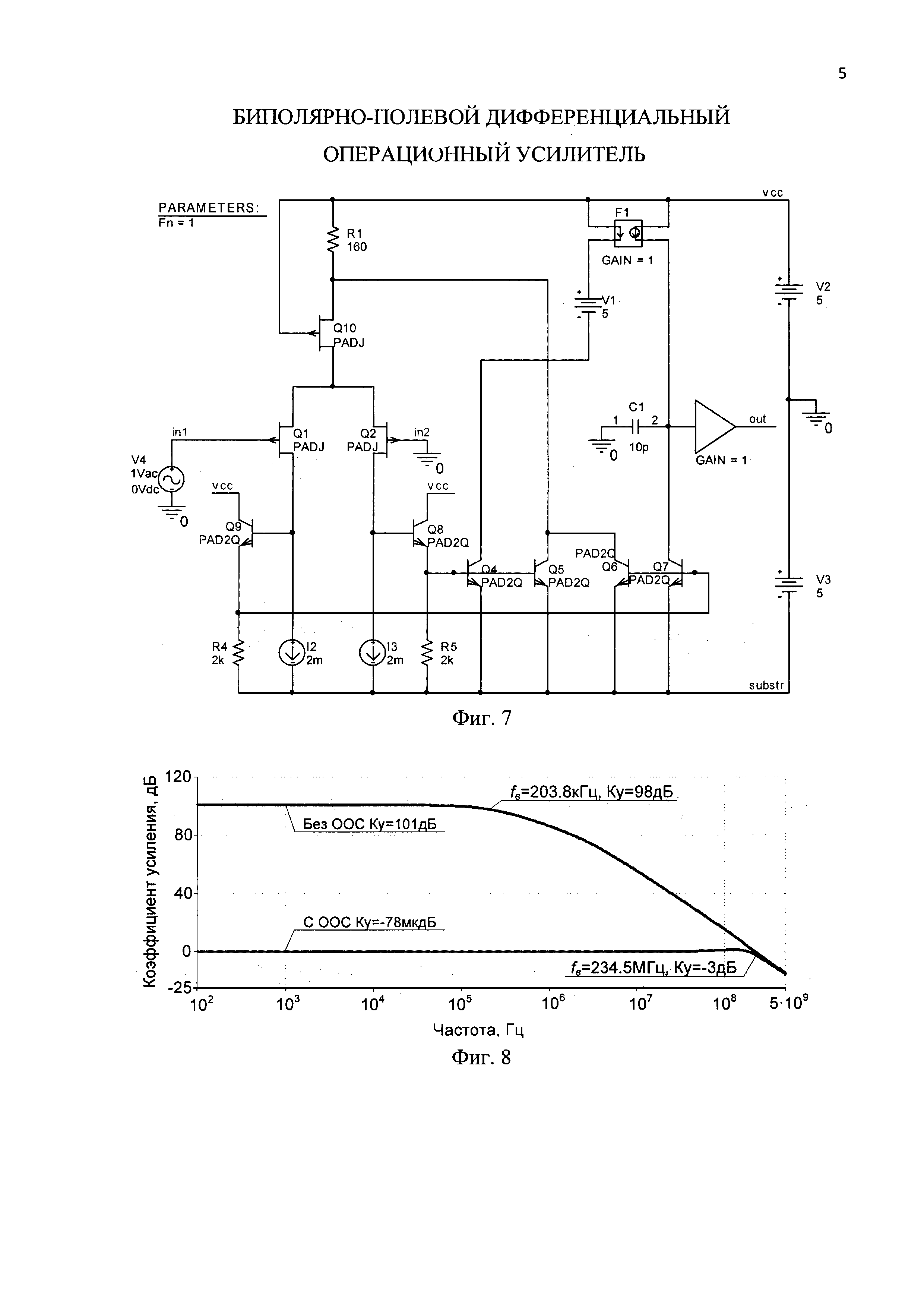

На чертеже фиг. 7 приведена схема заявляемого ОУ фиг. 2 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ОАО «Интеграл» (г. Минск).

На чертеже фиг. 8 показаны амплитудно-частотные характеристики коэффициента усиления по напряжению схемы фиг. 7 без отрицательной обратной связи (верхний график) и с отрицательной обратной связью (нижний график).

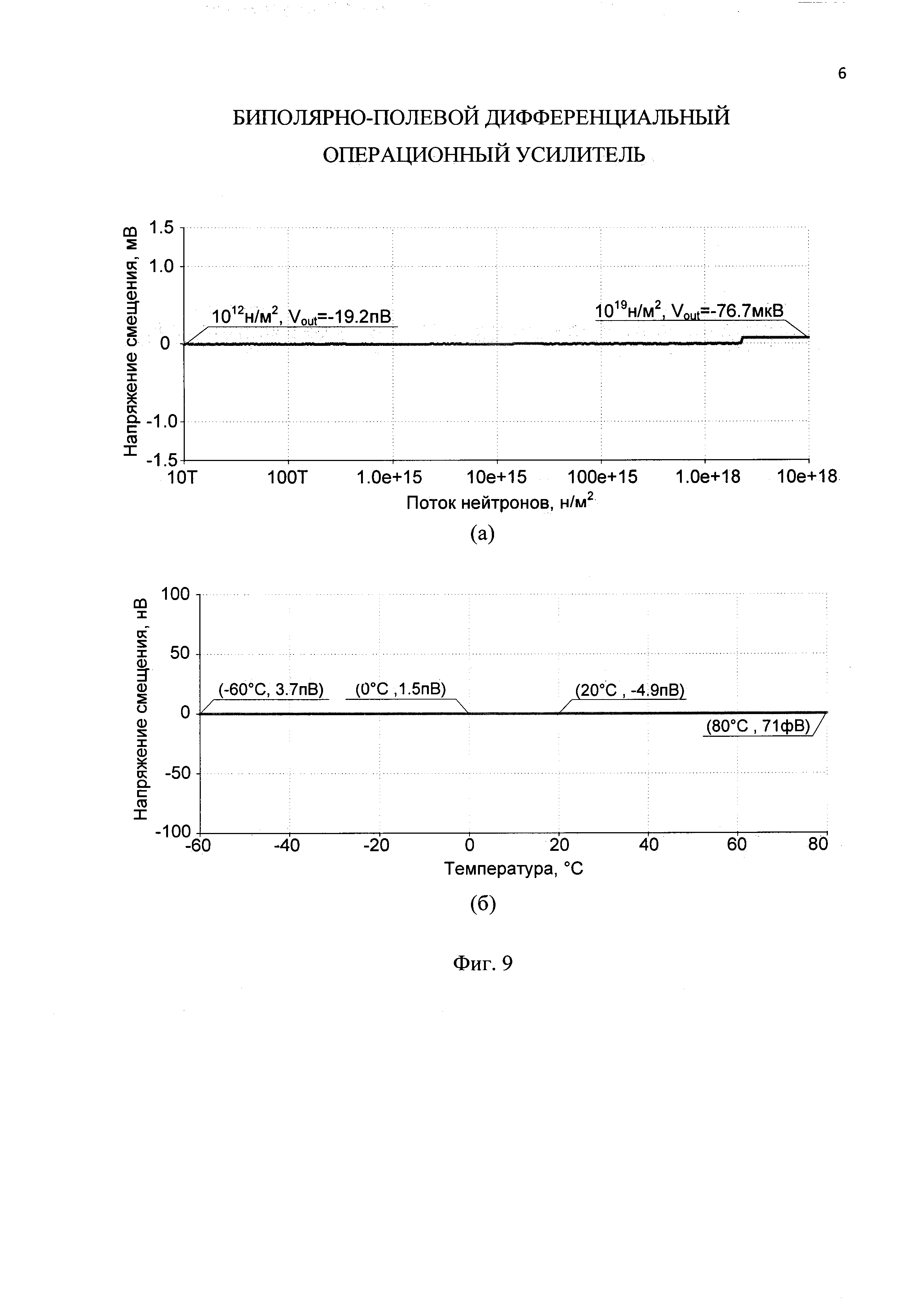

Графики фиг. 9 характеризуют предельные параметры заявляемого устройства по радиационной стойкости и температуре. Данные графики построены для идеальных элементов 12 и 14, при отсутствии разброса параметров элементов, а также при введении симметрирующего элемента 23.

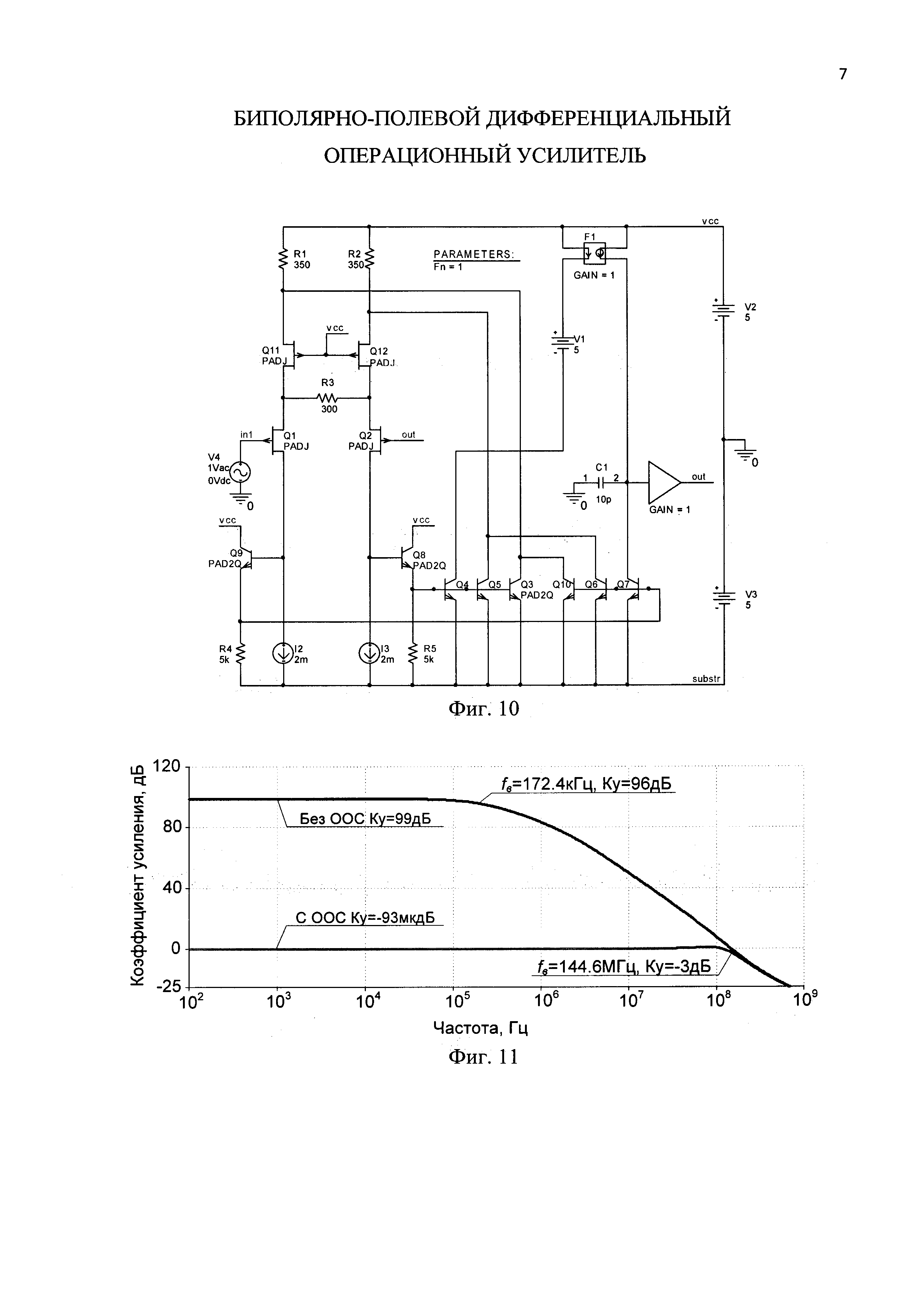

На чертеже фиг. 10 приведена схема ОУ фиг.6 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ОАО «Интеграл» (г. Минск).

На чертеже фиг. 11 показаны амплитудно-частотные характеристики коэффициента усиления по напряжению схемы фиг. 10 без отрицательной обратной связи (верхний график) и с отрицательной обратной связью (нижний график).

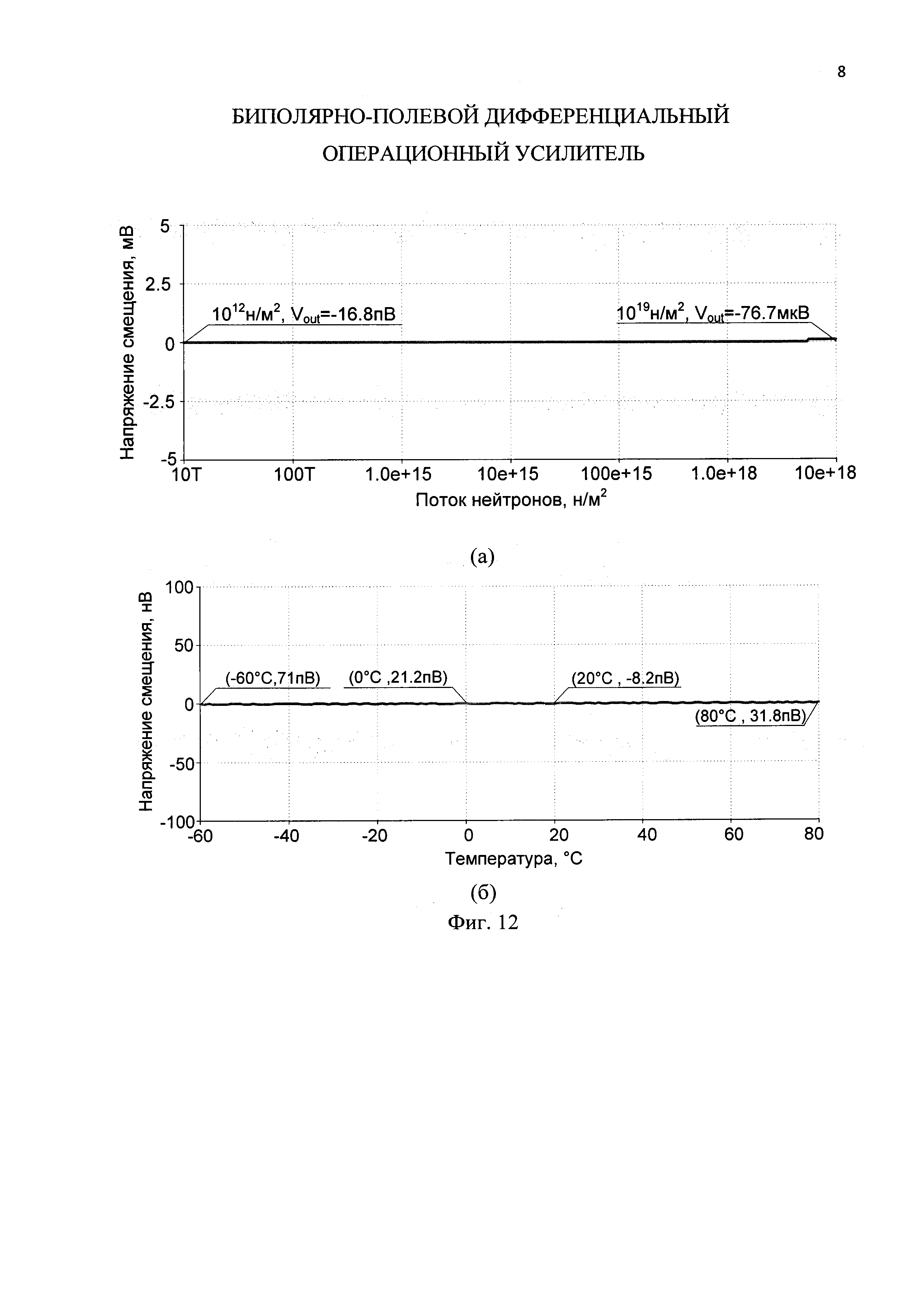

Графики фиг. 12 характеризуют предельные параметры заявляемого устройства по радиационной стойкости и температуре. Данные графики построены для идеальных элементов 12 и 14, при отсутствии разброса параметров транзисторов, а также при введении симметрирующего элемента 23.

Биполярно-полевой дифференциальный операционный усилитель фиг.2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 противофазными токовыми выходами, первый 4 токовый вход для установления статического режима по току транзисторов входного дифференциального каскада 1, подключенный к стоку первого 5 полевого транзистора с управляющим p-n переходом, затвор которого связан с первой 6 шиной источника питания, а исток подключен к первой 6 шине источника питания через первый 7 вспомогательный токостабилизирующий двухполюсник, первый 8 токостабилизирующий двухполюсник, включенный между первым 2 токовым выходом входного дифференциального каскада 1 и второй 9 шиной источника питания, второй 10 токостабилизирующий двухполюсник, включенный между вторым 3 токовым выходом входного дифференциального каскада 1 и второй 9 шиной источника питания, первый 11 выходной транзистор, эмиттер которого подключен ко второй 9 шине источника питания, а коллектор связан со входом токового зеркала 12, второй 13 выходной транзистор, эмиттер которого подключен ко второй 9 шине источника питания, а коллектор связан с выходом токового зеркала 12 и входом буферного усилителя 14, первый 15 и второй 16 вспомогательные транзисторы, коллекторы которых объединены и подключены к истоку первого 5 полевого транзистора с управляющим р-n переходом, а эмиттеры соединены со второй 9 шиной источника питания, причем база первого 15 вспомогательного транзистора соединена с базой первого 11 выходного транзистора, а база второго 16 вспомогательного транзистора соединена с базой второго 13 выходного транзистора. В схему введены первый 17 и второй 18 дополнительные транзисторы, коллекторы которых связаны с первой 6 шиной источника питания, база первого 17 дополнительного транзистора подключена к первому 2 токовому выходу входного дифференциального каскада 1, эмиттер первого 17 дополнительного транзистора связан со второй 9 шиной источника питания через второй 19 вспомогательный токостабилизирующий двухполюсник и соединен с объединенными базами второго 13 выходного транзистора и второго 16 вспомогательного транзистора, база второго 18 дополнительного транзистора подключена ко второму 3 токовому выходу входного дифференциального каскада 1, эмиттер второго 18 дополнительного транзистора связан со второй 9 шиной источника питания через третий 20 вспомогательный токостабилизирующий двухполюсник и соединен с объединенными базами первого 11 выходного транзистора и первого 15 вспомогательного транзистора.

В схеме фиг. 2 входной дифференциальный каскад 1 имеет противофазные потенциальные входы 21 и 22, а также симметрирующий элемент 23, который может выполняться на основе резисторов, источников опорного напряжения и т.п., обеспечивающий минимизацию систематической составляющей напряжения смещения нуля ОУ, обусловленной эффектом Эрли первого 11 и второго 13 выходных транзисторов.

В схеме фиг. 3 входной дифференциальный каскад 1 реализован на полевых транзисторах 25 и 26.

В схеме фиг. 4 входной дифференциальный каскад 1 выполнен на основе резистора местной отрицательной обратной связи 27, полевых транзисторах 28 и 29, а также имеет второй 30 токовый вход для установления статического режима по току транзисторов входного дифференциального каскада 1.

В схеме фиг. 5 входной дифференциальный каскад 1 реализован как элемент мультидифференциального ОУ [8] и содержит первый 31 и второй 32 дополнительные входы ОУ, а также полевые транзисторы 33, 34 и 35, 36. Статический режим транзисторов 35, 36 устанавливается здесь по второму 30 токовому входу.

На чертеже фиг. 6, в соответствии с п. 2 формулы изобретения, входной дифференциальный каскад 1 содержит второй 30 токовый вход для установления статического режима по току транзисторов входного дифференциального каскада 1, подключенный к стоку второго 37 полевого транзистора с управляющим p-n переходом, затвор которого связан с первой 6 шиной источника питания, а исток подключен к первой 6 шине источника питания через четвертый 38 вспомогательный токостабилизирующий двухполюсник, причем исток второго 37 полевого транзистора с управляющим p-n переходом соединен с объединенными коллекторами третьего 39 и четвертого 40 дополнительных транзисторов, эмиттеры которых связаны со второй 9 шиной источника питания, база третьего 39 дополнительного транзистора соединена с базами первого 15 вспомогательного и первого 11 выходного транзисторов, а база четвертого 40 дополнительного транзистора соединена с базами второго 13 выходного и второго 16 вспомогательного транзисторов.

Рассмотрим работу ОУ фиг.2.

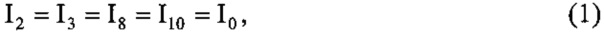

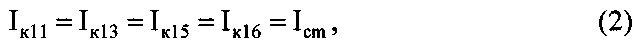

Статический режим транзисторов схемы фиг. 2 устанавливается за счет цепи отрицательной обратной связи по синфазному сигналу, которая организуется первым 15 и вторым 16 вспомогательными транзисторами и источником опорного тока на первом 5 полевом транзисторе, а также первым 17 и вторым 18 дополнительными транзисторами. При этом выходные токи узлов 2 и 3 (I2, I3) и токи коллекторов (Iкi) транзисторов определяются уравнениями

где I8, I10 - токи первого 8 и второго 10 токостабилизирующих двухполюсников;

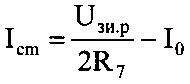

- статический ток коллектора первого 11 и второго 13 выходных транзисторов и первого 15 и второго 16 вспомогательных транзисторов;

- статический ток коллектора первого 11 и второго 13 выходных транзисторов и первого 15 и второго 16 вспомогательных транзисторов;

Uзи.5 - статическое напряжение между затвором и истоком первого 5 полевого транзистора при токе стока, равном Iс=2I0;

I0 - некоторый заданный разработчиком опорный ток, равный, например, 1 мА.

Таким образом, статический режим схемы ОУ фиг. 2 зависит от токов первого 8 и второго 10 токостабилизирующих двухполюсников, которые могут быть выполнены на основе n-p-n транзисторов. В конечном итоге это повышает радиационную стойкость ОУ [6].

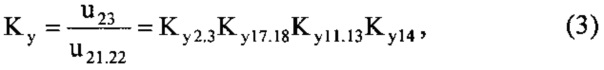

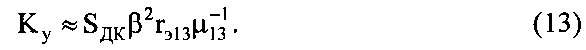

Коэффициент усиления по напряжению (Kу) схемы фиг. 2 определяется произведением

где u23 - напряжение между первым 2 и вторым 3 токовыми выходами ОУ;

u21.22 - входное дифференциальное напряжение ОУ (напряжение между входами 21, 22);

Kу2.3 - коэффициент преобразования входного дифференциального напряжения ОУ (u21.22) в напряжение между первым 2 и вторым 3 токовыми выходами; Kу2.3=u2.3/u21.22;

Kу17.18 - коэффициент преобразования напряжения между первым 2 и вторым 3 токовыми выходами в напряжение uбб между базами первого 11 и второго 13 выходных транзисторов; Kу17.18=uбб/u2.3;

Kу11.13 - коэффициент преобразования напряжения между базами первого 11 и второго 13 выходных транзисторов в напряжение u∑1 на входе буферного усилителя 14; Kу=u∑1/uбб;

Kу14 - коэффициент передачи по напряжению буферного усилителя 14.

Причем Kу17.18≈1, Kу14≈1.

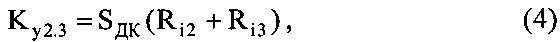

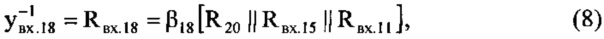

Основное усиление в схеме фиг. 2 обеспечивается первым (Kу2.3) и вторым (Kу11.13) каскадами. При этом

где SДК - крутизна преобразования напряжения между входами 21, 22 входного ДК 1 в выходные токи токовых выходов 2 и 3;

Ri2 - эквивалентное сопротивление в цепи первого 2 токового выхода;

Ri3 - эквивалентное сопротивление в цепи второго 3 токового выхода.

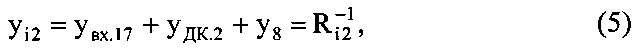

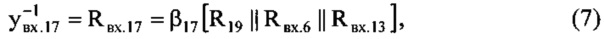

Численные значения Ri2 и Ri3 определяются формулами

где yвх.17 - входная проводимость первого 17 дополнительного транзистора по цепи базы;

yДК.2 - выходная проводимость входного дифференциального каскада 1 по цепи первого 2 токового выхода;

y8 - выходная проводимость первого 8 токостабилизирующего двухполюсника.

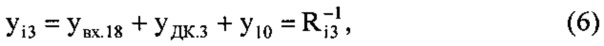

Аналогично для узла 3 можно найти

где yВх.18 - входная проводимость второго 18 дополнительного транзистора по цепи базы;

yДК.3 - выходная проводимость входного дифференциального каскада 1 по цепи второго 3 токового выхода;

y10 - выходная проводимость второго 10 токостабилизирующего двухполюсника.

Если считать, что yДК.1≈0, yДК.2≈0, y8≈0, y10≈0, то из формул (4)-(6) можно найти

где Rвх.15≈β15rэ15, Rвх.11≈β11rэ11, Rвх.13≈β13rэ13, Rвх.16≈ β16rэ16,

rэi, βi - сопротивление эмиттерного перехода и коэффициент усиления по току базы i-го транзистора.

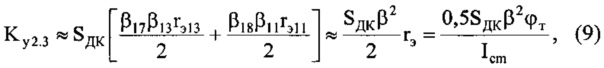

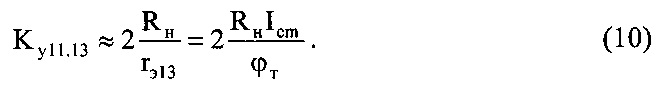

За счет надлежащего выбора сопротивления второго 19 (R19) и третьего 20 (R20) вспомогательных токостабилизирующих двухполюсников можно минимизировать их влияние на Kу2.3. Поэтому для данного случая

где ϕт≈26 мВ - температурный потенциал;

β=β13=β11, rэ=rэ13=rэ11;

Icm - статический ток эмиттера первого 11 и второго 13 выходных транзисторов.

Аналогично можно найти коэффициент усиления по току Kу11.13 промежуточного каскада (первый 11 и второй 13 выходные транзисторы)

где Rн - эквивалентное сопротивление в цепи коллектора (∑1) второго 13 выходного транзистора.

Таким образом, коэффициент усиления разомкнутого ОУ фиг. 2

Приближенно можно считать, что эквивалентное сопротивление Rн на входе буферного усилителя 14

где μ13 - коэффициент внутренней обратной связи второго 13 выходного транзистора.

Таким образом, в схеме фиг. 2 разомкнутый коэффициент усиления определяется произведением

Если считать, что μ13≈10-3, β=β17≈β13=100,  , то в заявляемом ОУ реализуется коэффициент усиления по напряжению не менее чем 90÷100 дБ.

, то в заявляемом ОУ реализуется коэффициент усиления по напряжению не менее чем 90÷100 дБ.

Данный вывод подтверждается результатами компьютерного моделирования фиг. 8, фиг. 11.

Анализ графиков фиг. 8 показывает, что введение дополнительных элементов в схеме фиг. 2 в соответствии с формулой изобретения повышает коэффициент усиления по напряжению ОУ до 101 дБ. Этого достаточно для его многих применений в устройствах автоматики и телекоммуникаций. Причем заявляемая схема ОУ характеризуется высокой стабильностью нулевого уровня (фиг. 12).

Реализация ОУ в соответствии с п. 2 формулы изобретения позволяет создавать на его основе так называемые мультидифференциальные операционные усилители (например, фиг. 5, фиг. 2), имеющие уникальные схемы включения [8], не реализуемые на основе классических ОУ.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с прототипом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US №3.959.733.

2. Патент US №6.157.255.

3. Патент RU №2331970 fig. 1.

4. Патентная заявка US 2007/0096814.

5. Патент US №5.610.547.

6. Элементная база радиационно-стойких информационно-измерительных систем: монография / Н.Н. Прокопенко, О.В. Дворников, С.Г. Крутчинский; под общ. ред. д.т.н. проф. Н.Н. Прокопенко; ФГБОУ ВПО «Южно-Рос. гос. ун-т. экономики и сервиса». - Шахты: ФГБОУ ВПО «ЮРГУЭС», 2011. - 208 с.

7. Операционные усилители с непосредственной связью каскадов / В.И. Анисимов, М.В. Капитонов, Н.Н. Прокопенко, Ю.М. Соколов - Л.: Энергия. Ленингр. отд-ние, 1979. - 151 с.

8. Основные свойства, параметры и базовые схемы включения мультидифференциальных операционных усилителей с высокоимпедансным узлом / Н.Н. Прокопенко, О.В. Дворников, П.С. Будяков // Электронная техника. Серия 2. Полупроводниковые приборы. Выпуск 2 (233), МоскваЮ ОАО «Пульсар», 2014 г. С. 53-64.