Результат интеллектуальной деятельности: МНОГОВЫХОДНОЕ УСТРОЙСТВО ПРИОРИТЕТА

Вид РИД

Изобретение

Изобретение относится к области вычислительной техники и может быть использовано для арбитража в системах обработки информации при организации передачи данных между устройствами, а также при сжатии данных, для упаковки и распаковки данных.

Известны приоритетные шифраторы (Дж. Ф. Уэйкерли. Проектирование цифровых устройств. В 2-х томах. - М.: Постмаркет, 2002. - 1088 с., с. 440-445; Лехин С.Н. Схемотехника ЭВМ. - СПб.: БХВ-Петербург, 2010. - 672 с., с. 213-220; Угрюмов Е.П. Цифровая схемотехника. - СПб.: БХВ-Петербург, 2000. - 528 с., с. 50-53), в которых формируется двоичный код номера устройства старшего приоритета.

Известен двойной приоритетный шифратор (Дж. Ф. Уэйкерли. Проектирование цифровых устройств. В 2-х томах. - М.: Постмаркет, 2002. - 1088 с., рис. 6.6, с. 561-562), содержащий два блока приоритетного шифратора, дешифратор, группу элементов И-НЕ и группу элементов НЕ. Данное устройство определяет не только сигнал с наивысшим приоритетом, но также сигнал «со вторым по старшинству приоритетом».

Недостатком данных устройств является необходимость преобразования кода номера в соответствующий сигнал в виде унитарного кода «1 из N» обращения к устройству со старшим приоритетом, например, с помощью двоичного дешифратора.

Известен указатель старшей единицы (Угрюмов Е.П. Цифровая схемотехника. - СПб.: БХВ-Петербург, 2000. - 528 с., рис. 2.8 с. 50-54), содержащий группу элементов И и группу элементов запрета И с одним инверсным входом. В данном устройстве реализована цепочечная схема передачи сигнала опроса путем последовательного опроса, начиная со старшего разряда, и прекращения дальнейшего опроса при выявлении первой же единицы.

Известен указатель старшей единицы (Схемотехника ЭВМ. Сборник задач: учебное пособие. М.: НИЯУ МИФИ, 2012. - 240 с., рис. 53, с. 55-56), содержащий группу элементов ИЛИ, объединенных в цепочку, и группу элементов запрета И с одним инверсным входом.

Известно многоканальное устройство для приоритетного обслуживания запросов (RU №2322689 С2, МПК G06F 9/50, заявлен 05.06.2006, опубликован 20.04.2008, Бюл. №11), содержащее генератор импульсов, два элемента И, два счетчика, схему сравнения, регистр, элемент НЕ, три элемента ИЛИ, элемент ИЛИ-НЕ, сумматор по модулю два, элемент задержки, дешифратор, формирователь импульсов и M каналов, каждый из которых содержит элемент И, элемент ИЛИ, элемент И с прямыми и инверсными входами. В данном устройстве реализована циклическая дисциплина обслуживания запросов и совмещение во времени этапа обслуживания запроса и этапа поиска следующего запроса на обслуживание.

Известно многоканальное устройство для подключения абонентов к общей магистрали (RU №2444780 C1, МПК G06F 13/37, заявлено 04.02.2011, опубликовано 10.03.2012, Бюл. №7), содержащее узел анализа приоритета, элемент НЕ устройства, тактовый вход, n запросных входов, n информационных выходов и n каналов, при этом каждый канал содержит элемент И, два элемента ИЛИ, элемент ИЛИ-НЕ, триггер, счетчик и два узла анализа приоритета, причем каждый узел анализа приоритета содержит элемент И, элемент ИЛИ, элемент НЕ, элемент ИЛИ-НЕ, информационный выход канала и запросный вход канала, который соединен с первым входом первого элемента И.

Недостатком данных устройств является определение только одного старшего приоритета.

К причинам, препятствующим достижению указанного ниже технического результата, относится отсутствие средств, обеспечивающих одновременную выдачу сигналов по группам с последовательным по старшинству приоритетом.

Техническим результатом изобретения является расширение функциональных возможностей в части формирования R групп указателей старших единиц в унитарном коде «1 из Ν» в порядке старшинства приоритетов.

Указанный технический результат при осуществлении изобретения достигается тем, что многовыходное устройство приоритета содержит группу из N внешних входов запроса Ζ0, Ζ1, …, Ζ(Ν-1) (где высший приоритет имеет вход Ζ0), R групп внешних выходов U указателей старшей единицы в унитарном коде «1 из Ν» (где R≤N, причем 0-я группа имеет высший приоритет (ранг)), причем N внешних входов запроса разделены на К групп (где К= ]N/4[ - большее целое), введены К модулей групп 10, 11, …, 1(К-1), соединенные последовательно между собой шинами 20, 21, …, 2(К-2) переноса суммы,

при этом 0-й модуль групп 10 содержит первый полусумматор 3, второй одноразрядный сумматор 4 с входом переноса CI, первый дешифратор 5, который содержит один адресный вход и два выхода, второй дешифратор 6, который содержит два адресных входа и три выхода, третий дешифратор 7, который содержит два адресных входа и четыре выхода, при этом первый 5, второй 6 и третий 7 дешифраторы имеют вход разрешения Е, а также 0-й модуль содержит четыре входа запроса модуля, четыре шины U внешних выходов и двухразрядную выходную шину 20 переноса суммы,

каждый i-й модуль групп 11, 12, …, 1(К-1), начиная с первого до (К-1) (где i=1, 2, …, К-1), содержит третий одноразрядный сумматор 8i с входом переноса CI, четвертый сумматор 9i без входа переноса, пятый сумматор 10i с входом переноса CI, шестой сумматор 11i без входа переноса и седьмой сумматор 12i с входом переноса CI, четвертый 13i, пятый 14i, шестой 15i и седьмой 16i дешифраторы, каждый из которых содержит группу адресных входов и вход разрешения Е, а также каждый i-й модуль групп содержит пять входов запроса i-го модуля, четыре шины U внешних выходов, входную шину 2(i-1) переноса суммы и выходную шину 2i переноса суммы,

причем в 0-м модуле групп 10 четыре входа запроса модуля соединены соответственно с четырьмя внешними первыми входами запроса Z0, Z1, Z2, Z3 устройства, первый вход запроса 0-го модуля соединен с адресным входом первого дешифратора 5, вход разрешения Ε которого соединен со вторым входом запроса 0-го модуля, первый и второй входы запроса 0-го модуля также соединены с входами суммирования первого полусумматора 3, выход суммы и переноса СО которого соединены с соответствующими адресными входами второго дешифратора 6, вход разрешения Ε которого соединен с третьим входом запроса 0-го модуля, первый и второй входы запроса 0-го модуля также соединены с входами суммирования второго одноразрядного сумматора 4, вход переноса CI которого соединен с третьим входом запроса 0-го модуля, выход суммы и переноса СО второго сумматора 4 соединены с соответствующими адресными входами третьего дешифратора 7, вход разрешения Ε которого соединен с четвертым входом запроса 0-го модуля, при этом первый вход запроса 0-го модуля является одноразрядной нулевой внешней шиной U0[0] 0-го модуля, два выхода первого дешифратора 5 являются соответственно двухразрядной первой шиной U1[0:1] 0-го модуля, три выхода второго дешифратора 6 являются соответственно трехразрядной второй шиной U2[0:2] 0-го модуля, четыре выхода третьего дешифратора 7 являются соответственно третьей четырехразрядной шиной U3[0:3] 0-го модуля, кроме того, выход суммы и переноса СО второго одноразрядного сумматора 4 являются двухразрядными выходами шины 20 переноса суммы 0-го модуля,

причем в каждом i-м модуле групп 11, 12, …, 1(К-1), начиная с первого до (К-1) (где i=1, 2, …, К-1), пять входов запроса i-го модуля соединены с соответствующими внешними входами запроса Z(4*(i-1)+3), Z(4*i), Z(4*i+1), Z(4*i+2), Z(4*i+3) устройства, входная шина 2(i-1) переноса суммы i-го модуля соединена с входами первых слагаемых четвертого 9i, пятого 10i, шестого 11i и седьмого 12i сумматоров, младший разряд второго слагаемого четвертого сумматора 9i соединен с первым входом Z(4*(i-1)+3) запроса i-го модуля, а на остальных старших входах второго слагаемого установлены нулевые значения, выходы суммы и выход переноса СО четвертого сумматора 9i соединены с соответствующими адресными входами четвертого дешифратора 13i, вход разрешения Ε которого соединен со вторым входом Z(4*i) запроса i-го модуля,

младший разряд второго слагаемого пятого сумматора 10i соединен с первым входом Z(4*(i-1)+3) запроса i-го модуля, а на остальных старших входах второго слагаемого установлены нулевые значения, вход переноса CI пятого сумматора 10i соединен со вторым входом Z(4*i) запроса i-го модуля, выходы суммы и выход переноса СО пятого сумматора 10i соединены с соответствующими адресными входами пятого дешифратора 14i, вход разрешения Ε которого соединен с третьим входом Z(4*i+1) запроса i-го модуля,

первый Z(4*(i-1)+3) и второй Z(4*i) входы запроса i-го модуля также соединены с входами слагаемых третьего одноразрядного сумматора 8i, вход переноса СО которого соединен с третьим входом Z(4*i+1) запроса i-го модуля, а выход суммы и выход переноса СО третьего одноразрядного сумматора 8i соединены с соответствующими младшими входами шестого 11i и седьмого 12i сумматоров, у которых на остальных старших входах вторых слагаемых установлены нулевые значения,

выходы суммы и переноса СО шестого сумматора 11i соединены с соответствующими адресными входами шестого дешифратора 15i, вход разрешения Ε которого соединен с четвертым входом Z(4*i+2) запроса i-го модуля,

вход переноса CI седьмого сумматора 12i соединен с четвертым входом Z(4*i+2) запроса i-го модуля, выходы суммы и переноса СО седьмого сумматора 12i соединены с соответствующими адресными входами седьмого дешифратора 16i, вход разрешения Ε которого соединен с пятым Z(4*i+3) входом запроса i-го модуля, кроме того, выходы суммы и переноса СО седьмого сумматора 12i являются выходами шины 2i переноса суммы i-го модуля,

при этом в каждом i-м модуле групп выходы четвертого дешифратора 13i являются первой выходной шиной i-го модуля, содержат 4*i+1≤R разрядов и являются шиной U(4*i) внешних выходов устройства, выходы пятого дешифратора 14i являются второй выходной шиной i-го модуля, содержат 4*i+2≤R разрядов и являются шиной U(4*i+1) внешних выходов устройства, выходы шестого дешифратора 15i являются третьей выходной шиной i-го модуля, содержат 4*i+3≤R разрядов и являются шиной U(4*i+2) внешних выходов устройства, выходы седьмого дешифратора 16i являются четвертой выходной шиной i-го модуля, содержат 4*i+4≤R разрядов и являются шиной U(4*i+3) внешних выходов устройства,

при этом нулевые разряды выходных шин U[0] модулей групп являются группой 0-го ранга высшего приоритета указателей старшей единицы в унитарном коде «1 из N» внешних выходов устройства, первые разряды выходных шин U[1] модулей групп являются группой 1-го ранга указателей старшей единицы в унитарном коде «1 из N» внешних выходов устройства, …, (R-1)-e разряды выходных шин U[R-1] модулей групп являются группой (R-1)-го ранга младшего приоритета указателей старшей единицы в унитарном коде «1 из N» внешних выходов устройства.

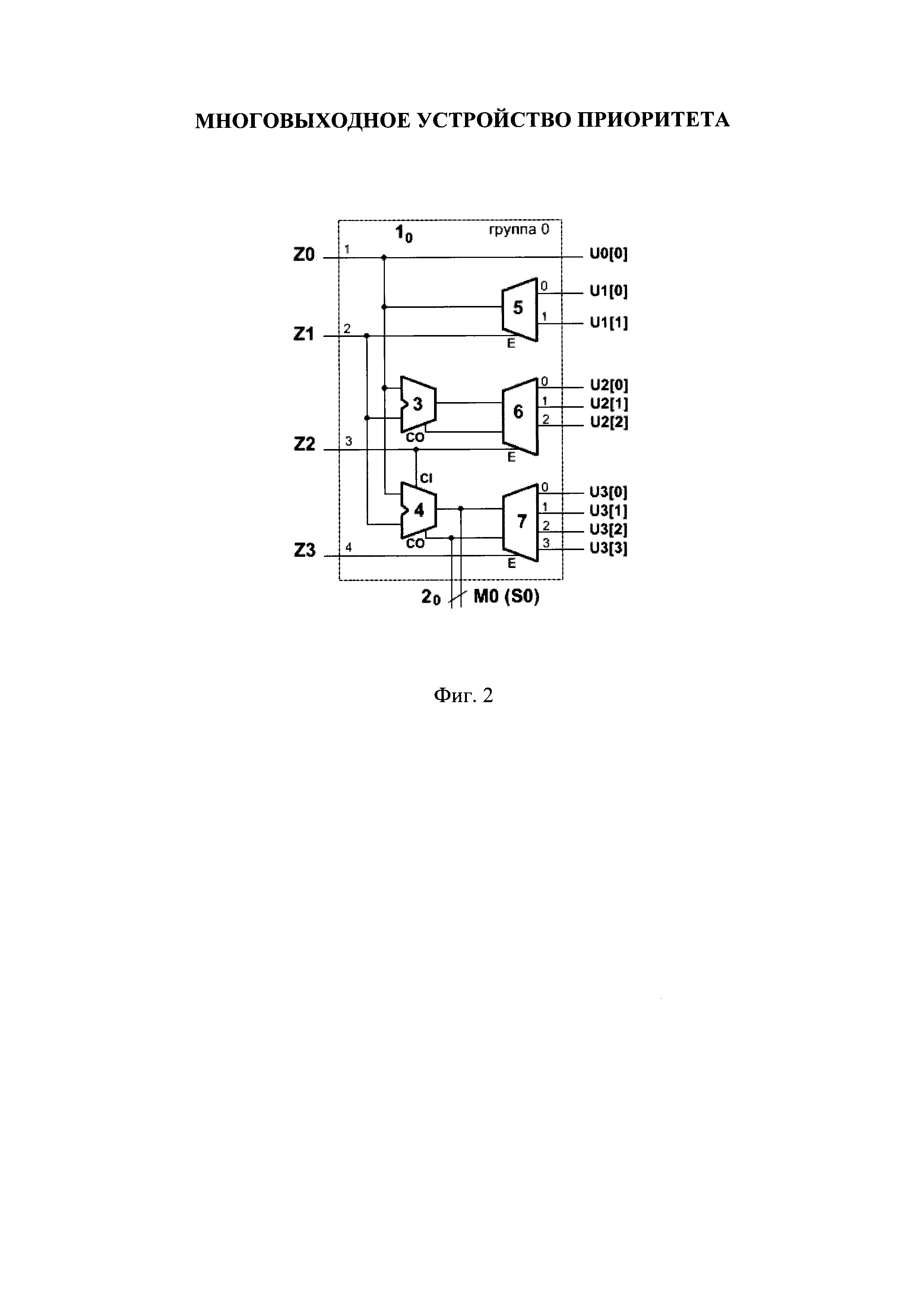

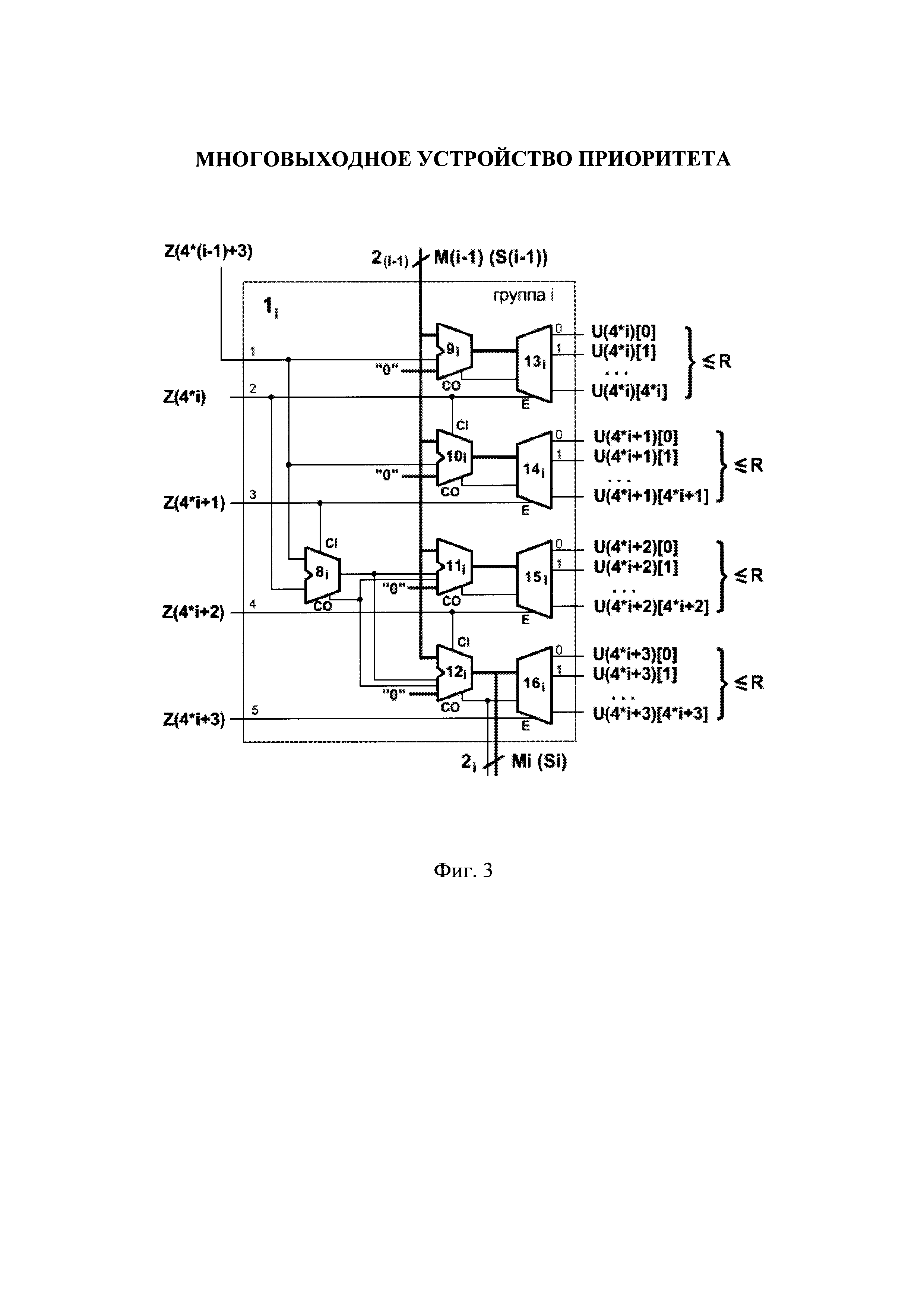

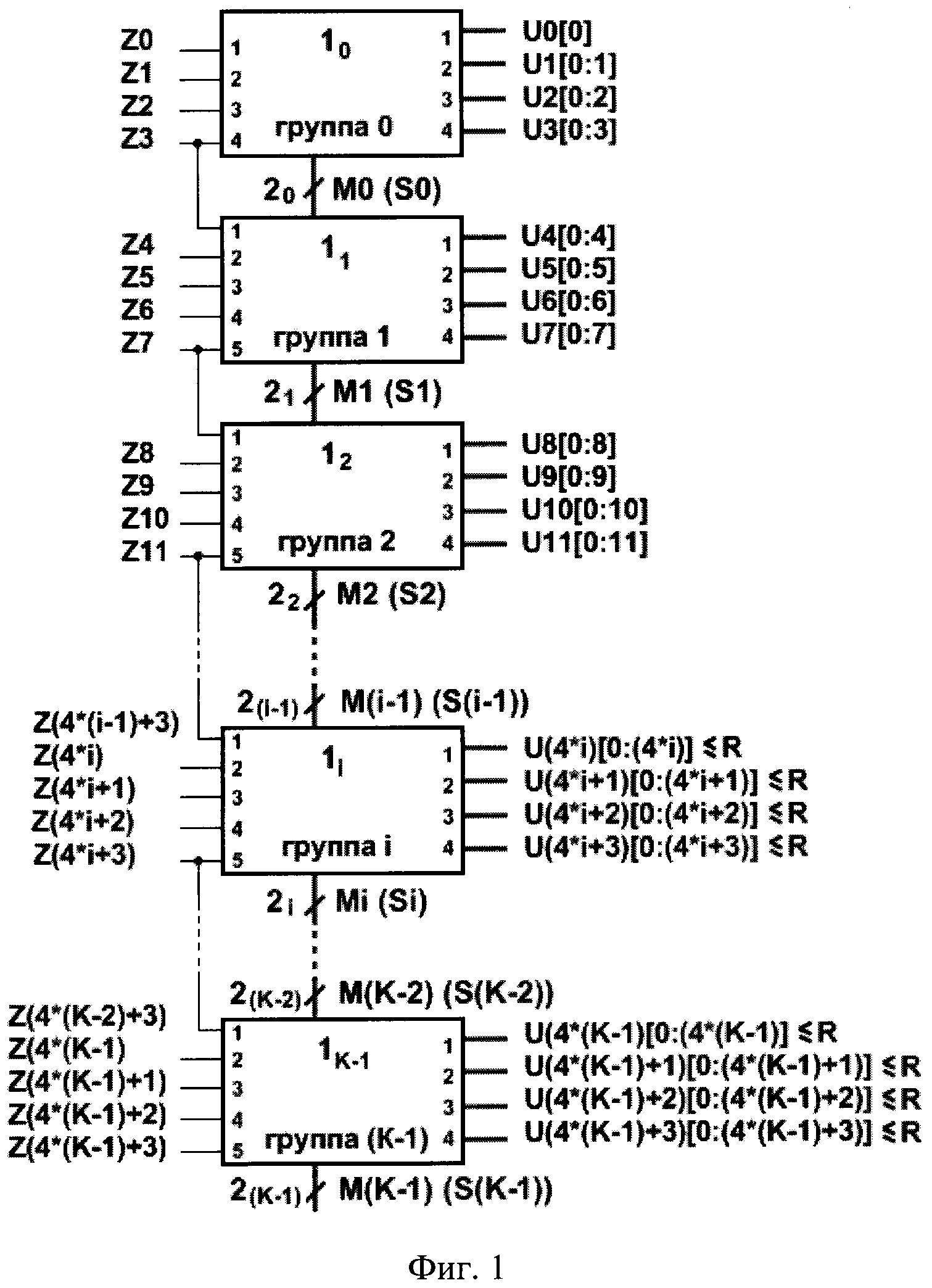

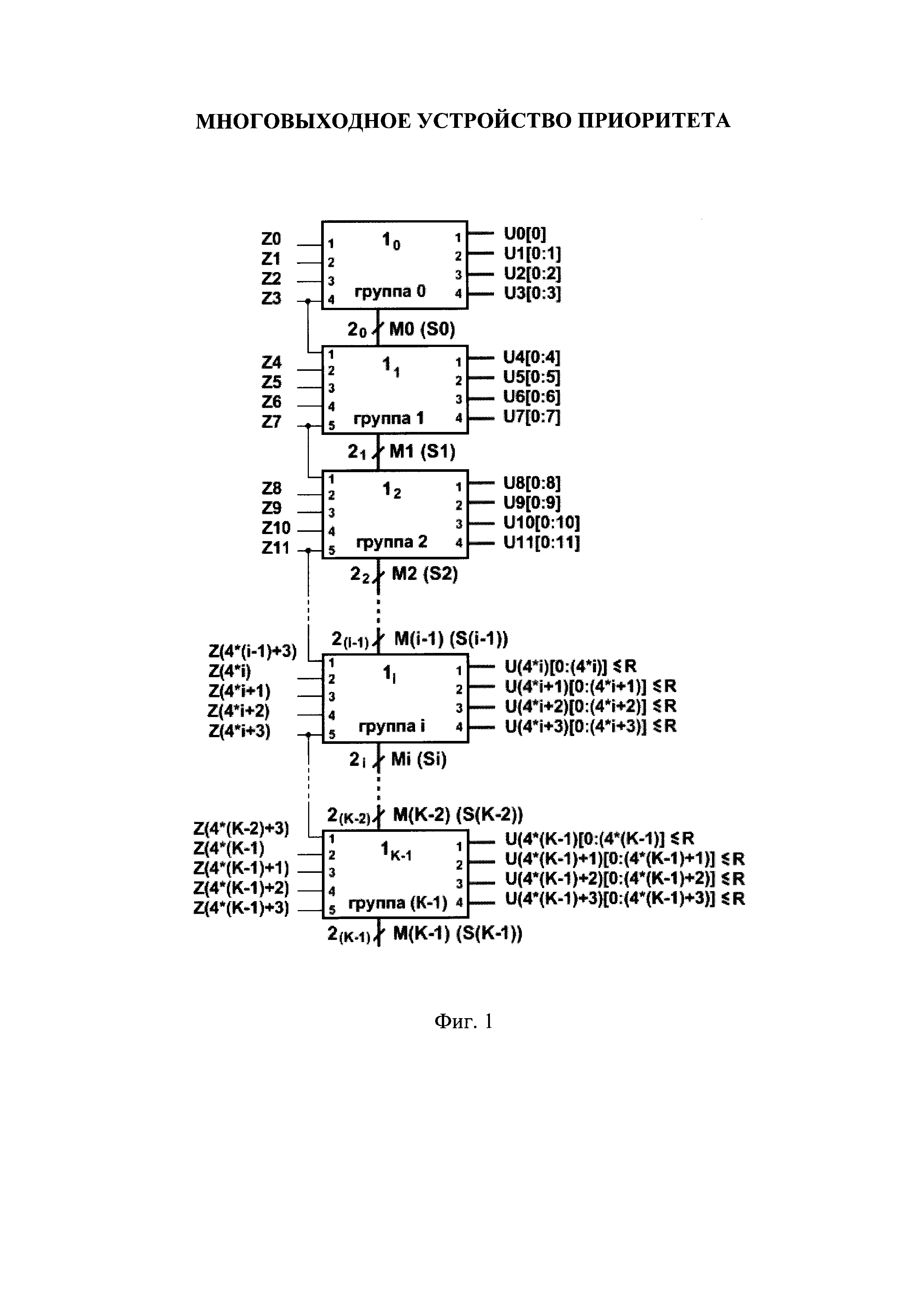

На фиг. 1 представлена схема предлагаемого многовыходного устройства приоритета. На фиг. 2 приведена схема 0-го модуля группы. На фиг. 3 приведена схема i-го модуля группы.

На фиг. 1-3 введены следующие обозначения:

Z0, Z1, …, Z(N-1) - группа из N внешних входов запроса (высший приоритет имеет вход Z0);

К - количество групп запросов, где К= ]N/4[ - большее целое;

UV - шины внешних выходов устройства, где V=0, 1, …, N-1;

U[L] - группы внешних выходов указателей старшей единицы в унитарном коде «1 из N», где L - группа (ранг) приоритета (L=0, 1, …, R-1), причем 0-я группа имеет высший приоритет (ранг);

R - количество групп (рангов) указателей старшей единицы (0-й ранг имеет высший приоритет);

10, 11, … 1(К-1) - модули групп;

20, 21,..., 2(К-1) - шины переносов суммы Si разрядностью Mi;

Элементы 0-й группы:

3 - первый полусумматор;

4 - второй одноразрядный сумматор с входом переноса CI;

5 - первый дешифратор, содержит один адресный вход, два выхода и вход разрешения Е);

6 - второй дешифратор, содержит два адресных входа, три выхода и вход разрешения Е;

7 - третий дешифратор, содержит два адресных входа, четыре выхода и вход разрешения Е;

Элементы i -й группы:

i - номер группы, где i=1, …, К-1;

Si - сумма единиц на шине переносов из i -й группы, где Si≤4*i+3;

Mi - разрядность шины переносов из i -й группы, где Mi=]log2 (max Si)[ - большее целое;

8i - третий одноразрядный сумматор с входом переноса CI;

9i - четвертый сумматор без входа переноса;

10i - пятый сумматор с входом переноса CI;

11i - шестой сумматор без входа переноса;

12i - седьмой сумматор с входом переноса CI;

13i - четвертый дешифратор, содержит Mi адресных входов, (4*i+1)≤R выходов, Ε - вход разрешения;

14i - пятый дешифратор, содержит Mi адресных входов, (4*i+2)≤R выходов, Ε - вход разрешения;

15i - шестой дешифратор содержит Mi адресных входов, (4*i+3)≤R выходов, Ε - вход разрешения;

16i - седьмой дешифратор содержит Mi адресных входов, (4*i+4)≤R выходов, Ε - вход разрешения.

Многовыходное устройство приоритета содержит группу из N внешних входов запроса Ζ0, Ζ1, …, Ζ(Ν-1) (где высший приоритет имеет вход Ζ0), R групп внешних выходов U указателей старшей единицы в унитарном коде «1 из N» (где R≤N, причем 0-я группа имеет высший приоритет (ранг)), причем N внешних входов запроса разделены на К групп (где К= ]N/4[ - большее целое), введены К модулей групп 10, 11, …, 1(К-1), соединенные последовательно между собой шинами 20, 21, …, 2(К-2) переноса суммы.

Нулевой модуль групп 10 содержит первый полусумматор 3, второй одноразрядный сумматор 4 с входом переноса CI, первый дешифратор 5, который содержит один адресный вход и два выхода, второй дешифратор 6, который содержит два адресных входа и три выхода, третий дешифратор 7, который содержит два адресных входа и четыре выхода. При этом первый 5, второй 6 и третий 7 дешифраторы имеют вход разрешения Е, а также 0-й модуль содержит четыре входа запроса модуля, четыре шины U внешних выходов и двухразрядную выходную шину 20 переноса суммы.

Каждый i-й модуль групп 11, 12, …, 1(К-1), начиная с первого до (К-1) (где i=1, 2, …, К-1), содержит третий одноразрядный сумматор 8i с входом переноса CI, четвертый сумматор 9i без входа переноса, пятый сумматор 10i с входом переноса CI, шестой сумматор 11i без входа переноса и седьмой сумматор 12i с входом переноса CI, четвертый 13i, пятый 14i, шестой 15i и седьмой 16i дешифраторы, а также пять входов запроса i-го модуля, четыре шины U внешних выходов, входную шину 2(i-1) переноса суммы и выходную шину 2i переноса суммы. Первый 13i, второй 14i, третий 15i и четвертый 16i дешифраторы содержат группу адресных входов и вход разрешения Е.

В 0-м модуле групп 10 четыре входа запроса модуля соединены соответственно с четырьмя внешними первыми входами запроса Z0, Z1, Z2, Z3 устройства. Первый вход запроса 0-го модуля соединен с адресным входом первого дешифратора 5, вход разрешения Ε которого соединен со вторым входом запроса 0-го модуля. Первый и второй входы запроса 0-го модуля также соединены с входами суммирования первого полусумматора 3, выход суммы и переноса СО которого соединены с соответствующими адресными входами второго дешифратора 6, вход разрешения Ε которого соединен с третьим входом запроса 0-го модуля. Первый и второй входы запроса 0-го модуля также соединены с входами суммирования второго одноразрядного сумматора 4, вход переноса CI которого соединен с третьим входом запроса 0-го модуля. Выход суммы и переноса СО второго сумматора 4 соединены с соответствующими адресными входами третьего дешифратора 7, вход разрешения Ε которого соединен с четвертым входом запроса 0-го модуля. При этом первый вход запроса 0-го модуля является одноразрядной нулевой внешней шиной U0[0] 0-го модуля, два выхода первого дешифратора 5 являются соответственно двухразрядной первой шиной U1[0:1] 0-го модуля, три выхода второго дешифратора 6 являются соответственно трехразрядной второй шиной U2[0:2] 0-го модуля, четыре выхода третьего дешифратора 7 являются соответственно третьей четырехразрядной шиной U3[0:3] 0-го модуля. Кроме того, выход суммы и переноса СО второго одноразрядного сумматора 4 являются двухразрядными выходами шины 20 переноса суммы 0-го модуля,

В каждом i-м модуле групп 11, 12, …, 1(К-1), начиная с первого до (К-1) (где i=1, 2, …, К-1), пять входов запроса i-го модуля соединены с соответствующими внешними входами запроса Z(4*(i-1)+3), Z(4*i), Z(4*i+1), Z(4*i+2), Z(4*i+3) устройства. Входная шина 2(i-1) переноса суммы i-го модуля соединена с входами первых слагаемых четвертого 9i, пятого 10i, шестого 11i и седьмого 12i сумматоров. Младший разряд второго слагаемого четвертого сумматора 9i соединен с первым входом Z(4*(i-1)+3) запроса i-го модуля, а на остальных старших входах второго слагаемого установлены нулевые значения. Выходы суммы и выход переноса СО четвертого сумматора 9i соединены с соответствующими адресными входами четвертого дешифратора 13i, вход разрешения Ε которого соединен со вторым входом Z(4*i) запроса i-го модуля.

Младший разряд второго слагаемого пятого сумматора 10i соединен с первым входом Z(4*(i-1)+3) запроса i-го модуля, а на остальных старших входах второго слагаемого установлены нулевые значения. Вход переноса CI пятого сумматора 10i соединен со вторым входом Z(4*i) запроса i-го модуля. Выходы суммы и выход переноса СО пятого сумматора 10i соединены с соответствующими адресными входами пятого дешифратора 14i, вход разрешения Ε которого соединен с третьим входом Z(4*i+1) запроса i-го модуля.

Первый Z(4*(i-1)+3) и второй Z(4*i) входы запроса i-го модуля также соединены с входами слагаемых третьего одноразрядного сумматора 8i, вход переноса СО которого соединен с третьим входом Z(4*i+1) запроса i-го модуля. Выход суммы и выход переноса СО третьего одноразрядного сумматора 8i соединены с соответствующими младшими входами шестого 11i и седьмого 12i сумматоров, у которых на остальных старших входах вторых слагаемых установлены нулевые значения.

Выходы суммы и переноса СО шестого сумматора 11i соединены с соответствующими адресными входами шестого дешифратора 15i, вход разрешения Ε которого соединен с четвертым входом Z(4*i+2) запроса i-го модуля.

Вход переноса CI седьмого сумматора 12i соединен с четвертым входом Z(4*i+2) запроса i-го модуля. Выходы суммы и переноса СО седьмого сумматора 12i соединены с соответствующими адресными входами седьмого дешифратора 16i, вход разрешения Ε которого соединен с пятым Z(4*i+3) входом запроса i-го модуля. Кроме того, выходы суммы и переноса СО седьмого сумматора 12i являются выходами шины 2i переноса суммы i-го модуля.

В каждом i-м модуле групп выходы четвертого дешифратора 13i являются первой выходной шиной i-го модуля, содержат 4*i+1≤R разрядов и являются шиной U(4*i) внешних выходов устройства, выходы пятого дешифратора 14i являются второй выходной шиной i-го модуля, содержат 4*i+2≤R разрядов и являются шиной U(4*i+1) внешних выходов устройства, выходы шестого дешифратора 15i являются третьей выходной шиной i-го модуля, содержат 4*i+3≤R разрядов и являются шиной U(4*i+2) внешних выходов устройства, выходы седьмого дешифратора 16i являются четвертой выходной шиной i-го модуля, содержат 4*i+4≤R разрядов и являются шиной U(4*i+3) внешних выходов устройства.

Нулевые разряды выходных шин U[0] модулей групп являются группой 0-го ранга высшего приоритета указателей старшей единицы в унитарном коде «1 из N» внешних выходов устройства, первые разряды выходных шин U[1] модулей групп являются группой 1-го ранга указателей старшей единицы в унитарном коде «1 из N» внешних выходов устройства, …, (R-1)-e разряды выходных шин U[R-1] модулей групп являются группой (R-1)-го ранга младшего приоритета указателей старшей единицы в унитарном коде «1 из N» внешних выходов устройства

Принцип работы устройства состоит в следующем.

Предлагаемые многовыходное устройство приоритета позволяет определить среди N внешних входов запроса Z0, Z1, …, Z(N-1) не только сигнал с наивысшим приоритетом, но также определить сигналы со вторым, третьим, …, R-м по старшинству приоритетами. Нулевые разряды выходных шин U0[0], U1[0], …, U(N-1)[0] образуют группу нулевого ранга, которой присвоен высший приоритет, среди которых разряд выхода U0[0] имеет старший приоритет. В группах одноименных разрядов выходов U[L] указателей старшей единицы, выходах одного ранга, вырабатывается результат в виде унитарного кода «1 из Ν».

На группу из N внешних входов запроса устройства Z0, Z1, …, Z(N-1) одновременно поступают сигналы запроса с установленными приоритетами. Высший приоритет установлен для входа с младшим номером Z0, а далее приоритет уменьшается при возрастании от номера к номеру. Младший приоритет задан для входа запроса со старшим номером Z(N-1).

При этом N внешних входов запроса устройства разделены на К групп по четыре входа, где К= ]N/4[ - большее целое, для которых введены К модулей групп 10, 11, …, 1(К-1).

В каждом i-м модуле групп на сумматорах проводится подсчет (суммирование единиц) количества запросов Z, начиная от входа наивысшего приоритета (вход запроса Z0) до текущего запроса.

Для сокращения оборудования внутри модулей проводится (одновременный) параллельный подсчет (суммирование) запросов, а между модулями по шинам 2i переносов суммы Si проводится межмодульный последовательный перенос вычисленной суммы.

Для текущего запроса Z, при наличии на его входе единичного значения, сигнал которого поступает на вход разрешения работы Ε соответствующего текущего дешифратора, в зависимости от значения на его адресных входах, соответствующего вычисленной сумме предыдущих запросов, начиная от высшего запроса Ζ0, на выходах текущего дешифратора устанавливается единичный сигнал на одном из его выходов в унитарном коде «1 из Ν».

Предлагаемое многовыходное устройство приоритета работает следующим образом.

На группу внешних входов запроса Z0, Ζ1, …, Ζ(Ν-1) устройства поступают сигналы с установленными приоритетами. Данные входы поступают на соответствующие входы модулей групп 10, 11, …, 1(К-1).

В нулевой группе 10 сигналы первых двух запросов Z0 и Z1 суммируются на первом полусумматоре 3, на выходах которого может быть установлено значение двоичного кода 0, 1 или 2, соответствующее количеству запросов. Сигналы первых трех запросов Z0, Z1 и Z3 суммируются на втором сумматоре 4, на выходах которого может быть установлено значение двоичного кода 0, 1, 2 или 3, соответствующее количеству запросов.

Если запрос подан входу запроса Z0 высшего приоритета, то на выходе U0[0] устройства будет установлено единичное значение, независимо от запросов Ζ по остальным входам. При этом на других нулевых разрядах группы выходов U1[0], U2[0], …, U(N-1)[0], которые образуют нулевую группу внешних выходов указателя старшей единицы, будут установлены нулевые значения, т.к. на адресных входах всех других дешифраторов будет установлен код, больший или равный единице. Таким образом, на выходах нулевой группы U[0] указателя единиц будет установлен унитарный код «1 из Ν».

При отсутствии единичного сигнала по входу запроса Z0, поступающего на адресный вход первого дешифратора 5, и наличии единичного сигнала по входу запроса Z1, поступающего на вход разрешения Ε первого дешифратора 5, на его выходах единичное значение будет установлено на выходе U1[0] и нулевое значение будет установлено на выходе U1[1]. Таким образом, на выходах U0[0], U1[0], …, U(N-1)[0] нулевой группы внешних выходов устройства вновь будет установлен унитарный код «1 из Ν», с единичным значением на выходе U1[0].

При наличии только запроса по входу Z2 и отсутствии запросов по входам Z0 и Z1 и другим входам Z, запросы Z0 и Z1 будут просуммированы на первом полусумматоре 3 и на выходах первого сумматора 3 будет установлен двоичный код 0, поступающий на адресные входы второго дешифратора 6, а на его входе разрешения Ε будет установлено единичное значение. Поэтому единичное значение будет установлено только на выходе U2[0] второго дешифратора 6. Кроме того, запросы Z0, Z1 и Z2 будут просуммированы на втором сумматоре 4, на выходах которого будет установлен двоичный код 1, поступающий на адресные входы второго дешифратора 6. При этом на всех выходах второго дешифратора 6 будут установлены нулевые значения, так как нулевое значение подано на вход разрешения Ε, соединенный с входом запроса Ζ3.

При наличии запроса по входу Ζ3 и отсутствии запросов по входам Z0, Ζ1 и Ζ2, на выходах первого полусумматора 3 и второго сумматора 4 будут установлены двоичные коды 0, поступающие на адресные входы второго дешифратора 6 и на адресные входы третьего дешифратора 7, а также двоичный код 0 будет подан на вход первого дешифратора 5. Но при этом только на входе разрешения Ε третьего дешифратора 7 будет установлено единичное значение, которое поступает с входа запроса Ζ3. Поэтому единичное значение будет установлено на выходе U3[0] третьего дешифратора 6, а на остальных выходах 0-го модуля групп будут установлены нулевые значения.

При единичных значениях двух сигналов запроса на входах Z0 и Z1, единичные значения будут установлены на выходах U0[0] и U1[1]. При единичных значениях трех сигналов запроса на входах Z0, Z1 и Z2, на выходах первого полусумматора 3 будет установлен двоичный код 2, поступающий на адресные входы второго дешифратора 6, а на его входе разрешения Ε будет установлено единичное значение по сигналу запроса Ζ2, поэтому единичное значение будет установлено на выходе U2[2] второго дешифратора 6, а также единичные значения будут установлены на выходах U0[0] и U1[1]. Одновременно двоичный код 3 с выходов второго сумматора 4 поступает на адресные входы третьего дешифратора 7. При этом, так как вход разрешения работы Ε третьего дешифратора 7 соединен с третьим входом запроса Ζ3, то при наличии запроса на этом входе единичное значение будет установлено на выходе U3[0] третьего дешифратора 7, а при отсутствии запроса Z3, на всех выходах третьего дешифратора 7 будут установлены нулевые значения.

Выходы суммы и переноса СО второго сумматора 4 поступают на шину 20 переноса суммы. При этом на шине 20 может быть установлен двоичный код 0, или 1, или 2, или 3 (S0≤3), для которого необходима два разряда, поэтому шина 20 выполнена двухразрядной (М0=2).

В первом модуле группы 11 на третьем одноразрядном сумматоре 81 проводится суммирование запросов Z3, Z4 и Z5. Четвертый 91, пятый 101, шестой 111 и седьмой 121 сумматоры выполнены двухразрядными с выходом переноса СО. Двоичный код суммы трех запросов Z0, Z1 и Z2 поступает с шины 20 на входы первых слагаемых четвертого 91, пятого 101, шестого 111 и седьмого 121 сумматоров. Так как на входы второго слагаемого четвертого 91 сумматора поступает запрос Z3, то на выходах суммы переноса СО четвертого 91 сумматора будет установлен двоичный код 0, или 1, или 2, или 3, или 4, соответствующий сумме четырех запросов Z0, Z1, Z2 и Z3. Аналогично на выходах пятого 101 сумматора двоичный код от 0 до 5, соответствующий сумме пяти запросов Z0 - Z4, шестого 111 сумматора двоичный код от 0 до 6, соответствующий сумме шести запросов Z0 - Z5, и седьмого 121 сумматора двоичный код от 0 до 7, соответствующий сумме семи запросов Z0 - Z6. Двоичные коды с четвертого 91 - седьмого 121 сумматоров поступают на адресные входы соответственно четвертого 131 - седьмого 161 дешифраторов, на входы разрешения которых поступают соответствующие запросы Z4 - Z7.

При наличии запроса по входу Z4 и отсутствии запросов по входам Z0, Z1, Z2 и Z3, на выходах четвертого сумматора 91 будет установлен двоичный код 0, поступающий на адресные входы четвертого дешифратора 131, а на его входе разрешения Ε будет установлено единичное значение с входа запроса Ζ4. Поэтому единичное значение будет установлено на выходе U4[0] четвертого дешифратора 131.

При наличии запроса по входу Z4 и запроса по одному из входов Z0, Z1, Z2 и Z3, на шине 20 будет установлен двоичный код 1, также на выходах четвертого сумматора 91 будет установлен двоичный код 1, поступающий на адресные входы четвертого дешифратора 131, а на его входе разрешения Ε будет установлено единичное значение с входа запроса Ζ4. Поэтому единичное значение будет установлено на выходе U4[1] четвертого дешифратора 131, что соответствует формированию в первой группе (первом ранге) U[1] на выходе указателя, что старший приоритет имеет запрос Z4. При наличии запроса по входу Z4 и двух запросов на входах Z0, Z1, Z2 и Z3, единичное значение будет установлено на выходе U4[2] четвертого дешифратора 131, что соответствует формированию старшего приоритета запроса по входу Z4 во второй группе (втором ранге) U[2] на выходе устройства.

Аналогично в первом модуле групп 11 формируются группы указателей старших единиц на выходах пятого 141, шестого 151 и седьмого 161 дешифраторов.

Двоичный код от 0 до 7 (S1≤7), соответствующий сумме семи запросов Z0 - Z6, с выходов суммы и переноса СО седьмого 121 сумматора первого модуля групп 11 поступает на трехразрядную шину 21 переносов суммы (М1=3). Аналогично во втором модуле групп 12 двоичный код от 0 до 11 (S2≤11), соответствующий сумме одиннадцати запросов Z0 - Ζ10, с выходов суммы и переноса СО седьмого 122 сумматора поступает на четырехразрядную шину 22 переносов суммы (М2=4) второго модуля групп 12. В третьем модуле 13 на четырехразрядную шину 23 переносов суммы (М3=4) третьего модуля 13 поступает двоичный код от 0 до 15 (S3≤15). Далее аналогично в четвертом модуле 14 на шину 24 переносов суммы четвертого модуля 14 поступает двоичный код от 0 до 19 (S4≤19) и т.д.

В каждом следующем i-м модуле групп 1i устройства на выходах четвертого 13i пятого 14i, шестого 15i и седьмого 16i дешифраторов, аналогично как в первом модуле групп 11, формируются единичные и нулевые значения в группах указателей старших единиц в унитарном коде «1 из N».

В 0-м модуле групп 10 первый дешифратор 5 содержит два выхода, второй дешифратор 6 - три выхода, четвертый дешифратор 7 - четыре выхода. В 1-м модуле групп 11 четвертый дешифратор 131 содержит четыре выхода, пятый дешифратор 141 - пять, шестой дешифратор 151 - шесть и седьмой дешифратор 161 - семь выходов соответственно. Далее в других i-x модулях групп в четвертом 13i, пятом 14i, шестом 15i и седьмом 16i дешифраторах формируется до R выходов (с 0-го до R-1), в соответствии с заданным количеством групп (рангов) указателей старшей единицы. В таблице приведены номера элементов групп, количество входов и выходов дешифраторов, а также количество разрядов в шинах U выходов устройства и объединение разрядов в группы U[L] указателей старшей единицы. Разряды нулевого ранга имеют высший приоритет. Разряды после ранга (R-1) (выделен в таблице) не формируются на выходах дешифраторов.

Суммирование запросов Ζ устройства в первом 3, втором 4 и третьем 8i сумматорах модулей групп выполняется одновременно (параллельно). Суммирование запросов в четвертых 9i - седьмых 12i сумматорах также выполняется одновременно, но первые слагаемые на входы сумматоров поступают с задержкой по цепи последовательного распространения значений предыдущих сумм по шинам 2i переноса, которые соединяют модули групп последовательно.

Таким образом, в предлагаемом устройстве на выходах R групп U[0], U[1], …, U[R-1] указателей старшей единицы будут установлены сигналы, соответствующие R рангам приоритета в унитарном коде «1 из N».

Вышеизложенные сведения позволяют сделать вывод, что предлагаемое многовыходное устройство приоритета обладает регулярностью узлов и связей и соответствует заявляемому техническому результату - расширение функциональных возможностей в части формирования R групп указателей старших единиц в унитарном коде «1 из N» в порядке старшинства приоритетов.