Результат интеллектуальной деятельности: СХЕМА ДВОЙНОГО ПИТАНИЯ В СХЕМЕ ПАМЯТИ

Вид РИД

Изобретение

Область техники

Раскрытые варианты осуществления относятся, в общем, к схеме памяти. Более конкретно, раскрытие относится к запоминающим устройствам, имеющим двойную конфигурацию источника питания.

Предшествующий уровень техники

Так как интегральные схемы памяти уменьшаются в размерах с увеличением емкости, становится желательным снизить напряжение источника питания. Однако ячейки памяти (например, статическое оперативное запоминающее устройство с произвольной выборкой или ячейки SRAM) и усилители считывания (SA's) очень чувствительны к снижениям приложенного напряжения. Когда напряжение снижают, происходит увеличение ошибок записи и чтения памяти вследствие, например, неопределенности в значении заряда, сохраненного ячейкой памяти, например кратковременные ошибки. Чтобы снизить потребляемую мощность и дать возможность дополнительного снижения размера схемы, один подход заключается в снижении уровня напряжения, подаваемого схемам кроме матрицы ячеек памяти (например, декодерам, схемам синхронизации), при сохранении напряжения, подаваемого ячейкам памяти, на некотором требуемом уровне. Даже если ячейки памяти продолжают работать на более высоком напряжении и уровнях мощности, суммарное воздействие заключается в том, чтобы существенно снизить потребляемую мощность, потому что вспомогательные схемы постоянно работают, тогда как только малое число ячеек памяти (например, только те, к которым фактически осуществляется доступ) полностью запитано в любое конкретное время.

Осуществление достаточно высокого дифференциала напряжения в пределах матрицы ячеек памяти при использовании пониженного напряжения для других структур памяти и устройств сопряжения может быть совершено посредством использования схем сдвига уровня для сопряжения компонентов. Например, «высокий» дифференциал напряжения с низким логическим уровнем 0 В и высоким логическим уровнем 1,3 В может быть использован в пределах матрицы ячеек памяти, тогда как высокий логический уровень только 0,7 В может быть использован за пределами матрицы для других структур памяти (например, вспомогательных схем для/связанных с матрицей ячеек памяти, таких как декодеры адреса и схемы синхронизации) и устройств сопряжения (например, шины адреса и данных). Переход от низких к более высоким логическим уровням напряжения может быть совершен, используя схемы сдвига уровня. Схемы сдвига уровня преобразовывают низкие логические уровни напряжения в более высокие напряжения, требуемые ячейками памяти матрицы ячеек памяти. При снижении требуемой мощности, включение этих схем сдвига уровня создает потребление дополнительной энергии для питания схем сдвига уровня и требует дополнительной площади или пространства на микросхеме (например, полезной площади подложки микросхемы). Схемы сдвига уровня могут также вносить задержку во время распространения сигнала, отклонение генератора тактовой частоты, сигналов управления и данных. Таким образом, число и конфигурация схем сдвига уровня может влиять на размер памяти, требуемую мощность и синхронизацию.

Краткое изложение существа изобретения

Согласно варианту осуществления настоящего раскрытия полупроводниковое устройство памяти с двойным напряжением включает в себя формирователь записи, схему отслеживания синхронизации, ячейки памяти. Формирователи записи принимают входные сигналы данных низкого напряжения и, в ответ, записывают значения данных в сердечник памяти. Схема отслеживания синхронизации задерживает сигнал числовой шины высокого напряжения в соответствии со временем, связанным с формирователями записи, записывающими данные в сердечник памяти. Ячейки памяти реагируют на сигнал числовой шины высокого напряжения и на формирователи записи, записывающие значения данных, для сохранения в них данных.

Согласно другому варианту осуществления полупроводниковое устройство памяти включает в себя схемы сдвига уровня адресного сигнала, декодер, формирователи записи и ячейки памяти. Схемы сдвига уровня адреса преобразовывают адресные сигналы низкого уровня в адресные сигналы более высокого уровня. Декодер принимает адресные сигналы более высокого уровня и, в ответ, обеспечивает сигналы числовой шины. Формирователи записи принимают входные сигналы данных низкого уровня и, в ответ, записывают значения данных в разрядные шины. Ячейки памяти реагируют на сигналы числовой шины и на разрядные шины для сохранения в них данных.

В еще одном варианте осуществления полупроводниковое устройство памяти включает в себя подложку и схемы сдвига уровня адресного сигнала, образованные на подложке. Схемы сдвига уровня преобразовывают адресные сигналы низкого уровня в адресные сигналы более высокого уровня. Устройство памяти также включает в себя декодер, образованный на подложке и сконфигурированный с возможностью приема адресных сигналов более высокого уровня и, в ответ, обеспечения сигналов числовой шины. Память дополнительно включает в себя контакты входа данных, подключенные к подложке и сконфигурированные с возможностью приема сигналов данных низкого уровня. Память также включает в себя формирователи записи, образованные на подложке и принимающие сигналы данных низкого уровня и, в ответ, записывающие значения данных. Память также включает в себя ячейки памяти, образованные на подложке и реагирующие на сигналы числовой шины и на записанные значения данных для сохранения в них данных.

В еще другом варианте осуществления представлен способ для работы ячеек памяти. Способ включает в себя этапы, на которых: проводят сигнал записи в разрядные шины, подключенные к ячейкам памяти, на основании входного сигнала данных низкого уровня; и сдвигают уровень адресного сигнала от низкого уровня до более высокого уровня. Способ также включает в себя этапы, на которых: декодируют адресный сигнал, чтобы предоставить сигнал числовой шины, активирующий выбранные некоторые из ячеек памяти; и сдвигают уровень приложенного тактового сигнала, чтобы обеспечить тактовый сигнал высокого уровня. Способ дополнительно включает в себя этапы, на которых: настраивают синхронизацию тактового сигнала высокого уровня, чтобы обеспечить задержанный тактовый сигнал; и сохраняют сигнал записи в выбранных некоторых из ячеек памяти из разрядных шин, в ответ на задержанный тактовый сигнал.

Вышеизложенное весьма ориентировочно обозначило признаки и технические преимущества настоящего изобретения с тем, чтобы подробное описание, которое следует, могло быть лучше понято. Дополнительные признаки и преимущества, которые образуют объект и формулу изобретения, будут описаны далее. Следует принять во внимание специалистам в данной области техники, что раскрытые концепция и конкретные варианты осуществления могут быть легко использованы в качестве основы для модификации и разработки других структур для осуществления тех же целей настоящего изобретения. Следует также осознавать специалистам в данной области техники, что такие равноценные конструкции не отклоняются от сущности и объема изобретения, как изложено в прилагаемой формуле изобретения. Новые признаки, которые считаются характерными для изобретения, как для его организации, так и способа работы, вместе с дополнительными задачами и преимуществами будут лучше поняты из нижеследующего описания, если рассматривать в связи с сопроводительными фигурами. Однако следует однозначно понимать, что каждая из фигур предоставлена только в целях иллюстрации и описания и не предназначена в качестве определения пределов настоящего изобретения.

Краткое описание чертежей

В дальнейшем изобретение поясняется описанием предпочтительных вариантов воплощения со ссылками на сопроводительные чертежи, на которых:

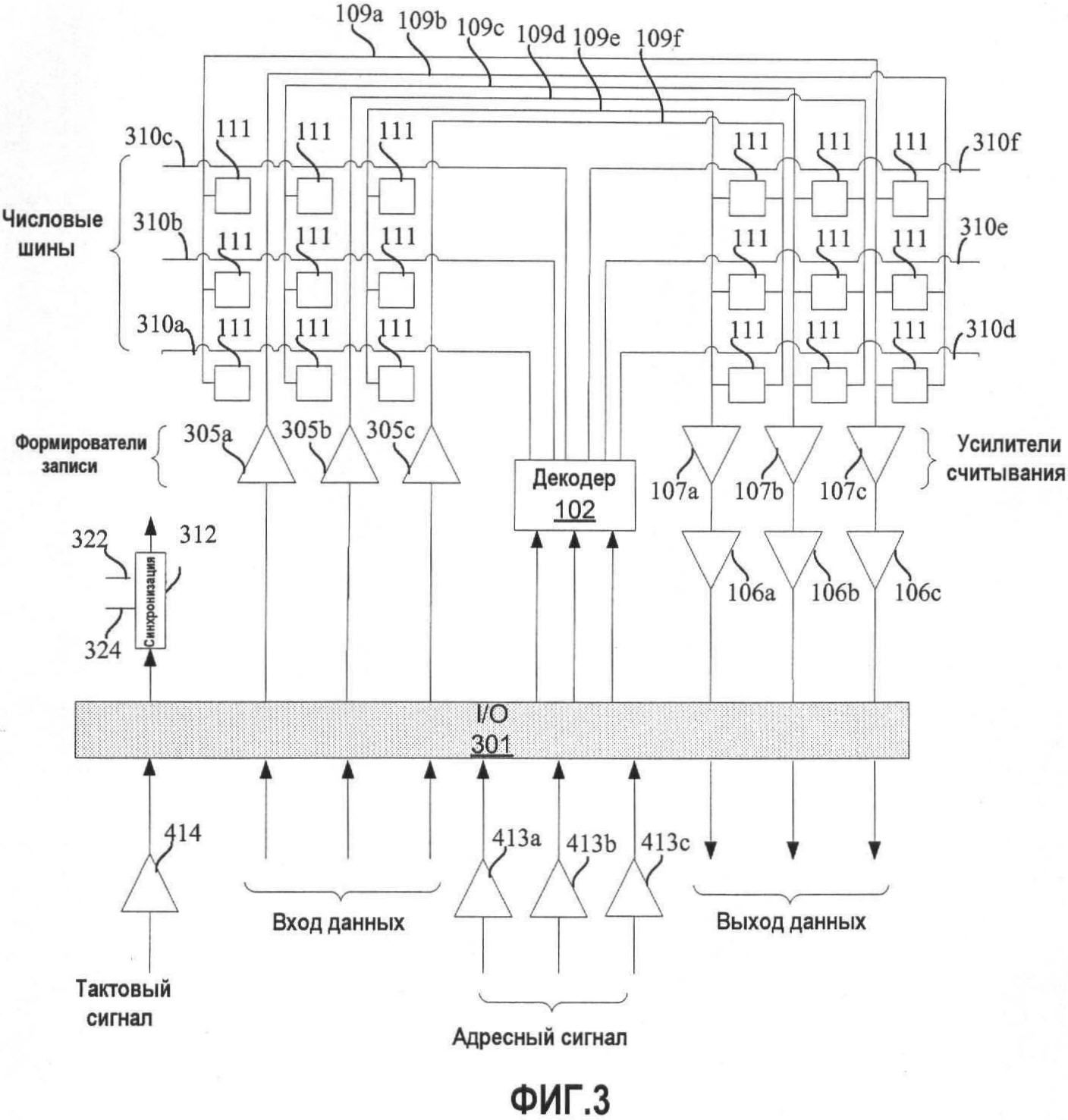

Фиг.1 изображает блок-схему традиционного устройства памяти, включающего в себя схемы сдвига уровня, связанные с соответственными числовыми шинами матрицы ячеек памяти.

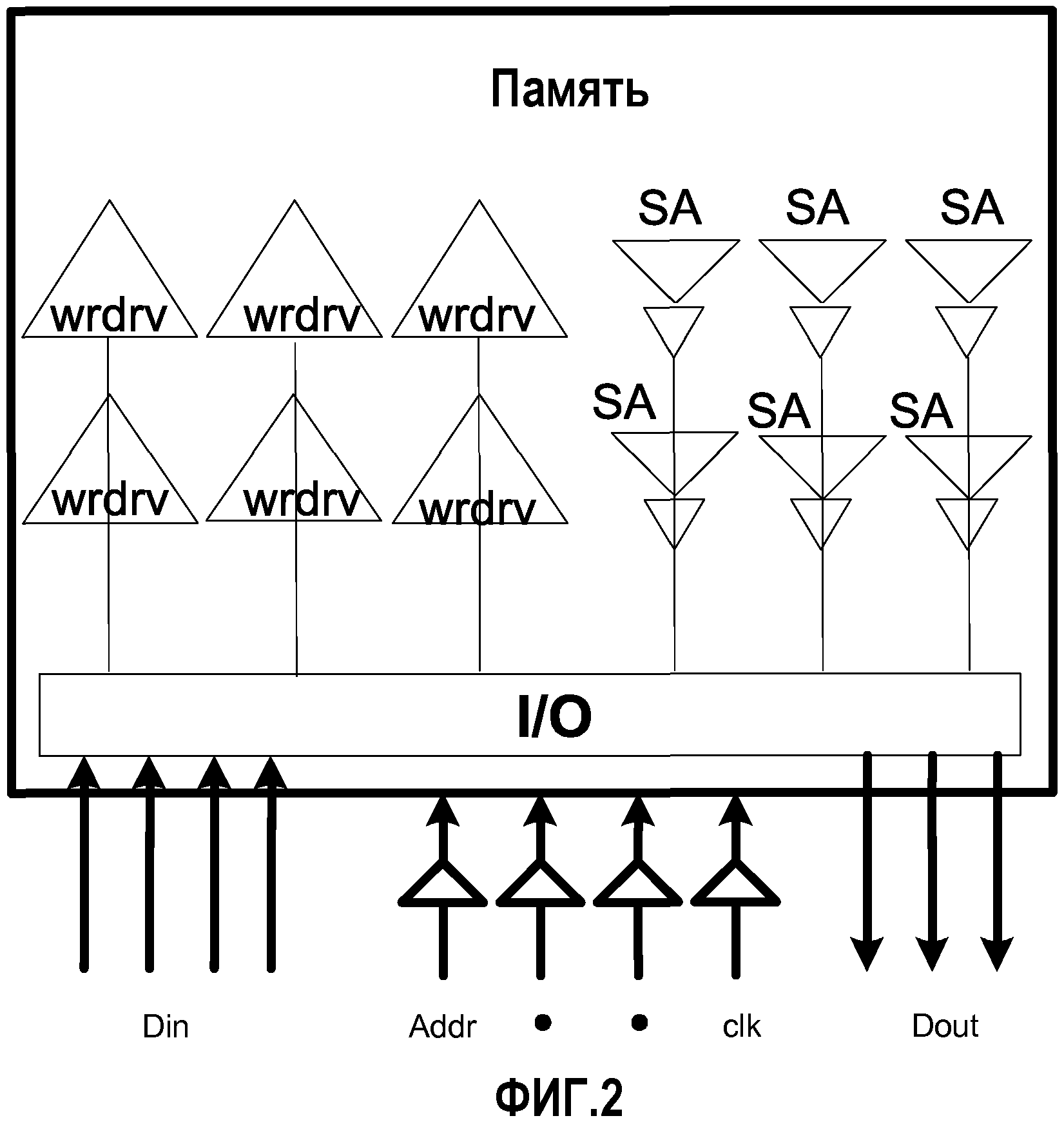

Фиг.2 изображает блок-схему высокого уровня устройства памяти с двойным напряжением, имеющего схемы сдвига уровня, снабжающие декодер, и схемы синхронизации матрицы ячеек памяти.

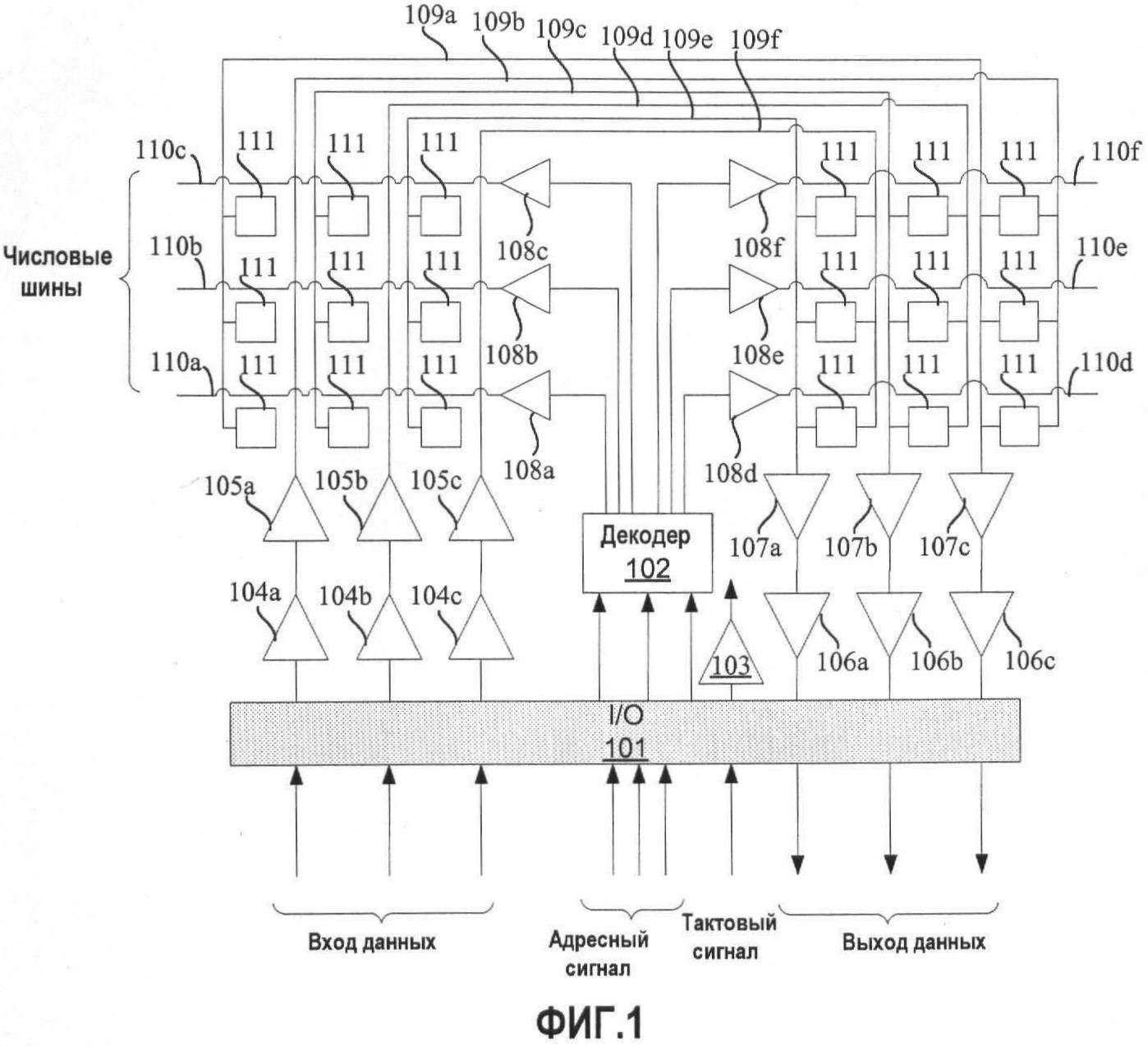

Фиг.3 изображает более подробную блок-схему устройства памяти с двойным напряжением, изображенную на фиг.3.

Фиг.4 изображает блок-схему для схемы отслеживания синхронизации как части устройства памяти с двойным напряжением, как изображено на фиг.4.

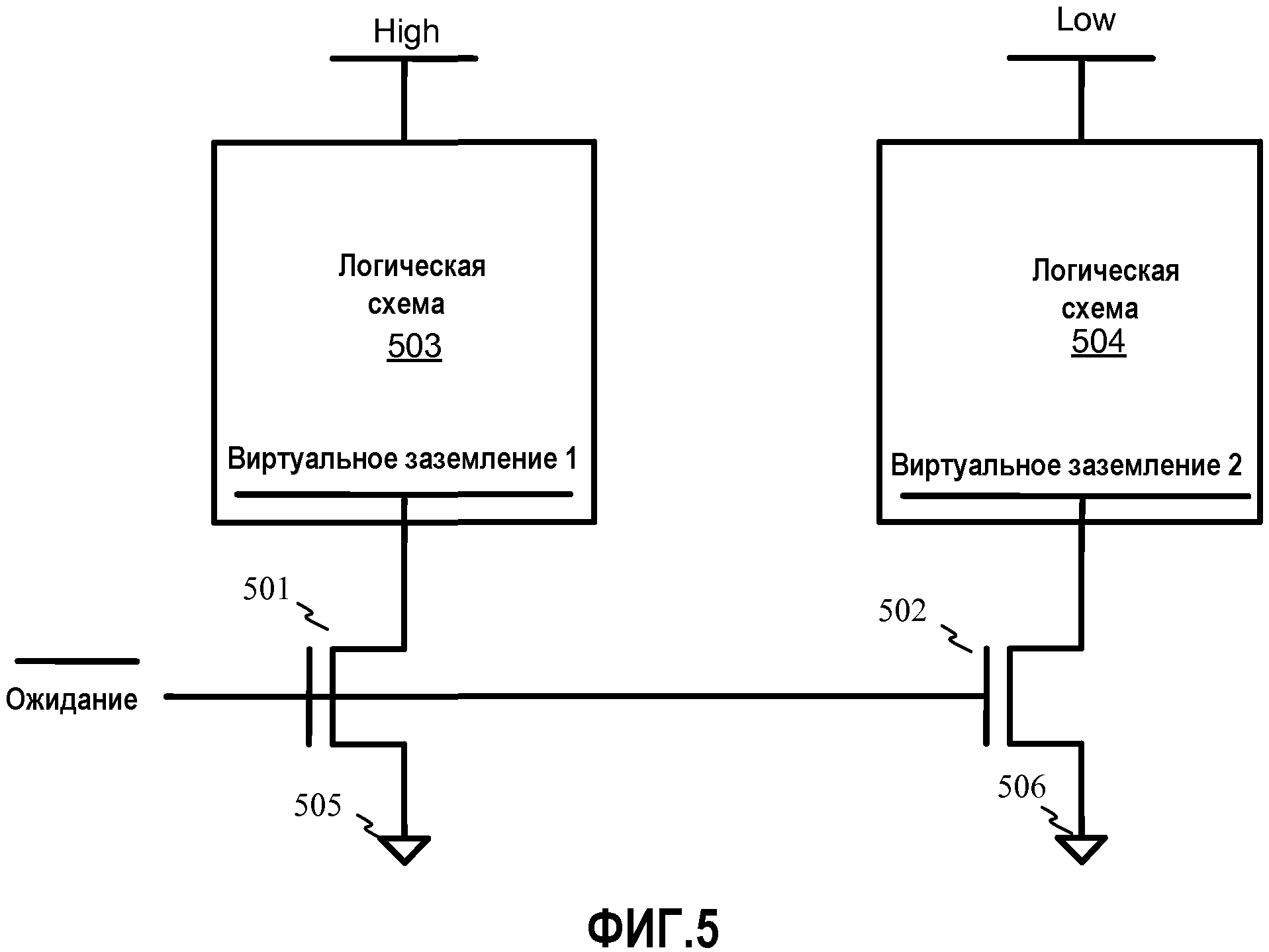

Фиг.5 схематически изображает пары переключателей основания, подключенных в путь возврата тока через землю соответственных участков устройства памяти с двойным напряжением.

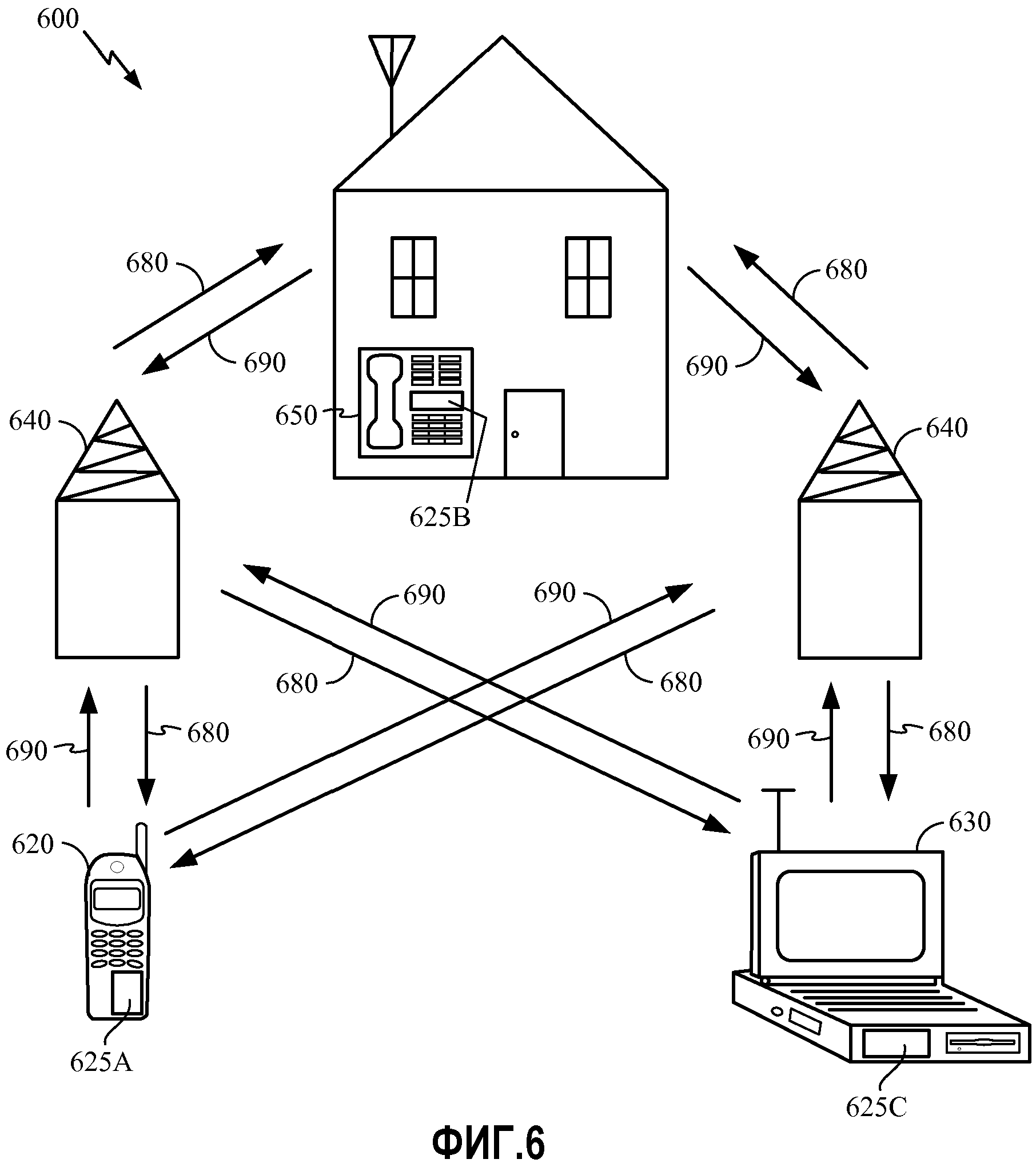

Фиг.6 изображает блок-схему примерной беспроводной системы связи, в которой может быть предпочтительно применен вариант осуществления изобретения.

Описание предпочтительных вариантов воплощения изобретения

Фиг.1 изображает блок-схему устройства памяти, включающего в себя традиционную схему двойного питания. Участки схемы памяти (например, декодер адреса) работают на относительно низких уровнях напряжения (например, 0-0,7 В), тогда как матрица ячеек памяти и усилители считывания работают на более высоком напряжении (например, 0-1,3 В). Рабочие схемы, не требующие высоких уровней напряжения (например, декодер адреса), при более низком напряжении снижают потребляемую мощность и выделяемое тепло. Таким образом, более высокий логический уровень в 1,3 В используют только для хранения информации и работы ячеек памяти матрицы ячеек памяти, так как более высокие уровни напряжения могут требоваться для повышения надежности хранения и извлечения данных.

Со ссылкой на фиг.1, схема 101 I/O (ввода/вывода) принимает и передает сигналы относительно низкого напряжения в и от устройства памяти, включающие в себя сигналы входа данных (Din), адресные (Addr) и тактовые (clk) сигналы, приложенные к схеме I/O, и передает сигналы Dout выхода данных низкого уровня от матрицы памяти к внешним устройствам (или другим схемам, которые могли быть включены в состав устройства или микросхемы памяти), принимающим данные. Сигналам Din входа данных сдвигают уровень от 0-0,7 В до номинального диапазона более высокого напряжения 0-1,3 В схемами 104a-104c сдвига уровня. Полученный в результате сигнал Din со сдвинутым уровнем затем подают в формирователи 105a-105c записи. Номинальные сигналы Din в 0-1,3 В из формирователей 105a-105c записи прикладывают к разрядным шинам 109a-f и передают ячейкам 111 SRAM памяти. Несмотря на то что показаны только подключенные к разрядным шинам 109b, 109d, 109f, в действительности формирователи 105a-105c записи связаны как с разрядными шинами 109b, 109d, 109f, так и с дополнительными разрядными шинами 109a, 109c, 109e.

Адресные и тактовые сигналы низкого уровня Addr и clk соответственно передают через схему 101 I/O декодеру 102 адреса и тактовым схемам 103 сдвига уровня. Декодер 102 сконфигурирован с возможностью приема адресного сигнала Addr низкого напряжения, декодирования его, выбора и предоставления подходящего сигнала выбора низкого уровня схемам 108a-108f сдвига уровня. Схемы 108a-108f сдвига уровня сдвигают логические уровни сигнала низкого уровня (например, 0-0,7 В), предоставленного декодером 102, до подходящего уровня выходного сигнала высокого напряжения (например, номинально имеющего низкий логический уровень 0 В и высокий логический уровень 1,3 В), соответствующего выбранным числовым шинам 110a-110f.

Выбранным ячейкам 111 памяти, соединенным или иным образом связанным с задействованными числовыми шинами 110a-110f, дают возможность записывать или сохранять данные в выбранные ячейки памяти из разрядных шин 109a-f или, при работе в режиме считывания, считывать информацию из ячейки памяти в соответствующую разрядную шину 109a-f. Поскольку декодер 102 предоставляет выходной сигнал выбора низкого напряжения матрице памяти (например, имеющий высокий логический уровень только 0-0,7 В), необходимо обеспечить схему сдвига уровня для каждой из числовых шин, чтобы получить более высокий уровень напряжения (например, сигнал, имеющий номинальный высокий логический уровень 1,3 В). Обычно число схем сдвига уровня, требуемых для n-разрядного адресного сигнала, приводит к 2n схемам сдвига уровня, связанным с соответственными числовыми шинами. Например, 16-мегабитная SRAM, организованная как один мегабит слов по 16 битов, будет включать в себя 10 адресных входных шин и до одного миллиона индивидуальных числовых шин, причем каждая требует отдельной схемы сдвига уровня.

Схема 103 сдвига уровня принимает тактовый сигнал clk низкого уровня от схемы 101 I/O и предоставляет сдвинутый по уровню тактовый сигнал clk высокого напряжения компонентам памяти, по мере надобности. Выходные сигналы высокого уровня из выбранных ячеек 111 памяти предоставляют усилителям 107a-107c считывания, которые, в свою очередь, предоставляют выходы последующим буферам 106a-106c, чтобы предоставить выходной сигнал Dout данных через схему 101 I/O.

Фиг.2 изображает блок-схему схемы памяти, реализующей схему с двойным питанием с уменьшенной нагрузкой, включающую в себя схемы сдвига уровня, обеспечивающие подходящие адресные и тактовые сигналы высокого напряжения (например, 0-1,3 В) секции I/O устройства памяти, тем самым уменьшая количество и мощность потребления, связанные со схемами сдвига уровня, связанными с индивидуальными числовыми шинами. Как показано, формирователи записи принимают сигнал данных от схемы I/O для того, чтобы записывать информацию в выбранные ячейки памяти без необходимости в схемах сдвига уровня. Ряд усилителей SA считывания предоставляют выходной сигнал Dout данных низкого уровня из выбранных ячеек памяти. В другом варианте осуществления усилители считывания работают на высоком напряжении, а последующий буфер работает на низком напряжении, как обсуждается ниже.

Обратите внимание, что в целях настоящего объяснения изображены однопортовые ячейки SRAM. Вместо них могут быть использованы другие типы ячеек памяти, например двухпортовая память. Подобно этому, хотя изображена конкретная архитектура памяти, могут быть реализованы другие компоновки и конфигурации, принятые в схемах двойного питания или двойного напряжения. Таким же образом, хотя показаны трехразрядные сигналы входа данных, выхода данных и адресные сигналы, типичная конфигурация будет включать в себя гораздо больше разрядов данных и адресной информации, передаваемых разным числом шин сигнала данных, адресного и управления.

Фиг.3 более подробно изображает блок-схему схемы памяти с двойным напряжением, реализующую схему двойного питания с уменьшенной нагрузкой, чтобы обеспечить динамическое энергосбережение при снижении размера памяти. В частности, вариант осуществления, изображенный на фиг.3, предоставляет обычную функциональность сдвига уровня для сигналов, приложенных к схеме 301 I/O, чтобы исключить необходимость в нескольких схемах сдвига уровня, связанных с индивидуальными числовыми шинами. Посредством сдвига уровня адресных сигналов низкого уровня до или в рамках схемы 301 I/O, меньше компонентов требуется для поддержки схемы двойного питания, тем самым уменьшая требуемое пространство, т.е. полезную площадь микросхемы, необходимое для сопряжения с относительно низкими напряжениями уровня, использованными компонентами за пределами самой матрицы памяти.

Со ссылкой на фиг.3, адресные и тактовые сигналы Addr и clk прикладывают к схемам 313a-313с и 314 сдвига уровня соответственно для того, чтобы преобразовать логические уровни низкого напряжения (например, 0-0,7 В) в логические сигналы высокого уровня (например, 0-1,3 В), которые будут приложены к схеме 301 I/O. Сигналы высокого уровня затем подают на декодер 302 и схему 312 отслеживания синхронизации. Декодер 302 декодирует адресный сигнал Addr, чтобы выборочно задействовать числовые шины 310a-310f приложением подходящего сигнала выбора ячейки памяти высокого уровня к подходящей числовой шине. Как и прежде ячейки 111 памяти работают на более высоких напряжениях (0-1,3 В) для сохранения целостности данных.

Din является сигналом низкого напряжения, поданным через схему 301 I/O непосредственно к формирователям 305a-305c записи без необходимости в отдельных схемах сдвига уровня (по сравнению с конфигурацией фиг.2). Формирователи 305a-305c записи предоставляют подходящим образом синхронизированные сигналы разрядным шинам 109a-f для записи информации в ячейки 111 памяти матрицы ячеек памяти. Несмотря на то что показаны только подсоединенные к разрядным шинам 109b, 109d, 109f, в действительности формирователи 305a-305c записи связаны как с разрядными шинами 109b, 109d, 109f, так и с дополнительными разрядными шинами 109a, 109c, 109e, чтобы разряжать либо разрядные шины, либо дополнительные разрядные шины на основании сигнала, который записан.

Из-за возможных задержек в предоставлении данных от формирователей 305a-305c записи в разрядные шины 109a-f, схема 312 синхронизации правильно синхронизирует тактовый сигнал clk. Синхронизация может включать в себя задержку или пропускание тактового сигнала, чтобы обеспечить скорость формирователей 305a-305c записи низкого уровня напряжения, записывающих данные в ячейки памяти. То есть, поскольку формирователи 305a-305c записи приводят в действие сигналом низкого напряжения, увеличенное время отклика может привести, до разрядки соответствующих разрядных шин, к записи требуемого значения. Чтобы обеспечить этот синхронизирующий результат, схема 312 отслеживания синхронизации может принимать различные входные сигналы, включающие в себя входные сигналы 322 и 324, чтобы подходящим образом пропускать сигналы разрешения записи, и, если необходимо, считывания, к различным ячейкам 111 памяти. Входные сигналы 322 и 324 происходят из каждой области питания (один сигнал из высокой области питания и один сигнал из низкой области питания). Поскольку путь числовой шины находится под высоким напряжением, а путь Din находится под низким напряжением, один сигнал из каждой области способствует управлению синхронизации между двумя областями питания.

Информация может быть извлечена или считана из ячеек 111 памяти подобным образом. То есть адресный сигнал Addr, обозначающий адреса ячеек 111 памяти, к которым осуществляют доступ, прикладывают к схемам 313a-313с сдвига уровня. Обратите внимание, что в целях настоящего примера, несмотря на то что показан адресный сигнал шириной в три разряда вместе с соответствующими схемами 313a-313с сдвига уровня, типично адресный сигнал будет иметь гораздо больше параллельных разрядов адресных данных, зависящих от размера памяти и конфигурации, например 10 разрядов адреса может быть использовано, чтобы предоставить доступ к одному миллиону слов (или другой имеющей адрес единице) памяти. Подобно этому, несмотря на то что Din и Dout показаны шириной в три разряда каждый, обычно такие сигналы будут существенно шире, например сигналы шириной в 16, 32 или 64 разряда.

В ответ на адресный сигнал декодер 102 предоставляет подходящие сигналы выбора в выбранную числовую шину 310a-310f, чтобы осуществить доступ (например, дать возможность) к соответствующим ячейкам 111 памяти для хранения и извлечения данных в них или из них. В режиме работы «считывание», данные из ячеек 111 памяти передают посредством разрядных шин 109a-f усилителям 107a-107c считывания и затем последующим буферам 106a-106c. Несмотря на то что для наглядности не показано на чертежах, следует принять во внимание, что усилители 107a-107c считывания связываются как с разрядными шинами, так и дополнительными разрядными шинами.

Последующие буферы 106a-106c работают на более низких уровнях напряжения, предоставляя подходящий сигнал Dout низкого уровня (0-0,7 В) внешнему устройству. В возможном варианте осуществления как усилители 107a-107c считывания, так и последующие буферы 106a-106c работают на низком напряжении. Несмотря на то что в целях иллюстрации и объяснения единственный набор разрядных шин может быть использован как для считывания, так и для записи в ячейки 111 памяти матрицы ячеек памяти, вместо этого могут быть использованы разрядные шины записи и считывания.

Фиг.4 изображает блок-схему схемы памяти с двойным напряжением, реализующей схему двойного питания с уменьшенной служебной нагрузкой, включающую в себя схему 312 отслеживания синхронизации. В частности, сигнал входа данных, предоставленный схемой 301 I/O (см. фиг.3), является сигналом низкого уровня, приводящим в действие формирователи 305a-305c записи. Как описано ранее, задержка может возникнуть в предоставлении подходящих данных в соответственных разрядных шинах 109a-f вследствие низкого уровня, приводящего в действие формирователи 305a-305c записи. Однако числовая шина WL должна быть доступна после того, как операция записи была завершена формирователями 305a-305c записи. Сигнал разрешения числовой шины находится в области высокого питания и, таким образом, должен быть задержан. Чтобы создать задержку, схема 312 отслеживания синхронизации, которая принимает тактовые сигналы clk от I/O ctrl (участка на схеме 301 I/O), может задерживать применение подходящего сигнала выбора числовой шины WL от декодера 102 посредством снабжения его задержанным тактовым сигналом clk_d. Схема 312 отслеживания синхронизации может реагировать на один или оба из сигналов 322 низкого уровня и сигналов 324 высокого уровня, чтобы предоставить подходящую синхронизацию тактового сигнала clk_d.

Сейчас объясняется работа отслеживания синхронизации. Триггер (401) (или схема-защелка) запирает данные снаружи памяти и, в ответ на тактовый сигнал, принятый от схемы 301 I/O (более конкретно, от участка схемы 301 I/O, названного I/O ctrl 301а), направляет запертые данные в формирователь 305 записи. Формирователь 305 записи затем готовится к записи запертых данных в ячейку 111 памяти. Схема 312 отслеживания синхронизации задерживает канал декодера, чтобы согласовать задержку канала Din генерированием задержанного тактового сигнала clk_d. Канал числовой шины (WL) быстрее, потому что он является высоким напряжением, а канал Din медленнее, потому что он является низким напряжением. Схема 312 отслеживания синхронизации отслеживает синхронизацию канала Din на основании входного сигнала 322. Поскольку декодер 102 задерживают относительно формирователя 305 записи, данные готовят к записи до того, как числовую шину WL задействуют декодером 102.

Схема отслеживания синхронизации может также отслеживать изменение синхронизации, вызванное колебанием напряжения. В одном варианте осуществления сигнал 322 низкого уровня поступает из канала Din (в низкой области питания), а сигнал 324 высокого уровня приходит от тактового сигнала высокой области питания. В другом варианте осуществления только сигналы из области высокого напряжения предоставляют схеме 312 отслеживания синхронизации.

Фиг.5 изображает блок-схему пары «переключателей 501 и 502 основания», каждый из которых управляет соответственными участками 503 и 504 высокого и низкого напряжения памяти соответственно для того, чтобы выборочно установить память в рабочий режим или режим ожидания или «сна». Каждый переключатель 501, 502 основания выборочно прерывает соединение с виртуальным заземлением 505, 506 для связанных участков 503, 504 памяти. Предоставлены два разных виртуальных заземления, потому что рабочие напряжения в разных областях питания отличаются. Как описано ранее, матрица ячеек памяти и согласно варианту осуществления изобретения декодер работают на высоком уровне напряжения и тем самым управляются переключателем 501 основания, чтобы выборочно устанавливать, что логическая схема находится либо в рабочем режиме, либо в режиме сна в ответ на сигнал режима «сон». Подобно этому схемы низкого уровня напряжения, включающие в себя, например, формирователи 305a-305c записи и последующие буферы 106a-106c, выборочно работают в рабочем режиме или режиме сна в ответ на положение переключателя 502. Режим сна обеспечивает пониженную утечку тока.

Фиг.6 изображает примерную беспроводную систему 600 связи, в которой вариант осуществления изобретения может быть предпочтительно применен. В целях иллюстрации, фиг.6 показывает три удаленных блока 620, 630 и 650 и две базовые станции 640. Следует понимать, что типичные беспроводные системы связи имеют гораздо больше удаленных блоков и базовых станций. Удаленные устройства 620, 630 и 650 включают в себя схемы памяти с двойным питанием 625A, 625B и 625C соответственно, которые являются вариантами осуществления изобретения, как обсуждалось выше. Фиг.6 изображает сигналы 680 прямой линии связи от базовых станций 640 к удаленным блокам 620, 630 и 650 и сигналы 690 обратной линии связи от удаленных блоков 620, 630 и 650 к базовым станциям 640.

На фиг.6 удаленный блок 620 показан как мобильный телефон, удаленный блок 630 показан как портативный компьютер, и удаленный блок 650 показан как удаленный блок с фиксированным местоположением в системе беспроводного абонентского доступа. Например, удаленные блоки могут быть сотовыми телефонами, переносными устройствами системы персональной связи (PCS), портативными устройствами обработки данных, такими как персональные карманные компьютеры, или блоками обработки данных с фиксированным местоположением, такими как оборудование считывания измерительного прибора. Несмотря на то что фиг.6 иллюстрирует удаленные блоки согласно идеям изобретения, изобретение не ограничено этими примерно иллюстрированными устройствами. Изобретение может быть соответствующим образом применено в любом устройстве, которое включает в себя схему памяти с двойным питанием.

Признаки различных схем памяти с двойным напряжением предоставляют преимущества над другими компоновками. Например, использование переключателя основания, включающего в себя отдельные переключающие элементы для схем высокого и низкого напряжения, приводит к уменьшению тока утечки в течение режима ожидания или сна. Использование формирователей записи низкого напряжения может устранить необходимость в отдельных схемах сдвига уровня, уменьшая площадь микросхемы и дополнительно снижая требуемую мощность. Предоставление схем сдвига уровня на входе в схемы I/O снижает число схем сдвига уровня, которые иначе могли бы потребоваться в других компоновках, таких как когда вместо этого сигналы подаются на выход декодера адреса. Еще одно преимущество согласно признакам описанных конфигураций памяти следует из усилителей считывания, которые обеспечивают низкий выходной уровень напряжения, тем самым снижая потребляемую мощность в течение операций считывания и минимизируя потери мощности, которые иначе могут последовать из пропускания высоких напряжений в длинные металлические соединения в микросхеме (например, выходную шину).

Несмотря на то что были изложены конкретные схемы, следует принять во внимание специалистам в данной области техники, что не все из раскрытых схем требуются для практического воплощения изобретения. Более того, некоторые хорошо известные схемы не были описаны, чтобы сфокусироваться на изобретении.

Несмотря на то что настоящее изобретение и его преимущества были описаны подробно, следует понимать, что различные изменения, замены и варианты могут быть выполнены здесь без отклонения от сущности и объема изобретения, как определено прилагаемой формулой изобретения. Более того, не предполагается, что объем настоящей заявки будет ограничен конкретными вариантами осуществления обработки, устройства, производства, состава объекта, средства, способов и этапов, описанных в описании изобретения. В качестве одного для специалистов в данной области техники можно будет легко принять во внимание из раскрытия настоящего изобретения, обработок, устройств, производства, составов объекта, средства, способов или этапов, существующих в настоящее время или которые будут разработаны позже, что осуществление, по существу, той же функции или достижение, по существу, того же результата как в соответствующих вариантах осуществления, описанных здесь, может быть использовано согласно настоящему изобретению. Согласно этому предполагается, что прилагаемая формула изобретения включает в пределы своего объема такие обработки, устройства, производство, составы объекта, средство, способы или этапы.