Результат интеллектуальной деятельности: БИПОЛЯРНО-ПОЛЕВОЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ

Вид РИД

Изобретение

Изобретение относится к области микроэлектроники и может быть использовано в качестве выходного каскада различных арсенид-галлиевых аналоговых устройств, в т.ч. допускающих работу в условиях воздействия проникающей радиации, низких и высоких температур.

Известно значительное количество схем выходных каскадов и буферных усилителей (БУ) аналоговых микроэлектронных изделий, которые реализуются на биполярных (BJT) и полевых (JFet, КМОП, КНИ, КНС и др.) транзисторах, а также при их совместном включении [1-25].

Во многих применениях схема БУ адаптируется под конкретные технологические процессы и внешние воздействующие факторы, т.к. только в этом случае обеспечивается реализациях предельных параметров БУ.

В настоящее время в российской и зарубежной микроэлектронике уделяется повышенное внимание арсенид-галлиевым микросхемам [26-30]. Данное направление создания электронной компонентной базы относится к числу наиболее перспективных в задачах космического приборостроения. Однако, особенности арсенид-галлиевых технологических процессов накладывают существенные ограничения на типы реализуемых транзисторов и их характеристики. Так, например, арсенид-галлиевый технологический процесс, предлагаемый фирмами США [26-29], а также Минским научно-исследовательским институтом радиоматериалов (https://mniirm.by/), ориентирован на изготовление аналоговых схем, содержащих только полевые GaAs транзисторы с управляющим p-n переходом и биполярные GaAs p-n-p транзисторы. Применение других полупроводниковых приборов не допускается. Это накладывает существенные ограничения на схемотехнику аналоговых устройств, ориентированных на биполярно-полевой технологический процесс. Примеры построения биполярно-полевых буферных усилителей приведены в [31-36].

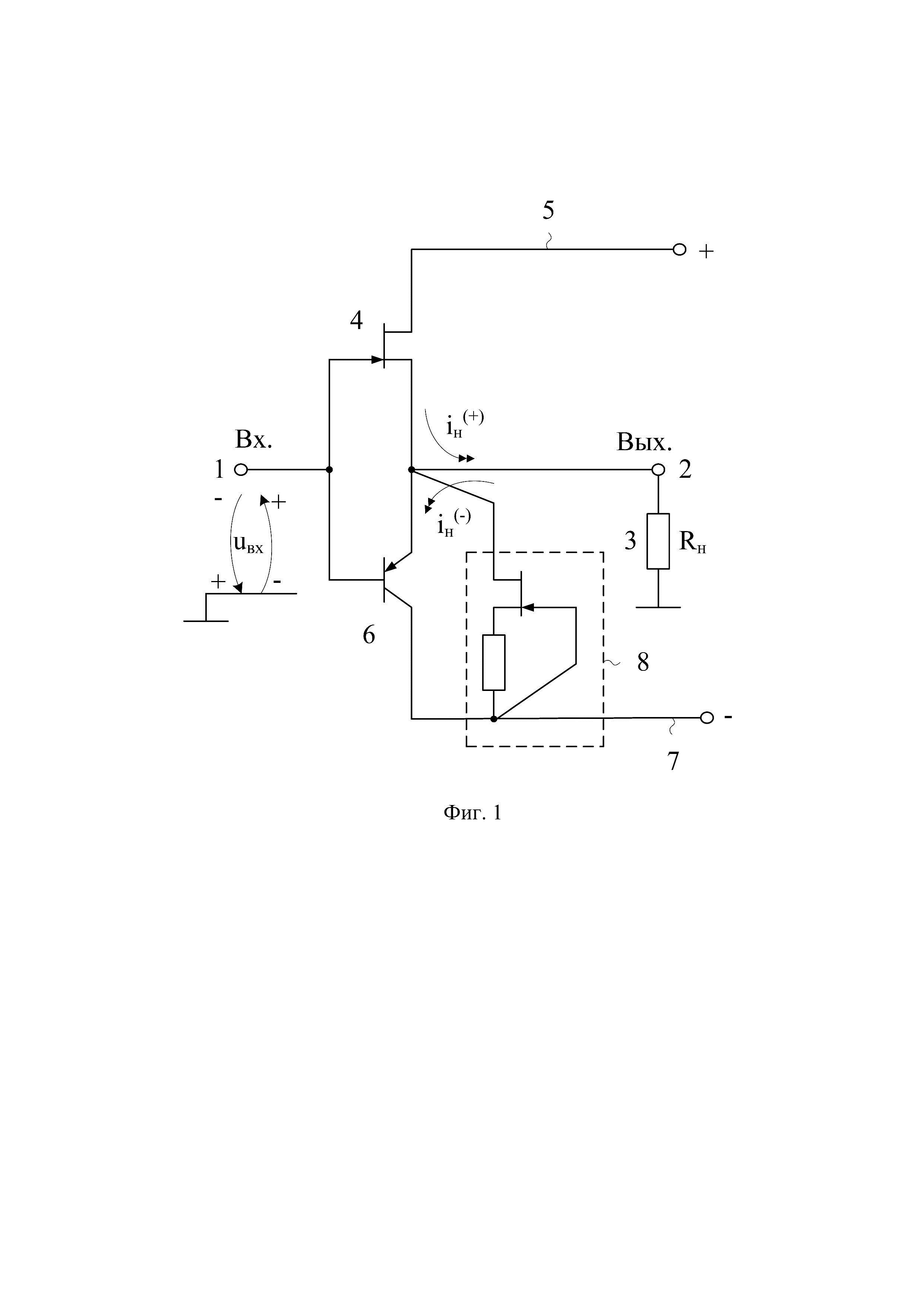

Ближайшим прототипом (фиг. 1) заявляемого устройства является буферный усилитель, представленный в патенте RU 2784376, 2022 г. Он содержит вход 1 и выход 2 устройства, к которому подключена нагрузка 3, входной полевой транзистор 4, затвор которого соединен со входом 1 устройства, сток согласован с первой 5 шиной источника питания, а исток соединен с выходом 2 устройства, биполярный транзистор 6, эмиттер которого соединен с истоком входного полевого транзистора 4, а коллектор связан со второй 7 шиной источника питания, токостабилизирующий двухполюсник 8.

Существенный недостаток БУ – прототипа состоит в том, что он не может обеспечить в относительно низкоомной нагрузке Rн токи двух направлений, т.е. он не работает в двухтактном режиме класса АВ.

Основная задача предполагаемого изобретения состоит в создании двухтактного буферного усилителя, реализуемого на JFET арсенид-галлиевых полевых транзисторах с управляющим p-n переходом и биполярных GaAs p-n-p транзисторах, который имеет малый статический ток потребления и обеспечивает в относительно низкоомной нагрузке токи двух направлений.

Поставленная задача достигается тем, что в буферном усилителе фиг. 1, содержащем вход 1 и выход 2 устройства, к которому подключена нагрузка 3, входной полевой транзистор 4, затвор которого соединен со входом 1 устройства, сток согласован с первой 5 шиной источника питания, а исток соединен с выходом 2 устройства, биполярный транзистор 6, эмиттер которого соединен с истоком входного полевого транзистора 4, а коллектор связан со второй 7 шиной источника питания, токостабилизирующий двухполюсник 8, предусмотрены новые элементы и связи - сток входного полевого транзистора соединен со входом дополнительного токового зеркала 9, согласованного со второй 5 шиной источника питания, выход которого подключен к выходу устройства 2 через цепь согласования потенциалов 10, а также связан с базой биполярного транзистора 6 и через токостабилизрующий двухполюсник 8 подключен ко второй 7 шине источника питания.

На чертеже фиг. 1 показана схема GaAs буферного усилителя – прототипа.

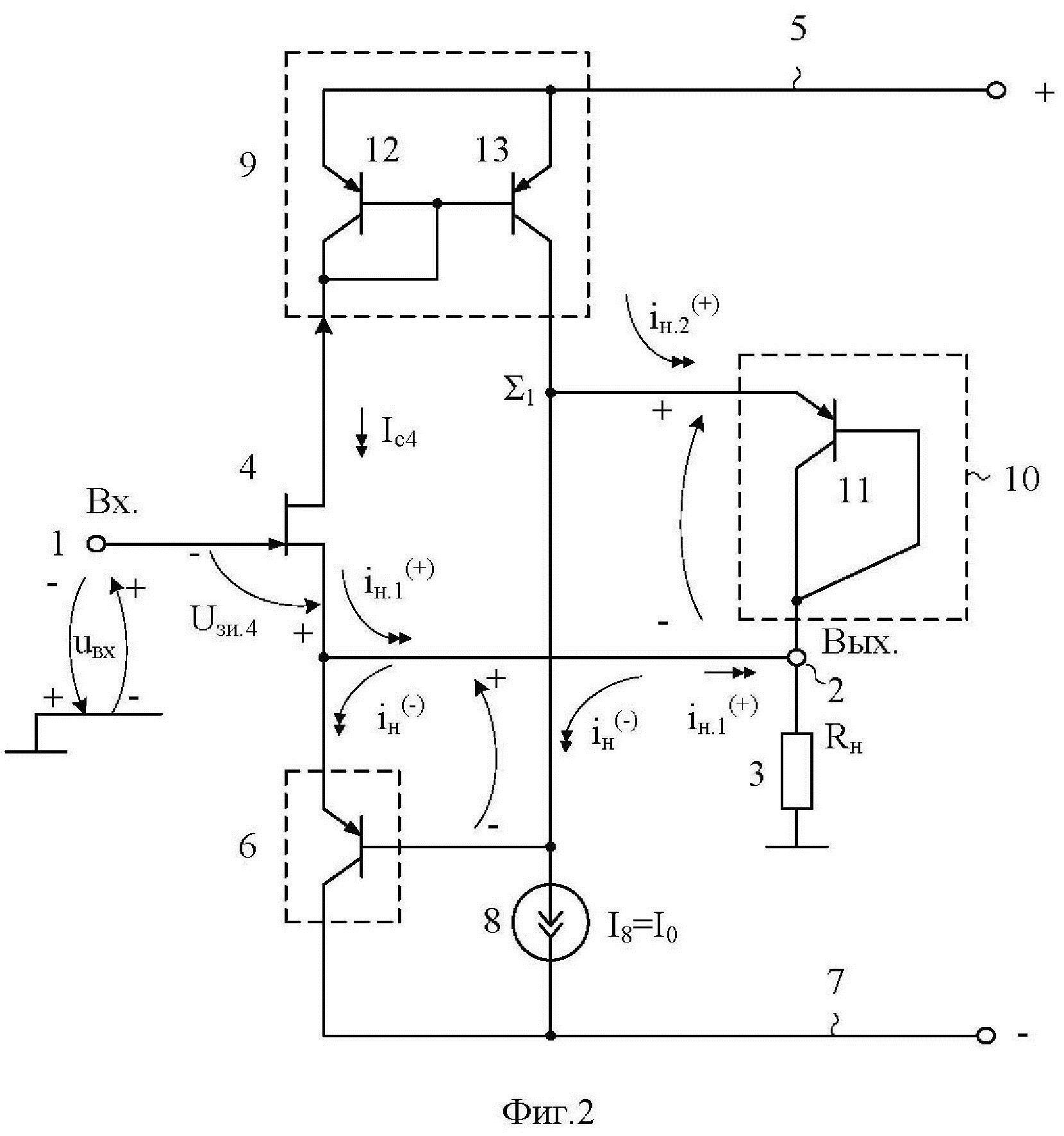

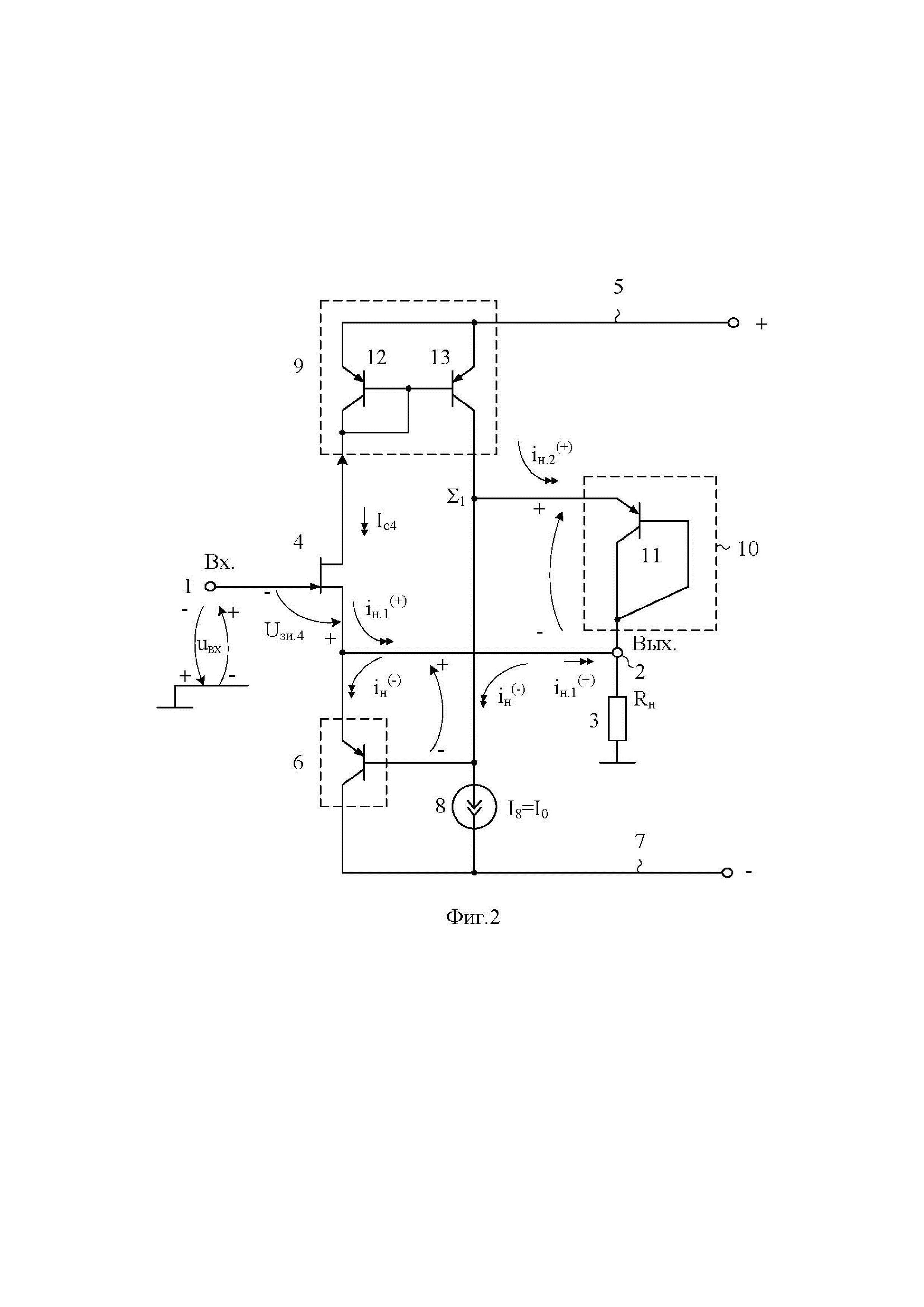

На чертеже фиг.2 представлена схема заявляемого буферного усилителя в соответствии с п.1, п.2 и п.3 формулы изобретения.

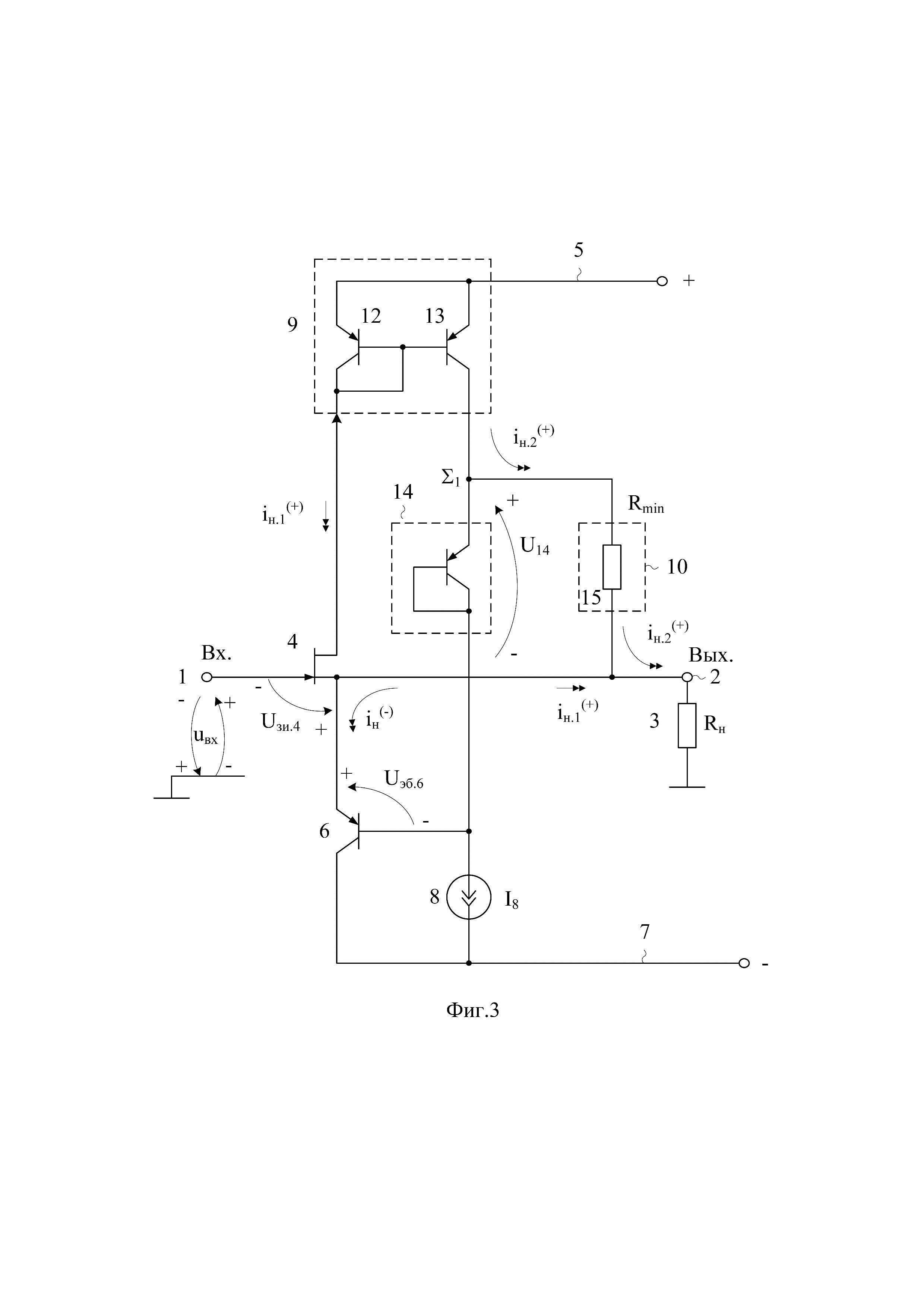

На чертеже фиг.3 приведена схема буферного усилителя в соответствии с п.4 формулы изобретения.

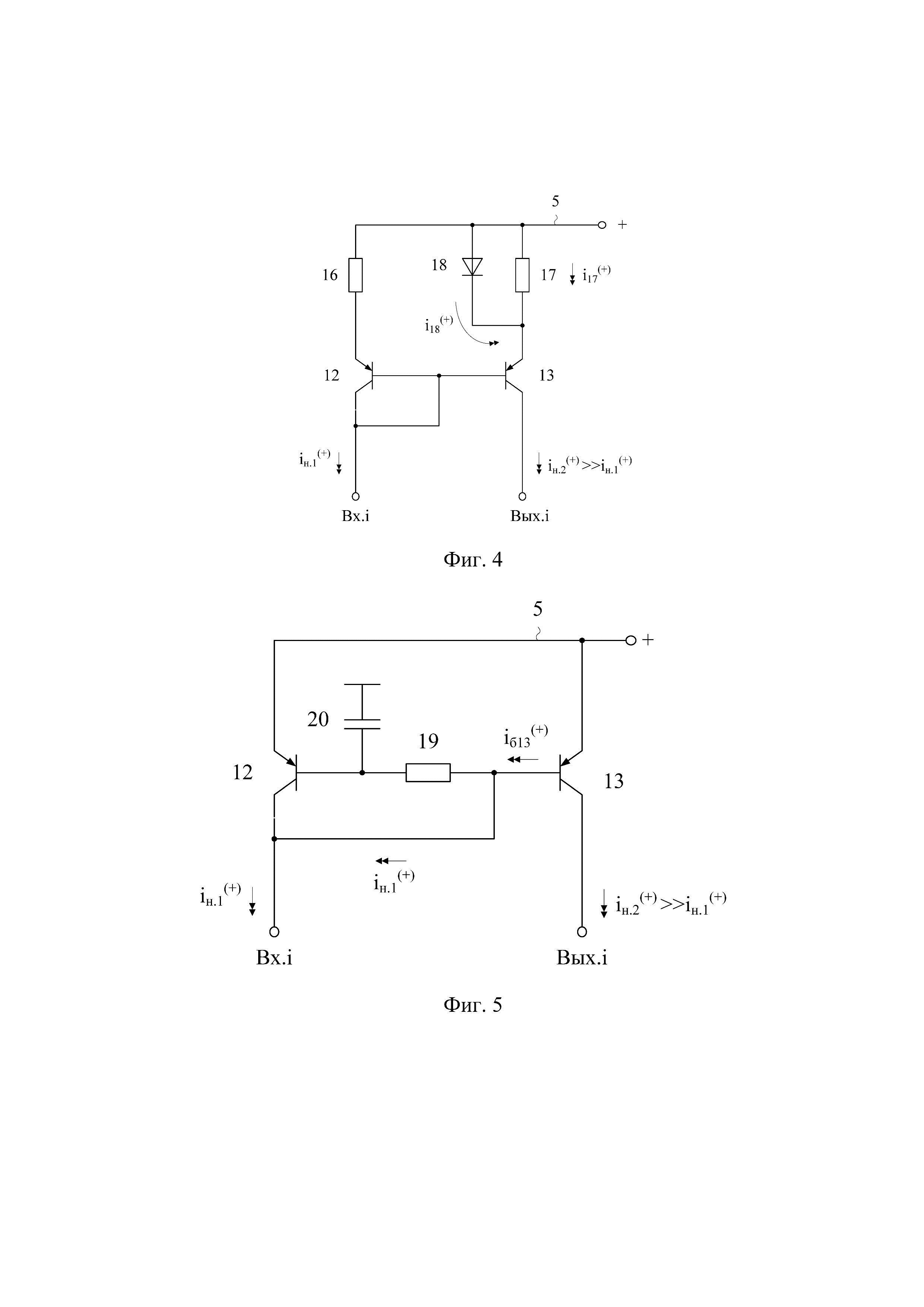

На чертеже фиг. 4 показана схема дополнительного токового зеркала 9, предназначенного для перспективной модификации заявляемого БУ фиг. 2, соответствующего п.5 формулы изобретения.

На чертеже фиг. 5 представлен пример построения дополнительного токового зеркала 9, которое может использоваться в других модификациях заявляемого БУ.

На чертеже фиг. 6 приведена схема для моделирования GaAs БУ фиг. 2 в среде LTspice при t=27 oC, +Vcc=-Vee=10 В, Rload=1 МОм, I1=100 мкА (отношение длины и ширины канала полевого транзистора 100u/0.2u).

На чертеже фиг. 7 показаны амплитудные характеристики GaAs БУ фиг. 6 в среде LTspice при t=27 oC, +Vcc=-Vee=10 В, I1=100 мкА и разных сопротивлениях нагрузки Rload=1 кОм/2 кОм/10 кОм /1 Мом.

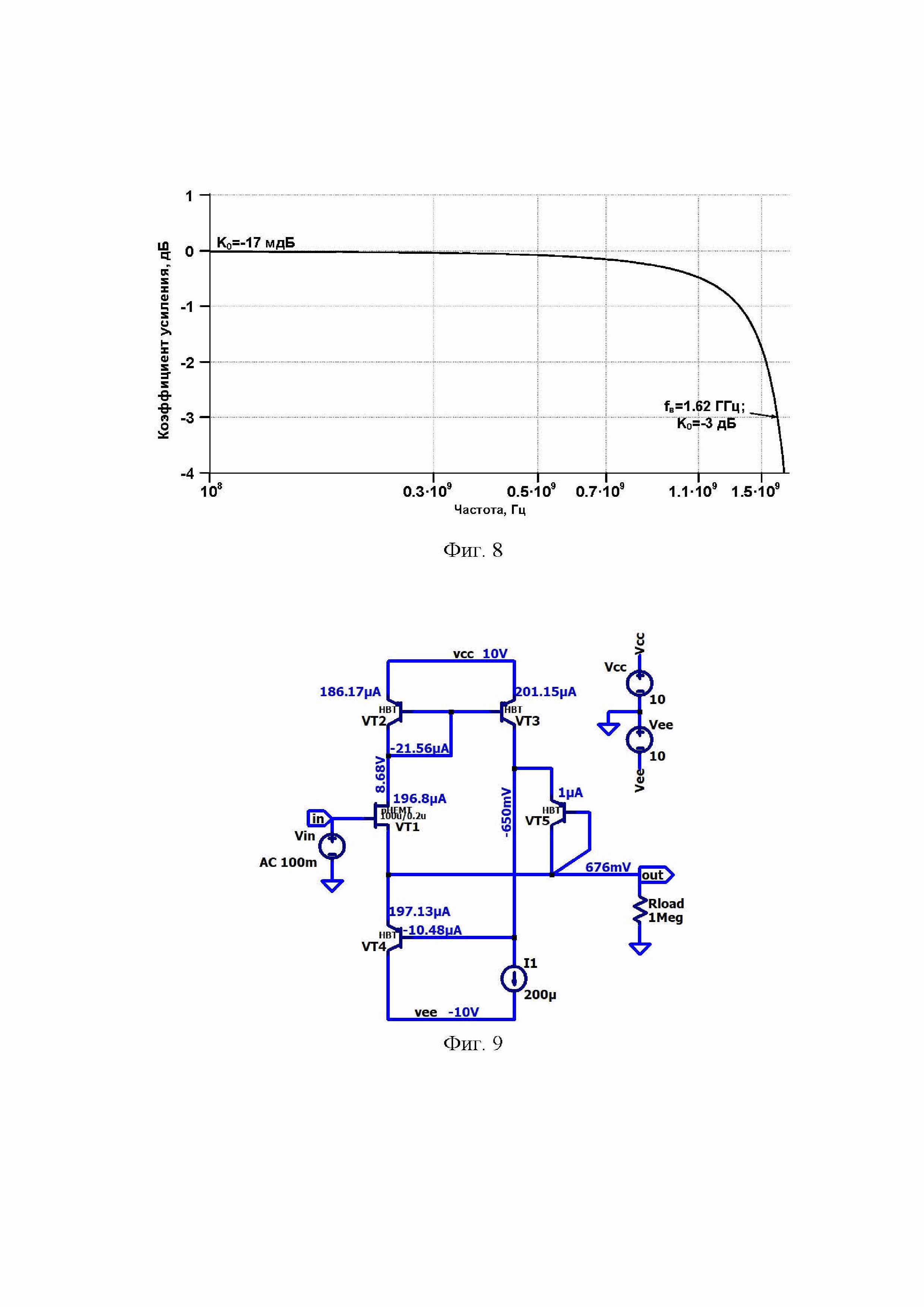

На чертеже фиг. 8 представлена логарифмическая амплитудно-частотная характеристика (ЛАЧХ) GaAs БУ фиг. 6 в среде LTspice при t=27 oC, +Vcc=-Vee=10 В, Rload=1 МОм, I1=100 мкА.

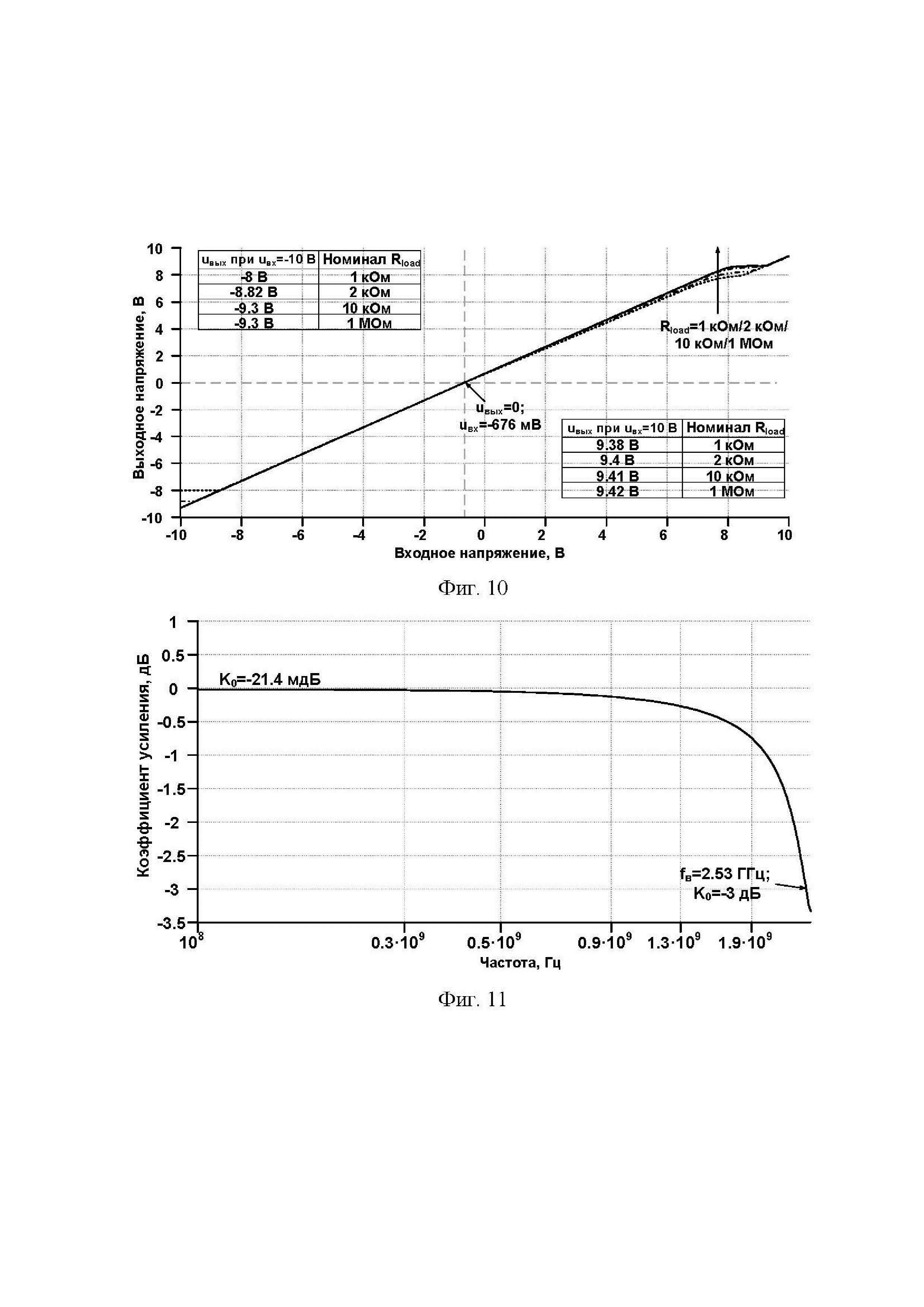

На чертеже фиг. 9 приведена схема для моделирования GaAs БУ фиг. 2 в среде LTspice при t=27 oC, +Vcc=-Vee=10 В, Rload=1 МОм (отношение длины и ширины канала полевого транзистора 100u/0.2u). Ее особенность – более высокий уровень тока источник опорного тока I1=200 мкА.

На чертеже фиг. 10 показана амплитудная характеристика GaAs БУ фиг. 9 в среде LTspice при t=27 oC, +Vcc=-Vee=10 В, I1=200 мкА и различных сопротивлениях нагрузки Rload=1 кОм/2 кОм/10 кОм /1 МОм.

На чертеже фиг. 11 представлена ЛАЧХ GaAs БУ фиг. 9 в среде LTspice при t=27 oC, +Vcc=-Vee=10 В, Rload=1 МОм, I1=200 мкА.

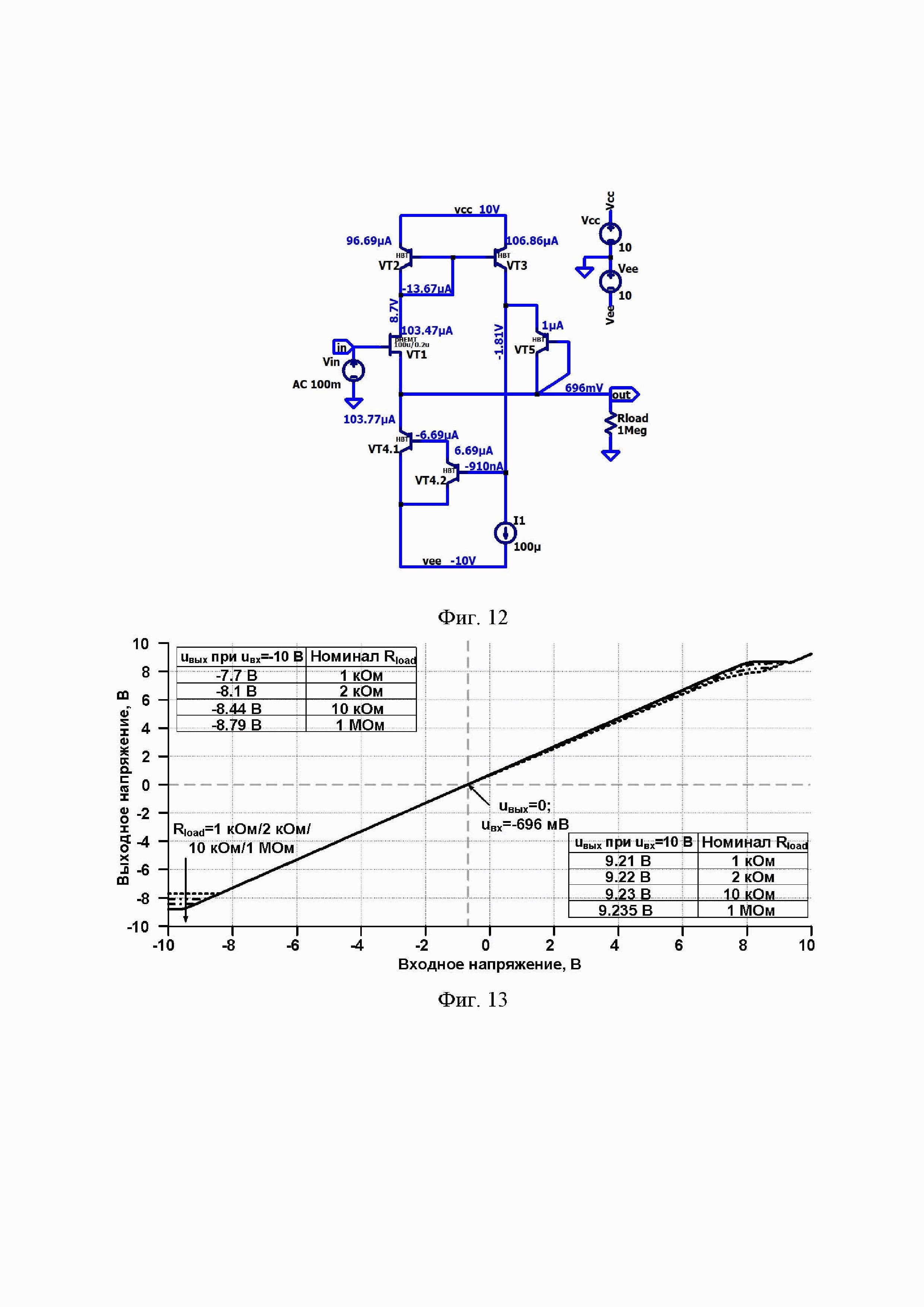

На чертеже фиг. 12 приведена схема для моделирования GaAs БУ фиг. 2 в среде LTspice при t=27 oC, +Vcc=-Vee=10 В, Rload=1 МОм, I1=100 мкА (отношение длины и ширины канала полевого транзистора 100u/0.2u) для случая, когда VT4 выполнен как составной транзистор по схеме Дарлингтона (VT4.1, VT4.2).

На чертеже фиг. 13 показана амплитудная характеристика GaAs БУ фиг. 12 в среде LTspice при t=27 oC, +Vcc=-Vee=10 В, I1=100 мкА, Rload=1 кОм/2 кОм/10 кОм /1 МОм.

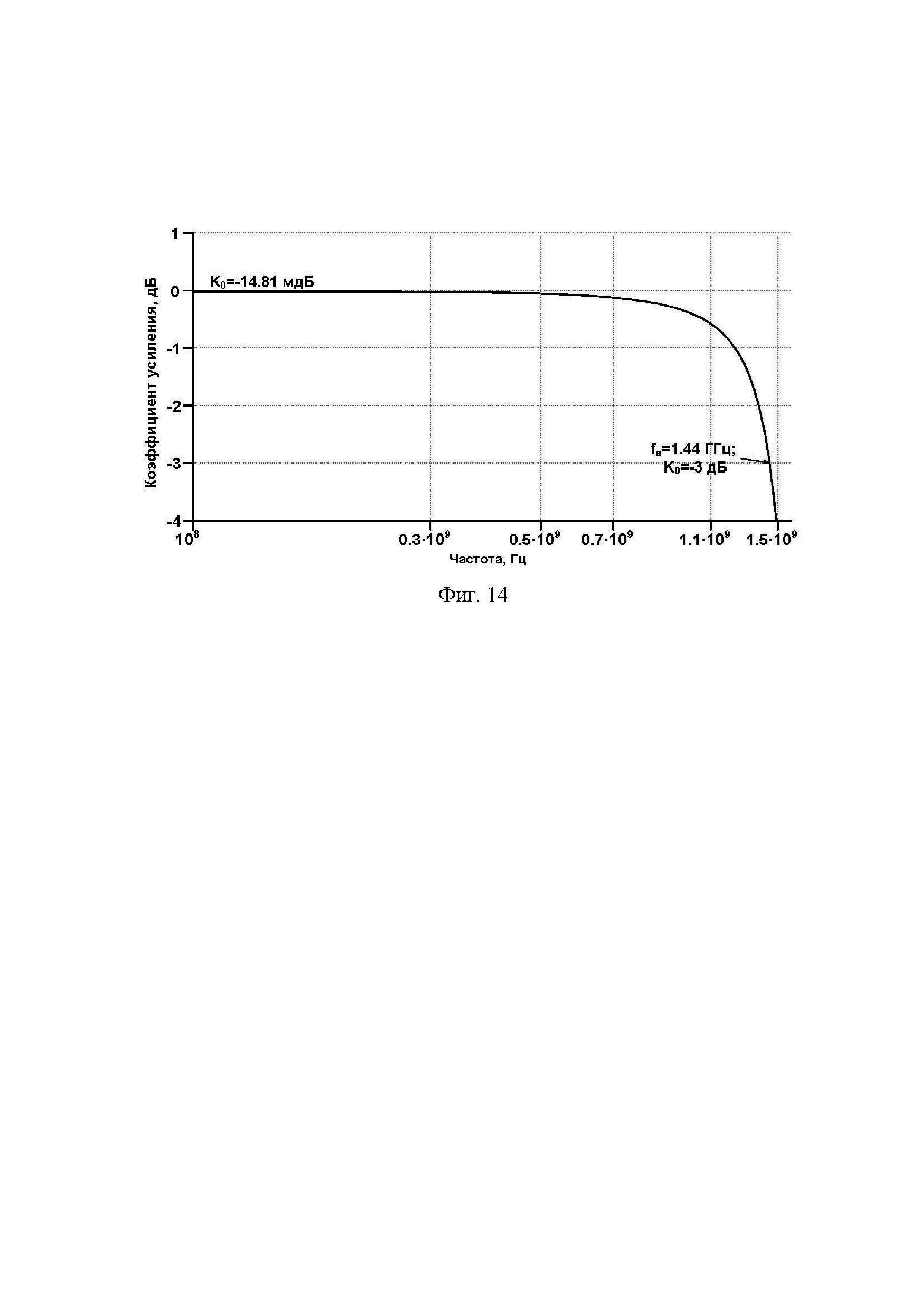

На чертеже фиг. 14 приведена ЛАЧХ GaAs БУ фиг. 12 в среде LTspice при t=27 oC, +Vcc=-Vee=10 В, Rload=1 МОм, I1=100 мкА.

Биполярно-полевой арсенид-галлиевый буферный усилитель фиг. 2 содержит вход 1 и выход 2 устройства, к которому подключена нагрузка 3, входной полевой транзистор 4, затвор которого соединен со входом 1 устройства, сток согласован с первой 5 шиной источника питания, а исток соединен с выходом 2 устройства, биполярный транзистор 6, эмиттер которого соединен с истоком входного полевого транзистора 4, а коллектор связан со второй 7 шиной источника питания, токостабилизирующий двухполюсник 8. Сток входного полевого транзистора соединен со входом дополнительного токового зеркала 9, согласованного со второй 5 шиной источника питания, выход которого подключен к выходу устройства 2 через цепь согласования потенциалов 10, а также связан с базой биполярного транзистора 6 и через токостабилизрующий двухполюсник 8 подключен ко второй 7 шине источника питания.

На чертеже фиг. 2, в соответствии с п. 2 формулы изобретения, цепь согласования потенциалов 10 реализована в виде эмиттерно-базового перехода на дополнительном биполярном транзисторе 11.

На чертеже фиг. 2, в соответствии с п. 3 формулы изобретения, дополнительное токовое зеркало 9 содержит первый 12 и второй 13 вспомогательные биполярные транзисторы, эмиттеры которых связаны с первой 5 шиной источника питания, базы объединены и подключены ко входу дополнительного токового зеркала 9, причем коллектор второго 13 вспомогательного биполярного транзистора связан с выходом дополнительного токового зеркала 9.

На чертеже фиг. 3, в соответствии с п. 4 формулы изобретения, выход дополнительного токового зеркала 9 в схеме БУ фиг. 2 связан с базой биполярного транзистора 6 через дополнительный p-n переход 14, а цепь согласования потенциалов 10 выполнена в виде низкоомного резистора 15.

На чертеже фиг. 4, в соответствии с п. 5 формулы изобретения, дополнительное токовое зеркало 9 в схеме БУ фиг. 2 содержит первый 16 вспомогательный резистор, включенный между эмиттером первого 12 вспомогательного биполярного транзистора и первой 5 шиной источника питания, второй 17 вспомогательный резистор, включенный между эмиттером второго 13 вспомогательного биполярного транзистора и первой 5 шиной источника питания, а также вспомогательный p-n переход 18, включенный параллельно второму 17 вспомогательному резистору.

Рассмотрим работу предлагаемого буферного усилителя фиг. 2.

Статический режим БУ на чертеже фиг. 2 при большом сопротивлении нагрузки Rн определяется токостабилизирующим двухполюсником 8. При этом в схеме выполняются следующие токовые уравнения Кирхгофа

Ic4 ≈ I8,

Iк13 ≈ I8,

Iэ6 ≈ Iи4,

где Iи4=Iс4 – ток истока и ток стока входного полевого транзистора 4,

Iк13 – статический ток коллектора второго 13 вспомогательного биполярного транзистора.

При положительном приращении напряжения на входе 1 увеличивается ток истока входного полевого транзистора 4, который формирует первую составляющую тока в нагрузке iн.1(+). Вторая составляющая тока в нагрузке формируется благодаря передаче тока стока входного полевого транзистора 4 в высокоимпедансный узел Σ1 через дополнительное токовое зеркало 9 и далее через цепь согласования потенциалов 10 на выход устройства 2, причем

iн(+) = iн.1(+) + iн.2(+).

В частном случае iн.2(+) может превышать iн.1(+), что обеспечивается соответствующим выбором площадей первого 12 и второго 13 вспомогательных биполярных транзисторов.

При отрицательном приращении напряжения на входе 1 входной полевой транзистор 4 подзапирается. Кроме этого, уменьшается и выходной ток дополнительного токового зеркала 9, что приводит к запиранию дополнительного биполярного транзистора 11, входящего в структуру цепи согласования потенциала 10. Как следствие, отрицательное приращение тока в нагрузке Rн iн(-) формируется биполярным транзистором 6, причем максимальное значение Iн.max(-) определяется формулой

Iн.max(-) ≈ I8β6,

где β6 - коэффициент усиления по току базы биполярного транзистора 6,

I8 - статический ток токостабилизирующего двухполюсника 8.

Таким образом, если в качестве биполярного транзистора 6 использовать составной транзистор Дарлингтона (см. фиг. 12), то БУ фиг. 2 может обеспечить более высокие токи в низкоомной нагрузке Rн.

В частном случае (фиг. 3) в качестве цепи согласования потенциалов 10 может применяться сравнительно низкоомный резистор 15, а между базой биполярного транзистора 6 и выходом дополнительного токового зеркала 9 необходимо включить дополнительный p-n переход 14. В данной схеме статическое напряжение на цепи согласования потенциалов 10 будет близко к нулю и резистор 15 может быть сравнительно низкоомным.

В соответствии с п. 5 формулы изобретения на чертеже фиг. 4 предлагается схема БУ, в котором дополнительное токовое зеркало 9 содержит дополнительные элементы - первый 16 и второй 17 вспомогательные резисторы и вспомогательный p-n переход 18 (фиг. 4). Такое схемотехническое решение обеспечивает в режиме большого сигнала коэффициент передачи дополнительного токового зеркала 9 больше единицы. Таким образом, схема фиг. 4 позволяет сформировать в заявляемом БУ фиг. 2 более высокие уровни второй составляющей тока нагрузки iн.2(+).

Схема токового зеркала на чертеже фиг. 5 может применяться в заявляемом БУ фиг. 2 для форсирования переходного процесса за счет введения вспомогательных резистора 19 и конденсатора 20. Действительно, импульсное изменение тока iн.1(+) передается на базу первого 12 вспомогательного биполярного транзистора с задержкой по времени. Как следствие, на переднем фронте переходного процесса ток базы второго 13 вспомогательного биполярного транзистора iб13 равен току iн.1(+). В результате фронт выходного тока дополнительного токового зеркала 9 будет иметь более крутой участок, что позволит сформировать на выходе 2 БУ фиг. 2 значительный дополнительный ток для заряда емкости нагрузки.

Представленные на чертежах фиг. 7, фиг. 10, фиг.13 амплитудные характеристики заявляемых модификаций БУ показывают, что рассмотренные схемы (при рациональном выборе статического режима и структуры составных транзисторов) обеспечивают работу БУ фиг. 2 в сравнительно широком диапазоне сопротивлений резисторов нагрузки.

Амплитудно-частотные характеристики предлагаемых схем БУ (фиг. 8, фиг. 11) показывают, что рассмотренная схемотехника обеспечивает работу БУ до частот 1,6-2,5 ГГц.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с БУ-прототипом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент RU № 2523947 fig. 4, 2014 г.

2. Патент WO 2007135139, 2007 г.

3. Патент US 4.743.862, 1988 г.

4. Патент US 6.433.638, fig. 1a-2, 2002 г.

5. Патентная заявка US 20050253653, 2005 г.

6. Патент US 4.825.174, fig. 3, fig. 6, 1989 г.

7. Патент RU 2099856, fig. 3, 1997 г.

8. Патент US 4.904.953, fig. 2, 1990 г.

9. Патент US 7.896.339, fig. 4, 2011 г.

10. Патент US 6.342.814, 2002 г.

11. Патентная заявка US 2010/0182086, 2010 г.

12. Патент US 5.387.880, fig. 1, 1995 г.

13. Патент US 4.598.253, 1986 г.

14. Патент US 4.667.165, fig. 2, 1987 г.

15. Патент US 4.596.958, 1986 г.

16. Патент US 7.116.172, fig. 4, fig. 5, 2006 г.

17. Патент US 5.648.743, 1997 г.

18. Патент US 5.367.271, fig. 2, 1994 г.

19. Патентная заявка US 2000/0112075, fig. 3, 2000 г.

20. Патент US 5.065.043, fig. 1f, 1991 г.

21. Патентная заявка US 2007/0115056, fig. 2, 2007 г.

22. Патент US 7.548.117, fig. 5, 2009 г.

23. Патент EP 0 293486 B1, fig. 5, 1991 г.

24. Патент US 4.420.726, fig. 1 – fig. 3, 1983 г.

25. Проектирование низкотемпературных и радиационно-стойких аналоговых микросхем для обработки сигналов датчиков: монография / Н.Н. Прокопенко, О.В. Дворников, А.В. Бугакова. – М.: СОЛОН-Пресс, 2021. – 200 с.

26. M. Fresina, "Trends in GaAs HBTs for wireless and RF," 2011 IEEE Bipolar/BiCMOS Circuits and Technology Meeting, Atlanta, GA, USA, 2011, pp. 150-153. doi: 10.1109/BCTM.2011.6082769

27. P. J. Zampardi, M. Sun, C. Cismaru and J. Li, "Prospects for a BiCFET III-V HBT Process," 2012 IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), La Jolla, CA, USA, 2012, pp. 1-3. doi: 10.1109/CSICS.2012.6340116

28. W. Liu, D. Hill, D. Costa and J. S. Harris, "High-performance microwave AlGaAs-InGaAs Pnp HBT with high-DC current gain," in IEEE Microwave and Guided Wave Letters, vol. 2, no. 8, pp. 331-333, Aug. 1992. doi: 10.1109/75.153604

29. Peatman W. et al. InGaP-Plus™: advanced GaAs BiFET technology and applications // CS MANTECH Conference, May 14-17, 2007, Austin, Texas, USA. pp. 243-246.

30. Дворников О.В., Павлючик А.А., Прокопенко Н.Н., Чеховский В.А., Кунц А.В., Чумаков В.Е. Арсенид-галлиевый аналоговый базовый кристалл // Проблемы разработки перспективных микро- и наноэлектронных систем (МЭС). 2021. Выпуск 2. С. 47-54. doi:10.31114/2078-7707-2021-2-47-54

31. Патент RU 2784376, 2022 г.

32. Патент RU 2668981, 2018 г.

33. Патент RU 2771316, 2022 г.

34. Патент 2773912, фиг. 2, 2022 г.

35. Патент 2766868, фиг. 2, 2022 г.

36. Патент RU 2523947, 2014 г.