Результат интеллектуальной деятельности: УСТРОЙСТВО ФОРМИРОВАНИЯ ДВОИЧНОЙ ГРУППОВОЙ ПОСЛЕДОВАТЕЛЬНОСТИ

Вид РИД

Изобретение

Изобретение относится к системам связи множественного доступа с кодовым разделением (МДКР) и, в частности, к устройству формирования групповой двоичной последовательности в передающем устройстве базовой станции.

В современных системах радиосвязи с МДКР в прямом радиоканале от базовой станции к мобильным станциям применяется способ линейного кодового сложения m канальных сигналов, модулированных соответствующими фазоманипулированными m канальными последовательностями длиной N+1 элементов, равных ±1. При этом на выходе устройства сложения получается многоуровневая многоканальная последовательность длиной N+1 элементов, которая является линейной суммой канальных сигналов, модулированных канальными последовательностями. Дальнейшая передача этой многоуровневой многоканальной последовательности по радиолинии приводит к увеличению мощности многоуровневой многоканальной последовательности пропорционально m и, соответственно, невысокой помехозащищенности радиолинии. Для решения этой проблемы проводится жесткое ограничение групповой многоуровневой многоканальной последовательности по уровням ±1. Однако это приводит к существенным перекрестным помехам между уплотняемыми каналами при числе активных каналов m больше  что существенно снижает помехоустойчивость передачи m канальных сигналов [1].

что существенно снижает помехоустойчивость передачи m канальных сигналов [1].

Наиболее близким по технической сущности к предлагаемому изобретению является выбранное в качества прототипа устройство нелинейного кодового уплотнения каналов, являющееся составной частью синхронной адресной системой связи с жестким ограничением группового сигнала (Варакин Л.Е. Системы связи с шумоподобными сигналами. Раздел 12.3, стр. 231- М.: Радио и связь, 1985 - [2]). Устройство содержит синхронизатор, генератор фазоманипулированных последовательностей, m перемножителей, устройство уплотнения и ограничитель, причем на первые входы m умножителей поступают информационные двоичные сигналы из m каналов, выход синхронизатора соединен с управляющим входом генератора, m выходов которого подключены ко вторым входам m умножителей, выходы умножителей подключены к соответствующим входам устройства уплотнения, выход которого подключен ко входу ограничителя, а выход которого является выходом устройства нелинейного кодового уплотнения каналов.

Недостатками данного устройства являются существенные перекрестные помехи между уплотняемыми каналами при числе активных каналов m больше  Перекрестные помехи, вызванные самим нелинейным уплотнением каналов, приводят к появлению ошибок в каналах. Соответственно, данное устройство имеет низкую помехоустойчивость передачи m канальных сигналов при числе активных каналов m больше

Перекрестные помехи, вызванные самим нелинейным уплотнением каналов, приводят к появлению ошибок в каналах. Соответственно, данное устройство имеет низкую помехоустойчивость передачи m канальных сигналов при числе активных каналов m больше

Целью изобретения является повышение помехоустойчивости передаваемой информации за счет оптимизации двоичной групповой последовательности посредством замены некоторых элементов начальной последовательности на противоположные элементы.

Поставленная цель достигается тем, что в устройство формирования двоичной групповой последовательности, содержащее генератор N ортогональных последовательностей, m перемножителей, устройство уплотнения, ограничитель и синхронизатор, дополнительно введены m сумматоров, m линий задержки на длительность цикла, отдельная линия задержки на длительность цикла, m корреляторов, селектор минимального начального корреляционного отклика (КО), блок оптимизации, состоящий из m перемножителей, постоянного запоминающего устройства, линии задержки на половину длительности шага, инвертора, блока расчета корреляционных откликов, включающего в себя m сумматоров, m оперативных запоминающих устройств расчетных корреляционных откликов, m первых ключей, m вторых ключей и m оперативных запоминающих устройств оптимальных корреляционных откликов, и блока управления по минимальному корреляционному отклику, включающего в себя селектор минимального расчетного корреляционного отклика, оперативное запоминающее устройство минимального расчетного корреляционного отклика, блок сравнения, первый ключ, оперативное запоминающее устройство минимального оптимального корреляционного отклика и второй ключ, при этом m источников двоичных информационных сигналов подключены к первым входам соответствующих m перемножителей, соответствующие N выходов генератора ортогональных последовательностей подключены к соответствующим входам m сумматоров, выходы которых подключены к соответствующим вторым входам m перемножителей, соответствующие выходы которых подключены к соответствующим входам m линий задержки на длительность цикла, к соответствующим входам устройства уплотнения и к соответствующим первым входам m корреляторов, выход устройства уплотнения подключен ко входу ограничителя, выход которого подключен ко входу отдельной линии задержки на длительность цикла и ко вторым входам m корреляторов, выходы которых подключены к соответствующим m входам селектора минимального начального корреляционного отклика и к соответствующим входам m вторых ключей блока расчета корреляционных откликов, управляющий выход синхронизатора подключен к управляющему входу генератора N ортогональных последовательностей, к управляющим входам m корреляторов, к управляющему входу селектора минимального начального корреляционного отклика, к управляющим входам m вторых ключей блока расчета корреляционных откликов и к управляющему входу второго ключа блока управления по минимальному корреляционному отклику, выходы m соответствующих линий задержки на длительность цикла подключены к соответствующим первым входам m перемножителей блока оптимизации, отдельной линии задержки на длительность цикла подключен соответственно ко вторым входам m перемножителей блока оптимизации и ко входу линии задержки на половину длительности шага блока оптимизации, выход которой соединен со входом инвертора, выход селектора минимального начального корреляционного отклика подключен ко входу второго ключа блока управления по минимальному корреляционному отклику, выход постоянного запоминающего устройства блока оптимизации подключен к третьим входам m перемножителей блока оптимизации, выходы которых подключены к соответствующим первым входам m сумматоров блока расчета корреляционных откликов, выходы которых подключены к соответствующим входам m оперативных запоминающих устройств расчетных корреляционных откликов и к соответствующим m входам селектора минимального расчетного корреляционного отклика блока управления по минимальному корреляционному отклику, соответствующие выходы m оперативных запоминающих устройств расчетных корреляционных откликов подключены к соответствующим входам m первых ключей, выходы которых подключены к соответствующим первым входам m оперативных запоминающих устройств оптимальных корреляционных откликов, соответствующие выходы которых подключены к соответствующим вторым входам m сумматоров блока расчета корреляционных откликов, соответствующие выходы m вторых ключей блока расчета корреляционных откликов подключены к соответствующим вторым входам m оперативных запоминающих устройств оптимальных корреляционных откликов, выход селектора минимального расчетного корреляционного отклика блока управления по минимальному корреляционному отклику подключен к первому входу блока сравнения и ко входу оперативного запоминающего устройства минимального расчетного корреляционного отклика, выход которого подключен ко входу первого ключа, выход которого подключен к первому входу оперативного запоминающего устройства минимального оптимального корреляционного отклика, выход которого подключен ко второму входу блока сравнения, управляющий выход которого подключен к управляющему входу первого ключа, к управляющему входу инвертора блока оптимизации и управляющим входам m первых ключей блока расчета корреляционных откликов, при этом первые входы m перемножителей 3 (31-3m) являются входами информационных сигналов устройства формирования двоичной групповой последовательности, выходом которого является выход инвертора.

Сопоставимый анализ заявляемого изобретения с прототипом показывает, что предлагаемое устройство формирования двоичной групповой последовательности отличается от прототипа наличием новых блоков: m сумматоров, m линий задержки на длительность цикла, отдельной линии задержки на длительность цикла, m корреляторов, селектора минимального начального корреляционного отклика, блока оптимизации, состоящего из m перемножителей, постоянного запоминающего устройства, линии задержки на половину длительности шага, инвертора, блока расчета корреляционных откликов, включающего в себя m сумматоров, m оперативных запоминающих устройств расчетных корреляционных откликов, m первых ключей, m вторых ключей и m оперативных запоминающих устройств оптимальных корреляционных откликов, и блока управления по минимальному корреляционному отклику, включающего в себя селектор минимального расчетного корреляционного отклика, оперативное запоминающее устройство минимального расчетного корреляционного отклика, блок сравнения, первый ключ, оперативное запоминающее устройство минимального оптимального корреляционного отклика и второй ключ, а также изменением связей между известными блоками устройства.

Таким образом, благодаря новой совокупности признаков заявляемое устройство формирования двоичной групповой последовательности соответствует критерию изобретения «новизна». Сравнение заявляемого решения с другими техническими решениями показывает, что введенные блоки широко известны и дополнительного творчества по их реализации не потребуется. Однако при их введении в указанной связи с остальными элементами схемы в заявляемое устройство формирования двоичной групповой последовательности вышеуказанные блоки проявляют новые свойства, что приводит к достижению поставленной цели.

Это позволяет сделать вывод о соответствии предлагаемого технического решения критерию «существенные отличия».

Заявляемое решение явным образом не следует из уровня техники и имеет изобретательский уровень, а используемые в устройстве блоки широко известны в литературе, что подтверждает возможность промышленной реализации устройства формирования двоичной групповой последовательности.

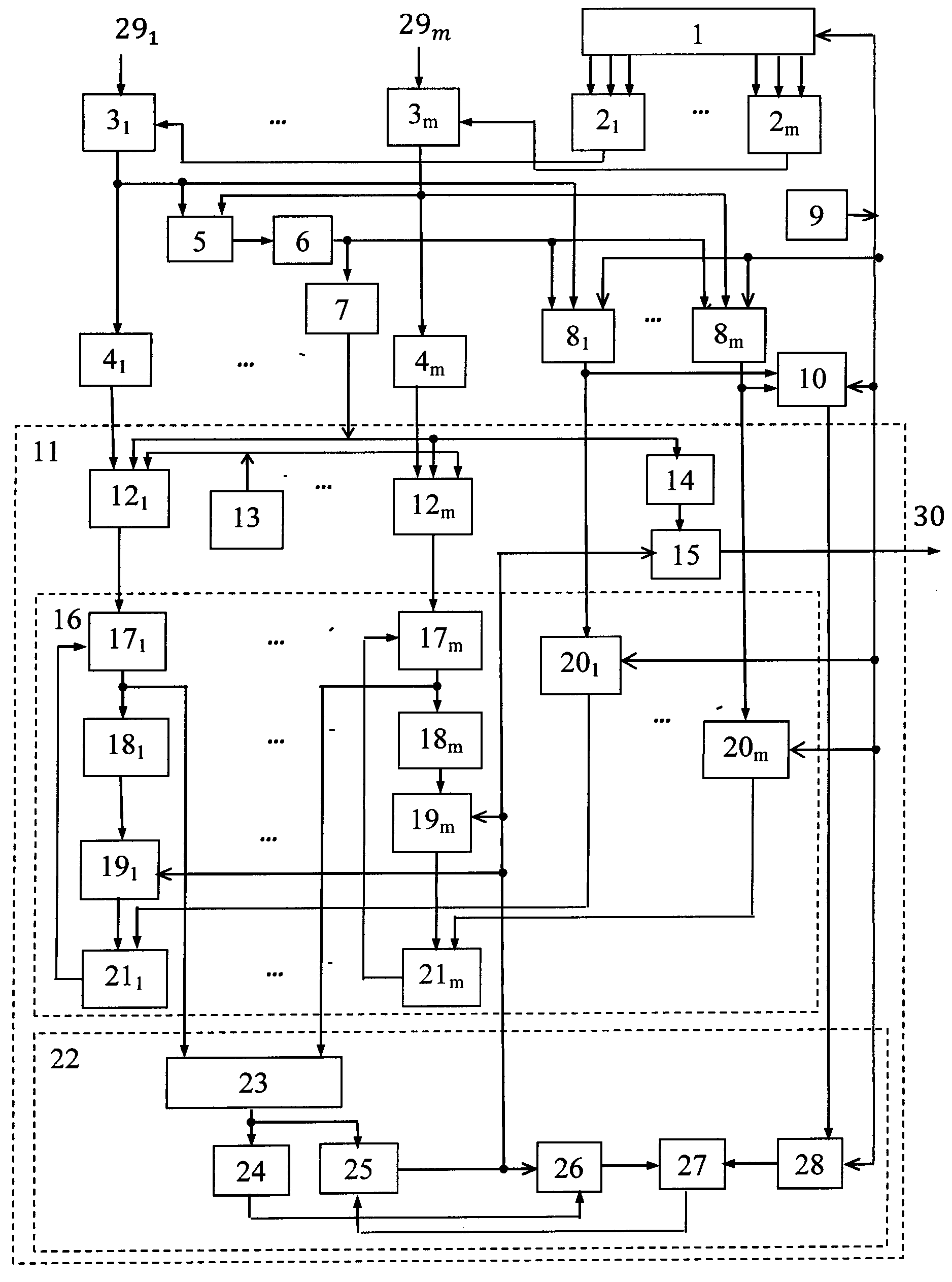

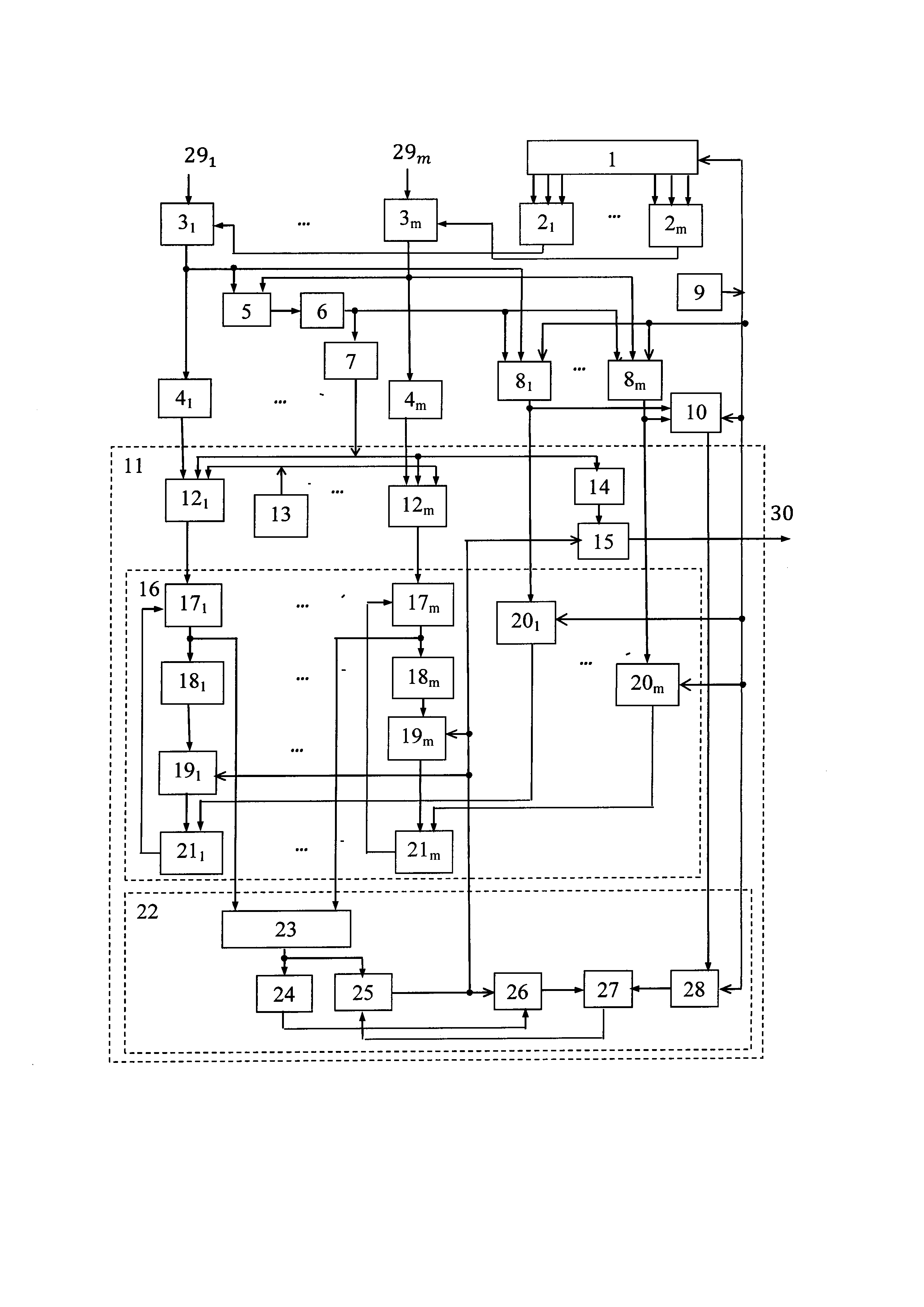

На чертеже приведена структурная электрическая схема устройства формирования двоичной групповой последовательности.

Устройство формирования двоичной групповой последовательности содержит генератор N ортогональных последовательностей 1, m сумматоров 2 (21-2m), m перемножителей 3 (31-3m), m линий задержки 4 (41-4m) на длительность цикла, устройство 5 уплотнения, ограничитель 6, отдельная линия задержки 7 на длительность цикла, m корреляторов 8 (81-8m), синхронизатор 9, селектор 10 минимального начального корреляционного отклика (КО), блок 11 оптимизации, состоящий из m перемножителей 12 (121-12m), постоянного запоминающего устройства 13, линии задержки 14 на половину длительности шага, инвертора 15, блока 16 расчета корреляционных откликов, включающего в себя m сумматоров 17 (171-17m), m оперативных запоминающих устройств 18 (181-18m) расчетных корреляционных откликов, m первых ключей 19 (191-19m), m вторых ключей 20 (201-20m) и m оперативных запоминающих устройств 21 (211-21m) оптимальных корреляционных откликов, блока 22 управления по минимальному корреляционному отклику, включающего в себя селектор 23 минимального расчетного корреляционного отклика, оперативное запоминающее устройство 24 минимального расчетного корреляционного отклика, блок 25 сравнения, первый ключ 26, оперативное запоминающее устройство 27 минимального оптимального корреляционного отклика и второй ключ 28, m источников 29 (291-29m) двоичных информационных сигналов и выход 30 двоичной групповой последовательности.

Соответствующие выходы m источников 29 (291-29m) двоичных информационных сигналов подключены к первым входам соответствующих m перемножителей 3 (31-3m), соответствующие N выходов генератора 1 ортогональных последовательностей подключены к соответствующим входам m сумматоров 2 (21-2m), выходы которых подключены к соответствующим вторым входам m перемножителей 3 (31-3m), соответствующие выходы которых подключены к соответствующим входам m линий задержки 4 (41-4m) на длительность цикла, к соответствующим входам устройства 5 уплотнения и к соответствующим первым входам m корреляторов, выходы которых подключены к соответствующим m входам селектора 10 начального корреляционного отклика и к соответствующим входам m вторых ключей 20 (201-20m) блока 16 расчета корреляционных откликов.

Управляющий выход синхронизатора 9 подключен к управляющему входу генератора N ортогональных последовательностей 1, к управляющим входам m корреляторов 8 (81-8m), к управляющему входу селектора 10 минимального начального корреляционного отклика, к управляющим входам m вторых ключей 20 (201-20m) блока 16 расчета корреляционных откликов и к управляющему входу второго ключа 28 блока 22 управления по минимальному корреляционному отклику. Выходы m соответствующих линий задержки 4 (41-4m) на длительность цикла подключены к соответствующим первым входам m перемножителей 12 (121-12m) блока 11 оптимизации, выход отдельной линии задержки 7 на длительность цикла подключен соответственно ко вторым входам m перемножителей 12 (121-12m) блока 11 оптимизации и ко входу линии задержки 14 на половину длительности шага блока 11 оптимизации, выход которой соединен со входом инвертора 15.

Выход селектора 10 минимального начального корреляционного отклика подключен ко входу второго ключа 28 блока 22 управления по минимальному корреляционному отклику, выход постоянного запоминающего устройства 13 блока 11 оптимизации подключен к третьим входам m перемножителей 12 (121-12m) блока 11 оптимизации, выходы которых подключены к соответствующим первым входам m сумматоров 17 (171-17m) блока 16 расчета корреляционных откликов, выходы которых подключены к соответствующим входам m оперативных запоминающих устройств 18 (181-18m) расчетных корреляционных откликов и к соответствующим m входам селектора 23 минимального расчетного корреляционного отклика блока 22 управления по минимальному корреляционному отклику. Соответствующие выходы m оперативных запоминающих устройств 18 (181-18m) расчетных корреляционных откликов подключены к соответствующим входам m первых ключей 19 (191-19m), выходы которых подключены к соответствующим первым входам m оперативных запоминающих устройств 21 (211-21m) оптимальных корреляционных откликов, соответствующие выходы которых подключены к соответствующим вторым входам m сумматоров 17 (171-17m) блока 16 расчета корреляционных откликов, соответствующие выходы m вторых ключей 20 (201-20m) блока 16 расчета корреляционных откликов подключены к соответствующим вторым входам m оперативных запоминающих устройств 21 (211-r21m) оптимальных корреляционных откликов. Выход селектора 23 минимального расчетного корреляционного отклика блока 22 управления по минимальному корреляционному отклику подключен к первому входу блока 25 сравнения и ко входу оперативного запоминающего устройства 24 минимального расчетного корреляционного отклика, выход которого подключен ко входу первого ключа 26, выход которого подключен к первому входу оперативного запоминающего устройства 27 минимального оптимального корреляционного отклика, выход которого подключен ко второму входу блока 25 сравнения, управляющий выход которого подключен к управляющему входу первого ключа 26, к управляющему входу инвертора 15 блока 11 оптимизации и управляющим входам m первых ключей 19 (191-19m) блока 16 расчета корреляционных откликов, при этом первые входы m перемножителей 3 (31-3m) являются входами информационных сигналов устройства формирования двоичной групповой последовательности, выходом 30 которой является выход инвертора 15, с которого поступает оптимальная двоичная групповая последовательность (ДТП).

Выделим в процессе оптимизации двоичной групповой последовательности, состоящей из N+1 элементов, равных ±1, начальный цикл работы длительностью Т0, в течение которого рассчитываются необходимые параметры начальной двоичной групповой последовательности и цикл коррекции ДТП длительностью Т0, в течение которого проводится оптимизация начальной ДТП. Каждый цикл длительностью Т0 состоит из (N+1) шагов коррекции длительностью, равной длительности t0 элемента двоичной групповой последовательности.

Устройство работает следующим образом.

От m источников 29 (291-29m) двоичных информационных сигналов m информационных двоичных сигналов, равных длительностью ±1, поступают на информационные входы m перемножителей 3 (31-3m) устройства формирования двоичной групповой последовательности (ДТП).

В течение начального цикла работы рассчитываются: m канальных информационных последовательностей, равных произведению m канальных последовательностей на соответствующие m информационных двоичных сигналов, суммарная последовательность, элементы которой на каждом шаге равны суммам m элементов канальных информационных последовательностей, начальная двоичная групповая последовательность.

В начале каждого цикла длительностью Т0, равного длительности ортогональных последовательностей, с выхода синхронизатора 9 сигнал цикловой синхронизации t1 длительностью t0 поступает на управляющий вход генератора ортогональных последовательностей 1, на управляющий вход селектора 10 минимального начального корреляционного отклика, на управляющие входы m корреляторов 8 (81-8m), на управляющие входы m вторых ключей 20 (201-20m) блока 11 оптимизации и на управляющий вход второго ключа 28 блока 22 управления по минимальному корреляционному отклику. При поступлении сигнала цикловой синхронизации t1 начинается начальный цикл работы устройства формирования ДТП.

На выходе генератора N ортогональных последовательностей 1 множество ортогональных последовательностей, состоящих из N+1 элементов, равных ±1 длительностью t0, разделено на предварительно выбранные непересекающиеся m подмножеств ортогональных последовательностей, состоящих из одной или нескольких ортогональных последовательностей. Длительность элементов ортогональных последовательностей равна t0. Нулевая ортогональная последовательность не используется. Каждая последовательность используется только один раз в каком-либо из m подмножеств последовательностей для формирования ортогональных канальных последовательностей. Предварительный выбор непересекающихся m подмножеств ортогональных последовательностей производится для снижения перекрестных помех между подмножествами. Эти m подмножеств ортогональных последовательностей поступают на соответствующие входы m сумматоров 2 (21-2m).

С выходов m сумматоров 2 (21-2m), полученные многоуровневые канальные последовательности поступают на вторые входы соответствующих m перемножителей 3 (31-3m). Каждый элемент многоуровневых канальных последовательностей длительностью t0 равен сумме элементов ортогональных последовательностей, которые затем поступают на соответствующий перемножитель 3 (31-3m).

На соответствующие первые входы m перемножителей 3 (31-3m) от m источников двоичных информационных сигналов 29 (291-29m) поступают m информационных двоичных сигналов равных ±1, длительностью Т0. В m перемножителях 3 (31-3m) канальные последовательности перемножаются на соответствующие информационные двоичные сигналы. С выходов перемножителей 3(31-3m) полученные канальные информационные последовательности поступают на устройство уплотнения 5, на входы соответствующих m линий задержки 4 (41-4m) на длительность цикла, а также на соответствующие вторые входы m корреляторов 8 (81-8m).

В m линиях задержки 4 (41-4m) на длительность цикла производится задержка на время Т0. По окончании начального цикла работы с выходов m линий задержки 4 (41-4m) на длительность цикла канальные информационные последовательности поступают на первые входы соответствующих m перемножителей 12 (121-12m) блока 11 оптимизации.

С выхода устройства 5 уплотнения многоуровневая суммарная групповая последовательность поступает на вход ограничителя 6. В ограничителе 6 производится жесткое ограничение элементов суммарной групповой последовательности согласно правилу: если элемент многоуровневой суммарной групповой последовательности на входе ограничителя меньше нуля, то на выходе ограничителя 6 соответствующий элемент двоичной групповой последовательности равен минус 1, если же на входе ограничителя 6 элемент многоуровневой суммарной последовательности больше или равен 0, то на выходе ограничителя 6 соответствующий элемент ДТП равен плюс 1.

С выхода ограничителя 6 начальная двоичная групповая последовательность, состоящая из N+1 двоичных элементов, равных ±1, поступает на соответствующие первые входы m корреляторов 8 (81-8m) и на вход отдельной линии задержки 7 на длительность цикла, в которой производится задержка на время Т0. По окончании начального цикла работы с выхода отдельной линии задержки 7 на длительность цикла начальная ДТП в течение цикла коррекции поступает на вторые входы соответствующих m перемножителей 12 (121-12m) блока 11 оптимизации и на вход линии задержки 14 на половину длительности шага блока 11 оптимизации.

В конце начального цикла работы на выходе m корреляторов 8 (81-8m) рассчитываются m начальных корреляционных откликов, равных сумме произведений соответствующих элементов начальной ДГП на соответствующие элементы канальных информационных последовательностей, при поступлении от синхронизатора 9 сигнала цикловой синхронизации t1 в начале цикла. Эти m начальных корреляционных откликов поступают на m соответствующих входов селектора 10 минимального начального корреляционного отклика и на входы соответствующих m вторых ключей 20 (201-20m) блока 16 расчета корреляционных откликов. Если ограничение не привело к ошибкам, то все начальные корреляционные отклики должны быть положительными. Если какой-либо начальный корреляционный отклик является отрицательным или равен нулю, то это означает, что ограничение суммарной групповой последовательности в ограничителе 6 привело к формированию ошибки в соответствующем канале.

Алгоритм работы селектора 10 минимального начального корреляционного отклика на последнем шаге начального цикла работы заключается в выборе минимального из m начальных корреляционных откликов и описывается математическим выражением

bo,min=minj bo,j, где j=1, m;

где bo,j - j-й начальный корреляционный отклик,

bo,min - минимальный начальный корреляционный отклик.

Соответственно, на начальном шаге цикла коррекции с выхода селектора 10 минимального начального корреляционного отклика на вход второго ключа 28 блока 22 управления по минимальному корреляционному отклику поступит начальный минимальный корреляционный отклик.

Блок 11 оптимизации предназначен для проведения пошаговой оптимизации начальной ДТП в течении цикла коррекции, которая заключается в вычислении на каждом текущем шаге m расчетных корреляционных откликов при условии замены текущего элемента ДГП на противоположное значение, и принятие решения по критерию максимума минимального расчетного корреляционного отклика проводить эту замену или нет.

С выхода синхронизатора 9 поступает следующий сигнал цикловой синхронизации, который запускает следующий вышеописанный начальный цикл, одновременно с этим в блоке 11 оптимизации проводится цикл коррекции длительностью То полученной начальной двоичной групповой последовательности.

В течение цикла коррекции ДГП с выхода постоянного запоминающего устройства 13 поступает постоянная величина минус 2 на соответствующие третьи входы m перемножителей 12 (121-12m), с выходов которых на первые входы соответствующих m сумматоров 17 (171-17m) на каждом шаге коррекции длительностью to поступают соответствующие m расчетных отклонений корреляционных откликов длительностью to, которые будут в случае замены текущего элемента ДТП на противоположное значение.

Блок 16 расчета корреляционных откликов предназначен для хранения оптимальных на предыдущем шаге корреляционных откликов и вычисления расчетных корреляционных откликов на текущем шаге, которые будут в случае замены текущего элемента ДГП на противоположное значение, а также замены соответствующих оптимальных на предыдущем шаге корреляционных откликов на соответствующие текущие расчетные корреляционные отклики при поступлении положительного сигнала управления от блока 22 управления по минимальному корреляционному отклику.

Блок 22 управления по минимальному корреляционному отклику предназначен для вычисления минимального расчетного корреляционного отклика из расчетных корреляционных откликов на текущем шаге, сравнению его с оптимальным минимальным корреляционным откликом на предыдущем шаге и выработке сигнала управления по результату этого сравнения.

В блоке 16 расчета корреляционных откликов в течение цикла коррекции с помощью расчетных отклонений корреляционных откликов на каждом шаге коррекции производится вычисление расчетных корреляционных откликов длительностью to, которые соответствуют замене текущего элемента ДТП на противоположный элемент. Кроме того, на этом шаге коррекции в оперативном запоминающем устройстве 21 (211-21m) оптимальных корреляционных откликов блока 16 расчета КО сохраняются оптимальные на предыдущем шаге коррекции корреляционные отклики.

В начале цикла коррекции с выходов соответствующих m корреляторов 8 (81-8m) блока 11 оптимизации начальные корреляционные отклики, длительностью to, поступают на входы соответствующих m вторых ключей 20 (201-20m) блока 16 расчета КО, а также с выхода селектора 10 минимального начального корреляционного отклика минимальный начальный корреляционный отклик длительностью to поступает на вход ключа 28 блока 22 управления по минимальному КО.

На начальном шаге цикла коррекции с выхода синхронизатора на управляющие входы соответствующих m вторых ключей 20 (201-20m) блока 16 расчета КО, а также на управляющий вход второго ключа 28 блока 22 управления по минимальному КО поступает сигнал цикловой синхронизации, который открывает эти ключи на время to. В результате этого в начале цикла коррекции начальные корреляционные отклики через открытые m вторых ключей 20 (201-20m) блока 16 расчета КО записываются в соответствующие m оперативных запоминающих устройств 21 (211-21m) оптимальных КО, а минимальный начальный корреляционный отклик через открытый второй ключ 28 блока 22 управления записывается в оперативное запоминающее устройство 27 минимального оптимального корреляционного отклика блока 22 управления по минимальному КО. Соответственно, на начальном шаге цикла коррекции оптимальными становятся начальные корреляционные отклики. По окончании начального шага коррекции m вторых ключей 20 (201-20m) блока 16 расчета КО 16, а также второй ключ 28 блока 22 управления по минимальному КО закрываются до окончания всего цикла коррекции.

На начальном шаге цикла коррекции начальные корреляционные отклики с выходов соответствующих m оперативных запоминающих устройств 21 (211-21m) оптимальных КО поступают на вторые входы соответствующих m сумматоров 17 (171-17m). Соответственно, на начальном шаге цикла коррекции соответствующие m начальных отклонений корреляционных откликов длительностью t0 поступают на первые входы соответствующих m сумматоров 17 (171-17m). С выходов соответствующих m сумматоров 17 (171-17m) m начальных расчетных КО поступают на входы соответствующих m оперативных запоминающих устройств 18 (181-18m) расчетных КО и на соответствующие m входы селектора 23 минимального расчетного КО блока 22 управления по минимальному корреляционному отклику.

В дальнейшем на каждом шаге коррекции с выходов соответствующих m оперативных запоминающих устройств 21 (211-21m) оптимальных КО хранящиеся в них оптимальные на предыдущем шаге коррекции корреляционные отклики поступают на вторые входы соответствующих m сумматоров 17 (171-17m). С выходов соответствующих m сумматоров 17 (171-17m) на входы соответствующих m оперативных запоминающих устройств 18 (181-18m) расчетных КО и на соответствующие m входы селектора 23 минимального расчетного КО блока 22 управления по минимальному КО поступают m расчетных корреляционных откликов длительностью t0, равных сумме соответствующих отклонений корреляционных откликов и соответствующих оптимальных на предыдущем шаге коррекции корреляционных откликов. С выходов соответствующих m оперативных запоминающих устройств 18 (181-18m) расчетных КО на входы соответствующих m первых ключей 19 (191-19m) на i-м шаге коррекции поступают расчетные корреляционные отклики, длительностью t0.

Во второй половине текущего шага коррекции с управляющего выхода блока 25 сравнения блока 22 управления по минимальному КО на управляющие входы m первых ключей 19 (191-9m) поступает сигнал управления коррекцией текущего элемента ДГП. Если сигнал управления равен 0, то m первых ключей 19 (191-19m) закрыты. Если сигнал управления равен 1, то m первых ключей 19 (191-19m) открываются и m расчетных корреляционных откликов во второй половине текущего шага коррекции поступают на первые входы m оперативных запоминающих устройств 21 (211-21m) оптимальных КО, в которые эти расчетные корреляционные отклики записываются в качестве оптимальных корреляционных откликов для следующего шага коррекции.

В блоке 22 управления по минимальному КО решается: сохранить соответствующий элемент ДГП или произвести замену текущего элемента ДГП на противоположное значение. Для этого блоке 22 управления по минимальному КО на каждом шаге коррекции из m расчетных корреляционных откликов в селекторе 23 минимального расчетного КО выбирается минимальный расчетный корреляционный отклик. Алгоритм работы селектора 23 минимального расчетного КО аналогичен алгоритму работы селектора 10 минимального начального корреляционного отклика и описывается математическим выражением

bi,min=minj bi,,j, где i=0, N, j=1, m;

где bi,j - j-й расчетный корреляционный отклик на i-м шаге коррекции,

bi,min - минимальный расчетный корреляционный отклик на i-м шаге коррекции.

На каждом шаге коррекции на основании сравнения оптимального на предыдущем шаге коррекции минимального КО и расчетного на текущем шаге коррекции минимального КО блок 25 сравнения блока 22 управления по минимальному КО во второй половине текущего шага коррекции формирует сигнал управления. Если расчетный на текущем шаге коррекции минимальный корреляционный отклик больше, чем оптимальный минимальный КО на предыдущем шаге коррекции, то сигнал управления на выходе блока 25 сравнения будет равен 1. В остальных случаях сигнал управления на выходе блока 25 сравнения будет равен 0. Если сигнал управления равен 1, то производится замена текущего элемента двоичной групповой последовательности на противоположный элемент, а также в блоке 22 управления по минимальному КО дополнительно производится замена оптимального на предыдущем шаге коррекции минимального КО на расчетный минимальный корреляционный отклик. Если сигнал управления равен 0, то сохраняется текущий элемент ДГП и сохраняется оптимальный на предыдущем шаге коррекции минимальный КО в ОЗУ 27 минимального оптимального корреляционного отклика.

В блоке 16 расчета КО при поступлении с управляющего выхода блока 25 сравнения блока 22 управления по минимальному КО сигнала управления коррекцией, равного 1, производится замена m оптимальных на предыдущем шаге коррекции корреляционных откликов на m расчетных на текущем шаге коррекции корреляционных откликов, которые теперь становятся оптимальными на следующем шаге коррекции.

В линии задержки 14 на половину длительности шага блока 11 оптимизации производится задержка текущего элемента ДГП на время, равное to/2, необходимое для согласования поступления элемента ДТП на вход инвертора 15 блока 11 оптимизации с поступлением во второй половине текущего шага коррекции от управляющего выхода блока 25 сравнения блока 22 управления по минимальному КО сигнала управления коррекцией текущего элемента ДТП на управляющий вход инвертора 15 блока 11 оптимизации. При поступлении на управляющий вход инвертора 15 сигнала управления коррекцией, равного 1, производится инвертирование текущего элемента ДГП в противоположный элемент, а при поступлении на управляющий вход инвертора 15 сигнала управления коррекцией, равного 0, текущий элемент ДГП сохраняется. Соответственно, с выхода инвертора 15 на выход 30 устройства формирования ДГП с задержкой на время t0/2 поступает оптимальная ДТП, длительностью Т0. При этом выход 30 является выходом устройства формирования двоичной групповой последовательности.

Технический результат от предлагаемого устройства заключается в повышении помехоустойчивости передаваемой информации, который достигается за счет введения в устройство новых элементов и оптимизации двоичной групповой последовательности посредством замены некоторых элементов начальной последовательности на противоположные элементы. В результате этого достигается устранение всех ошибок, заложенных в двоичной групповой последовательности вследствие перекрестных помех при жестком ограничении суммарной последовательности. Это позволяет повысить помехоустойчивость передаваемой групповой последовательности по сравнению с прототипом в несколько раз.

Источники информации.

1. Варакин Л.Е. Теория систем сигналов. - М.: «Сов. Радио», 1978, стр. 79-87.

2. Варакин Л.Е. Системы связи с шумоподобными сигналами. Раздел 12.3, стр. 231. - М.: Радио и связь, 1985 (прототип).

Устройство формирования двоичной групповой последовательности, содержащее генератор N ортогональных последовательностей, m перемножителей, устройство уплотнения, ограничитель и синхронизатор, отличающееся тем, что в него дополнительно введены m сумматоров, m линий задержки на длительность цикла, отдельная линия задержки на длительность цикла, m корреляторов, селектор минимального начального корреляционного отклика, блок оптимизации, состоящий из m перемножителей, постоянного запоминающего устройства, линии задержки на половину длительности шага, инвертора, блока расчета корреляционных откликов, включающего в себя m сумматоров, m оперативных запоминающих устройств расчетных корреляционных откликов, m первых ключей, m вторых ключей и m оперативных запоминающих устройств оптимальных корреляционных откликов, и блока управления по минимальному корреляционному отклику, включающего в себя селектор минимального расчетного корреляционного отклика, оперативное запоминающее устройство минимального расчетного корреляционного отклика, блок сравнения, первый ключ, оперативное запоминающее устройство минимального оптимального корреляционного отклика и второй ключ, при этом m источников двоичных информационных сигналов подключены к первым входам соответствующих m перемножителей, соответствующие N выходов генератора ортогональных последовательностей подключены к соответствующим входам m сумматоров, выходы которых подключены к соответствующим вторым входам m перемножителей, соответствующие выходы которых подключены к соответствующим входам m линий задержки на длительность цикла, к соответствующим входам устройства уплотнения и к соответствующим первым входам m корреляторов, выход устройства уплотнения подключен ко входу ограничителя, выход которого подключен ко входу отдельной линии задержки на длительность цикла и ко вторым входам m корреляторов, выходы которых подключены к соответствующим m входам селектора минимального начального корреляционного отклика и к соответствующим входам m вторых ключей блока расчета корреляционных откликов, управляющий выход синхронизатора подключен к управляющему входу генератора N ортогональных последовательностей, к управляющим входам m корреляторов, к управляющему входу селектора минимального начального корреляционного отклика, к управляющим входам m вторых ключей блока расчета корреляционных откликов и к управляющему входу второго ключа блока управления по минимальному корреляционному отклику, выходы m соответствующих линий задержки на длительность цикла подключены к соответствующим первым входам m перемножителей блока оптимизации, выход отдельной линии задержки на длительность цикла подключен соответственно ко вторым входам m перемножителей блока оптимизации и ко входу линии задержки на половину длительности шага блока оптимизации, выход которой соединен со входом инвертора, выход селектора минимального начального корреляционного отклика подключен ко входу второго ключа блока управления по минимальному корреляционному отклику, выход постоянного запоминающего устройства блока оптимизации подключен к третьим входам m перемножителей блока оптимизации, выходы которых подключены к соответствующим первым входам m сумматоров блока расчета корреляционных откликов, выходы которых подключены к соответствующим входам m оперативных запоминающих устройств расчетных корреляционных откликов и к соответствующим m входам селектора минимального расчетного корреляционного отклика блока управления по минимальному корреляционному отклику, соответствующие выходы m оперативных запоминающих устройств расчетных корреляционных откликов подключены к соответствующим входам m первых ключей, выходы которых подключены к соответствующим первым входам m оперативных запоминающих устройств оптимальных корреляционных откликов, соответствующие выходы которых подключены к соответствующим вторым входам m сумматоров блока расчета корреляционных откликов, соответствующие выходы m вторых ключей блока расчета корреляционных откликов подключены к соответствующим вторым входам m оперативных запоминающих устройств оптимальных корреляционных откликов, выход селектора минимального расчетного корреляционного отклика блока управления по минимальному корреляционному отклику подключен к первому входу блока сравнения и ко входу оперативного запоминающего устройства минимального расчетного корреляционного отклика, выход которого подключен ко входу первого ключа, выход которого подключен к первому входу оперативного запоминающего устройства минимального оптимального корреляционного отклика, выход которого подключен ко второму входу блока сравнения, управляющий выход которого подключен к управляющему входу первого ключа, к управляющему входу инвертора блока оптимизации и управляющим входам m первых ключей блока расчета корреляционных откликов, при этом первые входы m перемножителей 3 (3-3) являются входами информационных сигналов устройства формирования двоичной групповой последовательности, выходом которого является выход инвертора.