Результат интеллектуальной деятельности: ПРОМЕЖУТОЧНЫЙ КАСКАД ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С ПАРАФАЗНЫМ ВЫХОДОМ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ

Вид РИД

Изобретение

Предлагаемое изобретение относится к области радиотехники и микроэлектроники и может быть использовано в аналоговых микросхемах (АМ) и аналого-цифровых интерфейсах датчиков, работающих в тяжелых условиях эксплуатации (низкие температуры, проникающая радиация).

Одним из базовых функциональных узлов современных аналоговых микросхем, например, операционных усилителей (ОУ) и компараторов, является промежуточный каскад (ПК), обеспечивающий согласование входного дифференциального каскада и выходного буферного усилителя, который во многих случаях имеет единичный коэффициент усиления по напряжению. Для повышения симметрии в АМ на полевых транзисторах находят применение ПК на основе двух «перегнутых» каскодов [1-12] с четырьмя входами, два токовых входа которых согласованы с шиной положительного источника питания, а два других входа согласованы с шиной отрицательного источника питания. При этом в качестве входных каскадов аналоговых устройств с такими ПК используются дифференциальные усилители с четырьмя токовыми выходами – так называемый dual-input-stage [1-12]. Таким образом, в современных ОУ промежуточный каскад решает проблему обеспечения заданных коэффициентов усиления по току, что важно для многих применений. При этом достаточно перспективным для тяжелых условий эксплуатации являются ПК на полевых транзисторах с управляющим p-n переходом (JFet). В работах [13-23] показано, что на основе JFet возможно построение аналоговых микросхем, работающих в диапазоне криогенных температур и в условиях воздействия потока нейтронов и гамма-квантов. Предлагаемое устройство относится к данному классу микроэлектронных изделий. На его основе возможно построение низкотемпературных АМ с малым уровнем шумов.

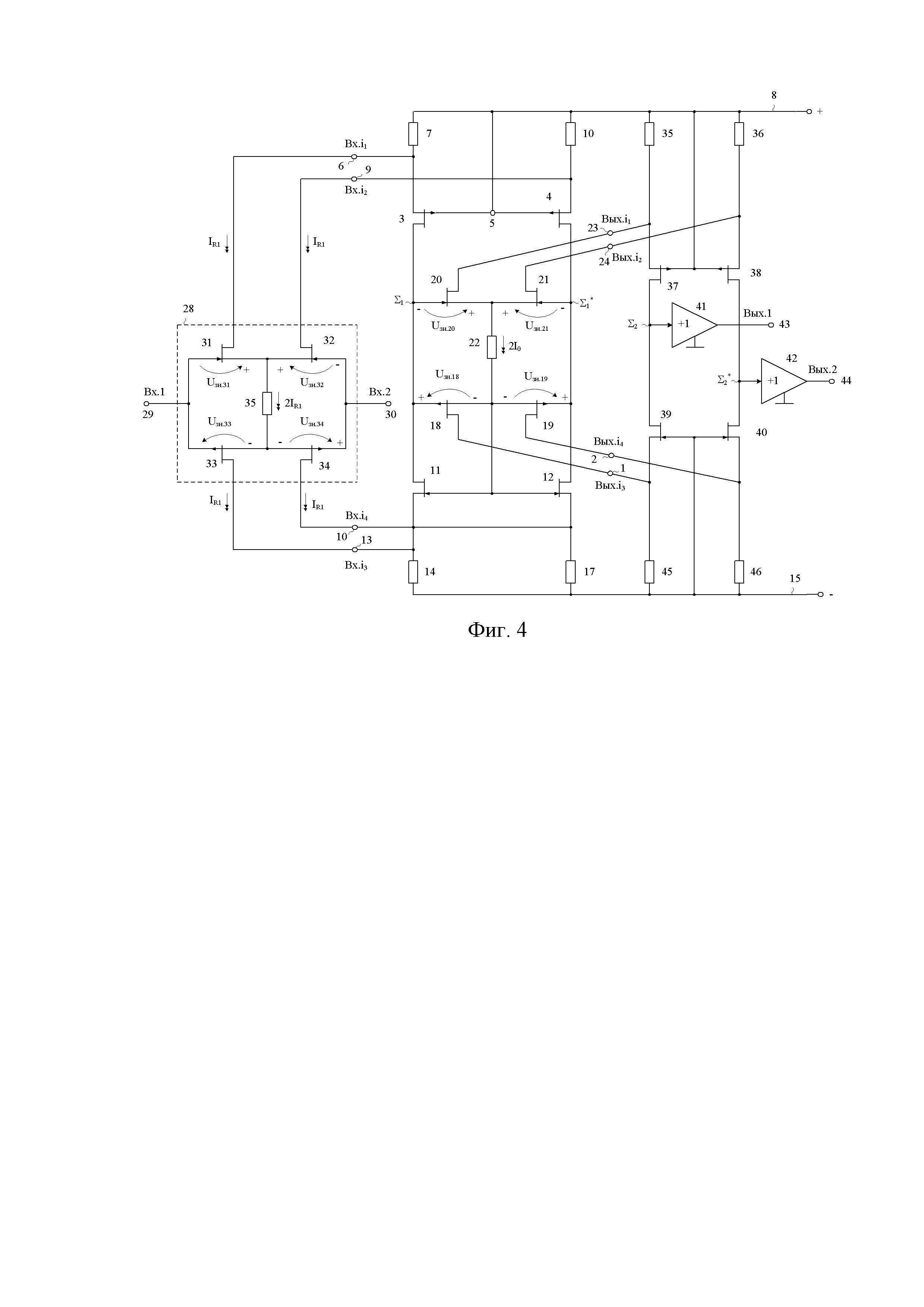

Ближайшим прототипом (фиг. 1) заявляемого устройства является промежуточный каскад в структуре ОУ по патенту US 8.604.878, fig.4. Он содержит (фиг. 1) первый 1 и второй 2 токовые выходы устройства, первый 3 и второй 4 входные полевые транзисторы, затворы которых объединены и подключены к источнику напряжения смещения 5, причем исток первого 3 входного полевого транзистора соединен с первым 6 токовым входом устройства и через первый 7 согласующий двухполюсник соединен с первой 8 шиной источника питания, а исток второго 4 входного полевого транзистора соединен со вторым 9 токовым входом устройства и через второй 10 согласующий двухполюсник соединен с первой 8 шиной источника питания, третий 11 и четвертый 12 входные полевые транзисторы с объединенными затворами, сток третьего 11 входного полевого транзистора соединен со стоком первого 3 входного полевого транзистора, сток четвертого 12 входного полевого транзистора соединен со стоком второго 4 входного полевого транзистора, причем исток третьего 11 входного полевого транзистора соединен с третьим 13 токовым входом устройства и через третий 14 согласующий двухполюсник соединен со второй 15 шиной источника питания, а исток четвертого 12 входного полевого транзистора соединен с четвертым 16 токовым входом устройства и через четвертый 17 согласующий двухполюсник соединен со второй 15 шиной источника питания.

Существенный недостаток известного ПК фиг. 1 состоит в том, что он имеет единичный коэффициент усиления по току со входов 6, 9, 13, 16 относительно первого 1 и второго 2 токовых выходов. Это не позволяет получить на его основе повышенные коэффициенты усиления соответствующих АМ.

Основная задача предлагаемого изобретения состоит в создании стабильно работающего в диапазоне криогенных температур и в условиях проникающей радиации промежуточного каскада с повышенным коэффициентом усиления по току со входов 6, 9, 13, 16 к основным первому 1 и второму 2 токовым выходам. Это позволяет создавать на основе заявляемого ПК широкий спектр CJFet низкотемпературных и радиационно-стойких аналоговых устройств с повышенным коэффициентом усиления по напряжению.

Поставленная задача достигается тем, что в ПК фиг.1, содержащем первый 1 и второй 2 токовые выходы устройства, первый 3 и второй 4 входные полевые транзисторы, затворы которых объединены и подключены к источнику напряжения смещения 5, причем исток первого 3 входного полевого транзистора соединен с первым 6 токовым входом устройства и через первый 7 согласующий двухполюсник соединен с первой 8 шиной источника питания, а исток второго 4 входного полевого транзистора соединен со вторым 9 токовым входом устройства и через второй 10 согласующий двухполюсник соединен с первой 8 шиной источника питания, третий 11 и четвертый 12 входные полевые транзисторы с объединенными затворами, сток третьего 11 входного полевого транзистора соединен со стоком первого 3 входного полевого транзистора, сток четвертого 12 входного полевого транзистора соединен со стоком второго 4 входного полевого транзистора, причем исток третьего 11 входного полевого транзистора соединен с третьим 13 токовым входом устройства и через третий 14 согласующий двухполюсник соединен со второй 15 шиной источника питания, а исток четвертого 12 входного полевого транзистора соединен с четвертым 16 токовым входом устройства и через четвертый 17 согласующий двухполюсник соединен со второй 15 шиной источника питания, предусмотрены новые элементы и связи – в схему введены первый 18 и второй 19 дополнительные полевые транзисторы с объединенными истоками, общий узел которых связан с объединенными затворами третьего 11 и четвертого 12 входных полевых транзисторов, сток первого 18 дополнительного полевого транзистора соединен с первым 1 токовым выходом устройства, сток второго 19 дополнительного полевого транзистора подключен ко второму 2 токовому выходу устройства, затвор первого 18 дополнительного полевого транзистора соединен со стоком первого 3 входного полевого транзистора, затвор второго 19 дополнительного полевого транзистора подключен к стоку второго 4 входного полевого транзистора, объединенные истоки первого18 и второго 19 дополнительных полевых транзисторов связаны с объединенными истоками третьего 20 и четвертого 21 дополнительных полевых транзисторов через дополнительный двухполюсник 22, причем затвор третьего 20 дополнительного полевого транзистора соединен со стоком первого 3 входного полевого транзистора, затвор четвертого 21 дополнительного полевого транзистора соединен со стоком второго 4 входного полевого транзистора, сток третьего 20 дополнительного полевого транзистора подключен к первому 23 дополнительному токовому выходу устройства, а сток четвертого 21 дополнительного полевого транзистора связан со вторым 24 дополнительным токовым выходом устройства.

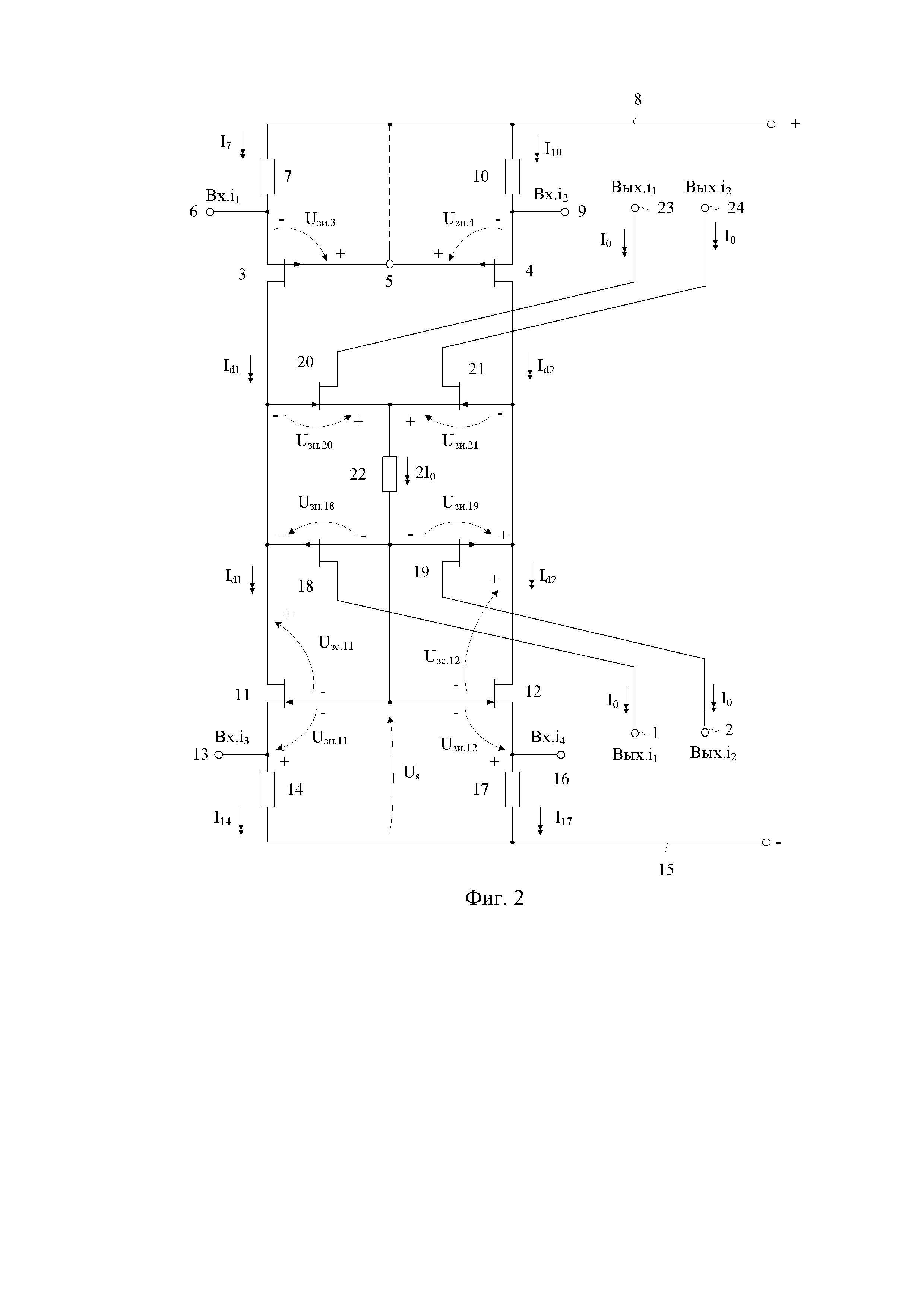

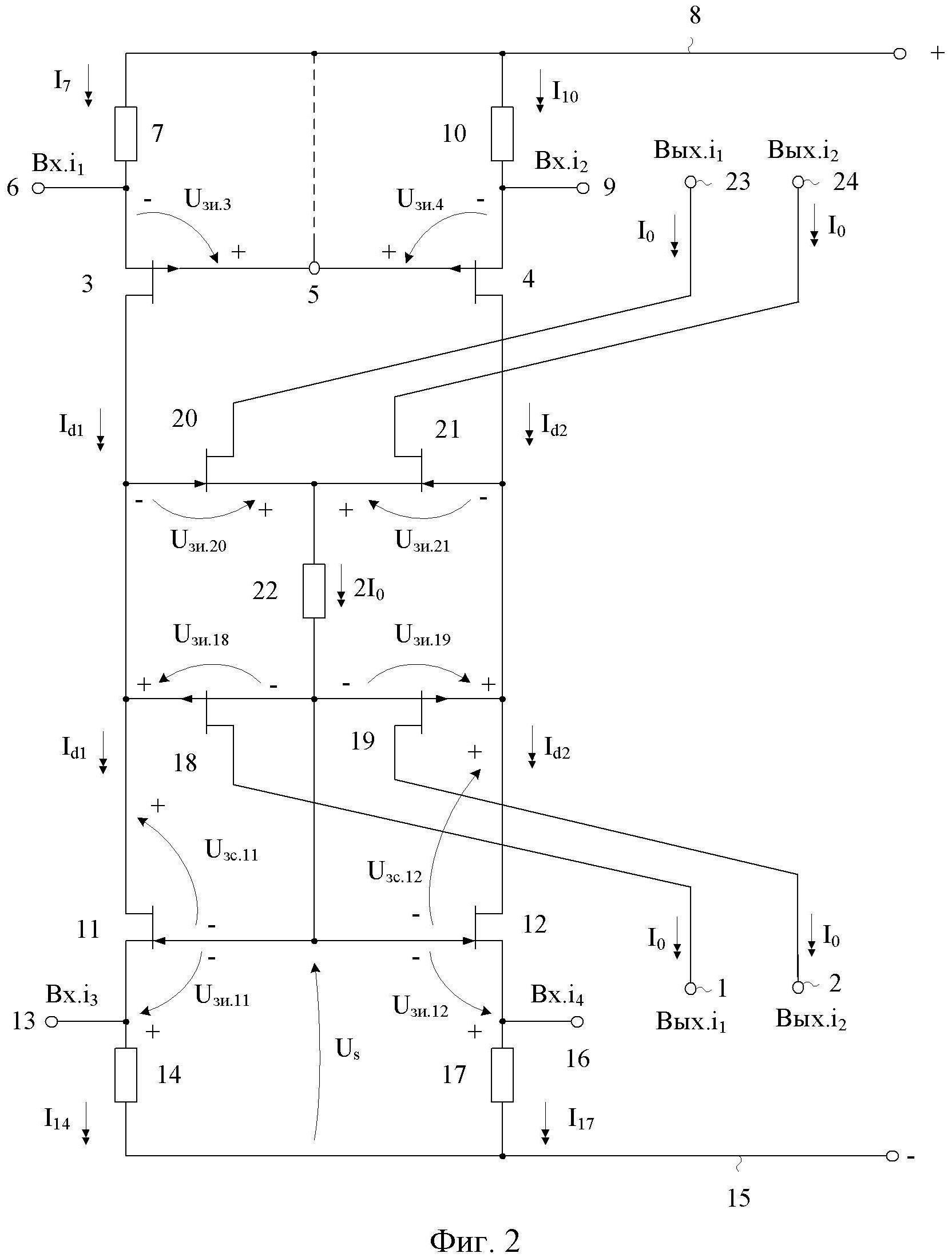

На чертеже фиг. 1 показана схема ПК-прототипа, который используется в структуре ОУ по патенту US 8.604.878, fig.4. На чертеже фиг. 2 представлена схема заявляемого устройства в соответствии с п. 1 и п. 2 формулы изобретения.

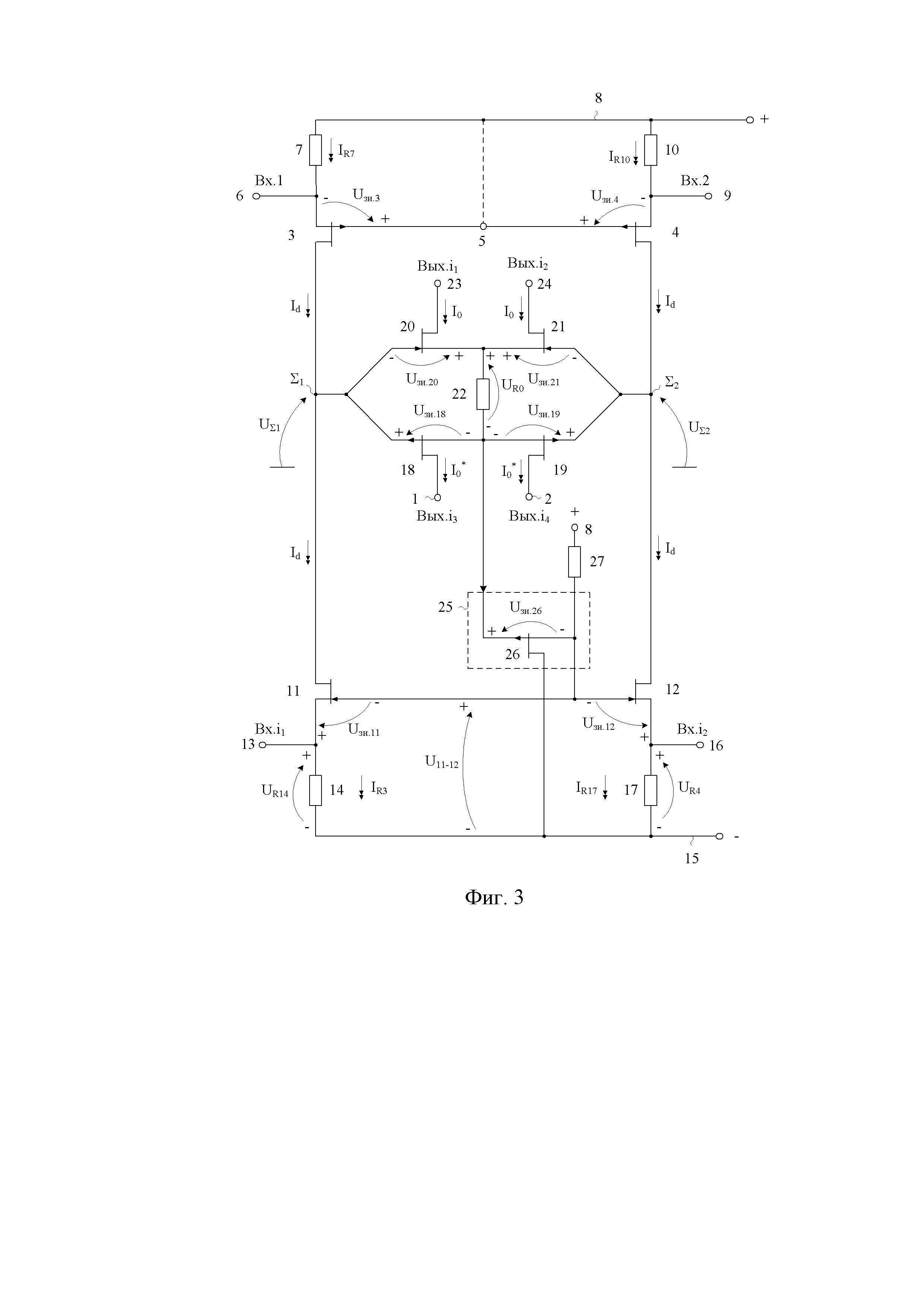

На чертеже фиг. 3 приведена схема заявляемого промежуточного каскада в соответствии с п. 3 и п. 4 формулы изобретения.

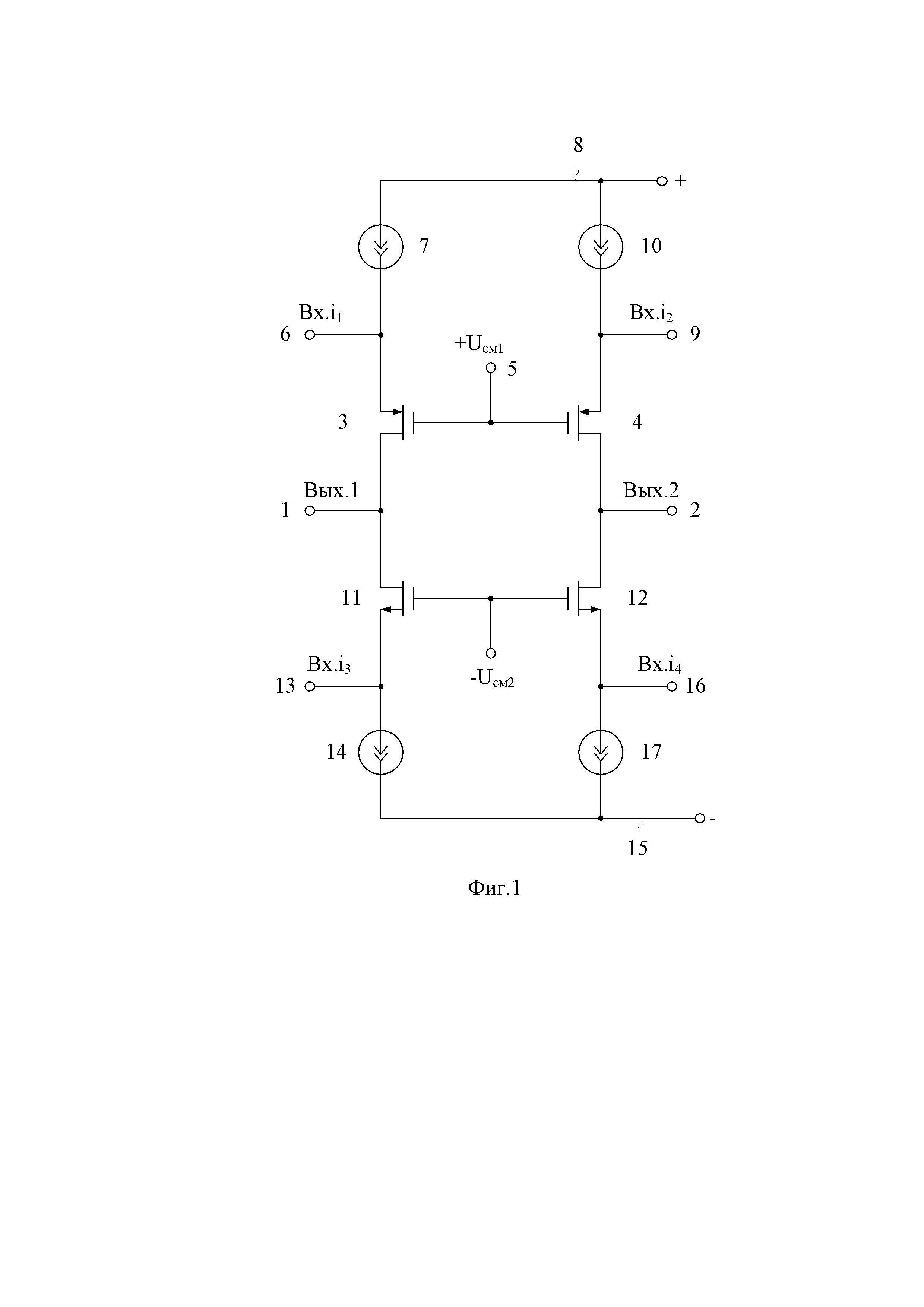

На чертеже фиг. 4 показана возможная схема включения заявляемого промежуточного каскада фиг. 2 в ОУ с парафазным выходом и дифференциальным входом.

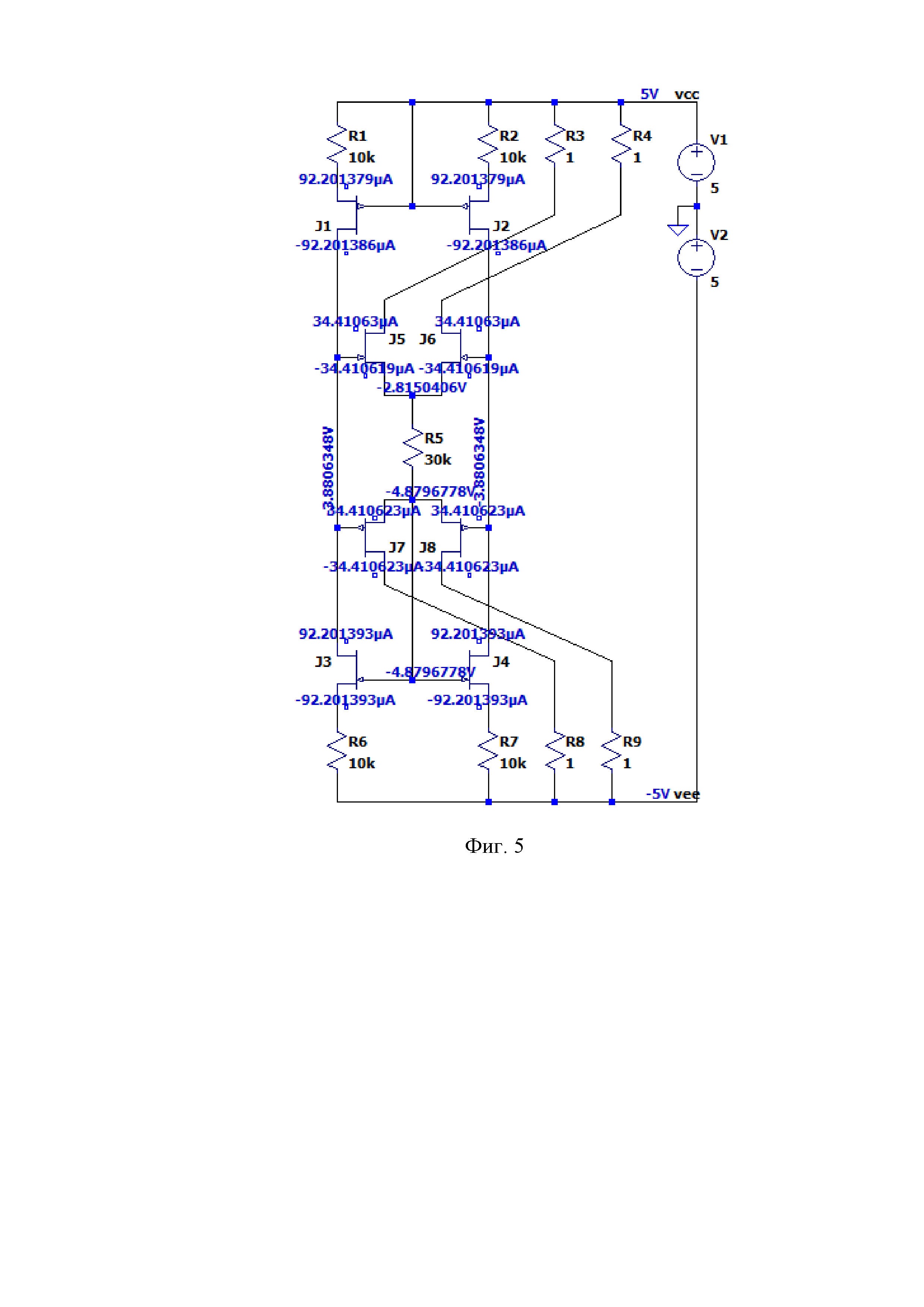

На чертеже фиг. 5 приведен статический режим заявляемого промежуточного каскада фиг. 2 в среде LTSpice при t=-1970C на моделях CJFET транзисторов АО «Интеграл» (г. Минск).

Промежуточный каскад операционного усилителя с парафазным выходом на комплементарных полевых транзисторах с управляющим p-n переходом фиг. 2 содержит первый 1 и второй 2 токовые выходы устройства, первый 3 и второй 4 входные полевые транзисторы, затворы которых объединены и подключены к источнику напряжения смещения 5, причем исток первого 3 входного полевого транзистора соединен с первым 6 токовым входом устройства и через первый 7 согласующий двухполюсник соединен с первой 8 шиной источника питания, а исток второго 4 входного полевого транзистора соединен со вторым 9 токовым входом устройства и через второй 10 согласующий двухполюсник соединен с первой 8 шиной источника питания, третий 11 и четвертый 12 входные полевые транзисторы с объединенными затворами, сток третьего 11 входного полевого транзистора соединен со стоком первого 3 входного полевого транзистора, сток четвертого 12 входного полевого транзистора соединен со стоком второго 4 входного полевого транзистора, причем исток третьего 11 входного полевого транзистора соединен с третьим 13 токовым входом устройства и через третий 14 согласующий двухполюсник соединен со второй 15 шиной источника питания, а исток четвертого 12 входного полевого транзистора соединен с четвертым 16 токовым входом устройства и через четвертый 17 согласующий двухполюсник соединен со второй 15 шиной источника питания. В схему введены первый 18 и второй 19 дополнительные полевые транзисторы с объединенными истоками, общий узел которых связан с объединенными затворами третьего 11 и четвертого 12 входных полевых транзисторов, сток первого 18 дополнительного полевого транзистора соединен с первым 1 токовым выходом устройства, сток второго 19 дополнительного полевого транзистора подключен ко второму 2 токовому выходу устройства, затвор первого 18 дополнительного полевого транзистора соединен со стоком первого 3 входного полевого транзистора, затвор второго 19 дополнительного полевого транзистора подключен к стоку второго 4 входного полевого транзистора, объединенные истоки первого18 и второго 19 дополнительных полевых транзисторов связаны с объединенными истоками третьего 20 и четвертого 21 дополнительных полевых транзисторов через дополнительный двухполюсник 22, причем затвор третьего 20 дополнительного полевого транзистора соединен со стоком первого 3 входного полевого транзистора, затвор четвертого 21 дополнительного полевого транзистора соединен со стоком второго 4 входного полевого транзистора, сток третьего 20 дополнительного полевого транзистора подключен к первому 23 дополнительному токовому выходу устройства, а сток четвертого 21 дополнительного полевого транзистора связан со вторым 24 дополнительным токовым выходом устройства.

На чертеже фиг. 2, в соответствии с п. 2 формулы изобретения, в качестве источника напряжения смещения 5 используется первая 8 шина источника питания.

На чертеже фиг. 3, в соответствии с п. 3 формулы изобретения, общий узел объединенных истоков первого 18 и второго 19 дополнительных полевых транзисторов связан с объединенными затворами третьего 11 и четвертого 12 входных полевых транзисторов через цепь согласования потенциалов 25, имеющую вход и выход. Такое схемотехническое решение позволяет установить заданные статические напряжения UΣ1, UΣ2 и обеспечить в конкретных схемах включения ПК симметричный режим работы по напряжениям затвор-сток транзисторов 18 и 19, а также транзисторов 20 и 21. В результате токовые выходы 1, 2 и 23, 24 могут быть подключены к следующему каскаду усиления в конкретной схеме ОУ, например, так, как показано на чертеже фиг. 4. Данное свойство ПК позволяет решить проблему построения многокаскадных операционных усилителей без применения токовых зеркал, которые являются слабым звеном современной аналоговой микросхемотехники (статические погрешности, инерционность и т.д.).

Кроме этого, на чертеже фиг. 3, в соответствии с п. 4 формулы изобретения, цепь согласования потенциалов 25 выполнена на вспомогательном транзисторе 26, затвор которого является входом цепи согласования потенциалов 25, сток подключен ко второй 15 шине источника питания, а исток является выходом цепи согласования потенциалов 25 и через токостабилизирующий двухполюсник 27 соединен с первой 8 шиной источника питания.

Схема ОУ на чертеже фиг. 4 показывает оригинальную архитектуру CJFET ОУ с заявляемым ПК фиг. 2 и CJFET входным дифференциальным каскадом 28, имеющим входы 29 и 30 и реализованном на полевых транзисторах 31, 32, 33, 34. В данной схеме токовые выходы 1 и 2, а также токовые выходы 23 и 24 подключены к выходной подсхеме ОУ, содержащей резисторы 35, 36, транзисторы 37, 38, 39, 40, буферные усилители 41 и 42, имеющие потенциальные выходы 43, 44, а также резисторы 45, 46. По существу, схема фиг. 4 показывает идею построения многокаскадных CJFET ОУ, содержащих заявляемый ПК и только «перегнутые» каскоды. При этом схема ОУ фиг. 4 имеет потенциальные парафазные выходы 43, 44, которые могут (в случае необходимости) использоваться для выделения выходного синфазного сигнала ОУ и организации отрицательной обратной связи по синфазному сигналу, стабилизирующей статический режим выходной подсхемы. В качестве буферных усилителей 41 и 42 могут также применяться CJFET БУ, например, по патенту РФ 2684489.

Схема фиг. 5, которая была получена в результате компьютерного моделирования в среде LTSpice при t=-197°C на моделях CJFET транзисторов АО «Интеграл» (г. Минск), показывает, что в заявляемой схеме обеспечивается стабильный статический режим при токах истока всех полевых транзисторов, не превышающих 100 мкА.

Рассмотрим работу схемы ПК фиг. 2.

Особенность схемы фиг. 2 состоит в том, что в ней предусмотрены четыре токовых входа 6, 9, 13 и 16 и четыре токовых выхода 1, 2, 23, 24, что является одним из условий построения многокаскадных CJFET ОУ с большим усилением, в котором каждый из последующих каскадов имеет такую же структуру, как и ПК фиг. 2. При этом выходы 23, 24 согласованы с первой 8 шиной источника питания, а выходы 1 и 2 – со второй 15 шиной источника питания.

Учитывая, что входные токи ПК фиг. 2 могут изменяться от нулевого значения до уровня статического тока в первом 7, втором 10, третьем 14 и четвертом 17 согласующих двухполюсниках, рассмотрим статический режим данной схемы при Iвх.i=0. В этом случае токи и напряжения на элементах схемы будут определяться следующими уравнениями

где  - статическое напряжение затвор-исток i-го полевого транзистора при заданном токе стока;

- статическое напряжение затвор-исток i-го полевого транзистора при заданном токе стока;

Id.i – статический ток истока (стока) первого 3, второго 4, третьего 11 и четвертого 12 входных полевых транзисторов.

Статический режим по току истока третьего 20 и четвертого 21 дополнительных полевых транзисторов, а также первого 18 и второго 19 дополнительных полевых транзисторов устанавливается дополнительным двухполюсником 22, который также определяет крутизну преобразования в токи выходов 1, 2 и 23, 24 напряжения между затворами третьего 20 и четвертого 21 дополнительных полевых транзисторов, а также первого 18 и второго 19 дополнительных полевых транзисторов.

Токовые выходы 23 и 24 ПК могут использоваться для обеспечения заданного Ку в последующих каскадах ОУ. Пример такого решения показан на чертеже фиг. 4.

Для обеспечения идентичных статических напряжений затвор-сток транзисторов 20 и 21 первой дифференциальной пары и напряжений затвор-сток транзисторов 18, 19 второй дифференциальной пары в схеме фиг. 3 введена цепь согласования потенциалов 25. За счет рационального выбора тока через токостабилизирующий двухполюсник 27 можно изменять статическое напряжение в узлах Σ1, Σ2 относительно общей шины. В частном случае в схеме фиг. 3 можно обеспечить UΣ1=UΣ2≈0, что дает полную симметрию статических напряжений на выходах 23, 24 и выходах 1, 2 относительно общей шины.

Результаты компьютерного моделирования в диапазоне криогенных температур статического режима заявляемого ПК фиг. 2, представленные на чертеже фиг. 5, показывают, что полевые транзисторы рассматриваемой схемы работают при токах стока, не превышающих 100 мкА. Это является важным условием обеспечения малого энергопотребления АМ при низких температурах.

Таким образом, заявляемый промежуточный каскад обладает существенными преимуществами в сравнении с прототипом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 8.604.878, fig.4, 2008 г.

2. Патент US 6.628.168, fig.2, 2003г.

3. Патент US 6.265.941, fig.3, 2001г.

4. Патент US 6.956.434, fig.1, 2005г.

5. Патент US 6.628.162, fig. 2, 2003 г.

6. Патент US 6.956.434, fig. 1, 2005 г.

7. Патент US 6.265.941, fig. 3, 2001 г.

8. Патент US 7.030.696, fig.1, fig. 4, 2006 г.

9. Патентная заявка US 2004/0080369, fig. 1, 2004 г.

10. Патентная заявка US 2004/0090268, 2004 г.

11. Патент US 5.805.021, fig. 1, 1998 г.

12. Патент US 6.690.894, fig. 1, 2004 г.

13. Дворников О.В., Прокопенко Н.Н., Пахомов И.В., Игнашин А.А., and Бугакова А.В.. "Прецизионный радиационно-стойкий BiJFet операционный усилитель для низкотемпературных аналоговых интерфейсов датчиков" Глобальная ядерная безопасность, № 1 (22), 2017, С. 36-45.

14. O. V. Dvornikov, N. N. Prokopenko, A. V. Bugakova, V. A. Tchekhovski and I. V. Maliy, "Cryogenic Operational Amplifier on Complementary JFETs," 2018 IEEE East-West Design & Test Symposium (EWDTS), Kazan, 2018, pp. 1-5. doi: 10.1109/EWDTS.2018.8524640

15. K. O. Petrosyants, M. R. Ismail-zade, L. M. Sambursky, O. V. Dvornikov, B. G. Lvov and I. A. Kharitonov, "Automation of parameter extraction procedure for Si JFET SPICE model in the −200…+110°C temperature range," 2018 Moscow Workshop on Electronic and Networking Technologies (MWENT), Moscow, 2018, pp. 1-5. doi: 10.1109/MWENT.2018.8337212M.

16. O. V. Dvornikov, N. N. Prokopenko, I. V. Pakhomov and A. V. Bugakova, "The analog array chip AC-1.3 for the tasks of tool engineering in conditions of cryogenic temperature, neutron flux and cumulative radiation dose effects," 2016 IEEE East-West Design & Test Symposium (EWDTS), Yerevan, 2016, pp. 1-4. doi: 10.1109/EWDTS.2016.7807724

17. Citterio, S. Rescia and V. Radeka, "Radiation effects at cryogenic temperatures in Si-JFET, GaAs MESFET, and MOSFET devices," in IEEE Transactions on Nuclear Science, vol. 42, no. 6, pp. 2266-2270, Dec. 1995. doi: 10.1109/23.489425

18. M. Citterio, S. Rescia and V. Radeka, "A study of low noise JFETs exposed to large doses of gamma-rays and neutrons," IEEE Conference on Nuclear Science Symposium and Medical Imaging, Orlando, FL, USA, 1992, pp. 794-796 vol.2. doi: 10.1109/NSSMIC.1992.301428

19. W. Buttler, B. J. Hosticka, G. Lutz and P. F. Manfredi, "A JFET-CMOS radiation-tolerant charge-sensitive preamplifier," in IEEE Journal of Solid-State Circuits, vol. 25, no. 4, pp. 1022-1024, Aug. 1990. doi: 10.1109/4.58299

20. A. Pullia, F. Zocca, S. Riboldi, D. Budjas, A. D'Andragora and C. Cattadori, "Cryogenic Performance of a Low-Noise JFET-CMOS Preamplifier for HPGe Detectors," in IEEE Transactions on Nuclear Science, vol. 57, no. 2, pp. 737-742, April 2010. doi: 10.1109/TNS.2009.2038697

21. T. S. Jung, H. Guckel, J. Seefeldt, G. Ott and Y. C. Ahn, "A fully integrated, monolithic, cryogenic charge sensitive preamplifier using N-channel JFETs and polysilicon resistors," in IEEE Transactions on Nuclear Science, vol. 41, no. 4, pp. 1240-1245, Aug. 1994. doi: 10.1109/23.322892

22. A. D'Andragora et al., "Spectroscopic performances of the GERDA cryogenic Charge Sensitive Amplifier based on JFET-CMOS ASIC, coupled to germanium detectors," 2009 IEEE Nuclear Science Symposium Conference Record (NSS/MIC), Orlando, FL, 2009, pp. 396-400. doi: 10.1109/NSSMIC.2009.5401678

23. D. M. Long, "Transient radiation response of jfets and misfets at cryogenic temperatures," in IEEE Transactions on Nuclear Science, vol. 21, no. 6, pp. 119-123, Dec. 1974. doi: 10.1109/TNS.1974.6498915