Результат интеллектуальной деятельности: УСТРОЙСТВО ФОРМИРОВАНИЯ ИЗОБРАЖЕНИЯ, СИСТЕМА ФОРМИРОВАНИЯ ИЗОБРАЖЕНИЯ И ДВИЖУЩИЙСЯ ОБЪЕКТ

Вид РИД

Изобретение

Уровень техники

Область техники, к которой относится изобретение

[0001] Настоящее изобретение относится к устройству формирования изображения, системе формирования изображения и движущемуся объекту.

Описание предшествующего уровня техники

[0002] Выложенная японская патентная заявка 2012-151847 обсуждает устройство, которое включает в себя множество пикселов, блок аналого-цифрового (AD) преобразования и блок выбора строки, предусмотренный на первой интегральной схеме, и схемы возбуждения для управления временем накопления заряда для множества пикселов, предусмотренные на второй интегральной схеме. В частности, согласно выложенной японской патентной заявке № 2012-151847, множество пикселов 18 предусматривается на первой интегральной схеме 12, а элементы 28 формирования сигналов активации предусматриваются на второй интегральной схеме 14. Схемы 28 формирования сигналов активации электрически соединяются с электрическими соединениями 38. Электрические соединения 38 вводятся на затворы транзисторов 56 переноса или транзисторов 46 сброса, предусмотренных в пикселах 18. Схемы 28 формирования сигналов активации могут, таким образом, управлять временем накопления заряда для зарядов, генерируемых посредством фотоэлектрического преобразования. Выложенная японская патентная заявка № 2012-151847 также обсуждает, что схемы 28 формирования сигналов активации предусматриваются для соответствующих групп пикселов (блоков пикселов), каждая из которых включает в себя множество пикселов.

[0003] Выложенная японская патентная заявка № 2012-151847 обсуждает только предоставление групп пикселов с помощью соответствующих схем формирования сигналов активации на второй интегральной схеме.

[0004] Настоящее изобретение направлено на предоставление устройства формирования изображения улучшенной производительности по сравнению с устройством из выложенной японской патентной заявки № 2012-151847.

Сущность изобретения

[0005] Согласно аспекту настоящего изобретения, устройство формирования изображения включает в себя первую интегральную схему, на которой множество первых блоков размещаются в виде матрицы, и вторую интегральную схему, на которой множество вторых блоков размещается в виде матрицы, первая и вторая интегральные схемы укладываются друг на друга, при этом каждый из множества первых блоков включает в себя множество пикселов, размещенных в виде матрицы, при этом каждый из множества вторых блоков включает в себя схему выбора, сконфигурированную, чтобы выбирать момент возбуждения множества пикселов, принадлежащих к каждому из множества первых блоков, и при этом каждый из множества вторых блоков включает в себя блок обработки сигнала, сконфигурированный, чтобы обрабатывать сигналы, выводимые от пикселов.

[0006] Согласно другому аспекту настоящего изобретения, устройство формирования изображения включает в себя первую интегральную схему, на которой множество первых блоков размещаются в виде матрицы, и вторую интегральную схему, на которой множество вторых блоков размещается в виде матрицы, первая и вторая интегральные схемы укладываются друг на друга, при этом каждый из множества первых блоков включает в себя множество пикселов, размещенных в виде матрицы, при этом каждый из множества вторых блоков включает в себя схему выбора, сконфигурированную, чтобы выбирать момент возбуждения множества пикселов, принадлежащих к каждому из множества первых блоков, и при этом каждый из множества вторых блоков включает в себя генератор тактовых сигналов, сконфигурированный, чтобы выводить сигнал для управления схемой сканирования первого блока и схемой сканирования второго блока.

[0007] Дополнительные признаки настоящего изобретения станут очевидны из последующего описания примерных вариантов осуществления со ссылкой на приложенные чертежи.

Краткое описание чертежей

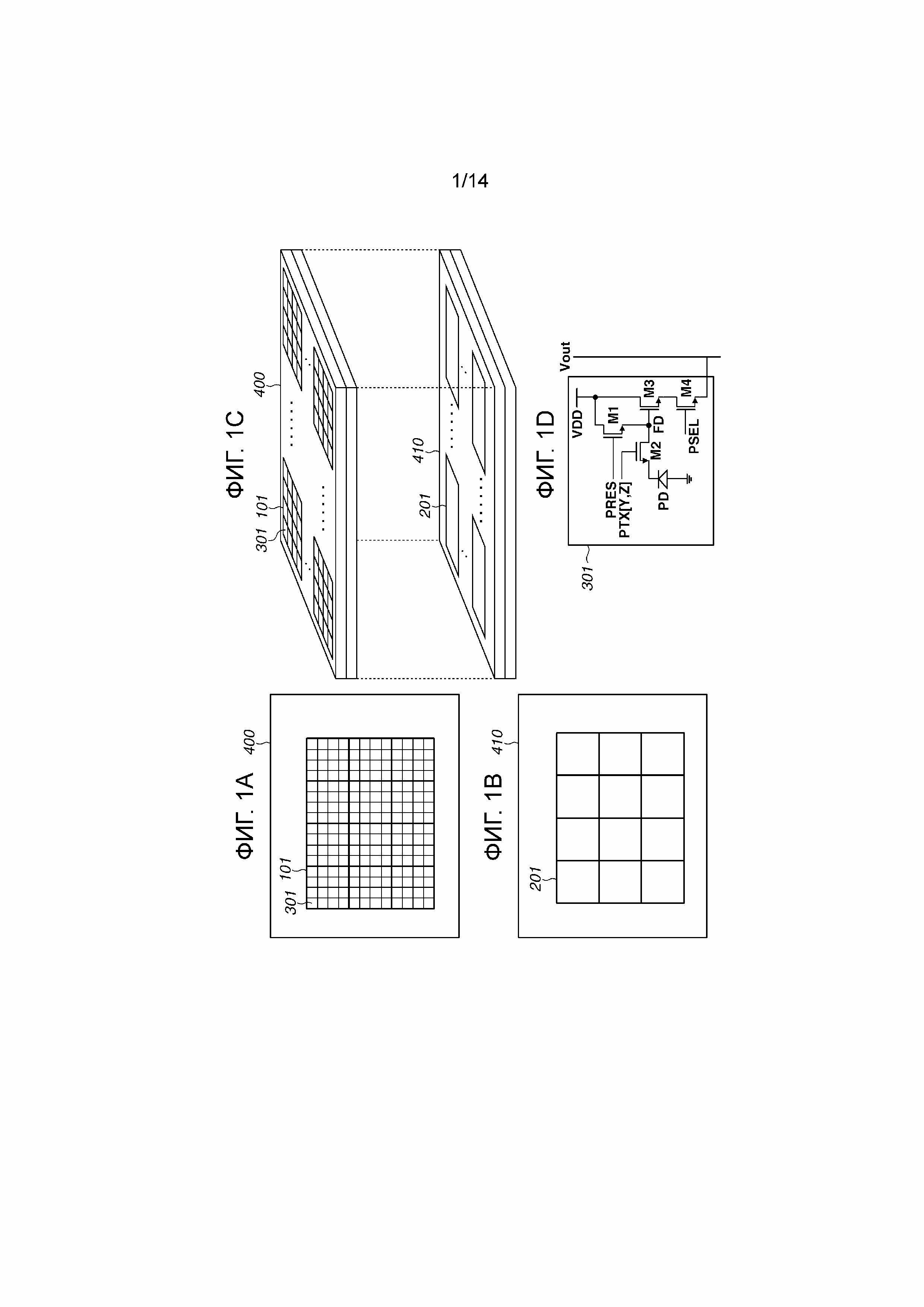

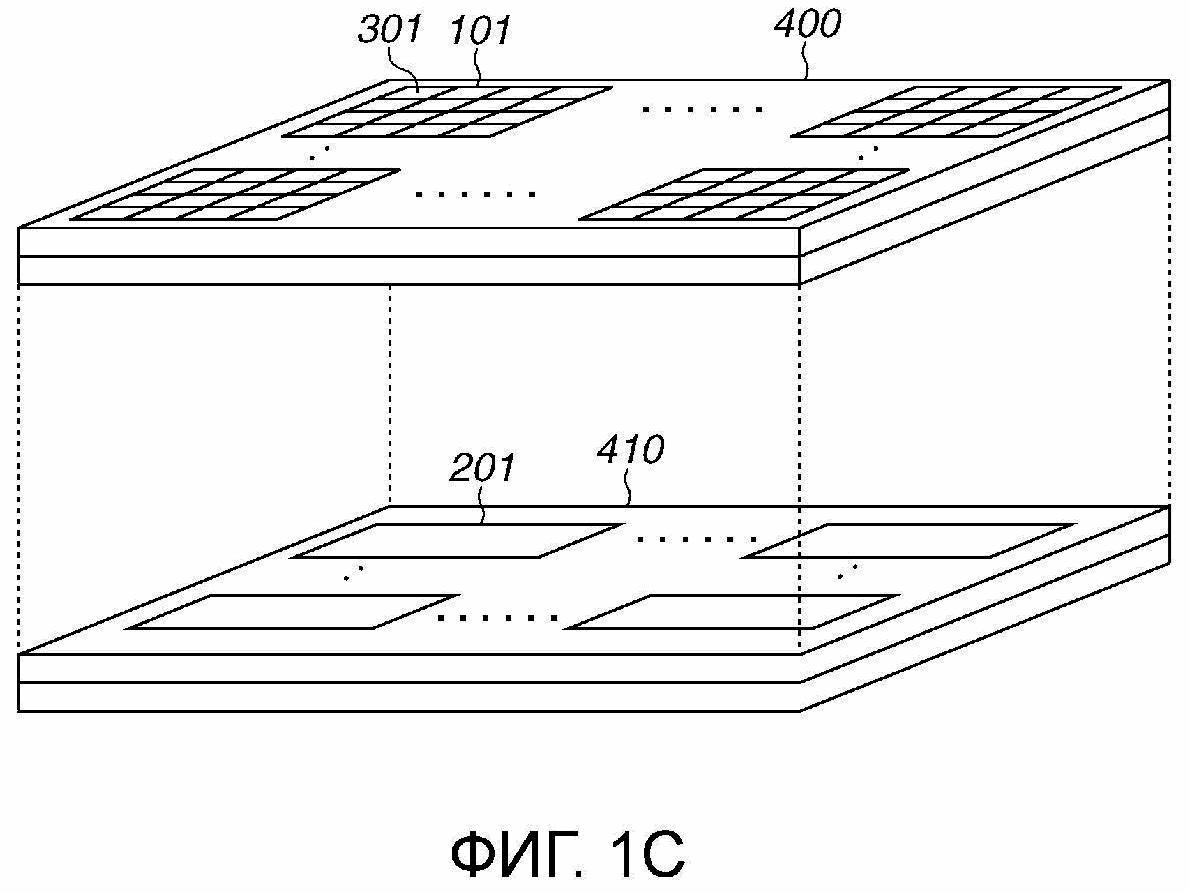

[0008] Фиг. 1A, 1B, 1C и 1D - это схемы, относящиеся к первому примерному варианту осуществления.

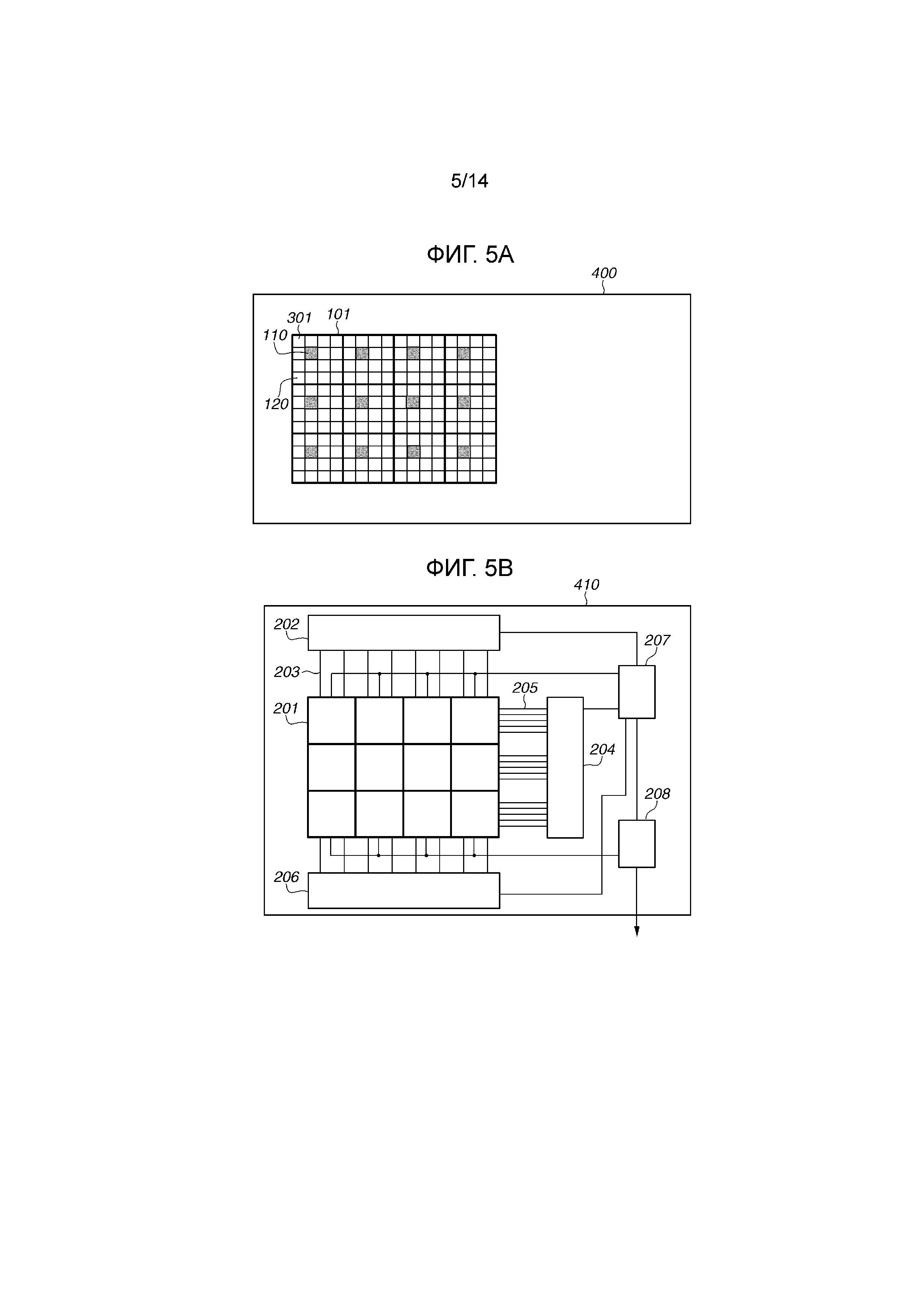

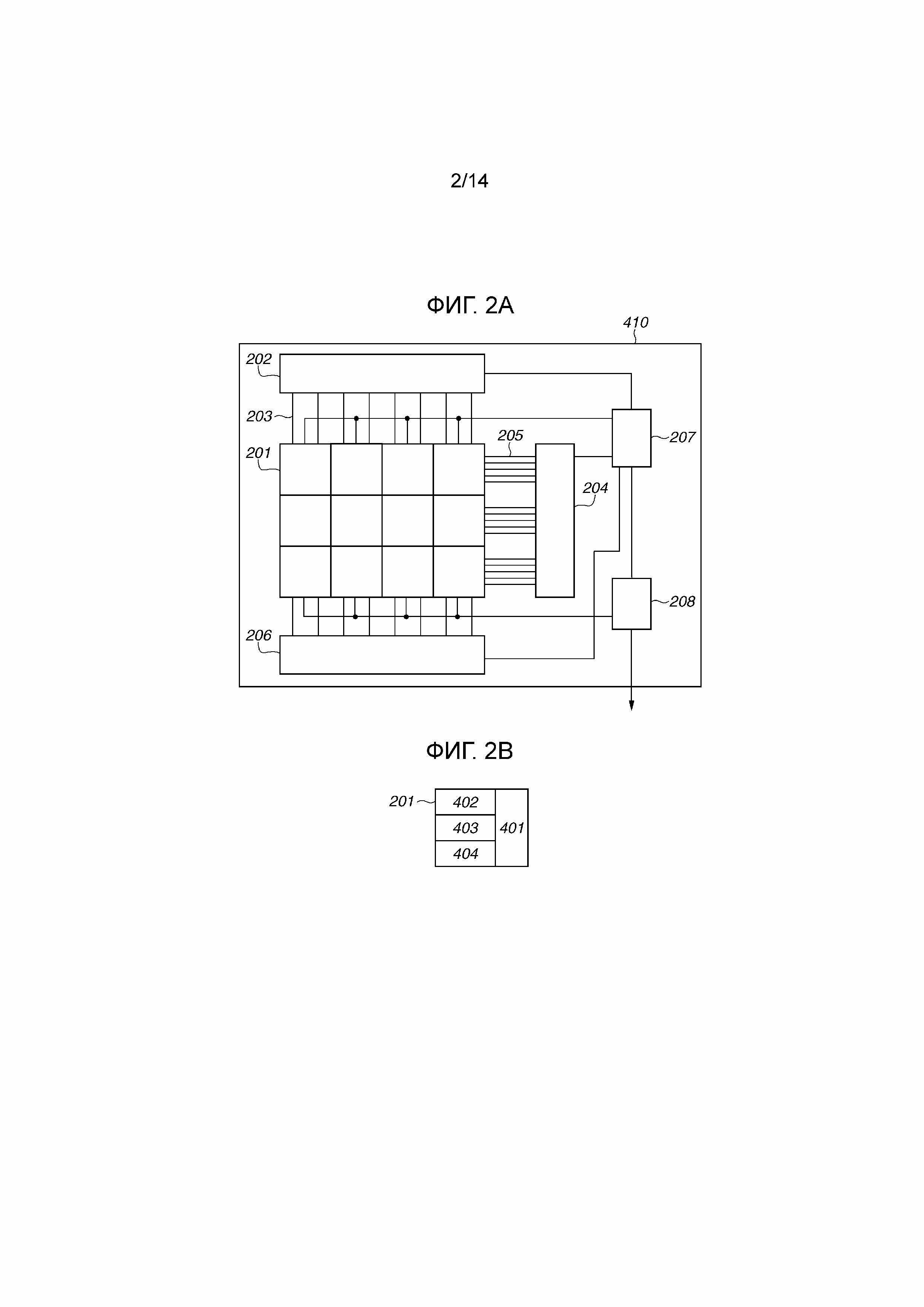

[0009] Фиг. 2A и 2B - это схемы, относящиеся к первому примерному варианту осуществления.

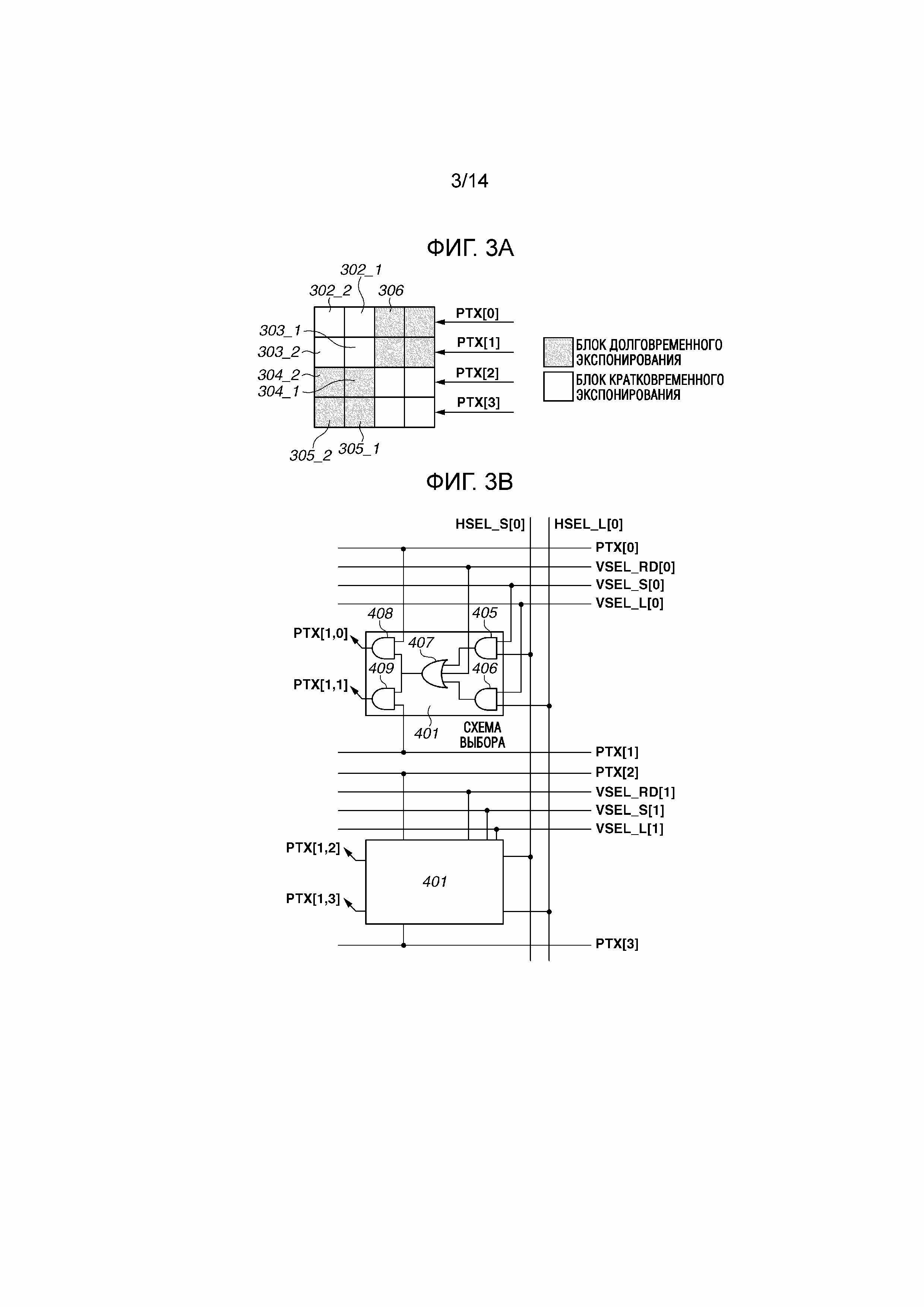

[0010] Фиг. 3A и 3B - это схемы, относящиеся к первому примерному варианту осуществления.

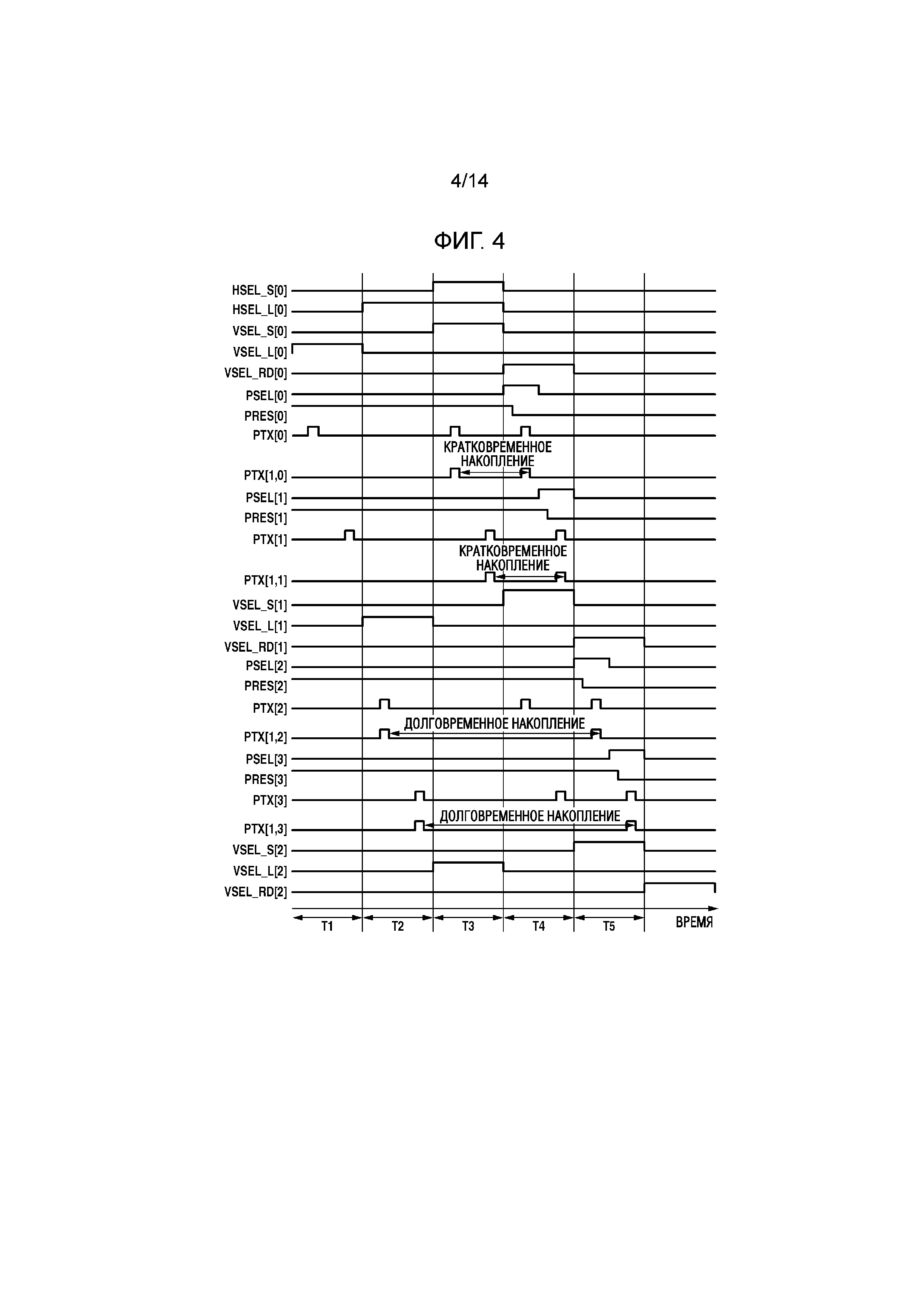

[0011] Фиг. 4 - это схема, относящаяся к первому примерному варианту осуществления.

[0012] Фиг. 5A и 5B - это схемы, относящиеся к первому примерному варианту осуществления.

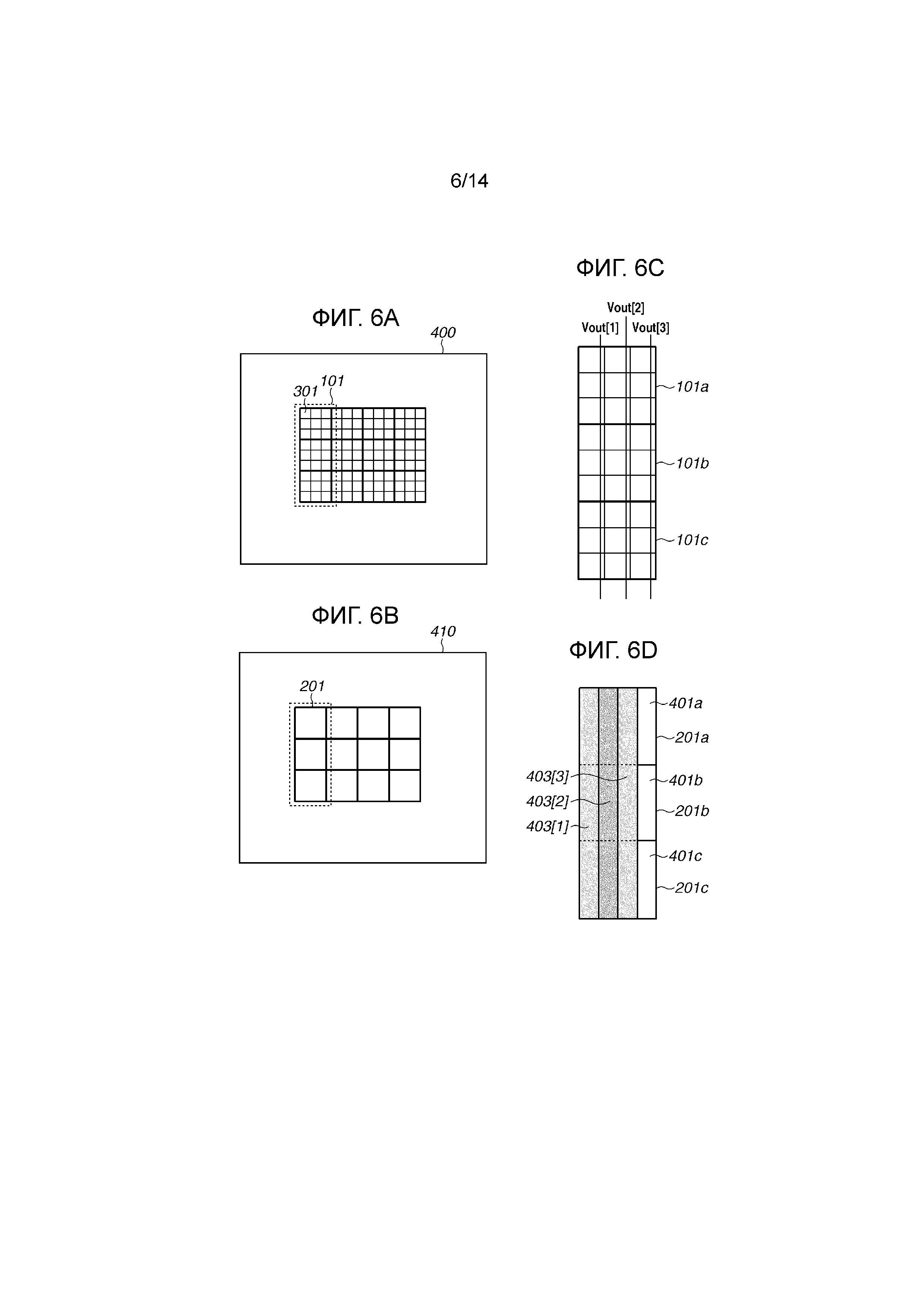

[0013] Фиг. 6A, 6B, 6C и 6D - это схемы, относящиеся к первому примерному варианту осуществления.

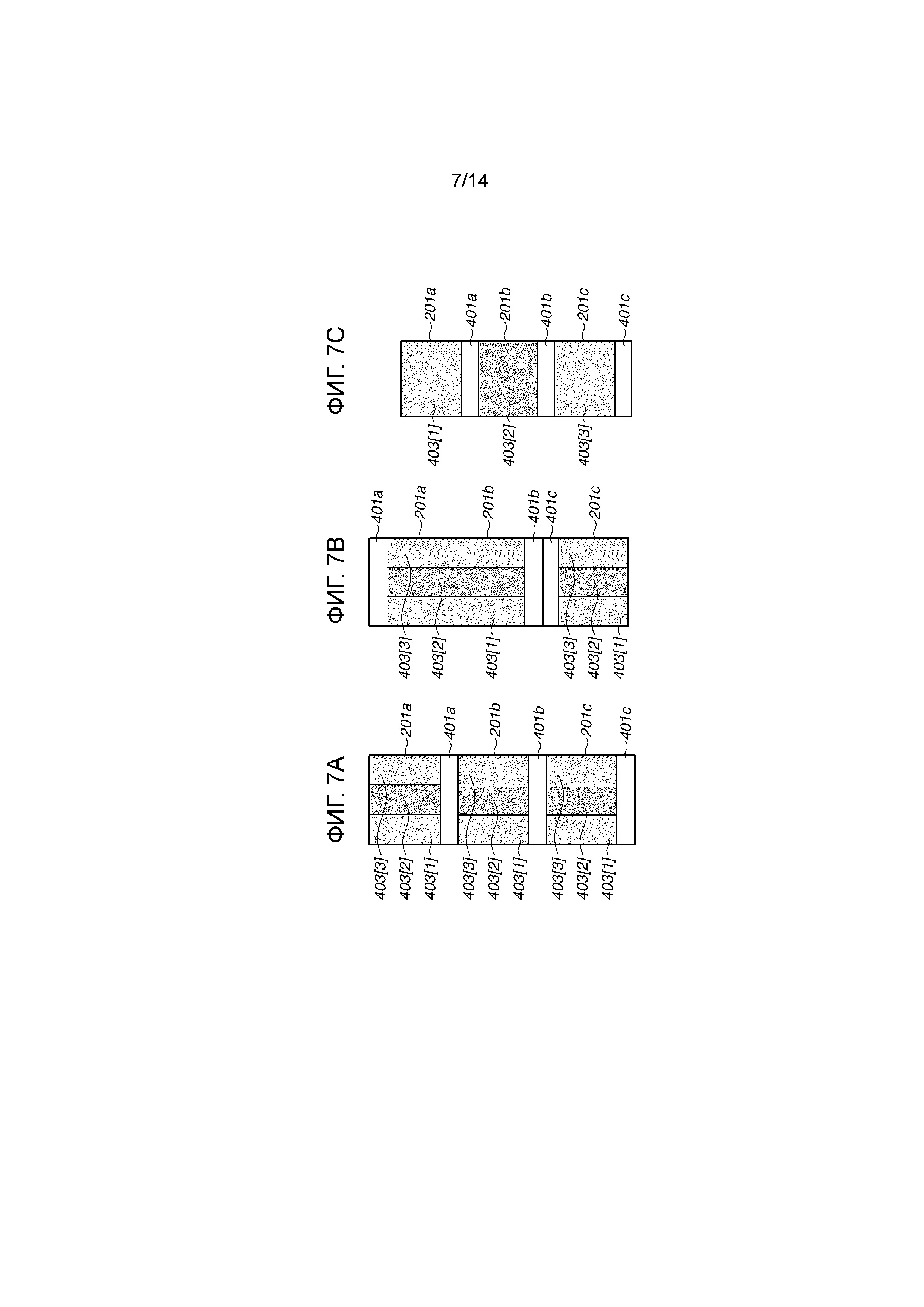

[0014] Фиг. 7A, 7B и 7C - это схемы, относящиеся к первому примерному варианту осуществления.

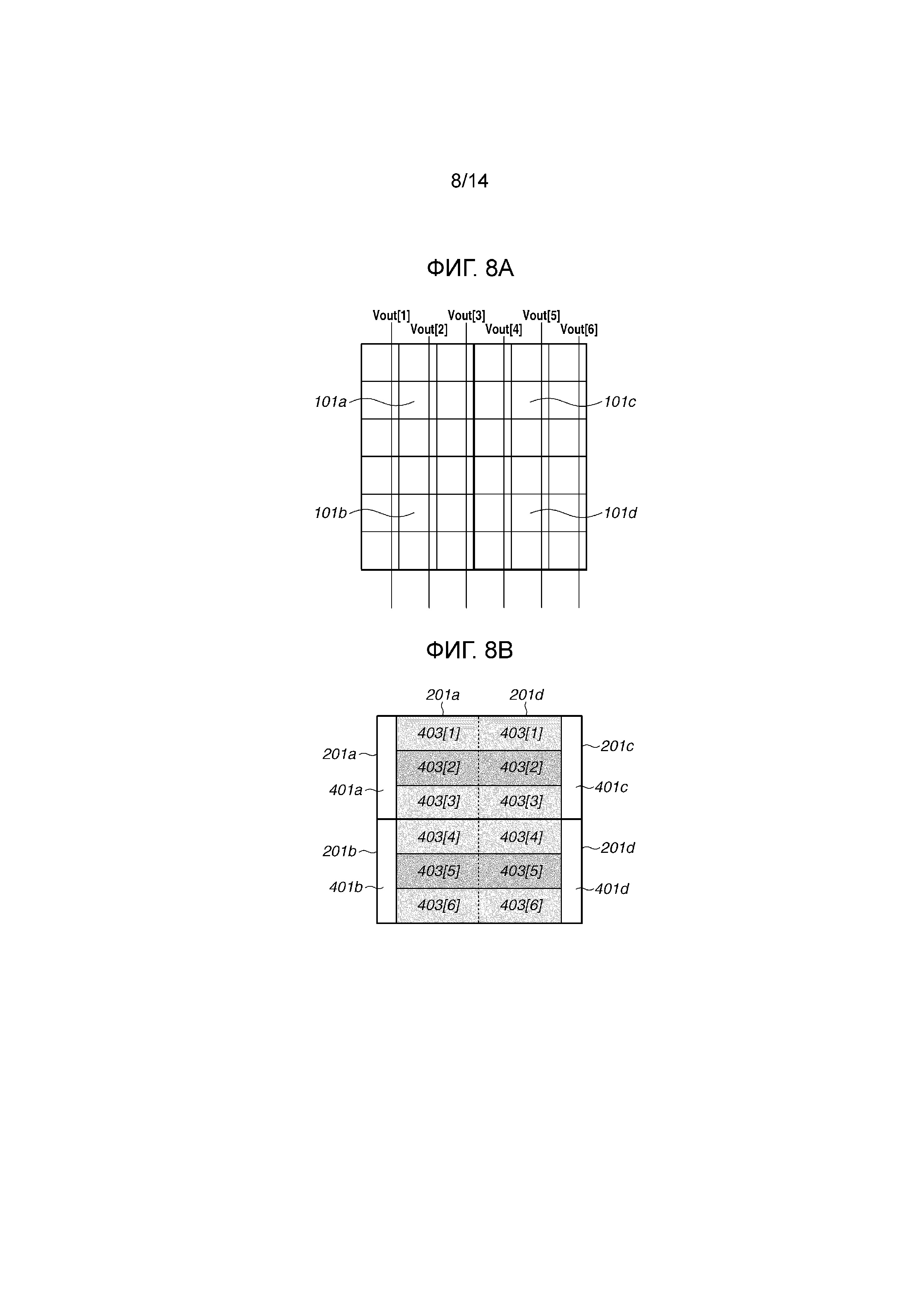

[0015] Фиг. 8A и 8B - это схемы, относящиеся к первому примерному варианту осуществления.

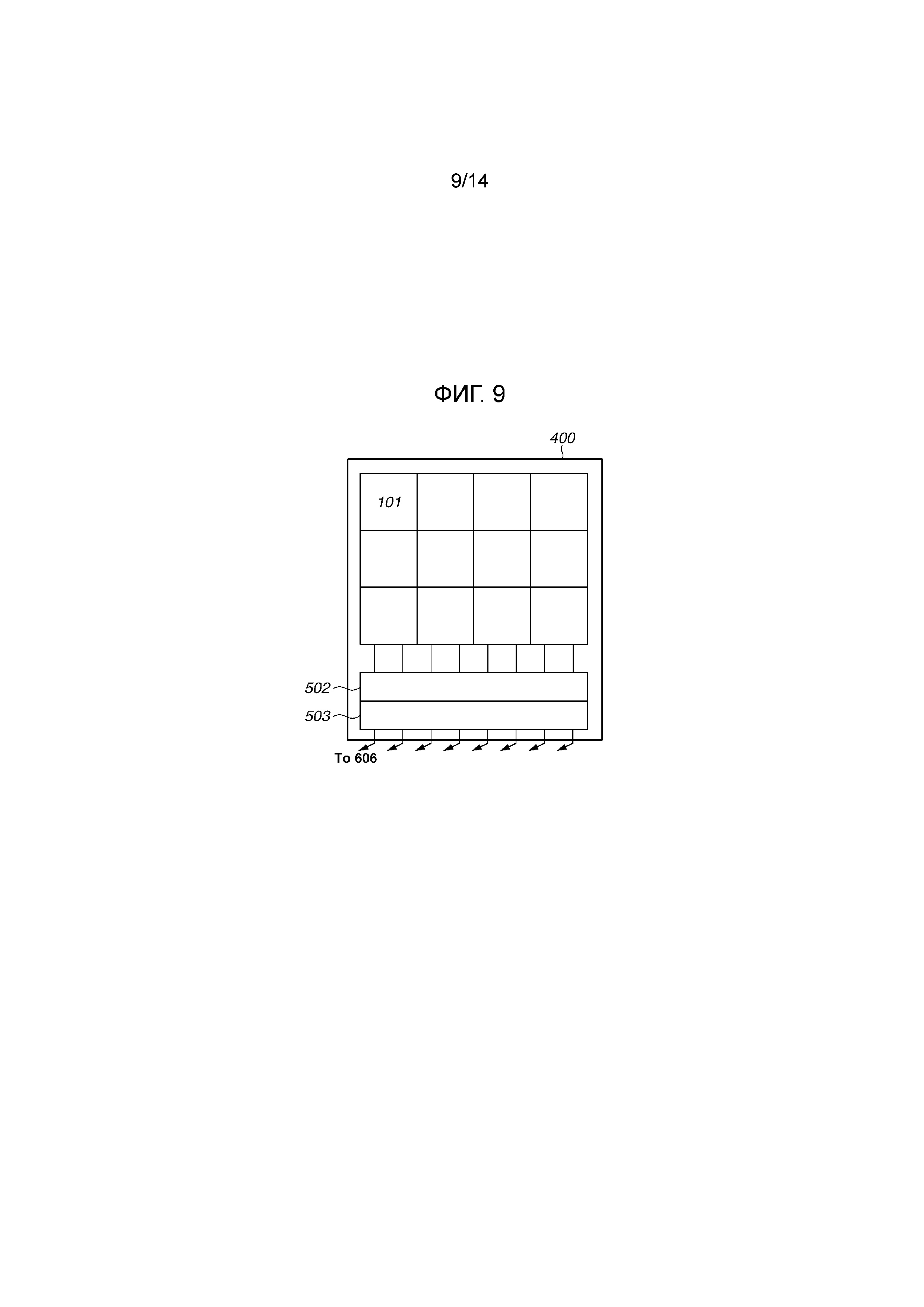

[0016] Фиг. 9 - это схема, относящаяся ко второму примерному варианту осуществления.

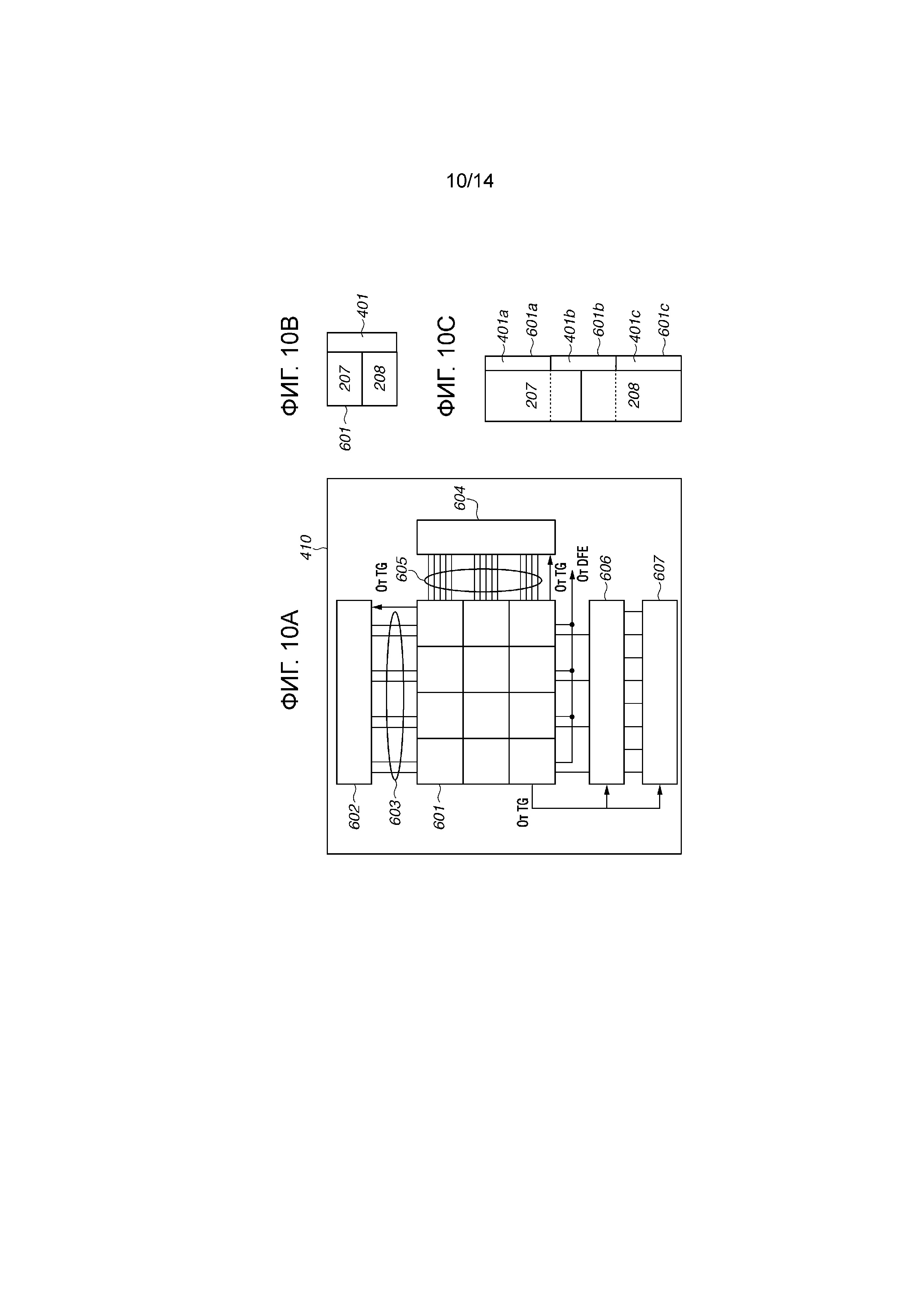

[0017] Фиг. 10A, 10B и 10C - это схемы, относящиеся ко второму примерному варианту осуществления.

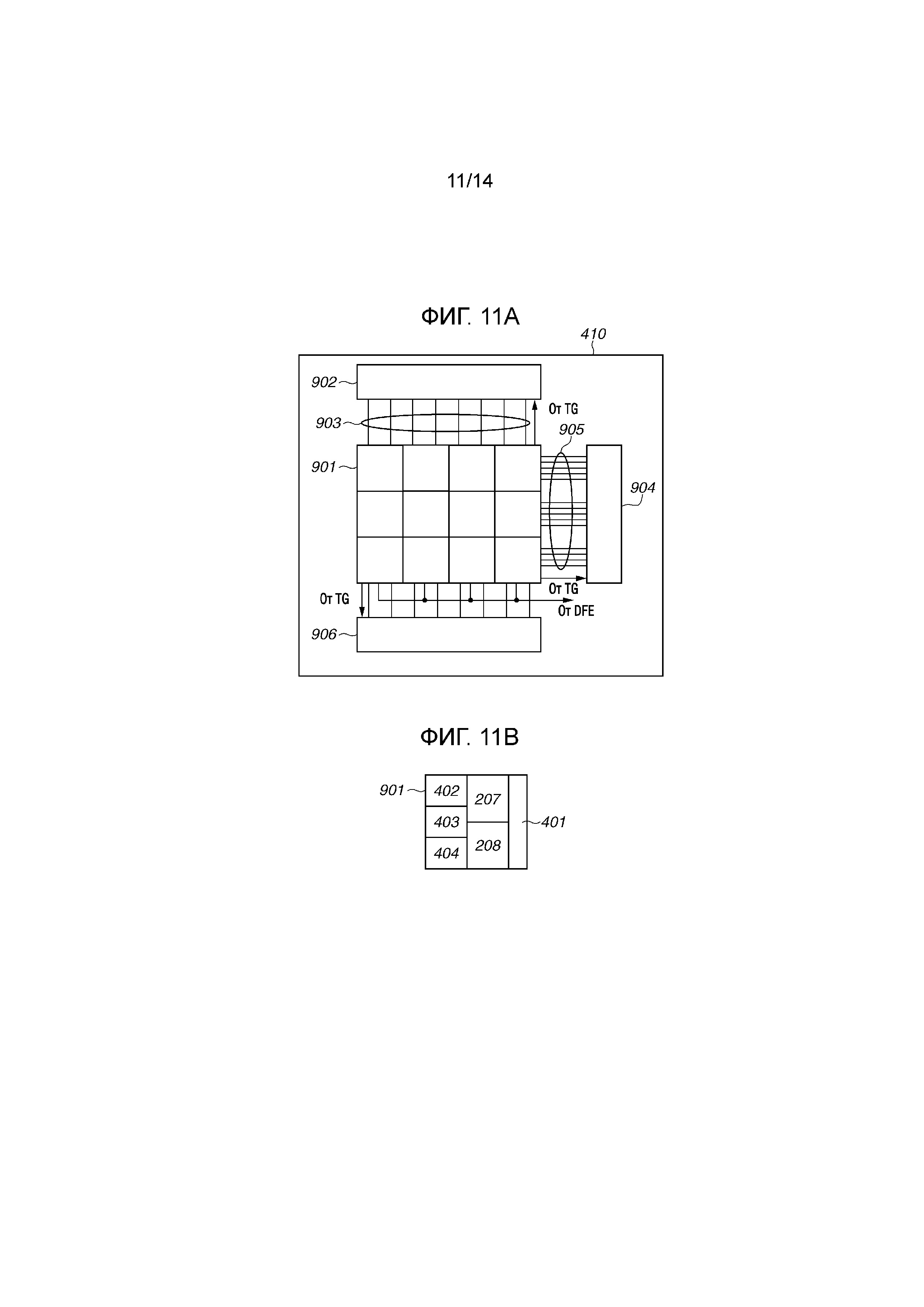

[0018] Фиг. 11A и 11B - это схемы, относящиеся к третьему примерному варианту осуществления.

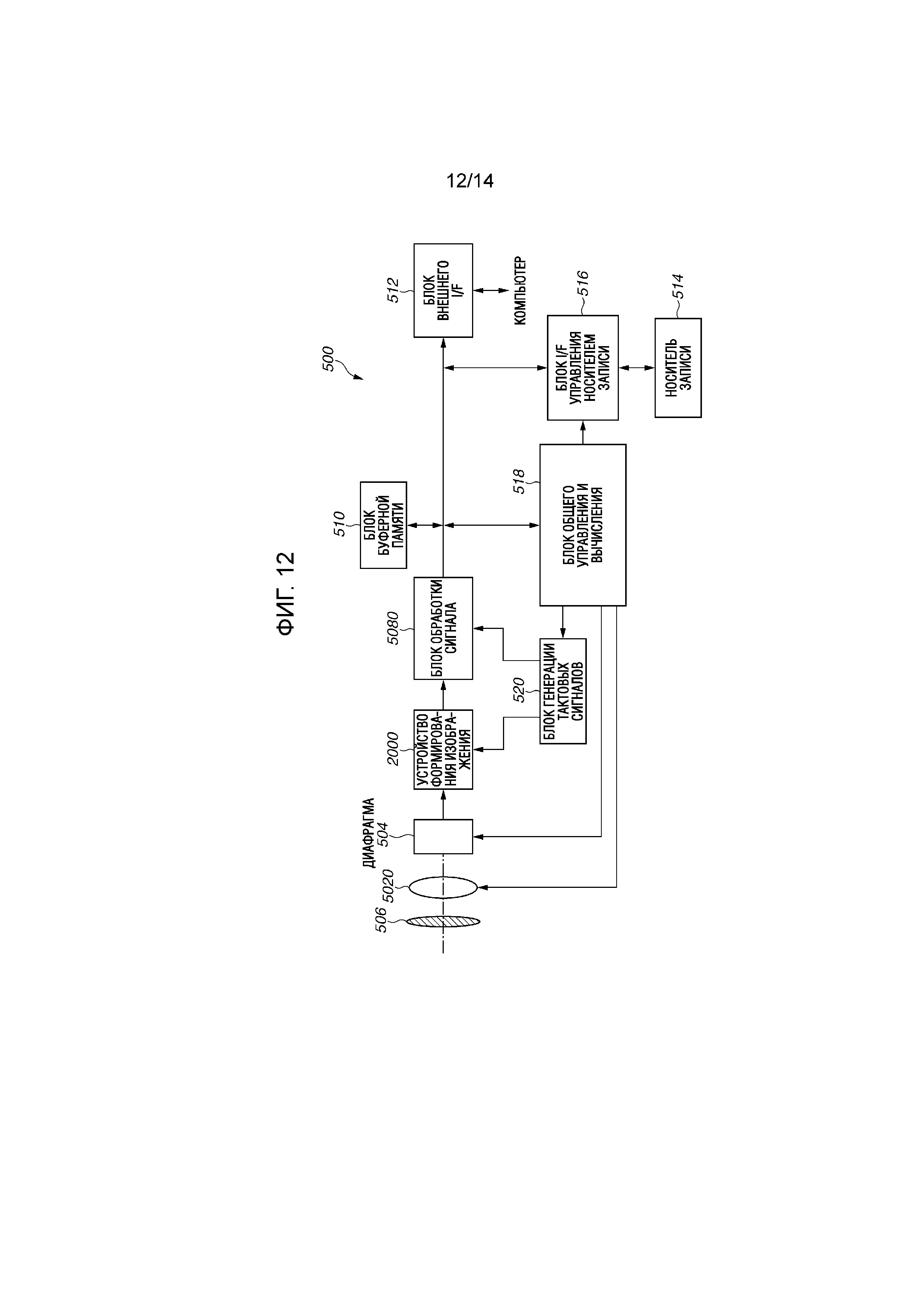

[0019] Фиг. 12 - это схема, относящаяся к четвертому примерному варианту осуществления.

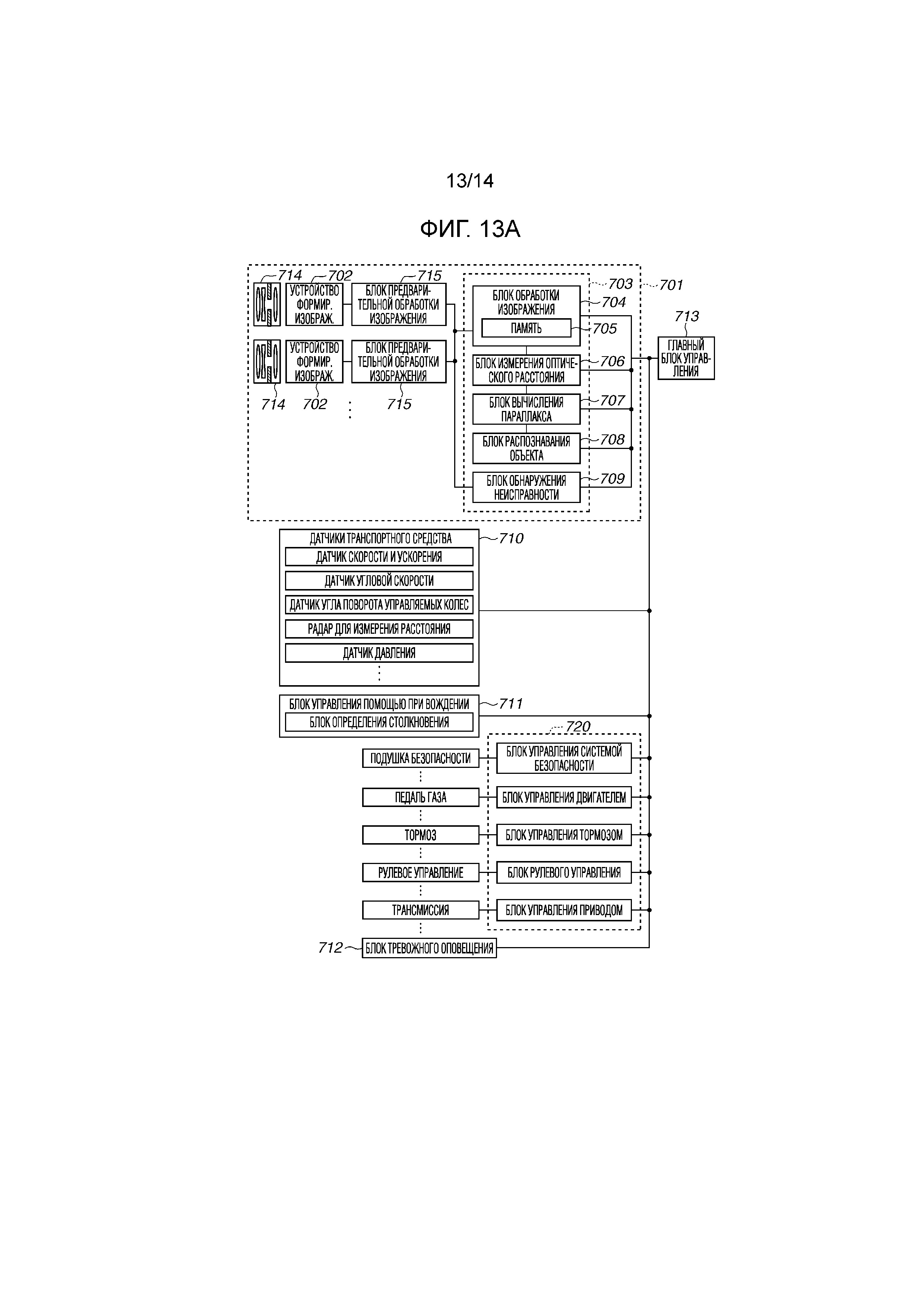

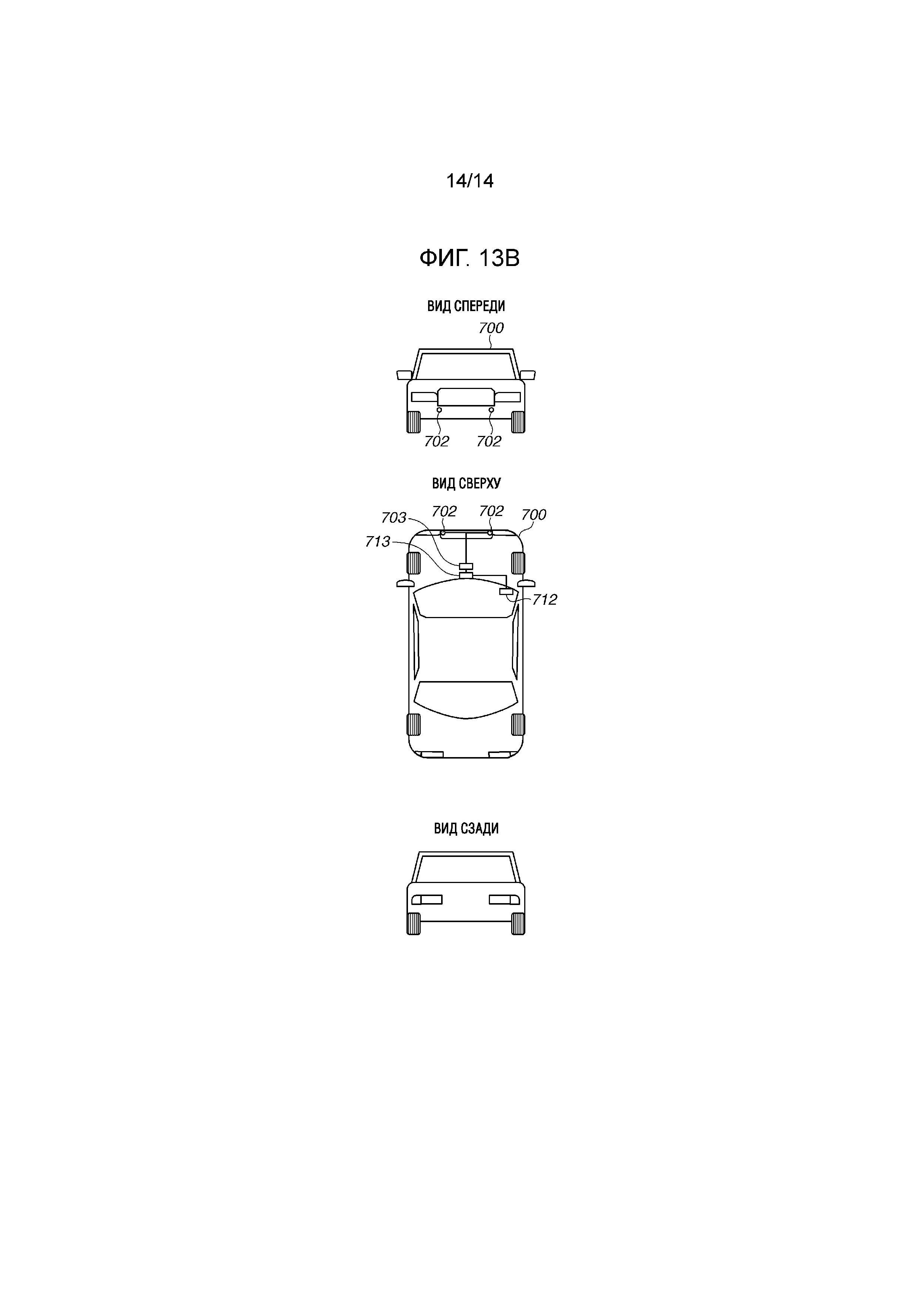

[0020] Фиг. 13A и 13B - это схемы, относящиеся к пятому примерному варианту осуществления.

Описание вариантов осуществления

(Базовая конфигурация)

[0021] Фиг. 1A-1C являются схематичными чертежами, иллюстрирующими устройство формирования изображения согласно первому примерному варианту осуществления. Первая интегральная схема 400 включает в себя множество блоков 101 пикселов (первых блоков), каждый из которых включает в себя множество пикселов 301. На фиг. 1A, например, каждый блок 101 пикселов включает в себя множество пикселов 301, размещенных в виде матрицы из четырех строк и четырех столбцов. Например, первая интегральная схема 400 включает в себя множество блоков 101 пикселов, размещенных в виде матрицы из трех строк и четырех столбцов.

[0022] Вторая интегральная схема 410 включает в себя множество блоков 201 (вторых блоков), каждый из которых включает в себя схему выбора. Первая интегральная схема 400 и вторая интегральная схема 410 укладываются друг на друга, чтобы формировать многослойное устройство формирования изображения.

[0023] Блоки 101 пикселов и блоки 201 соответствуют функционально на основе один к одному. Вторые блоки 201, каждый, включают в себя, по меньшей мере, схему выбора. Другими словами, предварительно определенный блок 201 предусматривается для предварительно определенного блока 101 пикселов, и схема выбора, включенная в предварительно определенный блок 201, выбирает момент накопления заряда (момент возбуждения) для предварительно определенного блока 101 пикселов. Детали схемы выбора будут описаны ниже. Блоки 101 пикселов и блоки 201 не только соответствуют функционально на основе один к одному, но также и с точки зрения физического позиционного соотношения. Более конкретно, в виде сверху, предварительно определенный блок 101 пикселов и предварительно определенный блок 201, которые соответствуют друг другу, предусматриваются в перекрывающихся позициях. Это сокращает пути электрического соединения между блоками 101 пикселов и блоками 201 для ускорения и предотвращения перекрестных помех.

[0024] Фиг. 1D иллюстрирует пример конфигурации пиксела 301. Пиксел 301 включает в себя блок PD фотоэлектрического преобразования, транзистор M2 переноса и транзистор M1 сброса. Транзистор M2 переноса переносит заряд блока PD фотоэлектрического преобразования в плавающий диффузионный фрагмент FD (далее в данном документе FD-фрагмент). Транзистор M1 сброса сбрасывает FD-фрагмент. FD-фрагмент соединяется с затвором транзистора M3 усиления. Напряжение VDD источника питания подается к транзистору M3 усиления и транзистору M1 сброса. Транзистор M4 выбора соединяется с истоком транзистора M3 усиления. Транзистор M4 выбора соединяется с вертикальной выходной линией Vout. Сигналы PRES, PTX и PSEL возбуждения вводятся на затворы транзистора M1 сброса, транзистора M2 переноса и транзистора M4 выбора, соответственно.

[0025] Сигнал пиксела от блока PD фотоэлектрического преобразования считывается с пиксела 301 через вертикальную выходную линию Vout. Вертикальная выходная линия Vout соединяется со слоем разводки второй интегральной схемы 410 через множество слоев разводки первой интегральной схемы 400. Например, первая интегральная схема 400 и вторая интегральная схема 410 электрически соединяются посредством физического контакта между фрагментами разводки, раскрытыми на самом верхнем слое разводки первой интегральной схемы 400, и фрагментами разводки, раскрытыми на самом верхнем слое разводки второй интегральной схемы 410.

(Конкретная конфигурация второй интегральной схемы)

[0026] Фиг. 2A иллюстрирует вторую интегральную схему 410 согласно настоящему примерному варианту осуществления. Генератор (TG) 207 тактовых сигналов предоставляет тактовый сигнал для схемы 204 сканирования вертикального блока (схемы сканирования первого блока), которая имеет функцию схемы вертикального сканирования (первой схемы сканирования). TG 207 также предоставляет тактовый сигнал для схемы 202 сканирования горизонтального блока (схемы сканирования второго блока) и схемы 206 горизонтального сканирования (второй схемы сканирования).

[0027] Сигналы вводятся во множество блоков 201 из схемы 204 сканирования вертикального блока через группу 205 сигнальных линий управления вертикальным блоком. Схема 204 сканирования вертикального блока выводит сигналы для управления моментом возбуждения множества пикселов 301, размещенных в направлении строки. Сигналы также вводятся во множество блоков 201 из схемы 202 сканирования горизонтального блока через группу 203 сигнальных линий управления горизонтальным блоком. Схема 202 сканирования горизонтального блока выводит сигналы для управления моментом возбуждения множества пикселов 301, размещенных в направлении столбца. Сигналы дополнительно вводятся во множество блоков 201 из схемы 206 горизонтального сканирования.

[0028] Фиг. 2B иллюстрирует конфигурацию блока 201. Блок 201 включает в себя схему 401 выбора, которая выбирает, предоставлять ли сигнал сигнальной линии PTX[X] пикселу 301, на основе сигналов от схемы 204 сканирования вертикального блока и схемы 202 сканирования горизонтального блока. Если сигнал сигнальной линии PTX[X] выбирается, чтобы быть предоставленным пикселу 301, сигнал, который должен быть предоставлен в сигнальную линию PTX[Y, Z], формируется. Сигнал, предоставленный в сигнальную линию PTX [Y, Z], подается к затвору транзистора M2 переноса, иллюстрированного на фиг. 1D, в результате чего, момент накопления заряда блока 101 пикселов управляется. Если уровень сигнала сигнальной линии PTX[Y, Z] изменяется с низкого уровня на высокий уровень, транзистор M2 переноса включается, и заряд переносится с блока PD фотоэлектрического преобразования на FD-фрагмент. Если уровень сигнала сигнальной линии PTX[Y, Z] изменяется с высокого уровня на низкий уровень, транзистор M2 переноса выключается, и перенос заряда с блока PD фотоэлектрического преобразования на FD-фрагмент заканчивается. Соответствующая величина экспонирования каждого блока 101 пикселов может быть задана посредством схемы 401 выбора. Например, если количество падающего света изменяется от одного блока 101 пикселов к другому, период накопления заряда блока 101 пикселов, в котором количество света в единицу времени является большим, может быть задан коротким. Период накопления заряда блока 101 пикселов, в котором количество света в единицу времени является небольшим, может быть задан более длительным, чем период накопления заряда блока 101 пикселов, в котором количество света является большим. Это может преимущественно расширять динамический диапазон устройства формирования изображения.

[0029] Блок 201 включает в себя блок 402 усиления, который электрически соединяется с сигнальной линией Vout, иллюстрированной на фиг. 1D. Блок 402 усиления предусматривается, если транзистор M3 усиления, предусмотренный в пикселе 301, сам по себе является недостаточным для усиления сигнала. Блок 402 усиления может быть опущен, если транзистор M3 усиления сам по себе является достаточным для усиления.

[0030] Блок 201 также включает в себя блок 403 AD-преобразования, который электрически соединяется с блоком 402 усиления. Блок 403 AD-преобразования преобразует аналоговый сигнал от пиксела 301 в цифровой сигнал. Например, блок 403 AD-преобразования включает в себя компаратор, генератор линейно изменяющегося напряжения и счетчик. Линейно изменяющийся сигнал (сигнал сравнения) от генератора линейно изменяющегося напряжения вводится в один узел ввода компаратора. Сигнальная линия Vout соединяется с другим узлом ввода компаратора. Компаратор сравнивает линейно изменяющийся сигнал (сигнал сравнения) и сигнал сигнальной линии Vout. Счетчик измеряет время до того момента, когда выходной сигнал компаратора изменяется или инвертируется, в соответствии с чем, получается цифровое значение сигнала. Вместо блока AD-преобразования линейно изменяющегося типа может быть использован блок AD-преобразования типа последовательного сравнения, использующий бинарные весовые конденсаторы. Поскольку блок 403 AD-преобразования имеет функцию преобразования аналогового сигнала в цифровой сигнал, блок 403 AD-преобразования может называться блоком обработки сигнала.

[0031] Блок 201 дополнительно включает в себя память 404, которая хранит цифровой сигнал из блока 403 AD-преобразования. Цифровой сигнал, сохраненный в памяти 404, управляется посредством схемы 206 горизонтального сканирования и выводится в блок 208 обработки сигнала. Блок 201 также включает в себя схему восприятия (не иллюстрирована), которая усиливает цифровой сигнал, сохраненный в памяти 404.

[0032] Цифровой сигнал, выведенный из памяти 404, обрабатывает посредством блока 208 обработки сигнала. Блок 208 обработки сигнала выполняет, например, вычисление разницы между сигналом области оптического уровня черного и сигналом области эффективного пиксела и суммы сигналов пикселов. На основе результата обработки блок 208 обработки сигнала выводит управляющий сигнал в TG 207. Например, как будет описано ниже, блок 208 обработки сигнала выводит сигнал для управления временем накопления заряда (временем экспонирования) каждого блока 101 пикселов.

[0033] В настоящем примерном варианте осуществления каждая из схем 401 выбора, соответствующих различному блоку из блоков 101 пикселов, предусматривается в другом блоке из блоков 201, соответствующих соответствующим блокам 101 пикселов. Блоки 101 пикселов и схемы 401 выбора соответствуют функционально в том смысле, что сигналы, предоставляемые затворам транзисторов M2 переноса, выбираются посредством схем 401 выбора и, тем самым, время накопления заряда множества пикселов, размещенных в блоках 101 пикселов, управляется. Поскольку блоки 101 пикселов и блоки 201 также соответствуют с точки зрения физического позиционного соотношения, как описано выше, схемы 401 выбора, предусмотренные в блоках 201 и блоках 101 пикселов, также соответствуют с точки зрения физического позиционного соотношения. Например, первые блоки 101 пикселов и схемы 401 выбора перекрываются в виде сверху.

[0034] Блоки 201, соответствующие соответствующим блокам 101 пикселов, каждый, включают в себя схемы, которые могут быть предусмотрены в первой интегральной схеме 400 или второй интегральной схеме 410, отличной от схемы 401 выбора. Примеры схем, отличных от схемы 401 выбора, включают в себя блок 402 усиления, блок 403 AD-преобразования и память 404. Размещение схем, отличных от схемы 401 выбора, в блоке 201 может уменьшать пространство первой интегральной схемы 400, отличной от блоков 101 пикселов, для экономии пространства. Число блоков 101 пикселов, предусмотренных в первой интегральной схеме 400, может, таким образом, быть увеличено.

[0035] Выложенная японская патентная заявка № 2012-151847 обсуждает "блок 24 AD-преобразования", который размещается в первой интегральной схеме. Напротив, согласно настоящему примерному варианту осуществления, блоки 403 AD-преобразования, соответствующие "блоку 24 AD-преобразования", обсужденному в выложенной японской патентной заявке № 2012-151847, предусматриваются в блоках 201 второй интегральной схемы 410. Больше пикселов 301 могут, таким образом, быть размещены в первой интегральной схеме 400. Поскольку блоки 403 AD-преобразования предусматриваются в соответствующих блоках 201, AD-преобразование может быть выполнено посредством параллельной обработки для ускорения. Выложенная японская патентная заявка № 2012-151847 обсуждает "блок 22 выбора строки", который также размещается в первой интегральной схеме. Напротив, согласно настоящему примерному варианту осуществления, схема 204 вертикального сканирования блока, соответствующая "блоку 22 выбора строки", обсужденному в выложенной японской патентной заявке № 2012-151847, предусматривается во второй интегральной схеме 410. Даже больше пикселов могут, таким образом, быть размещены в первой интегральной схеме 400. Предоставление множества функциональных блоков в первой интегральной схеме 410 может сужать пространство для блоков 201 на второй интегральной схеме 410. В таком случае, множество вторых интегральных схем 410 может быть использовано.

(Время экспонирования, изменяющееся от одного блока пикселов к другому, и схемы выбора)

[0036] Фиг. 3A иллюстрирует множество блоков 101 пикселов, которые размещаются в двух строках и двух столбцах. Каждый блок 101 пикселов включает в себя две строки и два столбца пикселов. Блоки 101 пикселов, иллюстрированные в незаштрихованных блоках, являются блоками, которые выполняют кратковременное экспонирование. Блоки 101 пикселов, иллюстрированные в заштрихованных блоках, являются блоками, которые выполняют долговременное экспонирование.

[0037] В области формирования изображения первый блок пикселов и второй блок пикселов, размещенный в позиции, отличной от первого блока, могут отличаться по уровню (значению сигнала) сигнала пиксела. Например, если значение сигнала пиксела в первом блоке пикселов падает ниже уровня шума, достаточную градацию может не быть возможности получить в темном фрагменте. Если, в таком случае, время экспонирования первого и второго блоков пикселов единообразно устанавливается в длительное, высокие значения сигнала пиксела во втором блоке пикселов могут достигать уровня насыщения. В результате, второму блоку пикселов может не удаваться обеспечивать достаточные градации. Следовательно, как иллюстрировано на фиг. 3A, в настоящем примерном варианте осуществления, предоставляется множество блоков, которые выполняют долговременное экспонирование, и множество блоков, которые выполняют кратковременное экспонирование, чтобы добиваться широкого динамического диапазона.

[0038] Импульсные сигналы PTX[X] выбора строки предоставляются в схемы 401 выбора из схемы 204 сканирования вертикального блока на фиг. 2A через группу 205 сигнальных линий управления вертикальным блоком. Сигналы сигнальных линий PTX[X] выбираются посредством схем 401 выбора, и импульсные сигналы (импульсные сигналы выбора блока пикселов) PTX[Y, Z] выбора пикселов предоставляются на затворы транзисторов M2 переноса согласно моменту выбора. Импульсные сигналы PTX[Y, Z] выбора пикселов могут называться сигналами возбуждения пикселов (сигналами возбуждения блока пикселов).

[0039] Как иллюстрировано на фиг. 3A, сигнальные линии PTX[0]-PTX[3] соответствуют пикселам в первой-четвертой строках. Фиг. 3A иллюстрируют две строки и да столбца, т.е., всего четыре блока, каждый включает в себя две строки и два столбца, т.е., четыре пиксела. Сигнальные линии PTX[0] и PTX[1] соответствуют двум блокам пикселов, а сигнальные линии PTX[2] и PTX[3] соответствуют другим двум блокам пикселов. На фиг. 3A пикселы 302_1 и 302_2 предназначаются для кратковременного экспонирования. Пиксел 306 предназначается для долговременного экспонирования. Если работа транзисторов M2 переноса для пикселов 302_1, 302_2 и 306 управляется с помощью только сигнальной линии PTX[0], только какое-либо одно из кратковременного и долговременного экспонирований может быть выполнено. Затем, в настоящем примерном варианте осуществления, время экспонирования каждого пиксела управляется посредством формирования импульсных сигналов PTX[Y, Z] выбора пиксела из импульсных сигналов PTX[X] выбора пиксела с помощью группы 203 сигнальных линий управления горизонтальным блоком, группы 205 сигнальных линий управления вертикальным блоком и схем 401 выбора.

[0040] Фиг. 3B иллюстрирует пример конфигурации группы сигнальных линий для передачи управляющих сигналов и схем 401 выбора. Сигнальные линии VSEL передают сигналы управления вертикальным блоком. Сигнальные линии HSEL передают сигналы управления горизонтальным блоком. Сигнальные линии VSEL_S предназначаются для кратковременного экспонирования. Сигнальные линии VSEL_L предназначаются для долговременного экспонирования. Сигнальная линия HSEL_S предназначается для кратковременного экспонирования. Сигнальная линия HSEL_L предназначается для долговременного экспонирования. Сигнальные линии VSEL_RD предназначаются для считывания.

[0041] Каждая схема 401 выбора формирует импульсные сигналы PTX[Y, Z] выбора пиксела из импульсных сигналов PTX[X] выбора строки, если оба уровня сигналов, предоставленных в сигнальные линии HSEL_S и VSEL_S, являются высокими, или оба уровня сигналов, предоставленных на сигнальные линии HSEL_L и VSEL_L, являются высокими. Сформированные импульсные сигналы PTX[Y, Z] выбора пиксела вводятся в затворы транзисторов M2 переноса. Что касается других комбинаций, импульсные сигналы PTX[Y, Z] выбора пиксела не формируются из импульсных сигналов PTX[X] выбора строки, и сигнал не вводится на затворы транзисторов M2 переноса.

[0042] В частности, сигнал VSEL_S управления вертикальным блоком и сигнал HSEL_S управления горизонтальным блоком вводятся в логическую схему 405 И. Логическая схема 405 И конфигурируется, чтобы выводить сигнал, если оба сигнала VSEL_S и HSEL_S управления блоками имеют высокий уровень. Сигнал VSEL_L управления вертикальным блоком и сигнал HSEL_L управления горизонтальным блоком вводятся в логическую схему 406 И. Логическая схема 406 И конфигурируется, чтобы выводить сигнал, если оба сигнала VSEL_L и HSEL_L управления блоками имеют высокий уровень. Сигнал VSEL_RD управления вертикальным блоком и выходные сигналы логических схем 405 и 406 И вводятся в логическую схему 407 ИЛИ. Логическая схема 407 или конфигурируется, чтобы выводить сигнал, если введен какой-либо из сигналов. Импульсные сигналы PTX[X] выбора строки и выходной сигнал логической схемы 407 ИЛИ вводятся в логические схемы 408 и 409 И. Логические схемы 408 и 409 И формируют импульсные сигналы PTX[Y, Z] выбора пиксела, если соответствующие сигналы PTX[X] выбора строки и выходной сигнал логической схемы 407 ИЛИ, оба вводятся.

[0043] Сигнальная линия PTX[1, 0] на фиг. 3B передает сигнал, вводимый на затворы транзисторов M2 переноса для пикселов 302_1 и 302_2. Аналогично, сигнальная линия PTX[1, 1] соответствует пикселам 303_1 и 303_2. Сигнальная линия PTX[1, 2] соответствует пикселам 304_1 и 304_2. Сигнальная линия PTX[1, 3] соответствует пикселам 305_1 и 305_2.

(Временная диаграмма)

[0044] Фиг. 4 иллюстрирует временную диаграмму, относящуюся к пикселам 302_1-305_2.

(Период T1)

[0045] Период T1 является периодом, в котором блок 101 пикселов в первой строке и первом столбце начинает накопление заряда для долговременного экспонирования и не начинает накопление заряда для кратковременного экспонирования. В настоящем примерном варианте осуществления блок 101 пикселов, включающий в себя пикселы 302_1, 302_2, 303_1 и 303_2, не является блоком долговременного экспонирования и не начинает накопление заряда в периоде T1. Другими словами, схема 401 выбора должна быть сконфигурирована, чтобы не формировать сигнал на сигнальной линии PTX[1, 0] или PTX[1, 1], даже если сигнал вводится на сигнальную линию PTX[0]. Сигнальная линия VSEL_L[0] соединяется с множеством пикселов, размещенных в первой строке совместно. Первая строка включает в себя пиксел 306, который выполняет долговременное экспонирование. Уровень сигнала сигнальной линии VSEL_L[0], следовательно, должен поддерживаться на высоком уровне. Если сигнал HSEL_L[0] управления горизонтальным блоком здесь имел высокий уровень, импульсный сигнал PTX[1, 0] выбора пиксела будет сформирован из импульсного сигнала PTX[0] выбора строки, поскольку уровень сигнала сигнальной линии VSEL_L[0] является высоким. Сигнал затем будет введен на затворы транзисторов M2 переноса для пикселов 302_1 и 302_2. По такой причине, уровень сигнала сигнальной линии HSEL_L[0] задается на низком уровне. На фиг. 4 уровни сигналов сигнальных линий HSEL_S[0] и VSEL_S[1] задаются на низком уровне.

[0046] Посредством такого возбуждения импульсный сигнал PTX[1, 0] выбора пиксела не формируется из импульсного сигнала PTX[0] выбора строки, и импульсный сигал PTX[1, 1] выбора пиксела не формируется из импульсного сигнала PTX[1] выбора строки. Сигнал, таким образом, не вводится на затворы транзисторов M2 переноса пикселов 302_1, 302_2, 303_1 и 303_2.

(Период T2)

[0047] Период T2 является периодом, в котором блок 101 пикселов во второй строке и первом столбце начинает накопление заряда, если блок 101 пикселов является блоком для долговременного экспонирования, и не начинает накопление заряда, если блок 101 пикселов является блоком для кратковременного экспонирования. В настоящем примерном варианте осуществления пикселы 304_1, 304_2, 305_1 и 305_2 принадлежат блоку 101 пикселов для долговременного экспонирования. Накопление заряда, следовательно, начинается в периоде T2. Сигнал VSEL_L[1] управления вертикальным блоком и сигнал HSEL_L[0] управления горизонтальным блоком затем устанавливаются на высоком уровне. В результате, импульсный сигнал PTX[1, 2] выбора пиксела формируется из импульсного сигнала PTX[2] выбора строки. Импульсный сигнал PTX[1, 2] выбора пиксела предоставляется на затворы транзисторов M2 переноса для пикселов 304_1 и 304_2. Аналогично, импульсный сигнал PTX[1, 3] выбора пиксела формируется из импульсного сигнала PTX[3] выбора строки. Импульсный сигнал PTX[1, 3] выбора пиксела предоставляется на затворы транзисторов M2 переноса для пикселов 305_1 и 305_2. Долговременное накопление, таким образом, начинается для пикселов блока 101 пикселов второй строки.

(Период T3)

[0048] Период T3 является периодом, в котором блок 101 пикселов в первой строке и первом столбце начинает накопление заряда для кратковременного экспонирования. В частности, накопление заряда для кратковременного экспонирования на пикселах 302_1, 302_2, 303_1 и 303_2 начинается в периоде T3. В таком случае уровни сигналов как для сигнала VSEL_S[0] управления вертикальным блоком, так и сигнала HSEL_S[0] управления горизонтальным блоком устанавливаются на высоком уровне. В результате, импульсный сигнал PTX[1, 0] выбора пиксела формируется из импульсного сигнала PTX[0] выбора строки. Импульсный сигнал PTX[1, 0] выбора пиксела предоставляется на затворы транзисторов M2 переноса для пикселов 302_1 и 302_2. Аналогично, импульсный сигнал PTX[1, 1] выбора пиксела формируется из импульсного сигнала PTX[1] выбора строки. Импульсный сигнал PTX[1, 1] выбора пиксела предоставляется на затворы транзисторов M2 переноса для пикселов 303_1 и 303_2. Кратковременное накопление, таким образом, начинается.

(Период T4)

[0049] Период T4 является периодом, в котором пикселы 302_1, 302_2, 303_1 и 303_2, принадлежащие блоку 101 пикселов в первой строке и первом столбце, прекращают накопление заряда для кратковременного экспонирования. Импульсные сигналы PTX[Y, Z] выбора пиксела должны быть предоставлены на затворы транзисторов M2 переноса таких пикселов. С этой целью, уровень сигнала сигнальной линии VSEL_RD[0] устанавливается на высоком уровне. Сигнальная линия VSEL_RD[X] предназначается для считывания. Если уровень сигнала этой сигнальной линии устанавливается на высоком уровне, импульсные сигналы PTX[Y, Z] выбора пиксела формируются из импульсных сигналов PTX[X] выбора строки независимо от того, на каком уровне находятся сигналы VSEL управления вертикальным блоком и сигналы HSEL управления горизонтальным блоком. Импульсные сигналы PTX[Y, Z] выбора пикселов, таким образом, предоставляются на затворы транзисторов M2 переноса для пикселов.

[0050] С другой стороны, пикселы 304_1, 304_2, 305_1 и 305_2, принадлежащие блоку 101 пикселов во второй строке и первом столбце, продолжают долговременное экспонирование в периоде T4. С этой целью, импульсный сигнал PTX[Y, Z] выбора пиксела предоставляется на затворы транзисторов M2 переноса для пикселов 304_1, 304_2, 305_1 и 305_2 в периоде T4. Здесь, уровень сигнала для сигнала VSEL_L[1] управления вертикальным блоком поддерживается на низком уровне, так что импульсный сигнал PTX[Y, Z] выбора пиксела не формируется из импульсного сигнала PTX[2] или PTX[3] выбора строки. Сигналы возбуждения пикселов, которые должны быть предоставлены на затворы транзисторов M2 переноса, таким образом, предохраняются от предоставления пикселам 304_1, 304_2, 305_1 и 305_2.

(Период T5)

[0051] Период T5 является периодом, в котором пикселы 304_1, 304_2, 305_1 и 305_2, принадлежащие блоку 101 пикселов во второй строке и первом столбце, прекращают накопление заряда для долговременного экспонирования. Импульсные сигналы PTX[Y, Z] выбора пиксела должны быть предоставлены на затворы транзисторов M2 переноса таких пикселов. Для этого импульса уровень сигнала сигнальной линии VSEL_RD[1] устанавливается на высоком уровне. Импульсные сигналы PTX[Y, Z] выбора пиксела, таким образом, формируются из импульсных сигналов PTX[2] и PTX[3] выбора строки. Импульсные сигналы PTX[Y, Z] выбора пиксела предоставляются на затворы транзисторов M2 переноса для пикселов 304_1, 304_2, 305_1 и 305_2.

[0052] Хотя не описано подробно выше, сигнальные линии PSEL, иллюстрированные на фиг. 4, передают сигналы для включения транзисторов M4 выбора. Сигнальные линии PRES передают сигналы для включения транзисторов M1 сброса. Сигнальные линии PSEL и сигнальные линии PRES включаются в группу 205 сигнальных линий управления вертикальным блоком.

[0053] Как описано выше, каждый блок 101 пикселов могут быть независимо выбраны и управляться по времени экспонирования посредством конфигурирования схем 401 выбора, схемы 204 сканирования вертикального блока, группы 205 сигнальных линий управления вертикальным блоком, схемы 202 сканирования горизонтальным блоком и группы 203 сигнальных линий управления горизонтальным блоком.

[0054] Выбор сигналов возбуждения пикселов с помощью группы 203 сигнальных линий управления горизонтальным блоком и группы 205 сигнальных линий управления вертикальным блоком, описанных выше, является лишь примером. Схемы 401 выбора согласно настоящему примерному варианту осуществления могут быть любой схемой, которая конфигурируется так, что момент ввода сигналов возбуждения пикселов, связанных с множеством блоков 101 пикселов, может быть выбран независимо. Например, в вышеупомянутом примере, схемы 401 выбора выбирают, формировать ли импульсные сигналы переноса пикселов (импульсные сигналы выбора пикселов) из импульсных сигналов переноса строки (импульсных сигналов выбора строки), на основе сигналов, предоставленных в первом направлении, и сигналов, предоставленных во втором направлении, отличном от первого направления. Когда применяются в данном документе, сигналы, предоставленные в первом направлении, ссылаются на сигналы от схемы 204 сканирования вертикального блока. Сигналы, предоставленные во втором направлении, ссылаются на сигналы от схемы 202 сканирования горизонтального блока. Однако, схемы, отличные от таких схем 401 выбора, могут быть использованы для управления временем экспонирования относительно каждого блока 101 пикселов.

[0055] Например, время экспонирования может управляться поблочно с помощью схемы, обсужденной в выложенной японской патентной заявке № 2012-151847.

[0056] В вышеупомянутом примере время экспонирования управляется посредством управления сигналами, вводимыми на затворы транзисторов M2 переноса. Однако, сигналы, управляемые посредством схем 401 выбора, не ограничиваются этим. Например, транзистор переполнения может быть предусмотрен между блоком PD фотоэлектрического преобразования и напряжением VDD источника питания, и время экспонирования может управляться посредством управления вводом сигнала на затвор транзистора переполнения. В таком случае сигналы, которые должны управляться посредством схем 401 выбора, ссылаются на сигналы, вводимые на затворы транзисторов переполнения.

[0057] В вышеупомянутом примере первый блок пикселов и второй блок пикселов, размещенные в одной и той же строке, описываются как имеющие различные времена накопления заряда. Однако, первый блок пикселов и второй блок пикселов могут иметь одинаковое время накопления заряда и могут возбуждаться, чтобы иметь различные времена начала и времена окончания экспонирования. Другими словами, такое возбуждение может быть выполнено, если момент ввода сигналов возбуждения пикселов, относящихся к множеству блоков 101 пикселов, является независимо выбираемым.

[0058] В вышеупомянутом примере схема 204 сканирования вертикального блока описывается как имеющая функцию схемы вертикального сканирования. Однако, схема 204 сканирования вертикального блока и схема вертикального сканирования могут быть предусмотрены раздельно.

(Определение времени экспонирования блока пикселов за блоком пикселов посредством предварительного экспонирования)

[0059] Фиг. 5A иллюстрирует блоки 101 пикселов, которые включают в себя пикселы 110 первого типа и пикселы 120 второго типа. Пикселы 110 первого типа являются некоторыми из пикселов, размещенных в блоках 101 пикселов, и используются для прореживающего считывания (разреженные пикселы). Пикселы 120 второго типа являются пикселами, неиспользуемыми в прореживающем считывании, но используются для формирования изображения (неразреженные пикселы).

[0060] Первоначально, прореживающее считывание выполняется по пикселам 110 первого типа, и определяется условие экспонирования каждого блока 101 пикселов. В частности, сигналы пикселов 110 первого типа, размещенные во множестве блоков 101 пикселов, считываются через вертикальные выходные линии Vout. Аналоговые сигналы пикселов 110 вводятся в блоки 402 усиления второй интегральной схемы 410, иллюстрированной на фиг. 5B, через множество слоев разводки. Аналоговые сигналы, усиленные посредством блоков 402 усиления второй интегральной схемы 410, преобразуются в цифровые сигналы посредством блоков 403 AD-преобразования. Сигналы от пикселов 110 первого типа, сохраненные в запоминающих устройствах 404, последовательно считываются и выводятся в блок 208 обработки сигнала с помощью TG 207 и схемы 206 горизонтального сканирования.

[0061] Блок 208 обработки сигнала определяет условие экспонирования каждого блока 101 пикселов. Например, блок 208 обработки сигнала сравнивает значение сигнала пиксела с пороговым значением. Если значение сигнала пиксела больше порогового значения, блок 208 обработки сигнала определяет выполнение кратковременного экспонирования на блоке 101 пикселов, к которому пиксел 110 первого типа принадлежит. Если значение сигнала пиксела меньше или равно пороговому значению, блок 208 обработки сигнала определяет выполнение долговременного экспонирования на блоке 101 пикселов, к которому пиксел 110 первого типа принадлежит. Блок 208 обработки сигнала может определять, выполнять ли кратковременное экспонирование или долговременное экспонирование, на основе таблицы, в которой значения сигнала пиксела ассоциируются с режимами времени экспонирования.

[0062] TG 207, схема 204 сканирования вертикального блока, схема 202 сканирования горизонтального блока и схемы 401 выбора управляются на основе результата обработки блока 208 обработки сигнала. Например, как иллюстрировано на фиг. 3A, различные времена экспонирования могут, таким образом, быть заданы для соответствующих блоков 101 пикселов.

[0063] Как описано выше, время экспонирования каждого блока 101 пикселов может управляться после прореживающего считывания по предварительно определенным пикселам, размещенным в блоке 101 пикселов. В настоящем примерном варианте осуществления, по сравнению со случаем, когда сигналы считываются со всех пикселов 301 перед определением времени экспонирования каждого блока 101 пикселов, оптимальные условия экспонирования могут, следовательно, быть определены в более короткое время, поскольку времена экспонирования управляются на основе пикселов, считанных посредством прореживающего считывания.

[0064] Информация о движении объекта в каждом блоке 101 пикселов может быть извлечена из различий между кадрами. Например, согласно движению объекта, блок 101 пикселов, в котором кратковременное экспонирование выполняется в предыдущем кадре, может быть подвергнут долговременному экспонированию, или наоборот, блок 101 пикселов, в котором долговременное экспонирование выполняется в предыдущем кадре, может быть подвергнут кратковременному экспонированию. Извлечение информации о движении может быть выполнено посредством блока 208 обработки сигнала.

(Модификация 1)

[0065] Фиг. 6A является схемой, соответствующей фиг. 1A. Различие лежит в том, что каждый блок 101 пикселов включает в себя три строки и три столбца пикселов 301, и множество блоков 101 пикселов размещается в трех строках и четырех столбцах. Фиг. 6B является схемой, соответствующей фиг. 1B.

[0066] Фиг. 6C является укрупненным видом блоков 101 пикселов в первом столбце, окруженном прерывистыми линиями на фиг. 6A. Фиг. 6C иллюстрирует блоки 101a-101c пикселов первой-третьей строк. Среди множества пикселов 301, составляющих блоки 101a-101c пикселов, множество пикселов 301, размещенных в первом-третьем столбцах, соединяется с первой вертикальной выходной линией Vout[1] по третью вертикальную выходную линию Vout[3], соответственно.

[0067] Фиг. 6D является укрупненным видом блоков 201 в первом столбце, окруженном прерывистыми линиями на фиг. 6B. Фиг. 6D иллюстрирует блоки 201a-201c первой-третьей строк. Схемы 401a-401c выбора предусматриваются соответствующими блокам 201a-201c. Блоки 403 AD-преобразования предусматриваются для соответствующих столбцов пикселов. Первая-третья вертикальные выходные линии Vout[1]-Vout[3] соединяются с первым-третьим блоками 403[1]-403[3] AD-преобразования. Например, аналоговый сигнал от первой вертикальной выходной линии Vout[1] преобразуется в цифровой сигнал посредством блока 403[1] AD-преобразования. Таким образом, множество блоков 201 могут совместно использовать схему, имеющую одну функцию. Такая конфигурация может увеличивать области, занятые соответствующими блоками 403 AD-преобразования, и может увеличивать степень свободы в компоновке.

(Модификация 2)

[0068] Как иллюстрировано на фиг. 6C, если множество пикселов 301 размещается на первой интегральной схеме 400 с равными шагами в направлении столбца, множество вертикальных выходных линий Vout также размещается с равными шагами. Однако, в случае компоновки, иллюстрированной на фиг. 6D, если разводка от множества вертикальных выходных линий Vout распространяется на вторую интегральную схему 410, расстояния между вертикальными выходными линиями Vout и блоками 403 AD-преобразования изменяется от столбца к столбцу. Например, длина пути разводки от третьей вертикальной выходной линии Vout[3] до третьего блока 403[3] AD-преобразования больше длины пути разводки от первой вертикальной выходной линии Vout[1] до первого блока 403[1] AD-преобразования, с разницей в емкости разводки. Это может увеличивать сложность маршрутизации разводки и делать компоновку разводки усложненной.

[0069] Фиг. 7A иллюстрирует пример конфигурации для решения такой проблемы. На фиг. 7A схемы 401a-401c выбора предусматриваются как соответствующие блокам 201a-201c. Отличие от фиг. 6D лежит в том, что схемы 401a-401c выбора предусматриваются не в боковых фрагментах, а в нижних фрагментах блоков 201a-201c. Первый-третий блоки 403[1]-403[3] AD-преобразования предусматриваются как соответствующие каждому из блоков 101a-101c пикселов. С такой конфигурацией шаг первого-третьего блоков 403[1]-403[3] AD-преобразования в направлении столбца является практически таким же, что и шаг первой-третьей вертикальных выходных линий Vout[1]-Vout[3] в направлении столбца. Поскольку расстояния между вертикальными выходными линиями Vout и блоками 403 AD-преобразования в соответствующих столбцах становятся практически одинаковыми, отклонения в емкости разводки могут быть уменьшены.

(Модификация 3)

[0070] Фиг. 7B иллюстрирует дополнительную модификацию конфигурации на фиг. 7A. Фиг. 7B является такой же, что и фиг. 7A, в том, что шаг первого-третьего блоков 403[1]-403[3] AD-преобразования в направлении столбца и шаг первой-третьей вертикальных выходных линий Vout[1]-Vout[3] в направлении столбца являются практически одинаковыми. Однако, на фиг. 7B, множество блоков 201 совместно использует блоки 403[1]-403[3] AD-преобразования. В частности, блоки 201a и 201b совместно используют первый-третий блоки 403[1]-403[3] AD-преобразования. Согласно конфигурации на фиг. 7B, области, занятые соответствующими блоками 403 AD-преобразования, могут быть увеличены, и блоки AD-преобразования схемы большого масштаба могут быть использованы, по сравнению с конфигурацией на фиг. 7A.

(Модификация 4)

[0071] На фиг. 7C схемы 401a-401c выбора предусматриваются как соответствующие блокам 201a-201c. Первая-третья вертикальные выходные линии Vout[1]-Vout[3] соединяются с первым-третьим блоками 403[1]-403[3] AD-преобразования. Первый-третий блоки 403[1]-403[3] AD-преобразования предусматриваются как соответствующие блокам 201a-201c. Согласно конфигурации на фиг. 7C, области, занятые соответствующими блоками 403 AD-преобразования, могут быть увеличены, и блоки AD-преобразования схемы большого масштаба могут быть использованы, по сравнению с конфигурацией на фиг. 7A. В то время как конфигурация на фиг. 7B ограничивается блоками 403[1]-403[3] AD-преобразования длинной и узкой компоновки, конфигурация на фиг. 7C свободна от такого ограничения и может обеспечивать степень свободы в компоновке.

(Модификация 5)

[0072] Фиг. 8A является схемой, иллюстрирующей первую интегральную схему, на которой размещаются четыре блока 101a-101d пикселов, каждый блок пикселов включает в себя множество пикселов в трех строках и трех столбцах. Первая-шестая вертикальные выходные линии Vout[1]-Vout[6] предусматриваются как соответствующие первому-шестому столбцам пикселов. Как иллюстрировано на фиг. 8B, вторая интегральная схема включает в себя блоки 201a-201d, которые предусматриваются как соответствующие блокам 101a-101d пикселов. Схемы 401a-401d выбора, соответствующие блокам 101a-101d пикселов, предусматриваются в блоках 201a-201d. Первая-шестая вертикальные выходные линии Vout[1]-Vout[6] соединяются с первым-шестым блоками 403[1]-403[6] AD-преобразования. Первый-третий блоки 403[1]-403[3] AD-преобразования совместно используются блоками 201a и 201c. Четвертый-шестой блоки 403[4]-403[6] AD-преобразования совместно используются блоками 201b и 201d. Это может увеличивать области, занимаемые соответствующими блоками 403 AD-преобразования, и могут быть использованы блоки AD-преобразования схемы большого масштаба. Первая-третья вертикальные выходные линии Vout[1]-Vout[3], предусмотренные на первой интегральной схеме, и первый-третий блоки 403[1]-403[3] AD-преобразования, предусмотренные на второй интегральной схеме, могут быть связаны проводкой и соединены поверх блока 201a. Аналогично, четвертая-шестая вертикальные выходные линии Vout[4]-Vout[6], предусмотренные на первой интегральной схеме, и четвертый-шестой блоки 403[4]-403[6] AD-преобразования, предусмотренные на второй интегральной схеме, могут быть связаны проводкой и соединены поверх блока 201d. Когда используется в данном документе, связывание проводкой и соединение поверх блока 201a или блока 201d означает, например, что соединения между первой интегральной схемой и второй интегральной схемой перекрываются с блоком 201a или 201d в виде сверху. Посредством использования такой конфигурации разводка, протягивающаяся от вертикальных выходных линий Vout[1]-Vout[6] до блоков 403[1]-403[6] AD-преобразования, может быть сокращена, и отклонения в емкостях разводки соответствующих разводок могут быть уменьшены. Упрощенная маршрутизация разводки от вертикальных выходных линий Vout[1]-Vout[6] до блоков 403[1]-403[6] AD-преобразования может обеспечивать степень свободы в компоновке разводки относительно другой разводки.

[0073] Второй примерный вариант осуществления отличается от первого примерного варианта осуществления в том, что первая интегральная схема 400 включает в себя блоки усиления и блоки AD-преобразования, и блоки, предусмотренные на второй интегральной схеме 410, включают в себя множество TG и блоки обработки сигнала.

[0074] Фиг. 9 иллюстрирует первую интегральную схему 400 согласно настоящему примерному варианту осуществления. Множество блоков 101 пикселов размещается в виде матрицы. Первая интегральная схема 400 включает в себя столбцовую схему, включающую в себя блок 502 усиления и блок 503 AD-преобразования относительно каждого столбца для множества блоков 101 пикселов. Блоки 502 усиления предусматриваются в добавочных целях и могут быть опущены в некоторых конфигурациях.

[0075] Фиг. 9 иллюстрирует конфигурацию, в которой все блоки 503 AD-преобразования предусматриваются на первой интегральной схеме 400. Однако, первые фрагменты элементов, составляющих блоки 503 AD-преобразования, могут быть предусмотрены на первой интегральной схеме 400, а вторые фрагменты - на второй интегральной схеме 410. Например, блоки 503 AD-преобразования могут быть предусмотрены на первой интегральной схеме 400, а счетчики - на второй интегральной схеме 410. Предоставление счетчиков на второй интегральной схеме 410 обеспечивает пространство на первой интегральной схеме 400, что является полезным в размещении большего числа пикселов.

[0076] Фиг. 10A иллюстрирует вторую интегральную схему 410 согласно настоящему примерному варианту осуществления. Сигналы от схемы 602 сканирования горизонтального блока вводятся во множество вторых блоков 601 через группу 603 сигнальных линий управления горизонтальным блоком. Сигналы от схемы 604 сканирования вертикального блока вводятся во множество вторых блоков 601 через группу 605 сигнальных линий управления вертикальным блоком.

[0077] Фиг. 10B иллюстрирует конфигурацию каждого второго блока 601. Второй блок 601 включает в себя TG 207 и блок 208 обработки сигнала помимо схемы 401 выбора.

[0078] Возвратимся к фиг. 9. Цифровые сигналы от блоков 503 AD-преобразования сохраняются в памяти 606, иллюстрированной на фиг. 10A. Сигналы из памяти 606 выводятся в блоки 208 обработки сигнала на фиг. 10B. Например, блоки 208 обработки сигнала выполняют вычисление разницы между сигналом области оптического уровня черного и сигналом области эффективного пиксела и суммы сигналов пикселов. На основе результата обработки блоки 208 обработки сигнала выводят управляющие сигналы во множество TG 207. Например, блоки 208 обработки сигнала выводят сигналы для управления временем накопления заряда (временем экспонирования) соответствующих блоков 101 пикселов. TG 207 управляют временем экспонирования соответствующих блоков 101 пикселов, выводя сигналы в схему 602 сканирования горизонтального блока и схему 604 сканирования вертикального блока и управляя сигналами PTX возбуждения через схемы 401 выбора. Например, первый блок пикселов может управляться, чтобы иметь первое время экспонирования, а второй блок пикселов может управляться, чтобы иметь второе время экспонирования, которое является временем экспонирования, более длительным, чем первое время экспонирования.

[0079] Фиг. 1°C иллюстрирует модификацию конфигурации второго блока 601. На фиг. 1°C схемы 401a-401c выбора предусматриваются как соответствующие блокам 601a-601c. Между тем, TG 207 совместно используется блоками 601a и 601b. Блок 208 обработки сигнала совместно используется блоками 601b и 601c.

[0080] В настоящем примерном варианте осуществления схемы 401 выбора, соответствующие блокам 101 пикселов, предусматриваются в блоках 201, соответствующих соответствующим блокам 101 пикселов. Блоки 201, соответствующие блокам 101 пикселов, также включают в себя схемы, которые могут быть предусмотрены на первой интегральной схеме 400 или второй интегральной схеме 410, отличные от схем 401 выбора. Примеры схем, отличных от схем 401 выбора, включают в себя множество TG 207 и блоки 208 обработки сигнала. Размещая схемы, отличные от схем 401 выбора, в блоках 201, пространство первой интегральной схемы 400, отличное от блоков 101 пикселов, и пространство второй интегральной схемы 410, отличное от блоков 201, может преимущественно быть уменьшено для экономии пространства.

[0081] Третий примерный вариант осуществления отличается от второго примерного варианта осуществления в том, что блоки усиления и блоки AD-преобразования, которые предусматриваются на первой интегральной схеме 400 во втором примерном варианте осуществления, размещаются во вторых блоках 901 на второй интегральной схемы 410.

[0082] Фиг. 11A иллюстрирует вторую интегральную схему 410 согласно настоящему примерному варианту осуществления. Сигналы от схемы 902 сканирования горизонтального блока вводятся во множество вторых блоков 901 через группу 903 сигнальных линий управления горизонтальным блоком. Сигналы от схемы 904 сканирования вертикального блока вводятся во множество вторых блоков 901 через группу 905 сигнальных линий управления вертикальным блоком.

[0083] Фиг. 11B иллюстрирует конфигурацию каждого второго блока 901. Второй блок 901 включает в себя TG 207, блок 208 обработки сигнала, блок 402 усиления, блок 403 AD-преобразования и память 404 помимо схемы 401 выбора.

[0084] Аналоговые сигналы от пикселов преобразуются в цифровые сигналы посредством блока 403 AD-преобразования через блок 402 усиления и сохраняются в памяти 404. Цифровые сигналы, сохраненные в памяти 404, выводятся в блок 208 обработки сигнала. Например, блок 208 обработки сигнала выполняет вычисление разницы между сигналом области оптического уровня черного и сигналом области эффективного пиксела и суммы сигналов пикселов. На основе результата обработки блок 208 обработки сигнала выводит управляющий сигнал в TG 207. Например, блок 208 обработки сигнала выводит сигнал для управления временем накопления заряда (временем экспонирования) каждого блока пикселов. TG 207 управляет временем экспонирования блока пикселов, выводя сигналы в схему 902 сканирования горизонтального блока и схему 904 сканирования вертикального блока и управляя сигналами PTX[Y, Z] возбуждения пикселов через схему 401 выбора. Например, первый блок пикселов может управляться, чтобы иметь первое время экспонирования, а второй блок пикселов может управляться, чтобы иметь второе время экспонирования, которое является временем экспонирования, более длительным, чем первое время экспонирования.

[0085] В настоящем примерном варианте осуществления схемы 401 выбора, соответствующие блокам 101 пикселов, предусматриваются во вторых блоках 901, соответствующих соответствующим блокам 101 пикселов. Вторые блоки 901, соответствующие соответствующим блокам 101 пикселов, включают в себя схемы, которые могут быть предусмотрены на первой интегральной схеме 400 или второй интегральной схеме 410, отличные от схем 401 выбора. Примеры схем, отличных от схем 401 выбора, включают в себя блоки 402 усиления, блоки 403 AD-преобразования, запоминающие устройства 404, множество TG 207 и блоки 208 обработки сигнала. Размещая схемы, отличные от схем 401 выбора, во вторых блоках 901, пространство первой интегральной схемы 400, отличное от блоков 101 пикселов, и пространство второй интегральной схемы 410, отличное от вторых блоков 901, может преимущественно быть уменьшено для экономии пространства.

[0086] Фиг. 12 является блок-схемой, иллюстрирующей конфигурацию системы 500 формирования изображения согласно четвертому примерному варианту осуществления. Система 500 формирования изображения согласно настоящему примерному варианту осуществления включает в себя устройство 2000 формирования изображения, к которому применяется конфигурация какого-либо одного из вышеупомянутых устройств формирования изображения. Конкретные примеры системы 500 формирования изображения включают в себя цифровую фотокамеру, цифровую видеокамеру и камеру наблюдения. Система 500 формирования изображения включает в себя устройство 2000 формирования изображения, линзу 5020, диафрагму 504 и защитный экран 506 для защиты линзы 5020. Система 500 формирования изображения включает в себя блок 5080 обработки сигнала (также называемый блоком формирования сигнала изображения), который обрабатывает выходной сигнал, выводимый из устройства 2000 формирования изображения. Блок 5080 обработки сигнала выполняет операции обработки сигнала для выполнения различных корректировок и сжатий по входному сигналу и вывода результирующего сигнала согласно необходимости. Блок 5080 обработки сигнала может иметь функцию выполнения обработки AD-преобразования по выходному сигналу, выводимому из устройства 2000 формирования изображения. Система 500 формирования изображения дополнительно включает в себя блок 510 буферной памяти для временного хранения данных изображения и блок 512 внешнего интерфейса (I/F) для связи с внешним компьютером. Система 500 формирования изображения дополнительно включает в себя носитель 514 записи, такой как полупроводниковое запоминающее устройство, для записи или считывания данных изображения и блок 516 I/F управления носителем записи для выполнения записи или считывания на носитель 514 записи.

[0087] Система 500 формирования изображения дополнительно включает в себя блок 518 общего управления и вычисления и блок 520 генерации тактовых сигналов. Блок 518 общего управления и вычисления выполняет различные вычисления и управляет всей системой 500 формирования изображения, такой как цифровая фотокамера. Блок 520 генерации тактовых сигналов выводит различные тактовые сигналы в устройство 2000 формирования изображения и блок 5080 обработки сигнала. Устройство 2000 формирования изображения выводит сигнал изображения в блок 5080 обработки сигнала. Блок 5080 обработки сигнала применяет предварительно определенную обработку сигнала к сигналу изображения, выводимому из устройства 2000 формирования изображения, и выводит данные изображения. Блок 5080 обработки сигнала формирует изображение с помощью сигнала изображения.

[0088] Система формирования изображения, приспособленная для получения изображений более высокого качества, может быть достигнута посредством построения системы формирования изображения с помощью устройства 2000 формирования изображения, которое является каким-либо одним из устройств формирования изображения вышеупомянутых примерных вариантов осуществления.

[0089] Система формирования изображения и движущийся объект согласно пятому примерному варианту осуществления будут описаны со ссылкой на фиг. 13A и 13B. Настоящий примерный вариант осуществления имеет дело с примером системы формирования изображения, относящейся к камере в транспортном средстве. Фиг. 13A и 13B иллюстрируют пример системы транспортного средства и системы формирования изображения, установленной в нем. Система 701 формирования изображения включает в себя устройства 702 формирования изображения, блоки 715 предварительной обработки изображения, интегральную схему 703 и оптические системы 714. Оптические системы 714 формируют оптические изображения объекта на устройствах 702 формирования изображения. Устройства 702 формирования изображения преобразуют оптические изображения объекта, сформированные посредством оптических систем 714, в электрические сигналы. Устройства 702 формирования изображения являются устройствами формирования изображения согласно какому-либо одному из вышеупомянутых примерных вариантов осуществления. Блоки 715 предварительной обработки изображения выполняют предварительно определенную обработку сигнала по сигналам, выводимым из устройств 702 формирования изображения. Система 701 формирования изображения включает в себя, по меньшей мере, два набора оптических систем 714, устройств 702 формирования изображения и блоков 715 предварительной обработки изображения. Выходные сигналы из блоков 715 предварительной обработки изображения соответствующих наборов вводятся в интегральную схему 703.

[0090] Интегральная схема 703 является интегральной схемой для применений в системе формирования изображения. Интегральная схема 703 включает в себя блок 704 обработки изображения, включающий в себя память 705, блок 706 измерения оптического расстояния, блок 707 вычисления параллакса, блок 708 распознавания объекта и блок 709 обнаружения неисправности. Блок 704 обработки изображения выполняет обработку изображения, такую как обработку развертки и исправление искажения, по выходным сигналам блоков 715 предварительной обработки изображения. Память 705 временно хранит захваченные изображения и хранит позиции искажений формирующих изображение пикселов. Блок 706 измерения оптического расстояния выполняет фокусировку на объекте и выполняет измерение расстояния. Блок 707 вычисления параллакса вычисляет параллакс (разность фаз между изображениями параллакса) из множества частей данных изображения, полученных посредством множества устройств 702 формирования изображения. Блок 708 распознавания объекта выполняет распознавание объектов, таких как транспортное средство, дорога, знак и человек. Блок 709 обнаружения неисправности обнаруживает неисправность устройства 702 формирования изображения и уведомляет главный блок 713 управления о неисправности.

[0091] Интегральная схема 703 может быть реализована посредством аппаратных средств специализированной конструкции, посредством модулей программного обеспечения или посредством их комбинации. Интегральная схема 703 может быть реализована посредством программируемой пользователем вентильной матрицы (FPGA), специализированной интегральной схемы (ASIC) или их комбинации.

[0092] Главный блок 713 управления руководит и управляет операциями системы 701 формирования изображения, датчиков 710 транспортного средства и блока 720 управления. Альтернативно, система 701 формирования изображения, датчики 710 транспортного средства и блок 720 управления могут индивидуально включать в себя интерфейс связи и передавать и принимать управляющие сигналы через соответствующие сети связи (например, по стандарту локальной сети контроллеров (CAN)) без предоставления главного блока 713 управления.

[0093] Интегральная схема 703 имеет функцию передачи управляющих сигналов и установки значений для устройств 702 формирования изображения посредством приема управляющих сигналов от главного блока 713 управления или согласно своему собственному блоку управления. Например, интегральная схема 703 передает настройки для переключателей напряжения возбуждения в устройствах 702 формирования изображения посредством сигналов и настройки для переключения переключателей напряжения по кадрам.

[0094] Система 701 формирования изображения соединяется с датчиками 710 транспортного средства и может обнаруживать условия движения рассматриваемого транспортного средства, такие как скорость транспортного средства, поворот относительно вертикальной оси и угол поворота управляемых колес, окружающую обстановку для рассматриваемого транспортного средства и состояния транспортных средств и препятствий. Датчики 710 транспортного средства также служат в качестве блока получения информации о расстоянии, который получает информацию о расстоянии относительно расстояния до объекта из изображений параллакса. Система 701 формирования изображения также соединяется с блоком 711 управления помощью при вождении, который выполняет различные операции помощи при вождении, такие как автоматическое рулевое управление, автоматическое поддержание заданной скорости и функция предотвращения столкновения. В частности, для функции определения столкновения, блок 711 управления помощью при вождении выполняет оценку столкновения и определяет присутствие или отсутствие столкновения с другим транспортным средством или препятствием на основе результатов обнаружения системы 701 формирования изображения и датчиков 710 транспортного средства. Блок 711 управления помощью при вождении, таким образом, выполняет управление уклонением, если столкновение оценивается как имеющее место, или активирует системы безопасности в случае столкновения.

[0095] Система 701 формирования изображения также соединяется с устройством 712 тревожного оповещения, которое выдает тревожное оповещение водителю на основе результата определения блока определения столкновения. Например, если результат определения блока определения столкновения показывает высокую вероятность столкновения, главный блок 713 управления выполняет управление транспортным средством для уклонения от столкновения или уменьшения повреждения посредством применения тормоза, отпускания педали газа и/или сдерживания выходной мощности двигателя. Устройство 712 тревожного оповещения предупреждает пользователя, выдавая тревожный звук, отображая информацию тревожного оповещения на экране блока отображения навигационной системы автомобиля или на приборной панели и/или прикладывая вибрации к ремню безопасности или рулевому колесу.

[0096] В настоящем примерном варианте осуществления система 701 формирования изображения захватывает изображения около, например, спереди или сзади транспортного средства. Фиг. 13B иллюстрирует пример компоновки системы 701 формирования изображения в случае, когда система 701 формирования изображения захватывает изображения спереди транспортного средства.

[0097] Настоящий примерный вариант осуществления описал управление для уклонения от столкновения с другими транспортными средствами. Однако, настоящий примерный вариант осуществления также применим к управлению для выполнения автоматического вождения, чтобы следовать за другим транспортным средством, и управлению для выполнения автоматического вождения, чтобы не отклоняться от полосы движения. Система 701 формирования изображения не ограничивается транспортным средством типа рассматриваемого транспортного средства и может быть применена к движущемуся объекту (движущемуся устройству), такому как судно, летательный аппарат и промышленный робот. Система 701 формирования изображения не ограничивается движущимся объектом, тем или иным, и может широко применяться к устройствам, которые используют распознавание объекта. Примеры включают в себя интеллектуальную транспортную систему (ITS).

(Другие примерные варианты осуществления)

[0098] В то время как примерные варианты осуществления были описаны выше, настоящее изобретение не ограничивается примерными вариантами осуществления, и могут быть выполнены различные модификации и изменения. Примерные варианты осуществления являются взаимно применимыми и могут быть реализованы исключительно или как комбинация множества вариантов осуществления или их отличительных признаков при необходимости, или когда комбинация элементов или отличительных признаков из отдельных элементов в одном варианте осуществления является полезной.

[0099] Устройство формирования изображения согласно примерному варианту осуществления настоящего изобретения направлено на предоставление устройства формирования изображения улучшенной производительности по сравнению с устройством выложенной японской патентной заявки № 2012-151847.

[0100] В то время как настоящее изобретение было описано со ссылкой на примерные варианты осуществления, должно быть понятно, что изобретение не ограничено раскрытыми примерными вариантами осуществления. Рамки следующей формулы должны соответствовать самой широкой интерпретации так, чтобы охватывать все такие модификации и эквивалентные структуры и функции.