Результат интеллектуальной деятельности: Широкодиапазонный генератор импульсов с кратно дробной автоподстройкой частоты

Вид РИД

Изобретение

ОБЛАСТЬ ТЕХНИКИ

Изобретение относится к области генерирования импульсов с автоматической подстройкой частоты для использования в цифровых многопроцессорных системах в качестве широкодиапазонного перестраиваемого генератора тактовых частот.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

Известен "ГЕНЕРАТОР ИМПУЛЬСОВ С ЦИФРОВОЙ ПЕРЕСТРОЙКОЙ ПЕРИОДА" - Патент РФ №2170490, содержащий последовательно соединенные инвертор и секционированную линию задержки, отводы которой подключены к соответствующим информационным входам мультиплексора, в то время как выход мультиплексора присоединен ко входу основного инвертора, соответствующие адресные входы мультиплексора соединены с выходами блока преобразования цифрового кода периода, который своими старшими входными отводами подключен к соответствующим входным зажимам, а младшим входным отводом подключен к нулевому отводу линии задержки через первый вход логической ячейки 2И-НЕ, второй вход которой подключен к младшему входному зажиму. Генерирование импульсов в устройстве обеспечивается за счет обратной связи инвертора через секционированную линию задержки. Время задержки в цепи обратной связи регулируется путем управляемого выбора отвода секционированной линии задержки, сигнал с которого используется в качестве сигнала обратной связи.

Недостатком устройства "ГЕНЕРАТОР ИМПУЛЬСОВ С ЦИФРОВОЙ ПЕРЕСТРОЙКОЙ ПЕРИОДА" - Патент РФ №2170490, является отсутствие синхронизации с опорной частотой, проблемная реализация в случае необходимости использования мультиплексоров с большим количеством информационных входов, узкий диапазон перестройки генерируемой частоты в случае большого количества элементов линии задержки, вероятность возникновения на выходе импульсных помех (глитчей) в моменты внешнего управления периодом генерации, возможность существенного отклонения скважности выходных импульсов от идеального меандра в случае несбалансированности элементов линии задержки по фронтам и спадам.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является, принятый за прототип, "ГЕНЕРАТОР ИМПУЛЬСОВ С АВТО ПОДСТРОЙ КОЙ ЧАСТОТЫ" - Патент РФ №2260904, выполненный в виде цепи последовательно соединенных - основного инвертора, основного и дополнительных элементов задержки замкнутой в кольцо через многоканальный мультиплексор, выход которого присоединен ко входу основного инвертора, а информационные входы - к выходам соответствующих дополнительных элементов задержки, в то время как к управляющим входам мультиплексора подключен реверсивный двухвходовый счетчик импульсов с формирователями на каждом его входе, один из которых является входом внешних опорных импульсов, а другой подключен к главному выходу генератора, который в свою очередь получает сигнал через буферизированный пассивный RC фильтр с выхода мультиплексора. Счетчик импульсов управляет частотой генератора путем изменения эффективной длины линии задержки и его состояние зависит от соотношения опорной и выходной частот. В процессе автоподстройки частоты происходит изменение состояния счетчика в направлении, когда опорные и выходные импульсы начинают поступать поочередно. Устройство переходит в следящий режим с погрешностью, не превышающей времени одного из элементов задержки.

Недостатком устройства "ГЕНЕРАТОР ИМПУЛЬСОВ С АВТОПОДСТРОЙКОЙ ЧАСТОТЫ" - Патент РФ №2260904, является его относительно проблемная реализация для интеграции в составе СБИС (сверхбольшая интегральная схема) - представляется довольно сложной внутрикристальная схема применяемого счетчика импульсов с двумя независимыми счетными входами, так как в типовых базисах современных субмикронных библиотек такие синхронные элементы попросту отсутствуют, как и мультиплексоры с большим количеством информационных входов. Недостаток, который вытекает из предыдущего - узкий диапазон перестройки генерируемой частоты в случае большого количества элементов линии задержки. Также в схеме автоподстройки не предусмотрено иных соотношений частот генератора к опорной частоте кроме как 1:1, то есть, отсутствуют режимы умножения и деления частоты входных опорных импульсов, а при самих процессах синхронизации на выходе чрезвычайно велика вероятность возникновения импульсных помех (глитчей). Чтобы хоть как-то их сглаживать необходим RC (resistor-capacitor) фильтр низких частот, который, как следствие данной проблемы, установлен в прототипе на выходе. Еще один недостаток заключается в потенциальной возможности существенного отклонения скважности выходных импульсов от идеального меандра в случае несбалансированности элементов линии задержки по фронтам и спадам.

ЗАДАЧА ИЗОБРЕТЕНИЯ

Задача, на решение которой направлено предлагаемое изобретение, заключается в создании широкодиапазонного управляемого генератора тактовых частот для многопроцессорных систем на кристалле, обладающего высокими эксплуатационными и низкими затратными характеристиками с возможностью легкой интеграции в составе СБИС на базе современных субмикронных технологических процессов, используя при этом только лишь цифровой маршрут проектирования - то есть без необходимости прохождения трудоемкого и дорогостоящего аналогового маршрута.

Техническим результатом изобретения является возможность легкой интеграции в составе СБИС на базе современных субмикронных технологических процессов, используя при этом только лишь цифровой маршрут проектирования (без привлечения длительного и дорогостоящего аналогового маршрута), широкий диапазон перестройки генерируемых частот, возможность как умножения так и деления частоты входных опорных импульсов на произвольный переменный коэффициент, отсутствие в выходном сигнале импульсных помех (глитчей), а также близкая к идеальному меандру скважность выходных импульсов.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Указанный технический результат при осуществлении изобретения достигается за счет того, что широкодиапазонный генератор импульсов с кратно дробной автоподстройкой частоты, содержит вход сброса, основной выход генератора, вход опорной частоты, линию задержки на логических элементах содержащую набор инверторов (A1, А2 … AN+1) на цифровых логических элементах общим числом N+1 и набор двухканальных инвертирующих мультиплексоров (X1, Х2 … XN+1) на цифровых логических элементах общим числом N+1, элемент логического AND, цифровую двунаправленную линию задержки на триггерах (D1, D2 … DN) общим числом N, шину управления цифровой линией задержки, управляющий компаратор, входную шину мантиссы масштабирующего коэффициента автоподстройки (M1 … ML), входную шину экспоненты масштабирующего коэффициента авто подстройки (E1 … EP), основной счетчик выходных импульсов с внутренней шиной счета (C1 … CL), счетчик делитель импульсов опорной частоты и транслятор сигнала между частотными доменами. Данные компоненты соединены следующим образом - вход сброса подключен ко входу сброса счетчика выходных импульсов, ко входу сброса счетчика делителя импульсов опорной частоты, ко всем входам сбросов триггеров (D1, D2 … DN) цифровой двунаправленной линии задержки, ко входу сброса транслятора сигнала между частотными доменами и к первому входу элемента логического AND. Выход элемента логического AND подключен ко входу первого инвертора (A1), второй вход элемента логического AND подключен к выходу первого двухканального инвертирующего мультиплексора (X1) линии задержки на логических элементах. Выход первого двухканального инвертирующего мультиплексора (X1) подключен к основному выходу генератора, который также подключен ко всем тактовым входам триггеров (D1, D2 … DN), к тактовому входу транслятора сигнала между частотными доменами и тактовому входу счетчика выходных импульсов. Выход счетчика выходных импульсов через шину счета выходных импульсов (C1 … CL) подключен к первому входу управляющего компаратора. Ко второму входу управляющего компаратора подключена входная шина мантиссы масштабирующего коэффициента автоподстройки (M1 … ML) Выход управляющего компаратора через шину управления цифровой линией задержки подключен ко входам управления цифровой двунаправленной линии задержки, содержащей триггера (D1, D2 … DN). Соответствующие выходы триггеров (D1, D2 … DN) подключены к соответствующим управляющим входам двухканальных инвертирующих мультиплексоров (X1, Х2 … XN), соединенных таким образом, что вторые информационные входы двухканальных инвертирующих мультиплексоров (X1, Х2 … XN) соединены с выходами двухканальных инвертирующих мультиплексоров (Х2, Х3 … XN+1) соответственно, а первые информационные входы двухканальных инвертирующих мультиплексоров (X1, Х2 … XN) соединены с соответствующими выходами инверторов (A1, А2 … AN). Выходы инверторов (A1, А2 … AN) подключены к соответствующим входам инверторов (А2, А3 … AN+1). Вход опорной частоты и шина экспоненты масштабирующего коэффициента автоподстройки (E1 … EP) подключены к соответствующим входам счетчика делителя импульсов опорной частоты. Выход счетчика делителя импульсов опорной частоты подключен ко входу транслятора сигнала между частотными доменами. Выход транслятора сигнала между частотными доменами подключен к счетчику выходных импульсов и управляющему компаратору.

ОСУЩЕСТВЛЕНИЕ ИЗОБРЕТЕНИЯ

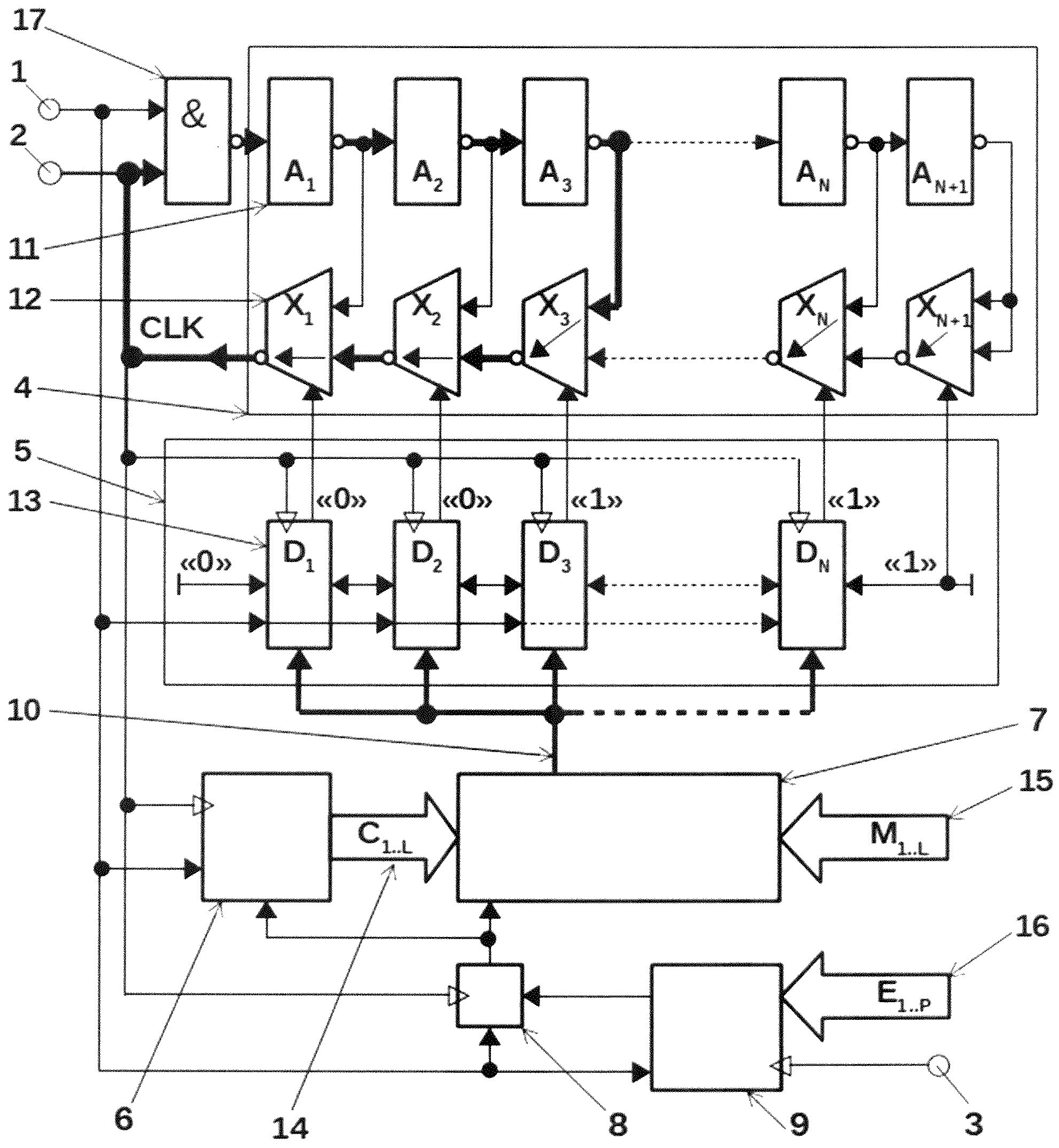

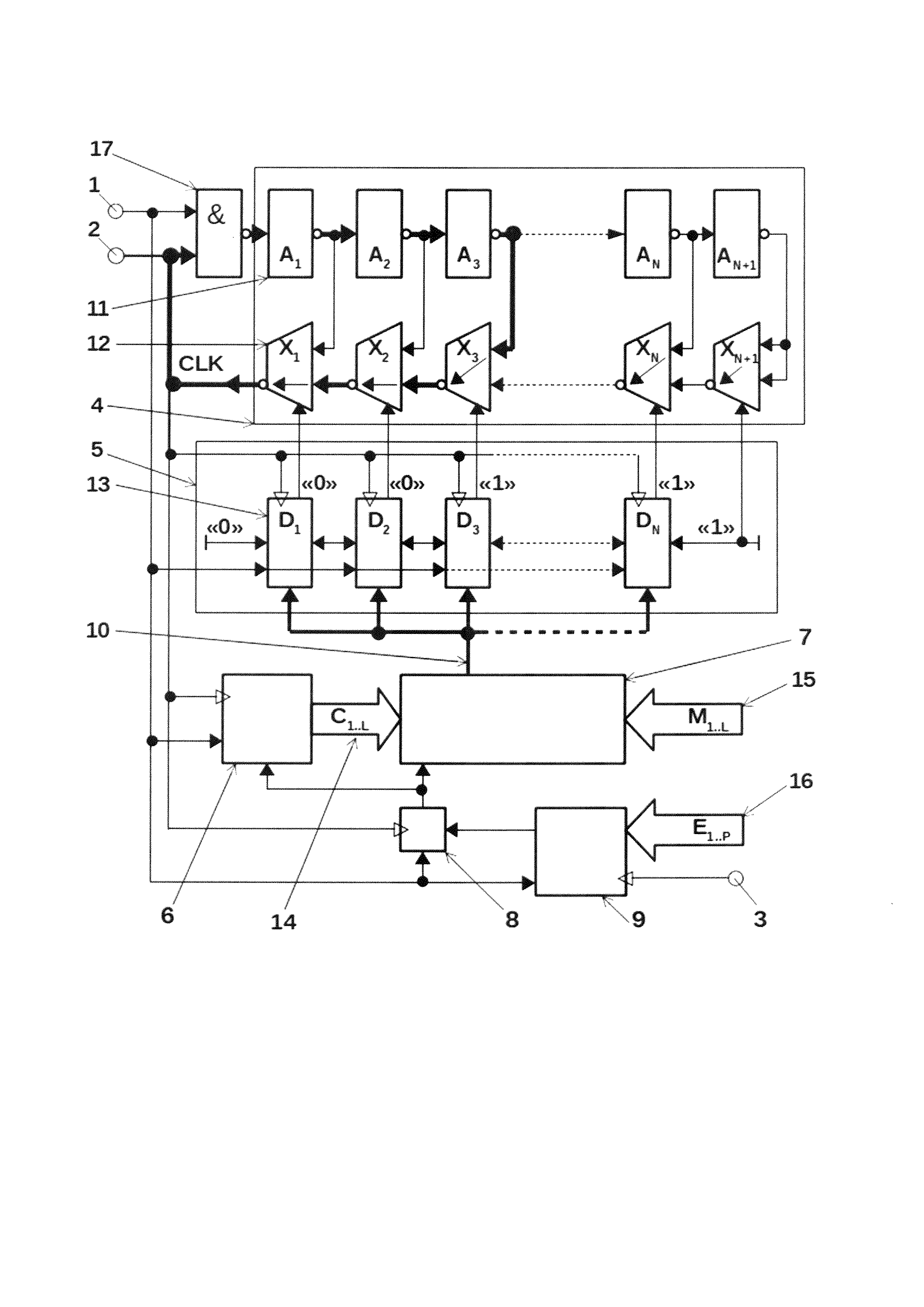

На чертеже представлена схема предлагаемого широкодиапазонного генератора импульсов с кратно дробной автоподстройкой частоты, на которой изображены: вход сброса 1, основной выход генератора 2, вход опорной частоты 3, линия задержки на логических элементах 4, цифровая двунаправленная линия задержки 5, основной счетчик выходных импульсов 6, управляющий компаратор 7, транслятор сигнала между частотными доменами 8, счетчик делитель импульсов опорной частоты 9, шина управления цифровой линией задержки 10, набор инверторов 11 (A1, А2 … AN+1) на цифровых логических элементах общим числом N+1, набор двухканальных инвертирующих мультиплексоров 12 (X1, Х2... XN+1) на цифровых логических элементах общим числом N+1, триггера 13 (D1, D2 … DN) общим числом N, внутренняя шина счета 14 (C1 … CL), входная шина мантиссы масштабирующего коэффициента автоподстройки 15 (M1 … ML), входная шина экспоненты масштабирующего коэффициента автоподстройки 16 (E1 … EP), элемент логического AND 17.

Компоненты широкодиапазонного генератора импульсов с кратно дробной автоподстройкой частоты соединены следующим образом - вход сброса 1 подключен ко входу сброса счетчика выходных импульсов 6, ко входу сброса счетчика делителя импульсов опорной частоты 9, ко всем входам сбросов триггеров 13 (D1, D2 … DN) цифровой двунаправленной линии задержки 5, ко входу сброса транслятора сигнала между частотными доменами 8 и к первому входу элемента логического AND 17. Выход элемента логического AND 17 подключен ко входу первого инвертора 11 (A1). Второй вход элемента логического AND 17 подключен к выходу первого двухканального инвертирующего мультиплексора 12 (X1) линии задержки 4 на логических элементах. Выход первого двухканального инвертирующего мультиплексора 12 (X1) подключен к основному выходу генератора 2, который 1также подключен ко всем тактовым входам триггеров 13 (D1, D2 … DN), к тактовому входу транслятора сигнала между частотными доменами 8 и тактовому входу счетчика выходных импульсов 6. Выход счетчика выходных импульсов 6 через шину счета выходных импульсов 14 (C1 … CL) подключен к первому входу управляющего компаратора 7, ко второму входу которого подключена входная шина мантиссы масштабирующего коэффициента автоподстройки 15 (M1 … ML). Выход управляющего компаратора 7 через шину управления цифровой линией задержки 10 подключен ко входам управления цифровой двунаправленной линии задержки 5, содержащей триггера 13 (D1, D2 … DN). Соответствующие выходы триггеров 13 (D1, D2 … DN) подключены к соответствующим управляющим входам двухканальных инвертирующих мультиплексоров 12 (X1, Х2 … XN), соединенных таким образом, что вторые информационные входы двухканальных инвертирующих мультиплексоров 12 (X1, Х2 … XN) соединены с соответствующими выходами двухканальных инвертирующих мультиплексоров 12 (Х2, Х3 … XN+1), а первые информационные входы двухканальных инвертирующих мультиплексоров 12 (X1, Х2 … XN) соединены с соответствующими выходами инверторов 11 (A1, А2 … AN). Выходы инверторов 11 (A1, А2 … AN) подключены к соответствующим входам инверторов 11 (А2, А3 … AN+1). Вход опорной частоты 3 и шина экспоненты масштабирующего коэффициента автоподстройки 16 (E1. … ЕР) подключены к соответствующим входам счетчика делителя импульсов опорной частоты 9, выход которого подключен ко входу транслятора сигнала между частотными доменами 8. Выход транслятора сигнала между частотными доменами 8 подключен к счетчику выходных импульсов 6 и управляющему компаратору 7.

Выбор инверторов и двухканальных инвертирующих мультиплексоров в качестве элементов задержки обусловлен тем, что в типовых современных субмикронных базисах такие элементы всегда присутствуют и являются наиболее быстродействующими (подробно см. [4]), что дает возможность уменьшить общий минимальный квант времени на который линия задержки 4 на логических элементах может перестраиваться при ее направленной адаптации, что, в свою очередь, дает улучшение точности регулирования и стабильности выходной частоты. Также, выбор инверторов и инвертирующих двухканальных мультиплексоров вместо неинвертирующих элементов задержки и неинвертирующего многоканального мультиплексора примененных в устройстве прототипе (подробно см. [1]), обусловлен лучшей балансировкой задержек по фронтам и спадам, и как следствие, лучшей скважности генерируемых импульсов. Например, при распространении сигнала во время первого полупериода через последовательность неинвертирующих цепей, как сделано в устройстве прототипе (подробно см. [1]), их суммарная задержка по нарастающим фронтам складываются из аналогичных задержек по нарастающим фронтам каждого элемента, тогда как для второго полупериода суммарная задержка складывается из аналогичных задержек каждого элемента по спадающим фронтам. Для любого логического элемента имеющего конкретную физическую реализацию эти времена никогда не совпадают и зачастую сильно отличаются (подробно см.[4]), давая в результате разные длительности полупериодов. При распространении же сигнала через цепочки инверторов и двухканальных инвертирующих мультиплексоров (как в предлагаемом генераторе), на каждую пару инверторов и двухканальных инвертирующих мультиплексоров приходится один фронт импульса и один его спад, что для обоих полупериодов дает примерно одинаковое количество фронтов и спадов (отличается максимум на единицу). В результате, для обоих полупериодов обеспечивается примерное равенство их длительностей вне зависимости от соотношений задержек по фронтам и спадам конкретных использованных библиотечных элементов, или, иными словами, делает форму выходных импульсов в предлагаемом генераторе близкой к идеальному меандру.

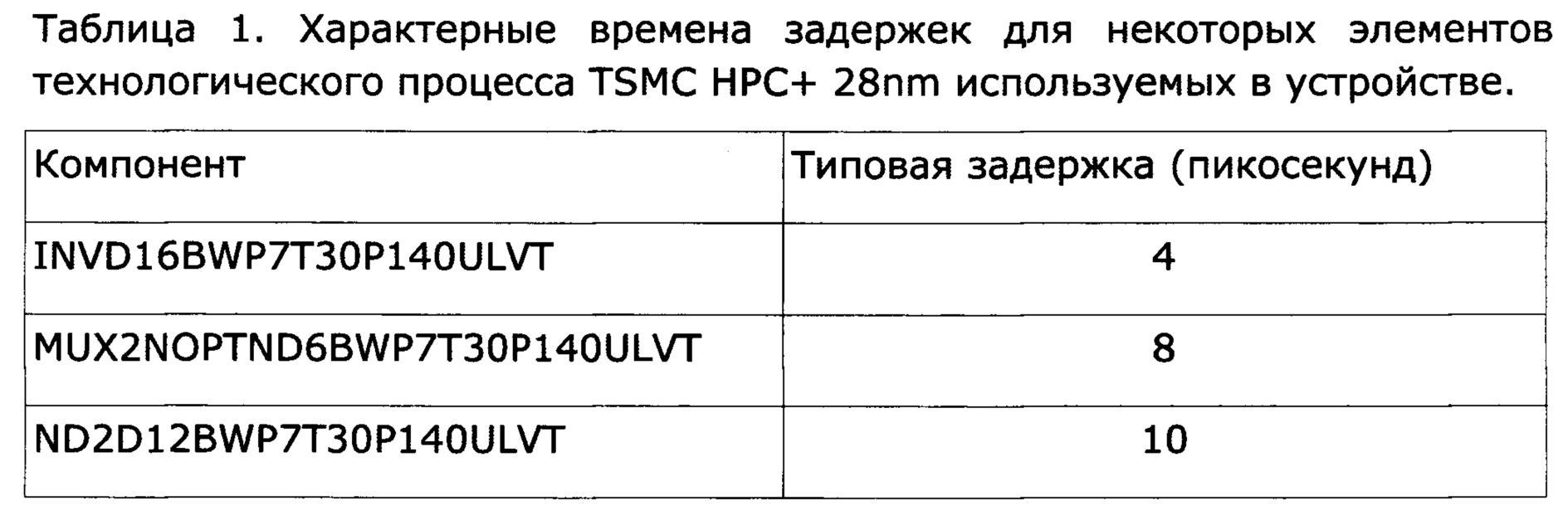

Для технологического процесса TSMC НРС+28nm с использованием библиотеки tcbn28hpcplusbwp7t30pl40ulvt в качестве инверторов были выбраны логические элементы INVD16BWP7T30P140ULVT, а в качестве двухканальных инвертирующих мультиплексоров логические элементы MUX2NOPTND6BWP7T30P140ULVT. Элемент логического AND 17, наряду с инверторами и мультиплексорами, также находится в замкнутом контуре кольцевого генератора, поэтому для него был выбран элемент с высоким быстродействием ND2D12BWP7T30P140ULVT. (Подробно см. [4]). На остальные блоки устройства, такие как счетчик выходных импульсов 6, управляющий компаратор 7, транслятор сигнала между частотными доменами 8, счетчик делитель импульсов опорной частоты 9, триггеры 13 (D1, D2 … DN) цифровой двунаправленной линии задержки 5, кроме проектных ограничений, никаких особых требований не накладывается, поэтому необходимость в структурном описании для них отпадает, оставляя возможность задать их свойства традиционным поведенческим RTL (register transfer level) способом, и удовлетворить всем требованиям дизайна встроенными средствами САПР (система автоматизированного проектирования).

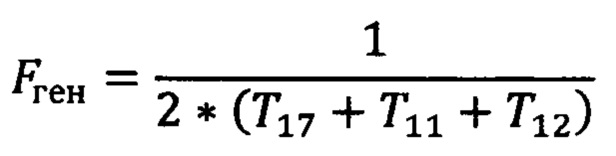

Частота следования импульсов в генераторах, построенных на кольцевых линиях задержки, равна обратной величине от удвоенной суммы задержек ее элементов (подробно см. [3]). Диапазон генерируемых частот предлагаемого генератора обусловлен соотношением минимальной и максимальной эффективных длин линии задержки 4 на логических элементах. Максимальная длина соответствует максимальной задержке и, соответственно, минимальной частоте генерации. Минимальная эффективная длина достигается при соответствующей коммутации двухканальных инвертирующих мультиплексоров 12 (X1, Х2 … XN+1) на цифровых логических элементах, а соответствующая ей максимальная частота равна обратной величине от удвоенной суммы задержек элементов логического AND 17, инвертора 11 (A1) и двухканального инвертирующего мультиплексора 12 (X1).

Fген - генерируемая частота

Т17 - задержка в элементе логического AND 17

Т11 - задержка в инверторе 11

Т12 - задержка в двухканальном инвертирующем мультиплексоре 12

Видно, что максимальная генерируемая частота для процесса TSMC НРС+28nm может достигать величины 20 ГГц (гигагерц), а поскольку минимальная частота генерации, как было показано выше, ограничена только общей длиной линии задержки, то теоретически достижимая полоса генерируемых частот фактически имеет то же значение - 20 ГГц, что соответствует чрезвычайно широкому максимально достижимому диапазону перестройки предлагаемого широкодиапазонного генератора импульсов с кратно дробной автоподстройкой частоты.

ПРИНЦИП ДЕЙСТВИЯ

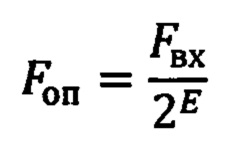

Принцип действия устройства основан на периодической направленной адаптации длины линии задержки (подробно см. [3]) на логических элементах 4 состоящей из инверторов 11 (A1, А2 … AN+1) на цифровых логических элементах общим числом N+1 и двухканальных инвертирующих мультиплексоров 12 (X1, Х2 … XN+1) на цифровых логических элементах общим числом N+1 путем соответствующей коммутации последних, что приводит к изменению общего количества активных элементов на пути распространения электрического сигнала, обеспечивая генерирование периодических импульсов необходимой частоты. Алгоритм адаптации основан на подсчете количества выходных импульсов широкодиапазонного генератора импульсов с кратно дробной автоподстройкой частоты за период сигнала поделенной опорной частоты приходящего со счетчика делителя импульсов опорной частоты 9 через транслятор сигнала между частотными доменами 8. Счетчик делитель импульсов опорной частоты 9 получает импульсы со входа опорной частоты 3 и делит их частоту на целочисленный коэффициент K численно равный двойке возведенной в степень Е (K=2Е), где Е представляет собой целочисленное значение двоичного кода поступающего с шины экспоненты масштабирующего коэффициента автоподстройки 16 (E1 … EP). В процессе этого деления и прохождения через транслятор сигнала между частотными доменами 8 образуются импульсы поделенной опорной частоты.

Fоп - частота поделенных опорных импульсов

Fвх - частота импульсов со входа опорной частоты 3

Е - целочисленное представление 16 (E1 … EP)

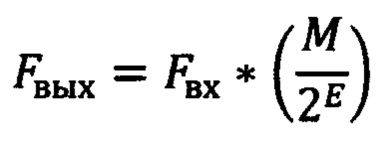

В процессе подсчета выходных импульсов поступающих на основной выход генератора 2 счетчиком выходных импульсов 6, на внутреннюю шину счета 14 (C1 … CL) поступает двоичный код С, целочисленное представление которого в момент активности импульса поделенной опорной частоты равно числу выходных импульсов генератора за период импульса поделенной опорной частоты. Двоичный код С со внутренней шины счета 14 (C1 … CL) поступает на первый вход управляющего компаратора 7, на второй вход которого поступает код мантиссы М представляющий собой целочисленное значение двоичного кода с шины мантиссы масштабирующего коэффициента автоподстройки 15 (M1 … ML). В моменты активности импульса поделенной опорной частоты управляющий компаратор 7 сравнивает значения кодов С и М и выдает на шину управления цифровой линией задержки 10 трехпозиционный код управления таким образом, что цифровая двунаправленная линия задержки 5 на триггерах 13 (D1, D2 … DN), задающая режим коммутации двухканальных инвертирующих мультиплексоров 12 (X1, Х2 … XN), либо не меняет своего значения, либо производит сдвиг на один бит влево, либо сдвиг на один бит вправо, что обеспечивает фактическое изменение состояния максимум одного триггера 13 из набора (D1, D2 … DN), что, соответственно, обеспечивает фактическое изменение направления коммутации максимум одного двухканального инвертирующего мультиплексора 12 из набора (X1, Х2 … XN). Данные изменения направления коммутации двухканальных инвертирующих мультиплексоров 12 (X1, Х2 … XN) приводят к адаптации времени распространения электрического сигнала линии задержки на логических элементах 4 на минимальный квант времени равный сумме задержек одного инвертора 11 из набора (A1, А2 … AN) плюс одного двухканального инвертирующего мультиплексора 12 из набора (X1, Х2 … XN). Данная перестройка происходит в моменты положительного фронта основного тактового сигнала CLK, или иначе, в моменты нулевой фазы, когда новый сформировавшийся положительный фронт импульса с линии задержки на логических элементах 4 поступает на основной выход генератора 2 и на второй вход элемента логического AND 17, в то время как уровень логического «0» от предыдущего полупериода уже полностью распространился по всем тем активным элементам линии задержки, которые на данный момент были замкнуты в кольцо генератора, как показано на чертеже жирными стрелками. Благодаря этому, на данный момент времени (момент нулевой фазы) все вышеупомянутые элементы замкнутого кольца имеют гарантированно стабильное логическое состояние, а двухканальные инвертирующие мультиплексоры 12 (X1, Х2 …), кроме всего прочего, еще и одинаковый логический уровень на обоих своих входах, что в случае их переключения ведет к сохранению логического уровня на их выходе. Данный факт приводит к возможности безопасной коммутации любого двухканального инвертирующего мультиплексора 12 (X1, Х2 …), примыкающего к границе вышеупомянутого кольца генерации, что в свою очередь обеспечивает гарантированное отсутствие импульсной помехи (глитча) на выходе генератора. На чертеже показано типовое состояние кольцевого генератора в моменты нулевой фазы, где стрелками обозначено направление коммутации мультиплексоров, а жирными стрелками распространение сигнала. Там же обозначено состояние триггеров 13 (D1, D2 … DN), которое всегда имеет вид, если смотреть на чертеже слева направо, непрерывной последовательности нулей со следующей за ними непрерывной последовательностью единиц (00…000111…11), вид которой обусловлен тем, что при сдвиге вправо, с левой стороны в цифровую двунаправленную линию задержки 5 всегда вдвигается логический "0", а при сдвиге влево, с правой стороны всегда вдвигается логическая "1". Производящаяся вышеописанная направленная адаптация под контролем управляющего компаратора 7, приводит к тому, что в устройстве генератора в целом на момент прихода импульса поделенной опорной частоты постоянно происходит попытка поддержания равенства кодов С и М, что эффективно соответствует поддержанию равенства поделенной на М выходной частоты генератора и поделенной на 2Е опорной частоты, что можно выразить формулой кратно дробного соотношения -

Fвх - частота выходных импульсов на основном выходе генератора 2

Fвх - частота импульсов со входа опорной частоты 3

М - целочисленное представление 15 (M1 … ML)

Е - целочисленное представление 16 (E1 … ЕР)

Коэффициент этого соотношения -  по своей сути представляет число с плавающей двоичной точкой, положение которой внутри двоичного представления мантиссы (M1 … ML) определяет целочисленное значение экспоненты (E1 … ЕР), что в свою очередь дает возможность использовать генератор импульсов не только в качестве умножителя, но и в качестве делителя опорной частоты. Также, в случае пропадания импульсов на входе опорной частоты 3, полностью перестает генерироваться импульс поделенной опорной частоты, что приводит к пропаданию источника событий для перестройки цифровой двунаправленной линии задержки 5. Соответственно, это приводит к отсутствию изменений коммутации двухканальных инвертирующих мультиплексоров 12 (X1, Х2 … XN), обеспечивая эффективное "запоминание" значения предыдущего периода генерации вплоть до момента возобновления подачи импульсов на входе опорной частоты 3, что в свою очередь ведет к снижению зависимости от их качества и увеличению общей помехоустойчивости описываемого широкодиапазонного генератора импульсов с кратно дробной автоподстройкой частоты.

по своей сути представляет число с плавающей двоичной точкой, положение которой внутри двоичного представления мантиссы (M1 … ML) определяет целочисленное значение экспоненты (E1 … ЕР), что в свою очередь дает возможность использовать генератор импульсов не только в качестве умножителя, но и в качестве делителя опорной частоты. Также, в случае пропадания импульсов на входе опорной частоты 3, полностью перестает генерироваться импульс поделенной опорной частоты, что приводит к пропаданию источника событий для перестройки цифровой двунаправленной линии задержки 5. Соответственно, это приводит к отсутствию изменений коммутации двухканальных инвертирующих мультиплексоров 12 (X1, Х2 … XN), обеспечивая эффективное "запоминание" значения предыдущего периода генерации вплоть до момента возобновления подачи импульсов на входе опорной частоты 3, что в свою очередь ведет к снижению зависимости от их качества и увеличению общей помехоустойчивости описываемого широкодиапазонного генератора импульсов с кратно дробной автоподстройкой частоты.

ОПИСАНИЕ ПРИМЕРОВ ОСУЩЕСТВЛЕНИЯ ИЗОБРЕТЕНИЯ

Предлагаемый широкодиапазонный генератор импульсов с кратно дробной автоподстройкой частоты может использоваться в составе цифровых многопроцессорных СБИС в качестве широкодиапазонного перестраиваемого генератора тактовых частот и может быть реализован на базе современных субмикронных технологических процессов. В качестве примера, было проведено проектирование данного генератора по цифровому маршруту на базе технологического процесса TSMC НРС+28nm с использованием библиотек tcbn28hpcplusbwp7t30p140ulvt и tcbn28hpcplusbwp7t30pl40. При помощи многократных симуляционных замеров были выбраны наиболее быстродействующие элементы: в качестве инверторов 11 (A1, А2 … AN+1) - INVD16BWP7T30P140ULVT, в качестве двухканальных инвертирующих мультиплексоров 12 (X1, Х2 … XN+1) - MUX2NOPTND6BWP7T30P140ULVT, и в качестве элемента логического AND 17 - ND2D12BWP7T30P140ULVT (подробно см. [4]).

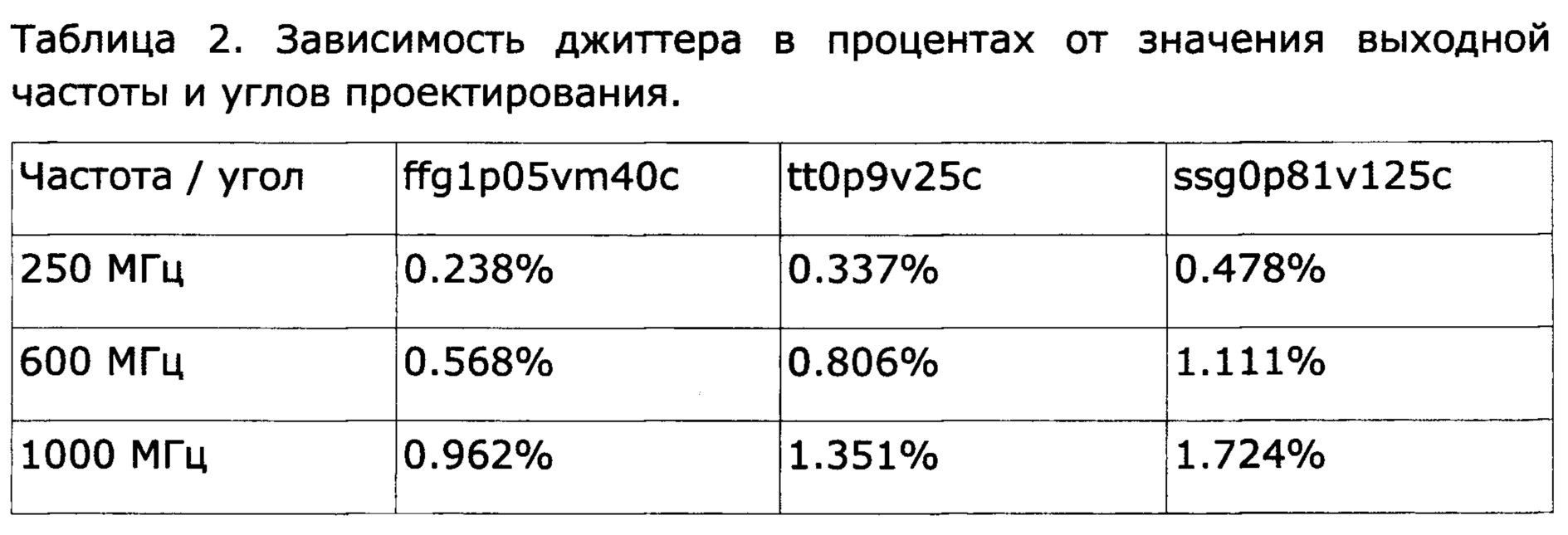

Дизайн был выполнен в гибридном стиле, где одна часть, отвечающая за кольцевой генератор, была задана прямым структурным описанием, в котором вышеуказанные компоненты представляющие линию задержки были соединены вручную, в то время как другая часть задана в виде традиционного поведенческого RTL (register transfer level) описания. Синтез производился в синтезаторе Cadence Genus, имплементация в САПР Cadence Innovus, симуляция в САПР (система автоматизированного проектирования) Mentor Modelsim. При длине кольцевой линии задержки равной 256, модуль генератора свободно разместился в прямоугольнике со сторонами 100 на 120 мкм. Разрядность мантиссы была выбрана равной 8 бит, экспоненты 3 бита. В процессе имплементации была произведена расстановка, разводка и оптимизация дизайна согласно проектным ограничениям. Последующая экстракция паразитов и моделирование средствами САПР показали полную работоспособность генератора в диапазоне перестройки выходных частот от 200 до 2000 МГц (мегагерц). Также были испытаны различные соотношения выходных и опорных частот, значений мантисс и экспонент и прочих параметров дизайна, в то время как переходных помех (глитчей) в выходных импульсах на всем протяжении моделирования не наблюдалось. Значение джиттера, или абсолютное отклонение выходной частоты от ее ожидания за конечное (большое) количество периодов, показало зависимость от различных факторов, а именно от абсолютного значения выходной частоты, от напряжения питания, от температуры и разброса технологических норм в процессе изготовления. В то же время, данные факторы никаким существенным образом не влияли на выходные значения частоты генерации по причине режима постоянной ее автоподстройки к внешней опорной частоте. В таблице 2 приведены полученные в результате моделирования имплементированного дизайна, характерные числа для выходного джиттера в процентах, и их зависимость от значения выходной частоты и углов проектирования.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемое устройство и его принцип действия решают поставленную задачу -создание широкодиапазонного генератора импульсов с кратно дробной автоподстройкой частоты и соответствует заявляемым техническим результатам, таким как - возможность легкой интеграции в составе СБИС на базе современных субмикронных технологических процессов, используя при этом только лишь цифровой маршрут проектирования без привлечения длительного и дорогостоящего аналогового маршрута, широкий диапазон перестройки генерируемых частот, возможность как умножения так и деления частоты входных опорных импульсов на произвольный переменный коэффициент, отсутствие в выходном сигнале импульсных помех (глитчей), а также близкая к идеальному меандру скважность выходных импульсов.

ЛИТЕРАТУРА

1. «ГЕНЕРАТОР ИМПУЛЬСОВ С АВТОПОДСТРОЙКОЙ ЧАСТОТЫ» RU 2260904 С1 МПК H03K 3/86 H03L 7/00 Чулков В.А.

2. «ГЕНЕРАТОР ИМПУЛЬСОВ С ЦИФРОВОЙ ПЕРЕСТРОЙКОЙ ПЕРИОДА» RU 2170490 С1 МПК НОЗК 5/14 H03K 5/156 H03L 7/00 Чулков В.А.

3. «Управляемые кольцевые генераторы импульсов в технике синхронизации» УДК 681.58 DOI 10.21685/2072-3059-2017-1-3 Чулков В.А.

4. «TCBN28HPCPLUSBWP7T30 P140ULVT TSMC N28HPC Standard Cell Library» Datasheet

Широкодиапазонный генератор импульсов с кратно дробной автоподстройкой частоты, содержащий линию задержки на логических элементах, вход опорной частоты и основной выход генератора, отличающийся тем, что линия задержки на логических элементах содержит набор инверторов (A, А … A) на цифровых логических элементах общим числом N+1 и набор двухканальных инвертирующих мультиплексоров (X, Х … X) на цифровых логических элементах общим числом N+1, при этом в устройство введены элемент логического AND, цифровая двунаправленная линия задержки на триггерах (D1, D … D) общим числом N, шина управления цифровой линией задержки, управляющий компаратор, вход сброса, входная шина мантиссы масштабирующего коэффициента автоподстройки (M … M), входная шина экспоненты масштабирующего коэффициента автоподстройки (E … Е), основной счетчик выходных импульсов с внутренней шиной счета (C … С), счетчик-делитель импульсов опорной частоты, транслятор сигнала между частотными доменами, где вход сброса подключен к входу сброса счетчика выходных импульсов, к входу сброса счетчика делителя импульсов опорной частоты, ко всем входам сбросов триггеров (D, D … D) цифровой двунаправленной линии задержки, к входу сброса транслятора сигнала между частотными доменами, а также к первому входу элемента логического AND, выход которого подключен к входу первого инвертора (A), причем второй вход элемента логического AND подключен к выходу первого двухканального инвертирующего мультиплексора (X) линии задержки на логических элементах, причем выход первого двухканального инвертирующего мультиплексора (X) подключен к основному выходу генератора, который также подключен ко всем тактовым входам триггеров (D, D … D), к тактовому входу транслятора сигнала между частотными доменами и тактовому входу счетчика выходных импульсов, выход которого через шину счета выходных импульсов (C … C) подключен к первому входу управляющего компаратора, ко второму входу которого подключена входная шина мантиссы масштабирующего коэффициента автоподстройки (M … M), при этом выход управляющего компаратора через шину управления цифровой линией задержки подключен к входам управления цифровой двунаправленной линии задержки, содержащей триггеры (D, D … D), соответствующие выходы которых подключены к соответствующим управляющим входам двухканальных инвертирующих мультиплексоров (X, Х … X), соединенных таким образом, что вторые информационные входы двухканальных инвертирующих мультиплексоров (X, Х … X) соединены с выходами двухканальных инвертирующих мультиплексоров (Х, Х … X) соответственно, а первые информационные входы двухканальных инвертирующих мультиплексоров (X, Х … X) соединены с соответствующими выходами инверторов (A, А … A), причем сами выходы инверторов (A, А … A) подключены к соответствующим входам инверторов (А, А … A), при этом вход опорной частоты и шина экспоненты масштабирующего коэффициента автоподстройки (E … Е) подключены к соответствующим входам счетчика-делителя импульсов опорной частоты, выход которого подключен к входу транслятора сигнала между частотными доменами, причем выход транслятора сигнала между частотными доменами подключен к счетчику выходных импульсов и управляющему компаратору.