Результат интеллектуальной деятельности: УСТРОЙСТВО СЛОЖЕНИЯ-ВЫЧИТАНИЯ ЧИСЕЛ ДЛЯ ЦИФРО-СИГНАЛЬНОГО ПРОЦЕССОРА

Вид РИД

Изобретение

Изобретение относится к устройствам обработки цифровых данных и может использоваться в качестве IP-блока для цифро-сигнальных процессоров.

Известны устройства для выполнения различных арифметических операций в формате чисел с плавающей запятой.

Из патента США US5487022 известна нормализация экспоненциальной части числа средствами, использующими дешифраторы, память, логические элементы, мультиплексоры. Средства реализуются в виде комплексного устройства, характеризующегося высокими аппаратными затратами.

Известно устройство операционного умножения с плавающей запятой (заявка на патент США US20150347089). Для выполнения операции умножения в устройство введены блоки нормализации чисел, избыточно выполняющие эквивалентные функции, что усложняет конструкцию.

Патент США US6516332 раскрывает устройство для выполнения математических операций над числами в формате с плавающей точкой. Это устройство позволяет осуществлять над числами операции сложения, вычитания, умножения, деления, и построено на базе процессора для операций с плавающей точкой. Устройство содержит микроконтроллер, блок памяти микроконтроллера, вентильную матрицу, множество модулей оператора с плавающей точкой для выполнения математических операций сложения, вычитания, умножения и деления, каждый из которых включает сумматор, вычитающее устройство, множитель и делитель, первый мультиплексор для получения данных от сумматора и вычитающего устройства, второй мультиплексор для получения данных от умножителя и делителя, и третий мультиплексор для получения соответствующих данных от первого и второго мультиплексоров. Недостатком устройства является то, что фиксированная величина (разрядность) мантиссы и экспоненты ограничивают область его применения, а само оно предназначено для управления моторами.

Наиболее близким аналогом заявленного изобретения является устройство с плавающей точкой для сложения-вычитания согласно патенту США US5568412. Это устройство включает схему выравнивания, схему сложения-вычитания и округления и схему нормализации. Схема выравнивания выравнивает части первых и вторых операндов, основанных на различии их образцов. Схема сложения-вычитания и округления выполняет, по крайней мере, два сложения-вычитания между выровненными частями части первых и вторых операндов и выборочно производит значение результата одного из округленных результатов сложения/вычитания частей первых и вторых операндов. Схема нормализации нормализует округленный от значения результат, чтобы произвести конечный результат сложения/вычитания частей. Указанные три схемы устройства построены на базе компаратора, первого и второго сумматора, схемы выравнивания, схем подкачки, первого логического элемента «исключающее ИЛИ», логического элемента «И», множества логических элементов «ИЛИ», логической схемы полусумматора, двух мультиплексоров, счетчика начального нуля, преобразователя. Устройство требует синхронного обмена данными между его функциональными узлами и имеет недостаточное быстродействие.

Как и предыдущие устройства, устройство-аналог характеризуется высокими аппаратными затратами.

Задачей настоящего изобретения является устранение недостатков известных устройств сложения-вычитания чисел, улучшение их технико-эксплуатационных характеристик.

Технический результат заключается в упрощении конструкции и повышении быстродействия устройства сложения-вычитания чисел при асинхронном обмене данными.

Поставленная задача решается, а заявленный технический результат достигается в устройстве сложения-вычитания чисел для цифро-сигнального процессора, содержащем первый блок условного выбора младшей части мантисс, второй блок условного выбора старшей части мантисс, блок выбора максимума экспоненциальной части двух операндов, блок разницы экспонент, блок абсолютной величины разницы, узел прибавления единицы, блок сдвига мантиссы, первый блок формирования величины насыщения, второй блок формирования величины насыщения, блок формирования инверсного кода, блок вычитания двойного формата, первый, второй и третий блок условного перехода. Первый вход первого блока условного выбора младшей части мантисс служит для поступления младшего разряда мантиссы первого числа, второй его вход – для поступления младшего разряда мантиссы второго числа, третий его вход – для поступления экспоненты первого числа, четвертый его вход – для поступления экспоненты второго числа. Первый вход второго блока условного выбора старшей части мантиссы служит для поступления старшей части мантиссы первого числа, а второй его вход – для поступления старшей части мантиссы второго числа. Третий вход и четвертый вход первого блока условного выбора младшей части мантисс соединен соответственно с третьим входом и четвертым входом второго блока условного выбора старшей части мантисс. Третий вход и четвертый вход первого блока условного выбора младшей части мантисс соединен соответственно с первым входом и вторым входом блока выбора максимума экспоненциальной части двух операндов. Третий вход и четвертый вход первого блока условного выбора младшей части мантисс соединен соответственно с первым входом и вторым входом блока разницы экспонент. Первый выход первого блока условного выбора младшей части мантисс соединен с первыми входами первого блока и второго блока формирования величины насыщения. Второй выход первого блока условного выбора младшей части мантисс соединен с первым входом блока сдвига мантиссы. Первый выход второго блока условного выбора младшей части мантисс соединен соответственно со вторым входом первого блока формирования величины насыщения и вторым входом второго блока формирования величины насыщения. Второй выход второго блока условного выбора младшей части мантисс соединен со вторым входом блока сдвига мантиссы. Выход блока выбора максимума экспоненциальной части двух операндов соединен с входом узла прибавления единицы и первым входом третьего блока условного перехода. Выход узла прибавления единицы соединен со вторым входом третьего блока условного перехода. Выход блока разницы экспонент соединен с входом блока абсолютной величины разницы, выход которого соединен с третьим входом блока сдвига мантиссы. Первый выход блока сдвига мантиссы соединен с третьими входами первого и второго блоков формирования величины насыщения. Второй выход блока сдвига мантиссы соединен с четвертыми входами первого и второго блоков формирования величины насыщения. Первый выход первого блока формирования величины насыщения соединен с первым входом блока формирования инверсного кода и первым входом второго блока условного перехода. Второй выход первого блока формирования величины насыщения соединен со вторым входом блока формирования инверсного кода, с первым и третьим входами первого блока условного перехода, с третьим входом второго блока условного перехода и третьим входом третьего блока условного перехода. Выход второго блока формирования величины насыщения соединен с четвертыми входами первого, второго и третьего блоков условного перехода. Первый и второй выходы блока формирования инверсного кода соответственно соединены с первым и вторым входами блока вычитания двойного формата, первый выход которого соединен со вторым входом второго блока условного перехода, а второй выход – со вторым входом первого блока условного перехода. Выходы первого, второго и третьего блоков условного перехода служат выходами соответственно мантиссы старших разрядов, мантиссы младших разрядов и экспоненты сложения-вычитания чисел.

Преимущества, а также особенности настоящего изобретения поясняются с помощью варианта его выполнения со ссылками на фигуры.

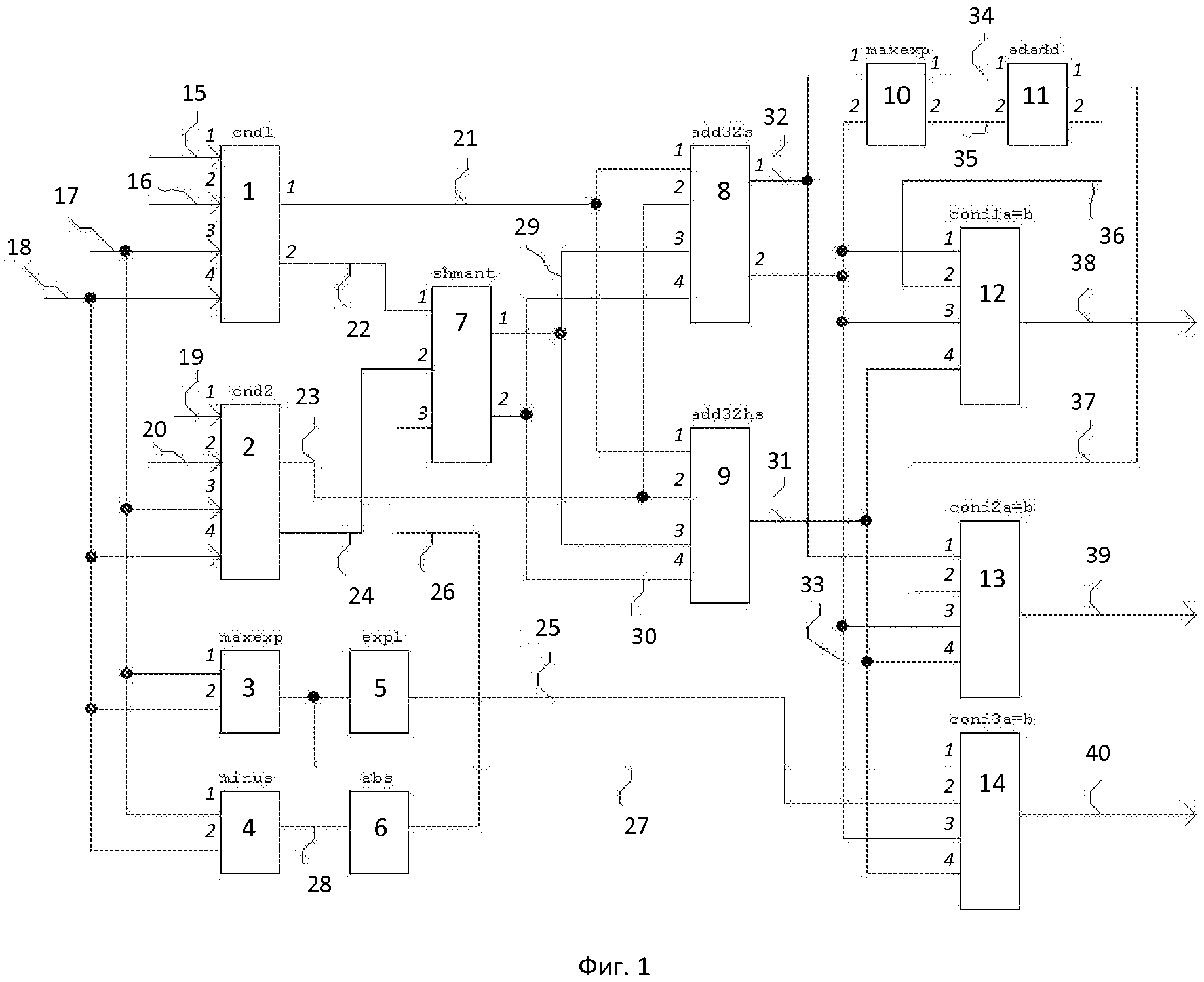

Фиг. 1 изображает функциональную схему заявленного устройства;

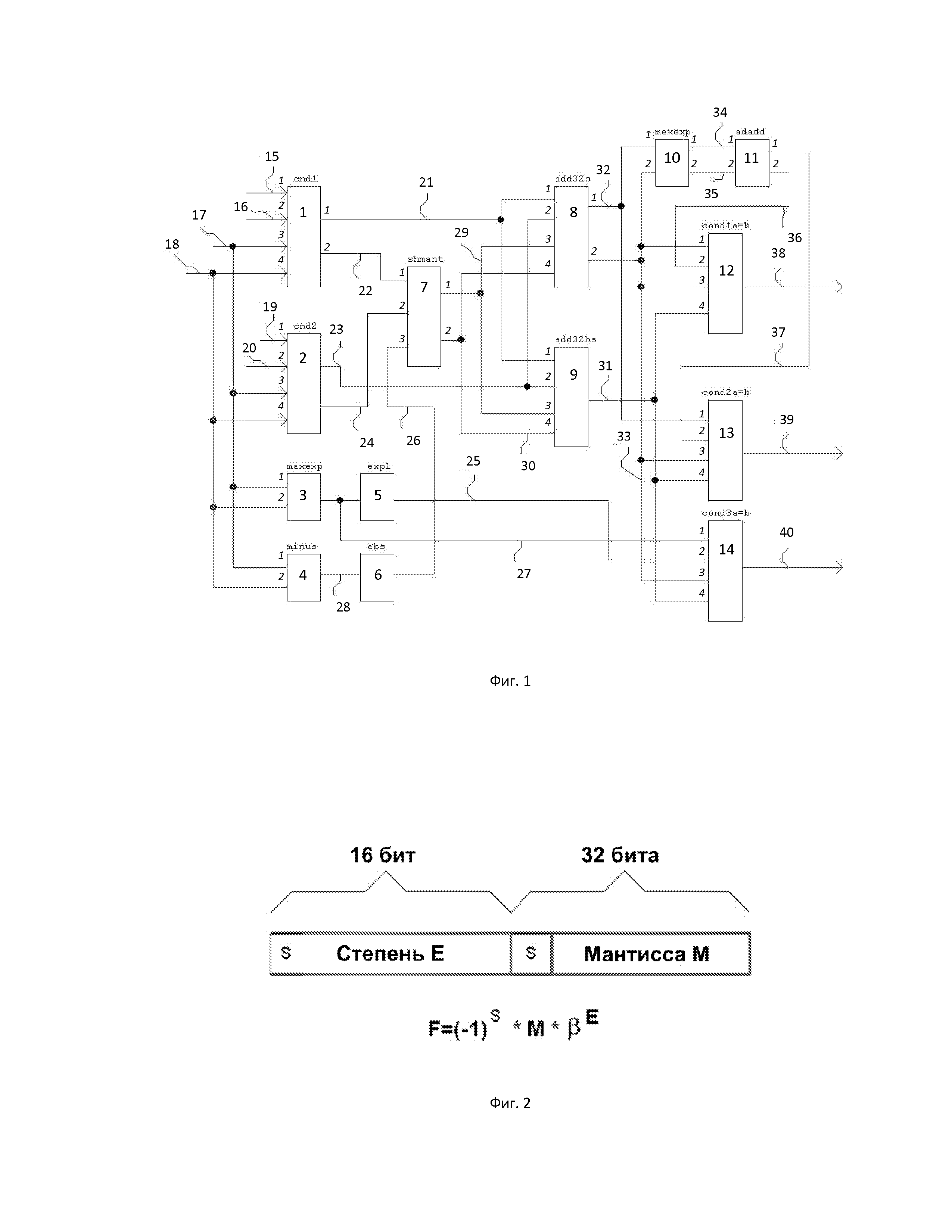

На фиг. 2 приведен общий формат числа с плавающей запятой.

На фиг. 1 обозначены следующие позиции:

1 – первый блок условного выбора младшей части мантисс

2 – второй блок условного выбора старшей части мантисс

3 – блок выбора максимума экспоненциальной части двух операндов

4 – блок разницы экспонент

5 – блок абсолютной величины разницы

6 – узел прибавления единицы

7 – блок сдвига мантиссы

8 – первый блок формирования величины насыщения

9 – второй блок формирования величины насыщения

10 – блок формирования инверсного кода

11 – блок вычитания двойного формата

12, 13, 14 – соответственно первый, второй и третий блоки условного перехода

15, 16, 17, 18 – входы (входные шины) данных чисел

19–37 – шины соединений

38, 39, 40 – выходы (выходные шины) данных чисел.

Словарь терминов, использованных в описании и на фигурах:

Add – сложение

Cond – условие

Exp – экспонента

Mant – мантисса

Shift – операция сдвига числа

Sub – вычитание

Cnd1- блок условий 1

Cnd2- блок условий 2

Shmant – блок сдвига мантиссы

Maxexp –максимальная величина экспоненты

Exp1 – блок формирования абсолютной величины экспоненты результата

FP – формат чисел с плавающей точкой

IP-блок (ай-пи-блок) – законченное функциональное устройство

Minus – минус или вычитание.

Устройство сложения-вычитания для процессора (фиг. 1) содержит первый блок 1 условного выбора младшей части мантисс, второй блок 2 условного выбора старшей части мантисс, блок 3 выбора максимума экспоненциальной части двух операндов, блок 4 разницы экспонент, блок 5 абсолютной величины разницы, узел 6 прибавления единицы, блок 7 сдвига мантиссы, первый блок 8 формирования величины насыщения, второй блок 9 формирования величины насыщения, блок 10 формирования инверсного кода, блок 11 вычитания двойного формата, первый блок 12 условного перехода, второй блок 13 условного перехода и третий блок 14 условного перехода. Первый вход 15 первого блока 1 условного выбора младшей части мантисс служит для поступления младшего разряда мантиссы первого числа, второй его вход 16 – для поступления младшего разряда мантиссы второго числа, третий его вход 17 – для поступления экспоненты первого числа, четвертый его вход 18 – для поступления экспоненты второго числа. Первый вход 19 второго блока 2 условного выбора старшей части мантиссы служит для поступления старшей части мантиссы первого числа, а второй его вход 20 – для поступления старшей части мантиссы второго числа. Третий вход 17 и четвертый вход 18 первого блока 1 условного выбора младшей части мантисс соединен соответственно с третьим входом и с четвертым входом второго блока 2 условного выбора старшей части мантисс. Третий вход 17 и четвертый вход 18 первого блока 1 условного выбора младшей части мантисс соединен соответственно с первым входом и со вторым входом блока 3 выбора максимума экспоненциальной части двух операндов. Третий вход 17 и четвертый вход 18 первого блока 1 условного выбора младшей части мантисс соединен соответственно с первым входом и со вторым входом блока 4 разницы экспонент. Первый выход первого блока 1 условного выбора младшей части мантисс соединен с первыми входами первого блока 8 и второго блока 9 формирования величины насыщения. Второй выход первого блока 1 условного выбора младшей части мантисс соединен с первым входом блока 7 сдвига мантиссы. Первый выход второго блока 2 условного выбора младшей части мантисс соединен соответственно со вторым входом первого блока 8 формирования величины насыщения и со вторым входом второго блока 9 формирования величины насыщения. Второй выход второго блока 2 условного выбора старшей части мантисс соединен со вторым входом блока 7 сдвига мантиссы. Выход блока 3 выбора максимума экспоненциальной части двух операндов соединен с входом узла 6 прибавления единицы и с первым входом третьего блока 14 условного перехода. Выход узла 6 прибавления единицы соединен со вторым входом третьего блока 14 условного перехода. Выход блока 4 разницы экспонент соединен с входом блока 5 абсолютной величины разницы, выход которого соединен с третьим входом блока 7 сдвига мантиссы. Первый выход блока 7 сдвига мантиссы соединен с третьими входами первого и второго блоков 8, 9 формирования величины насыщения, второй выход блока 7 сдвига мантиссы соединен с четвертыми входами первого и второго блоков 8, 9 формирования величины насыщения. Первый выход первого блока 8 формирования величины насыщения соединен с первым входом блока 10 формирования инверсного кода и с первым входом второго блока 13 условного перехода. Второй выход первого блока 8 формирования величины насыщения соединен со вторым входом блока 10 формирования инверсного кода, с первым и с третьим входом первого блока 12 условного перехода, с третьим входом второго блока 13 условного перехода и с третьим входом третьего блока 14 условного перехода. Выход второго блока 9 формирования величины насыщения соединен с четвертыми входами первого блока 12 условного перехода, второго блока 13 условного перехода и третьего 14 блока условного перехода. Первый и второй выходы блока 10 формирования инверсного кода соответственно соединены с первым и вторым входами блока 11 вычитания двойного формата, первый выход которого соединен со вторым входом второго блока 13 условного перехода, а второй выход – со вторым входом первого блока 12 условного перехода. Выходы 38, 39, 40 соответственно первого блока 12 условного перехода, второго блока 13 условного перехода и третьего блока 14 условного перехода служат выходами соответственно мантиссы старших разрядов, мантиссы младших разрядов и экспоненты сложения-вычитания чисел.

Заявленное устройство работает следующим образом.

На входы 15, 16, 17, 18, 19, 20 поступают сигналы мантисс (старших и младших разрядов) и экспонент двух операндов.

Производимая операция в заявленном устройстве – сложение или вычитание операндов. В отличие от ближайшего аналога, для осуществления этих операций производятся вычисления в зависимости от состояния на шинах соединений 29 и 30 только в первом и втором блоках 8, 9 формирования величины насыщения, второй блок 9 формирования величины насыщения блоках 8 и 9 (для сложения или вычитания).

Для корректного выполнения операций необходимо согласовать экспоненциальные части двух операндов. В этой связи эти функции более комплексные для таких форматов, как сложение и вычитание, чем для выполнения операции умножения. Согласование экспоненциальных частей операндов производится блоком 3 выбора максимума экспоненциальной части двух операндов, блоком 4 разницы экспонент, блоком 5 абсолютной величины разницы, узлом 6 прибавления единицы.

Блок 1 условного выбора младшей части мантиссы предназначен для формирования на первом и втором выходах или на втором и первом выходах соответственно первого и второго операндов (мантиссы младшей части операнда) в зависимости от того, чья экспоненциальная часть больше. Это работает как коммутатор с условным переключением. Аналогично назначение для блока 2 условного выбора мантиссы (старшей части). Блок 3 максимума экспоненциальной части операндов предназначен для сравнения этих величин и выбора максимальной части из двух экспонент. Блок 4 формирует разницу экспонент двух операндов (exp1 - exp2), и далее блок 6 формирует абсолютную величину этого значения. Блок 7 сдвига мантиссы обеспечивает программируемый сдвиг мантиссы (в совокупности старшей и младшей частей) на то количество битов, которое поступает с выхода блока 6. Блоки 8 и 9 формирования величин насыщения предназначены для определения максимальной величины мантиссы, если она при операциях сдвига превышает максимальную величину, например, 1111…1. Первый и второй блоки условного перехода 12 и 13 предназначены для формирования финальной величины мантиссы (старшей и младшей частей). Третий блок условного перехода 14 предназначен для финального формирования экспоненциальной части результата.

По шине 25 максимальная величина экспоненты двух операндов, увеличенная на 1 (при необходимости нормализации) поступает второй вход блока 14 условного перехода. При этом на первый вход блока 14 условного перехода от выхода блока 3 выбора максимума экспоненциальной части двух операндов поступает максимальная величина экспоненты без модернизации (например, 23 и 25 – из них выбирается 25). В блоке 14 осуществляется выбор между указанными двумя величинами в зависимости от сигналов на шинах 31 и 33. Если эти сигналы равны (нормализации не требуется), то на выход 40 передается экспонента, сформированная на шине 27, иначе поступает информация с шины 25. На выходах 38 и 39 формируется старшая и младшая части мантиссы результата. Мантисса представляет собой 32 разрядное слово, соответственно по шине 16 разрядов.

Общий формат F числа с плавающей запятой представлен на фиг. 2:

F = (-1)S·M·βE,

где S – знак числа: S=0 – положительное число, S=1 – отрицательное число; M – мантисса – дробная часть числа; β – базовая часть экспоненты; Е – степень экспоненты.

На шинах 21, 22, 23 и 24 формируются младшие и старшие составляющие мантисс в зависимости от величин экспоненты поступающих операндов, например, с входа 15 – на шину 21 или шину 22 и с входа 16 – на шину 22 или шину 21; аналогично с входа 19 – на шину 23 или шину 24, и с входа 20 – на шину 24 или шину 23. Таким образом, в зависимости от значений чисел (что больше или меньше) происходит передача чисел на соответствующие выходы – шины 21 или 22, и 23 или 24. Величина сдвига 32 разрядной мантиссы осуществляется в блоке 7 сдвига и определяется абсолютной величиной разницы экспонент (например, разница 4 означает сдвиг на два разряда – 22=4), поступающей по шине 26. При этом диапазон величин, который обеспечивает данный формат, приведен ниже:

Minimum (абсолютная величина) = 2,328306436538696·10-10 (исключая “0”);

Maximum (абсолютная величина) = 232768;

Maximum отрицательной величины по абсолютному значению = -2-65536·2-31;

Minimum = -232768.

В первом и втором блоках 8, 9 формирования величины насыщения выполняется операция сложения или вычитания в зависимости от кода команды. При этом формируются величины с учетом максимальной величины – saturation (насыщенность): например, максимальное значение положительного числа или максимальное значение абсолютной величины отрицательного числа – соответственно 0.1111…1 или 1.0000…0.

Для формирования отрицательного числа в устройство включены блок 10 инверсного кода и вычитатель 11 двойного формата, в котором из числа 7fff ffff (гексагональное представление числа) вычитается инверсная величина выбранной мантиссы, где далее блоки 12 и 13 условного перехода в зависимости от состояния сигналов («0» или «1») на шинах 33, 36 и 32, 37 для каждого из них формируют выходную мантиссу результата.

Устройство построено по асинхронному принципу, поэтому временные диаграммы и критические цепи (при разбросе параметров) не влияют на его работоспособность. Устройство полностью автономно и может применяться как IP-блок для цифро-сигнальных процессоров с фиксированной запятой, в которых, например, необходимо провести операции с плавающей запятой. Заявленный технический результат, заключающийся, в том числе, в упрощении конструкции и повышении быстродействия при асинхронном обмене данными, достигается за счет применения новой функциональной схемы, представленной на фиг. 1, с новым принципом работы.

В конкретной приведенной функциональной схеме каждый блок оперирует в формате 16- или 32-разряда. Автономность блоков может обеспечиваться также наличием буфера FIFO (в частности, малого размера) на входе и выходе схемы. Размер этой памяти определяется общей структурой цифро-сигнальных процессоров и выбором системы команд. Глубина FIFO, может быть, например, 8–16 слов. В целом, предложенное техническое решение позволяет эффективно реализовать функциональные требования к цифро-сигнальным процессам. Буферная память (память буфера) по желанию разработчика позволяет хранить последовательность входных данных и результата зависимости от реализуемого устройства.

Наиболее успешно заявленное устройство сложения-вычитания чисел для цифро-сигнального процессора промышленно применимо в IP-блоках цифро-сигнальных процессоров с фиксированной запятой, в которых необходимо провести операции с плавающей запятой для различной аппаратуры обработки цифровых данных.