Результат интеллектуальной деятельности: СПОСОБ ПОСТОЯННОГО ПОЭЛЕМЕНТНОГО ДУБЛИРОВАНИЯ В ЦИФРОВЫХ ТРАНЗИСТОРНЫХ МИКРОСХЕМАХ

Вид РИД

Изобретение

Область техники, к которой относится изобретение

Изобретение относится к области цифровой вычислительной техники и автоматики, а именно к способам повышения надежности цифровых систем, работающих в условиях радиации, и более точно, к способам постоянного поэлементного дублирования в цифровых транзисторных микросхемах, находящихся под воздействием частиц излучения. Эти микросхемы состоят из транзисторных логических элементов. В данном изобретении под элементами этих микросхем понимаются логические элементы, а под поэлементным дублированием понимается дублирование логических элементов. Под постоянным дублированием понимается дублирование, при котором дублируемые элементы постоянно работают одновременно.

Изобретение может найти применение в цифровых системах, которые подвергаются воздействию радиации и в первую очередь воздействию потока высокоэнергетических частиц. При этом важные области применения предлагаемого изобретения представляют нано- и микро- цифровые системы.

Уровень техники

Известен способ постоянного поэлементного дублирования в дискретных электронных системах, или в частности, в цифровых транзисторных микросхемах, при котором для каждого транзисторного логического элемента устанавливают идентичный ему дублирующий логический элемент, объединяют одноименные входы дублирующих друг друга логических элементов, в качестве дублирующих элементов используют логические элементы, не имеющие памяти, располагают дублирующие друг друга логические элементы на расстоянии между ними, превышающем размер области повреждения микросхемы от одной частицы излучения, попадающей в нее, и объединяют одноименные выходы дублирующих друг друга логических элементов, образуя пары дублирующих друг друга элементов, каждая из которых представляет дублированный логический элемент (см. патент RU 2475820 от 10.08.2011 г., «Способ постоянного поэлементного дублирования в дискретных электронных системах (варианты)», вариант 1 (пункты 1-3 формулы изобретения), авторы - Александров П.А., Жук В.И., Литвинов В.Л., патентообладатель - Национальный исследовательский центр «Курчатовский институт».

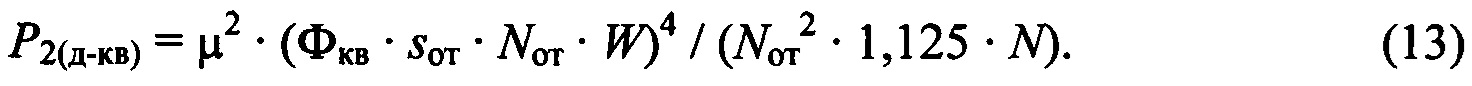

В этом патенте дана оценка вероятности отказа микросхемы с дублированием логических элементов при ее облучении:

P2=P12/N,

где

Р2 - вероятность отказа облучаемой микросхемы с дублированием логических элементов;

Р1 - вероятность отказа нерезвированной микросхемы при отказе любого элемента в ней под действием одной частицы облучения;

N - количество пар дублирующих друг друга элементов в микросхеме.

Этот способ был затем исследован в ряде статей. В статье П.А. Александрова, В.В. Бударагина, В.И. Жука и В.Л. Литвинова «Отказоустойчивость покомпонентно дублированной микросхемы при облучении» («Нано- и микросистемная техника», 2015, №3, С. 10-23, на русском и англ.) представлен более подробный вывод указанной выше формулы для Р2, приведенной в нашем патенте RU 2475820. В статье П.А. Александрова, B. В. Бударагина, В.И. Жука, В.Л. Литвинова и С.Е. Стельмак «Сравнительные оценки отказоустойчивости мажоритарно резервированных и покомпонентно дублированных микросхем при облучении» («Нано- и микросистемная техника», 2016, Том 18, №3, C. 176-192, на русском и англ.) приведено уточнение (1.12) формулы для Р2, приведенной в указанном патенте при N» 2:

где Рп - вероятность отказа одного дублирующего элемента из множества непарных дублирующих элементов, т.е. дублирующих элементов, не составляющих дублированного элемента ни с одним дублирующим элементом из этого множества; другими словами Рп - аналог вероятности Р1, приведенной в указанном патенте.

В статье П.А. Александрова, В.В. Бударагина, Горемыкина A.M., В.И. Жука и В.Л. Литвинова «О построении дублированных логических элементов для повышения отказоустойчивости микросхем при облучении» («Нано- и микросистемная техника», 2016, Том 18, № 4, С. 239-256, на русском и англ.) на рис. 2 (С. 243) приведен пример принципиальной схемы двухвходового дублированного элемента «ИЛИ-НЕ» состоящего из двух двухвходовых дублирующих (или, иначе говоря, дублируемых) логических элементов «ИЛИ-НЕ», в каждом из которых выходной каскад выполнен из диода D и резистора R2.

Прототипом настоящего изобретения является способ постоянного поэлементного дублирования в цифровых транзисторных микросхемах, описанный в нашем патенте RU 2475820 от 2011 г. и исследованный в наших последующих статьях [1-5]. Недостаток этого прототипа состоит в том, что хотя он и позволяет существенно снизить вероятность отказа дублированной микросхемы по сравнению с нерезервированной микросхемой при их облучении, но во многих случаях не обеспечивает требуемой значительно более высокой отказоустойчивости микросхем при облучении.

Известен также совершенно иной способ повышения отказоустойчивости транзисторных микросхем, состоящий в том, что вместо одиночного транзистора используют учетверенную транзисторную структуру, которую называют N2-транзисторной структурой при N=2, а также учетверенным или квадрированным транзистором (см. статью Aiman Н. Maleh, Bashir М. Al-Hashimir, Aissa Melouki, Farhan Khan. Defect Tolerant N2-Transistor Structure for Reliable Nanoelectronic Designs. - IET Computers & Digital Techniques, Volume 3, Issue 6, November 2009. pp. 570-580, http://eprints.soton.ac.uk/267678/1/IET_DefectTolerantStrucureNanoelectronics.pdf

Каждый квадрированный транзистор представляет четверку соединенных между собой параллельно и последовательно одиночных транзисторов, объединенные входы А которых являются входом квадрированного транзистора, а объединенные одноименные свободные выходы одиночных транзисторов являются выходами квадрированного транзистора.

Квадрированный транзистор выполняют либо в виде двух последовательно соединенных каскадов, каждый из которых состоит из параллельно соединенных между собой двух одиночных транзисторов со входами А, реализуя логическую функцию (А+А)(А+А), либо в виде двух параллельных цепочек последовательно соединенных между собой двух одиночных транзисторов со входами А, реализуя логическую функцию АА+АА. Здесь знак + означает логическое сложение, а под умножением имеется в виду логическое умножение.

В литературе не рассматривается отказоустойчивость микросхемы из квадрированных транзисторов, работающей под действием облучения.

Можно показать, что по сравнению со способом-прототипом, основанным на дублировании логических элементов, способ построения микросхемы на квадрированных транзисторах без дублирования логических элементов, может снизить вероятность отказа микросхемы при ее облучении на один - два порядка. Но существует множество случаев, когда требуется более существенное снижение вероятности отказа микросхемы.

Раскрытие (сущность) изобретения

Задачей предлагаемого изобретения является разработка такого способа постоянного поэлементного резервирования в нано- и микро- цифровых транзисторных микросхемах, который бы обеспечил технический результат в виде существенного повышения отказоустойчивости микросхем при воздействии на них излучения и в том числе потока высокоэнергетических частиц.

Этот технический результат достигается благодаря тому, что в способе постоянного поэлементного дублирования в цифровых транзисторных микросхемах, при котором для каждого транзисторного логического элемента устанавливают идентичный ему дублирующий логический элемент, объединяют одноименные входы дублирующих друг друга логических элементов, в качестве дублирующих элементов используют логические элементы, не имеющие памяти, располагают дублирующие друг друга логические элементы на расстоянии между ними, превышающем размер области повреждения микросхемы от одной частицы излучения, попадающей в нее, и объединяют одноименные выходы дублирующих друг друга логических элементов, образуя пары дублирующих друг друга элементов, каждая из которых представляет дублированный логический элемент, каждый входящий в дублирующие логические элементы транзистор выполняют в виде квадрированного транзистора, представляющего четверку соединенных между собой параллельно и последовательно одиночных транзисторов, объединенные входы которых являются входом квадрированного транзистора, а объединенные одноименные свободные выходы одиночных транзисторов являются выходами квадрированного транзистора. При этом квадрированный транзистор выполняют выполняют в виде двух последовательно соединенных каскадов, каждый из которых состоит из параллельно соединенных между собой двух одиночных транзисторов, или в виде двух параллельных цепочек последовательно соединенных между собой двух одиночных транзисторов.

Краткое описание чертежей

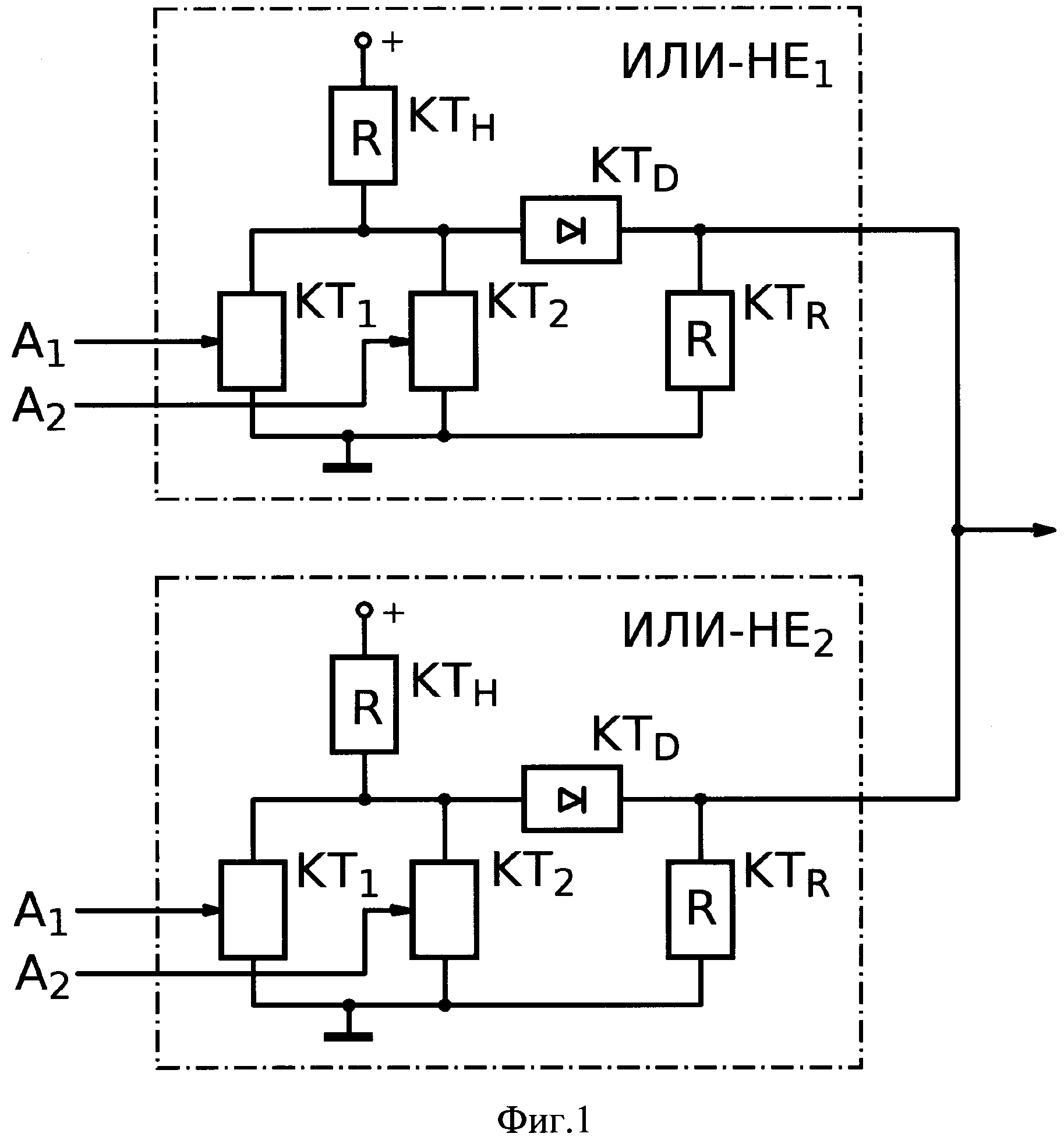

На фиг. 1 в качестве примера показана схема двухвходового дублированного элемента ИЛИ-НЕ, выполненного на квадрированных транзисторах.

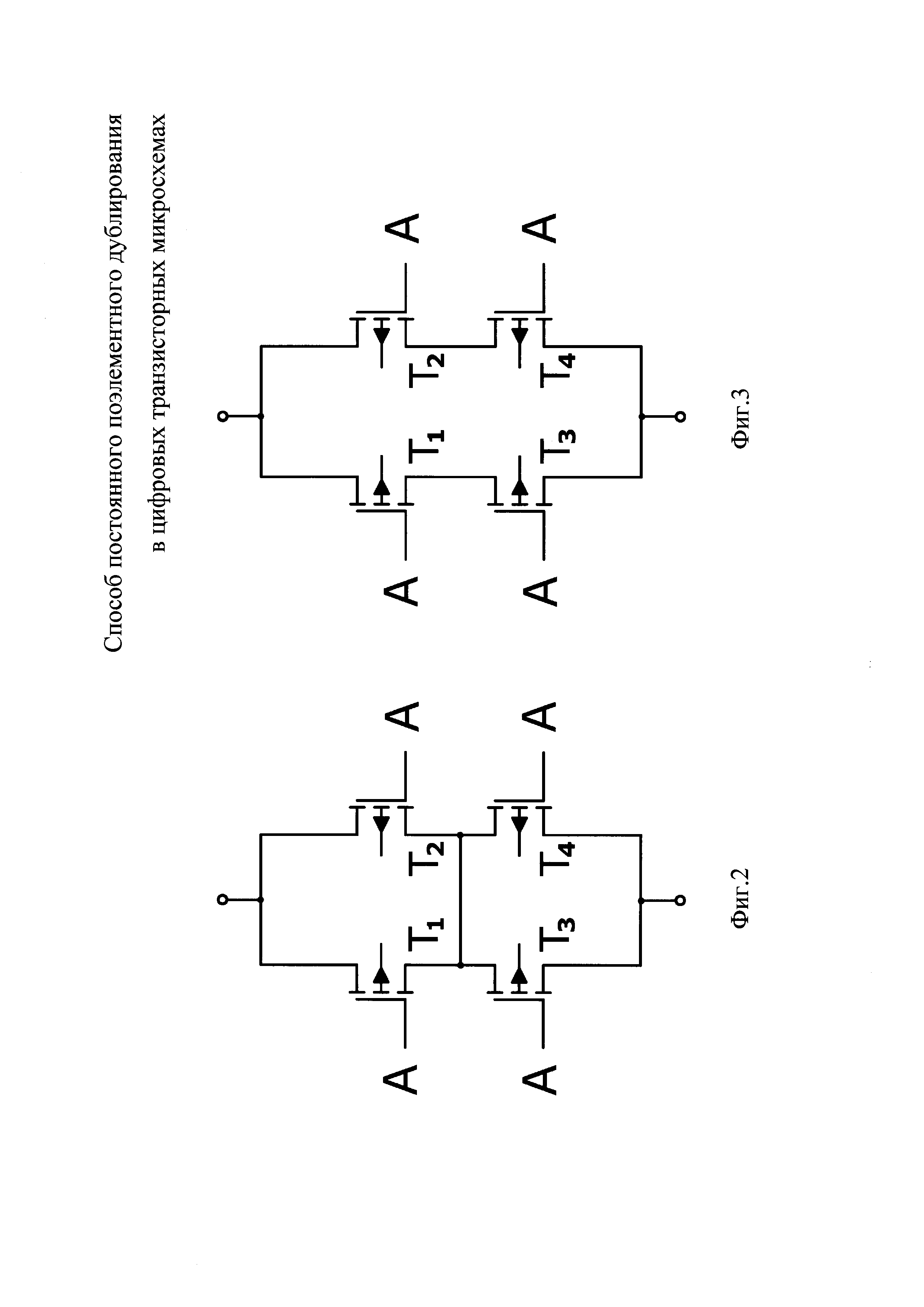

На фиг. 2 показана схема квадрированного транзистора, построенного на одиночных полевых транзисторах и выполненного в виде двух последовательно соединенных каскадов, каждый из которых состоит из параллельно соединенных между собой двух одиночных транзисторов.

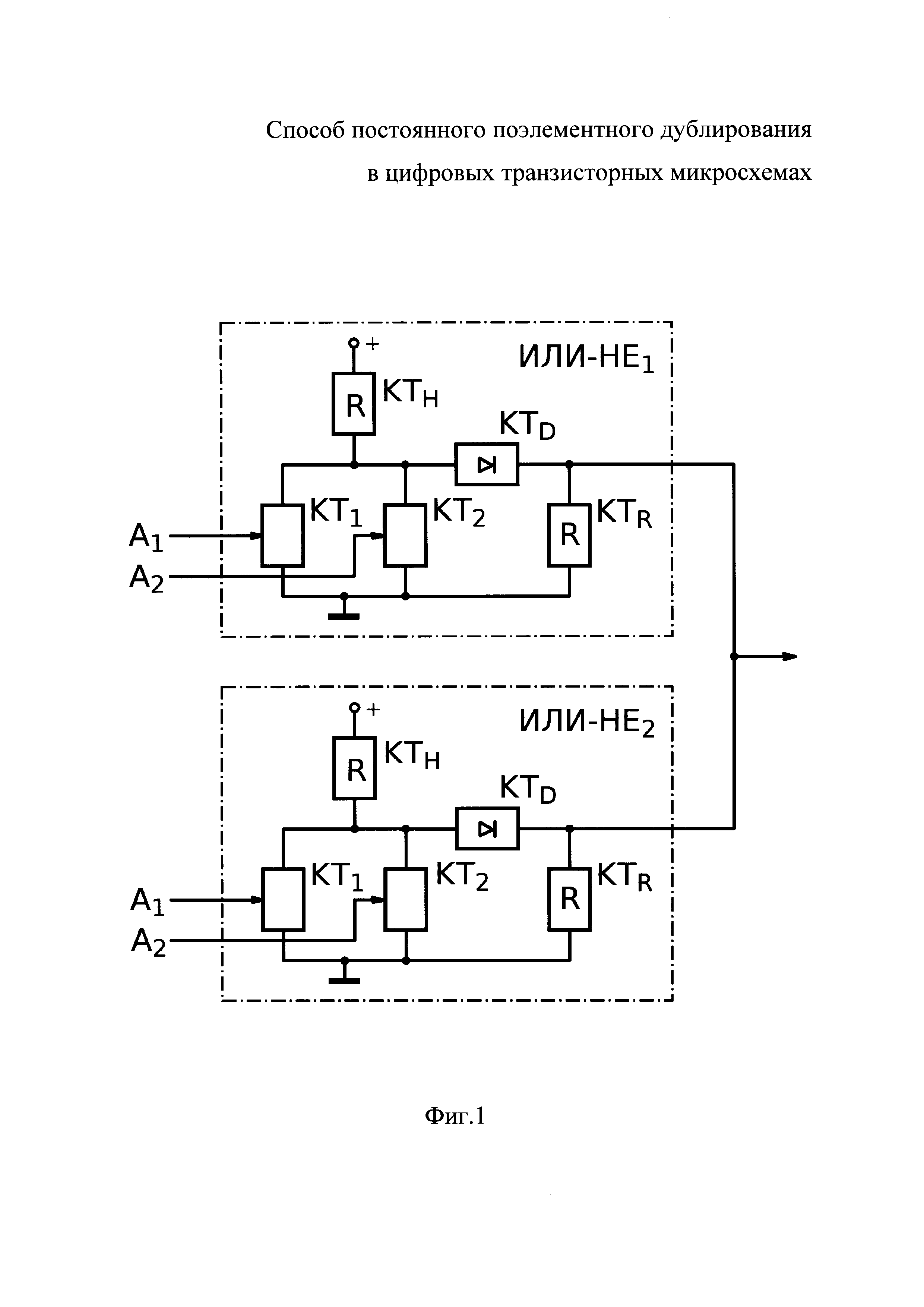

На фиг. 3 показана схема квадрированного транзистора, построенного на одиночных полевых транзисторах и выполненного в виде двух параллельных цепочек последовательно соединенных между собой двух одиночных транзисторов.

Осуществление изобретения

Двухвходовой дублированный логический элемент ИЛИ-НЕ (фиг. 1) состоит из двух дублирующих логических элементов «ИЛИ-НЕ1» и «ИЛИ-НЕ2». Каждый из этих дублирующих элементов состоит из входного - управляющего каскада и выходного каскада. Управляющий каскад в каждом дублирующем элементе «ИЛИ-НЕ» содержит два управляющих квадрированных транзистора КТ1 и КТ2 и квадрированный транзистор нагрузки КТн, выполняющий функцию резистора. Выходной каскад дублирующего элемента «ИЛИ-НЕ» содержит квадрированный транзистор КТд, выполняющий функцию диода, и квадрированный транзистор КTR, выпоняющий функцию резистора. В принципе квадрированный транзистор КТд может быть заменен на квадрированный диод, а квадрированные транзисторы КТн и КTR могут быть заменены на квадрированные резисторы. Однако здесь эти замены не сделаны не только из соображений однородности технологии, но и для того, чтобы упростить оценку вероятности отказа микросхемы.

Каждый квадрированный транзистор (фиг. 2 и фиг. 3) заменяет одиночный транзистор в обычной схеме логического элемента и выполнен в виде четверки соединенных между собой параллельно и последовательно одиночных транзисторов Т1, Т2, Т3 и T4. Входы А одиночных транзисторов соединены между собой (на фиг. 2 и фиг. 3 это не показано) и являются входом квадрированного транзистора, а объединенные одноименные свободные выходы одиночных транзисторов являются выходами квадрированного транзистора. Одноименные выходы одиночных транзисторов - это их «сток», либо «исток». «Свободными» являются выходы, не соединенные с другими одиночными транзисторами в квадрированном транзисторе.

Квадрированный транзистор выполняют в двух вариантах. В одном из них (фиг. 2) квадрированный транзистор выполняют виде двух последовательно соединенных каскадов, один из которых состоит из параллельно соединенных между собой двух одиночных транзисторов Т1 и Т2, а другой каскад состоит из параллельно соединенных между собой двух одиночных транзисторов Т3 и Т4. Этот вариант реализует логическую функцию (А+А)(А+А). В другом из этих вариантов (фиг. 3) квадрированный транзистор выполняют в виде двух параллельных цепочек последовательно соединенных между собой двух одиночных транзисторов. Одна из этих цепочек состоит из транзисторов Т1 иТ3, а другая цепочка состоит из транзисторов Т2 и Т4. Этот вариант реализует логическую функцию АА+АА.

Микросхему, построенную предлагаемым способом, а именно - с дублированием логических элементов и квадрированными транзисторами вместо одиночных транзисторов будем называть дублированно-квадрированной микросхемой.

Оценим вероятность отказа дублированно-квадрированной микросхемы. Для этого представим дублированно-квадрированную микросхему, состоящую из N дублированно-квадрированных логических элементов, в виде двух непересекающихся подмножеств М1-э и М2-э, каждое из которых содержит дублируемые квадрированные логические элементы, не образующие между собой пары, представляющие дублированные квадрированные логические элементы. С учетом этого вероятность отказа дублированно-квадрированной микросхемы по аналогии с приведенной выше формулой (1.12) представим в виде:

где

Р2(д-кв) - вероятность отказа дублированно-квадрированной микросхемы;

Рм - вероятность отказа хотя бы одного логического элемента любого подмножества Mj-э (j=1 и 2), содержащего N непарных дублируемых элементов, или, иначе говоря, вероятность отказа половины квадрированной микросхемы при попадании двух частиц или одной частицы в разные одиночные транзисторы отказывающей пары одного квадрированного транзистора; здесь отказывающей парой квадрированного транзистора называется пара его одиночных транзисторов, при отказе которой он выходит из строя.

Число квадрированных транзисторов в подмножестве Mj-э составляет

где

N- число дублирующих квадрированных логических элементов в подмножестве Mj-э,

nд-квт - суммарное число квадрированных транзисторов во входном и выходном каскаде одного дублирующего квадрированного логического элемента; для упрощения оценок примем величину nд-квт постоянной.

Величину nд-квт представим в виде:

где

nквт - число квадрированных транзисторов во входном каскаде дублируемого квадрированного логического элемента; например, для двухвходового «ИЛИ-НЕ» nквт=3;

b - число квадрированных транзисторов в выходном каскаде дублируемого квадрированного транзистора; b=2.

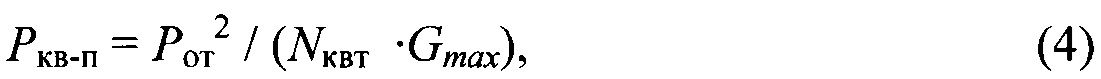

Найдем вероятность Ркв-п попадания двух частиц или одной частицы в два одиночных транзистора, входящих в один квадрированный транзистор, т.е. в одну любую пару одиночных транзисторов одного квадрированного транзистора:

где

Рот - вероятность отказа одиночного транзистора в квадрированной микросхеме при попадании в нее одной частицы;

Gmax - максимальное число пар одиночных транзисторов в одном квадрированном транзисторе; Gmax=6 (т.е. число сочетаний из 4-х по 2);

Nквт - число квадрированных транзисторов подмножестве Мjэ определено в (2).

Оценим вероятность Рот для случаев, когда в квадрированной микросхеме при попадании в нее одной частицы возможны только одинаковые типы дефектов («обрыв» или «КЗ» - короткое замыкание):

где

Фкв - флюенс для квадрированной микросхемы,

Sкв - площадь половины квадрированной микросхемы, соответствующей одному подмножеству Mj-э (j=1 и 2), содержащему N непарных дублируемых элементов.

W - вероятность повреждения единицы площади микросхемы при попадании в нее частицы, определенная в упомянутой статье П.А. Александрова и др. «Отказоустойчивость покомпонентно дублированной микросхемы при облучении ((1-12), с. 12).

Площадь Sкв половины квадрированной микросхемы без учета площади внешних соединений представим в виде:

где Sот - площадь ячейки нижнего уровня микросхемы, содержащей один одиночный транзистор; Nот - число одиночных транзисторов в половине квадрированной микросхемы.

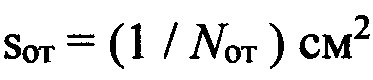

Если принять Sкв = 1 см2, то из (5) найдем:

Подставим (6) в (5):

Так как каждый квадрированный транзистор содержит 4 одиночных транзистора, то

где Nквт - число квадрированных транзисторов в половине квадрированной микросхеме, определенное в (2).

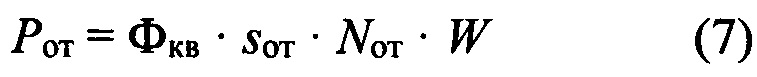

Вероятность Рм отказа половины квадрированной микросхемы при попадании двух частиц или одной частицы в разные одиночные транзисторы отказывающей пары одного квадрированного транзистора найдем как вероятность того, что в этой половине квадрированной микросхемы пара одиночных транзисторов одного квадрированного транзистора, пораженных двумя частицами или одной частицей, окажется отказывающей:

где вероятность Ркв-п определена в (4),

μ - относительная вероятность попадания частицы в отказывающую пару одиночных транзисторов:

где Gотк - число отказывающих пар транзисторов в квадрированном транзисторе; число Gmax определено выше в (4); можно показать, что при одинаковом типе дефектов в одиночных транзисторах имеем μ=1/3, либо μ=2/3.

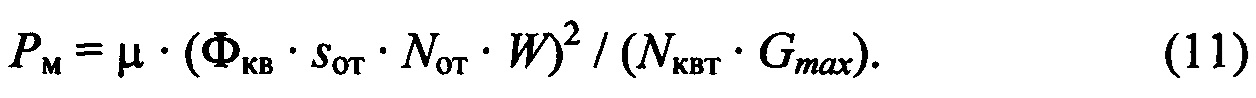

Подставив (4) и (7) в (9), получим:

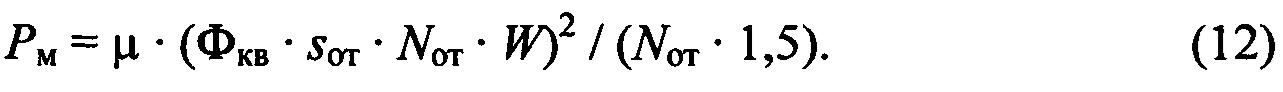

Подставив Gmax = 6 в (11), с учетом (8) получим

Подставим (12) в (1):

Из (2) и (8) имеем:

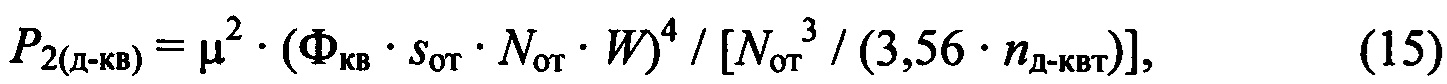

Подставив (14) в (13), получим

где

nд-квт - суммарное число квадрированных транзисторов во входном и выходном каскаде одного квадрированного логического элемента, указанное в формуле (2), остальные величины определены выше.

Для упрощения оценок величина nд-квт принята постоянной; например, примем, что в микросхеме используется только трехвходовой квадрированный элемент ИЛИ-НЕ, для которого nд-квт = 6.

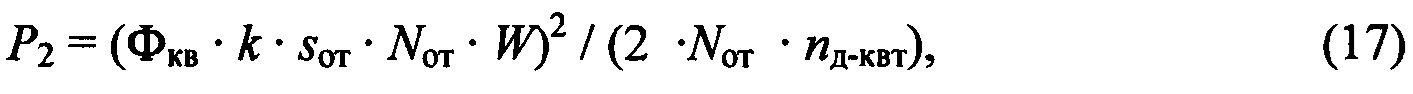

Сравним отказоустойчивость дублированной микросхемы в прототипе (т.е. без использования квадрированных транзисторов) и дублировано-квадрированной микросхемы, рассмотренной выше.

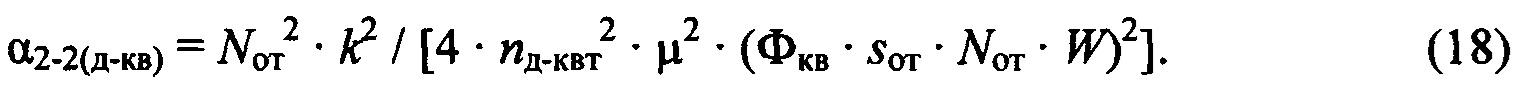

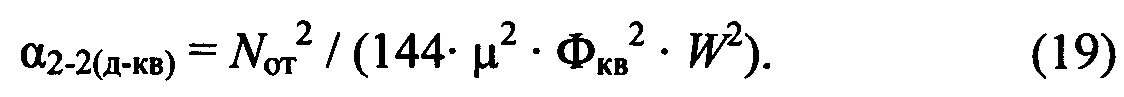

Найдем показатель α2-2(д-кв) изменения отказоустойчивости:

где

Р2 - вероятность отказа дублированной микросхемы без использования квадрированных транзисторов;

P2(д-кв) - вероятность отказа дублированно-квадрированной микросхемы, определенная в (15).

Исходя из формулы (1.12), приведенной в разделе «Уровень техники», для удобства вычисления показателя α2-2(Д-кв) представим вероятность Р2 через Nот:

где k - число одиночных транзисторов в дублирующем логическом элементе без использования в нем квадрированных транзисторов; k>1; остальные величины определены выше.

Подставим (15) и (17) в (16):

Примем, что sот ⋅ Nот = 1 см2, nд-квт = 6 (для трехвходового дублирующего элемента ИЛИ-НЕ) и k=1 (с большим запасом). Тогда из (18) получим:

Для оценки α2-2(д-кв) примем следующие параметры:

Фкв = 1011/2,25, W = 1,5⋅10-7

(эти значения величин Фкв и W указаны в упомянутой выше статье П.А. Александрова и др. «Отказоустойчивость покомпонентно дублированной микросхемы при облучении», см. формулы (1.13), (2.12), с. 13-15);

как указано выше, μ = 1/3, либо μ = 2/3; примем худший случай: μ = 2/3.

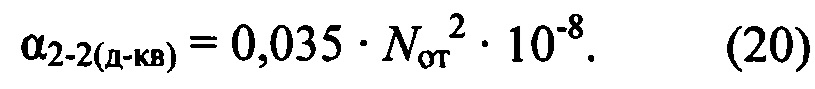

Подставив значения этих параметры в (19), после преобразований получим:

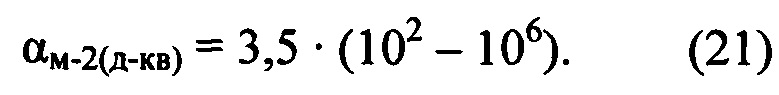

Для оценки примем Nот = 106-108. Тогда из (20) получим следующую оценку:

Таким образом, предлагаемый способ позволяет существенно (на 2-6 порядков) уменьшить вероятность отказа дублированно-квадрированной микросхемы по сравнению с вероятностью отказа прототипа - дублированной микросхемы без квадрирования одиночных транзисторов.

Как указывалось в разделе «Уровень техники», вероятность отказа микросхемы, построенной на квадрированных транзисторах без дублирования логических элементов, ниже вероятности отказа микросхемы с дублированием логических элементов, но без квадрированных транзисторов, на один-два порядка. Вследствие этого можно показать, что вероятность отказа дублированно-квадрированной микросхемы будет ниже вероятности отказа квадрированной микросхемы без дублирования логических элементов примерно на 2-5 порядков.