Результат интеллектуальной деятельности: АНАЛОГОВЫЙ ПРОЦЕССОР

Вид РИД

Изобретение

Изобретение относится к автоматике и аналоговой вычислительной технике и может быть использовано для построения функциональных узлов аналоговых вычислительных машин, средств автоматического регулирования и управления и др.

Известны аналоговые процессоры (см., например, фиг. 1 в описании изобретения к патенту РФ 2446462, кл. G06G 7/52, 2012 г.), которые содержат реляторы и реализуют выбор из пяти входных аналоговых сигналов х1,…,х5 сигнала х(r) любого заданного ранга r∈{1,…,5} (х(1)=min(x1,…,x5),…,х(5)=max(x1,…,x5)).

К причине, препятствующей достижению указанного ниже технического результата при использовании известных аналоговых процессоров, относятся ограниченные функциональные возможности, обусловленные тем, что не допускается обработка шести входных аналоговых сигналов.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип аналоговый процессор (фиг. 1 в описании изобретения к патенту РФ 2474875, кл. G06G 7/52, 2013 г.), который содержит реляторы и реализует выбор из пяти входных аналоговых сигналов x1,…,x5 сигнала х(r) любого заданного ранга r∈{1,…,5} (х(1)=min(x1,…,x5),…,х(5)=max(x1,…x5)).

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся ограниченные функциональные возможности, обусловленные тем, что не допускается обработка шести входных аналоговых сигналов.

Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения реализации выбора из шести входных аналоговых сигналов x1,…,x6 сигнала х(r) любого заданного ранга r∈{1,…,6} (х(1)=min(x1,…,x6),…,x(6)=max(x1,…,x6)) при сохранении элементного базиса прототипа.

Указанный технический результат при осуществлении изобретения достигается тем, что в аналоговом процессоре, содержащем двенадцать реляторов, каждый из которых содержит компаратор, подключенный выходом к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого является входом управления релятора, а выход соединен с управляющим входом замыкающего и размыкающего ключей, выходы которых объединены и образуют выход релятора, первым и вторым входами которого являются соответственно неинвертирующий и инвертирующий входы компаратора, присоединенные соответственно к входам замыкающего и размыкающего ключей, причем первые входы третьего, пятого и вторые входы четвертого, пятого реляторов соединены соответственно с выходами второго, четвертого и восьмого, девятого реляторов, входы управления первого, шестого реляторов подключены к первому управляющему входу аналогового процессора, второй и третий управляющие входы которого соединены соответственно с входами управления двенадцатого и десятого реляторов, особенность заключается в том, что в него дополнительно введены пять аналогичных вышеупомянутым реляторов, первый, второй входы второго и первый, второй входы седьмого реляторов соединены соответственно с выходами первого, шестого и четырнадцатого, пятнадцатого реляторов, первый, второй входы j-го ( ) и первый, второй входы двенадцатого реляторов подключены соответственно к выходам (j+1)-го, (j+3)-го и шестнадцатого, семнадцатого реляторов, первый, второй входы одиннадцатого и первый, второй входы тринадцатого реляторов соединены соответственно с выходами четырнадцатого, шестого и первого, пятнадцатого реляторов, первый, второй входы шестнадцатого, второй вход и выход третьего реляторов подключены соответственно к выходам первого, шестого, седьмого и первому входу четвертого реляторов, а входы управления седьмого, восьмого, девятого и выход пятого реляторов соединены соответственно с первым управляющим входом и выходом аналогового процессора, второй и третий управляющие входы которого подключены соответственно к объединенным входам управления второго, четвертого, одиннадцатого, тринадцатого, четырнадцатого, пятнадцатого, семнадцатого реляторов и объединенным входам управления третьего, пятого, шестнадцатого реляторов.

) и первый, второй входы двенадцатого реляторов подключены соответственно к выходам (j+1)-го, (j+3)-го и шестнадцатого, семнадцатого реляторов, первый, второй входы одиннадцатого и первый, второй входы тринадцатого реляторов соединены соответственно с выходами четырнадцатого, шестого и первого, пятнадцатого реляторов, первый, второй входы шестнадцатого, второй вход и выход третьего реляторов подключены соответственно к выходам первого, шестого, седьмого и первому входу четвертого реляторов, а входы управления седьмого, восьмого, девятого и выход пятого реляторов соединены соответственно с первым управляющим входом и выходом аналогового процессора, второй и третий управляющие входы которого подключены соответственно к объединенным входам управления второго, четвертого, одиннадцатого, тринадцатого, четырнадцатого, пятнадцатого, семнадцатого реляторов и объединенным входам управления третьего, пятого, шестнадцатого реляторов.

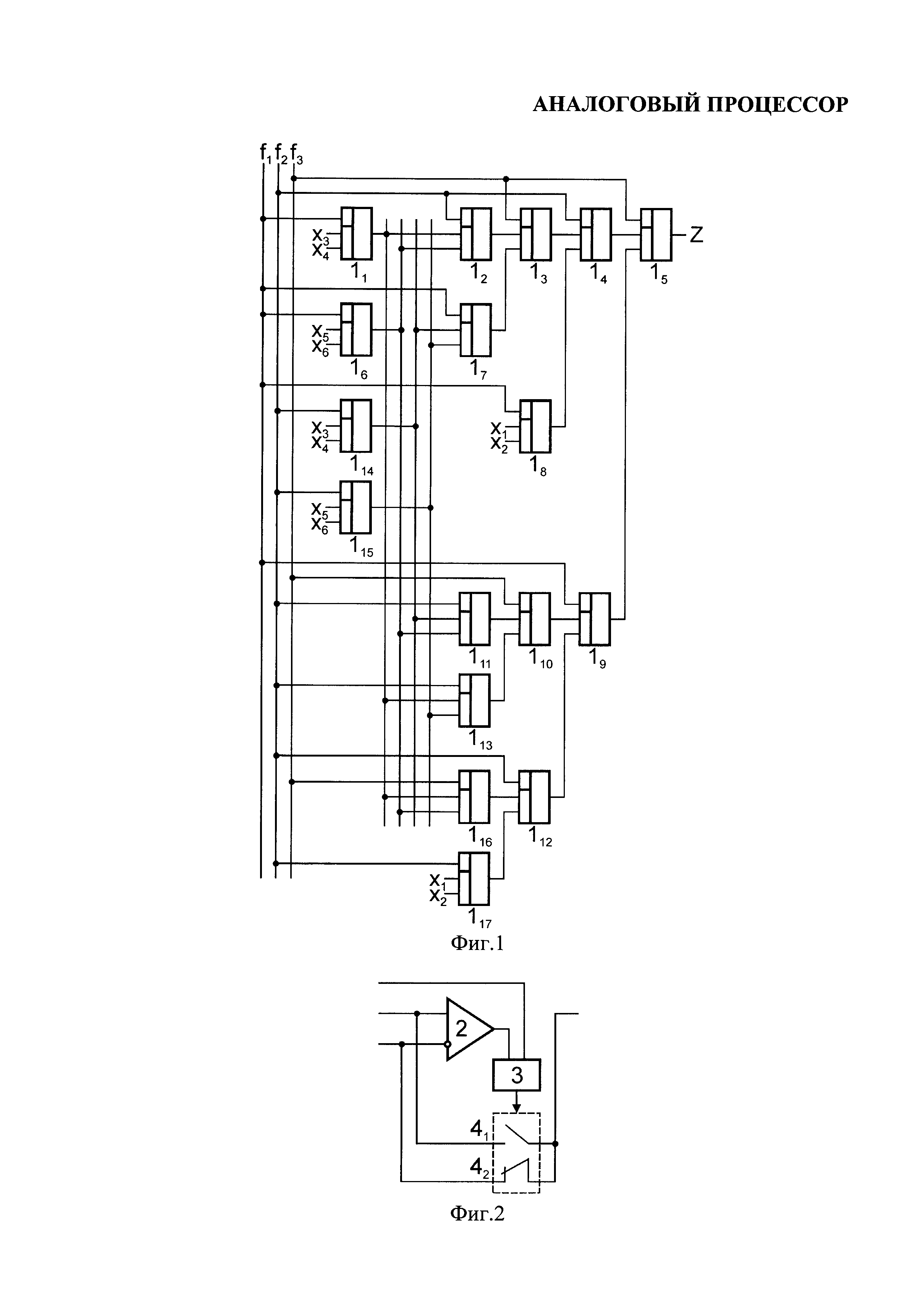

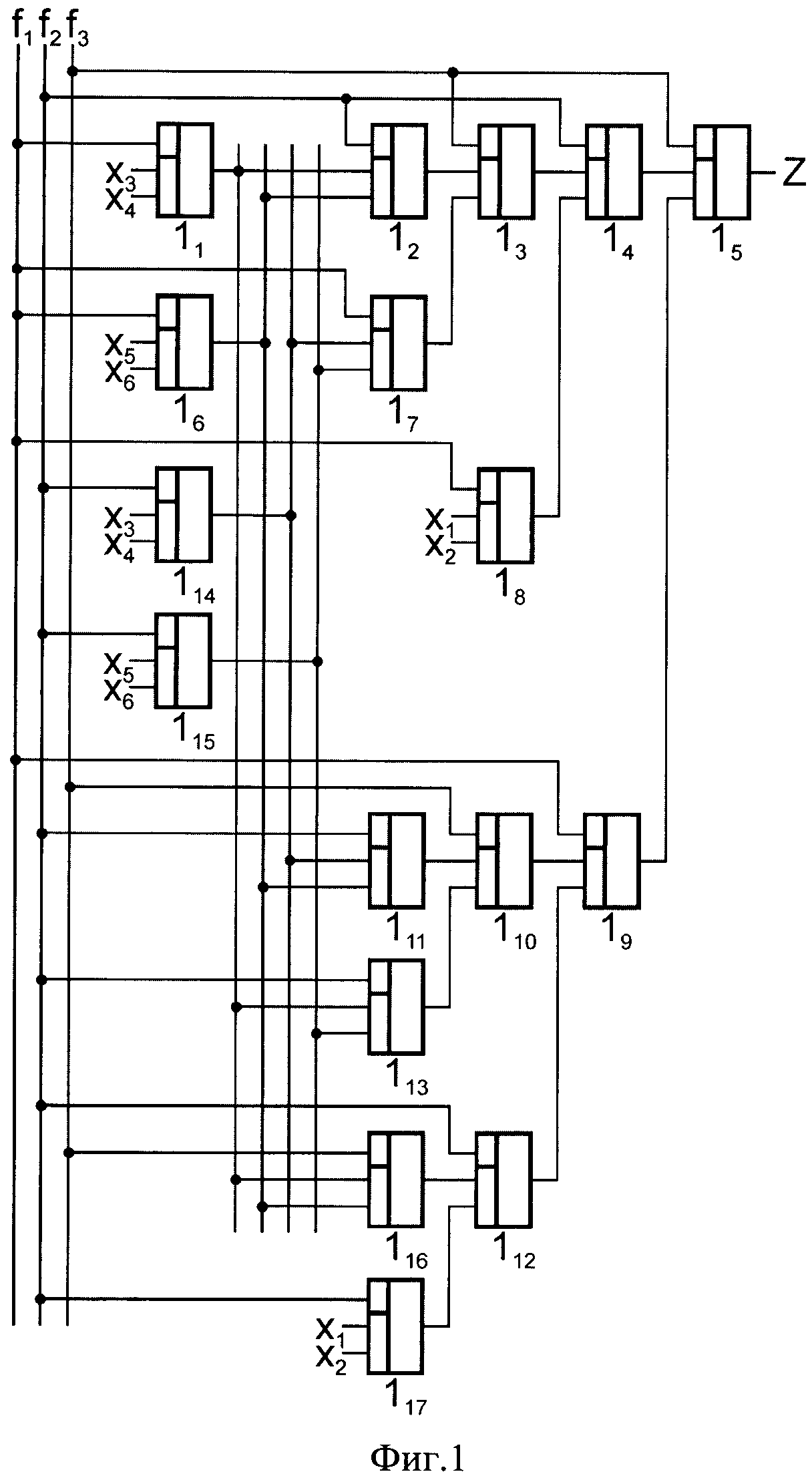

На фиг. 1 и фиг. 2 представлены соответственно схема предлагаемого аналогового процессора и схема релятора, использованного при построении указанного процессора.

Аналоговый процессор содержит реляторы 11,…,117. Каждый релятор содержит компаратор 2, подключенный выходом к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3, второй вход которого является входом управления релятора, а выход соединен с управляющим входом замыкающего и размыкающего ключей 41 и 42, выходы которых объединены и образуют выход релятора, первым и вторым входами которого являются соответственно неинвертирующий и инвертирующий входы компаратора 2, присоединенные соответственно к входам ключей 41 и 42. Первый, второй входы релятора 1i ( ) и первый, второй входы релятора 17 соединены соответственно с выходами реляторов 1j-1, 1i+4 и 114, 115, первый, второй входы релятора 1j (

) и первый, второй входы релятора 17 соединены соответственно с выходами реляторов 1j-1, 1i+4 и 114, 115, первый, второй входы релятора 1j ( ) и первый, второй входы релятора 112 подключены соответственно к выходам реляторов 1j+1, 1j+3 и l16, l17, первый, второй входы релятора 111 и первый, второй входы релятора 113 соединены соответственно с выходами реляторов 114, 16 и l1, 115, а первый, второй входы релятора l16, выход релятора 15 и объединенные входы управления реляторов 11, 16, 17, 18, 19 подключены соответственно к выходам реляторов 11 16, выходу и первому управляющему входу аналогового процессора, второй и третий управляющие входы которого соединены соответственно с объединенными входами управления реляторов 12, 14, 111, 112, 113, 114, 115, 117 и объединенными входами управления реляторов 13, 15, 110, 116.

) и первый, второй входы релятора 112 подключены соответственно к выходам реляторов 1j+1, 1j+3 и l16, l17, первый, второй входы релятора 111 и первый, второй входы релятора 113 соединены соответственно с выходами реляторов 114, 16 и l1, 115, а первый, второй входы релятора l16, выход релятора 15 и объединенные входы управления реляторов 11, 16, 17, 18, 19 подключены соответственно к выходам реляторов 11 16, выходу и первому управляющему входу аналогового процессора, второй и третий управляющие входы которого соединены соответственно с объединенными входами управления реляторов 12, 14, 111, 112, 113, 114, 115, 117 и объединенными входами управления реляторов 13, 15, 110, 116.

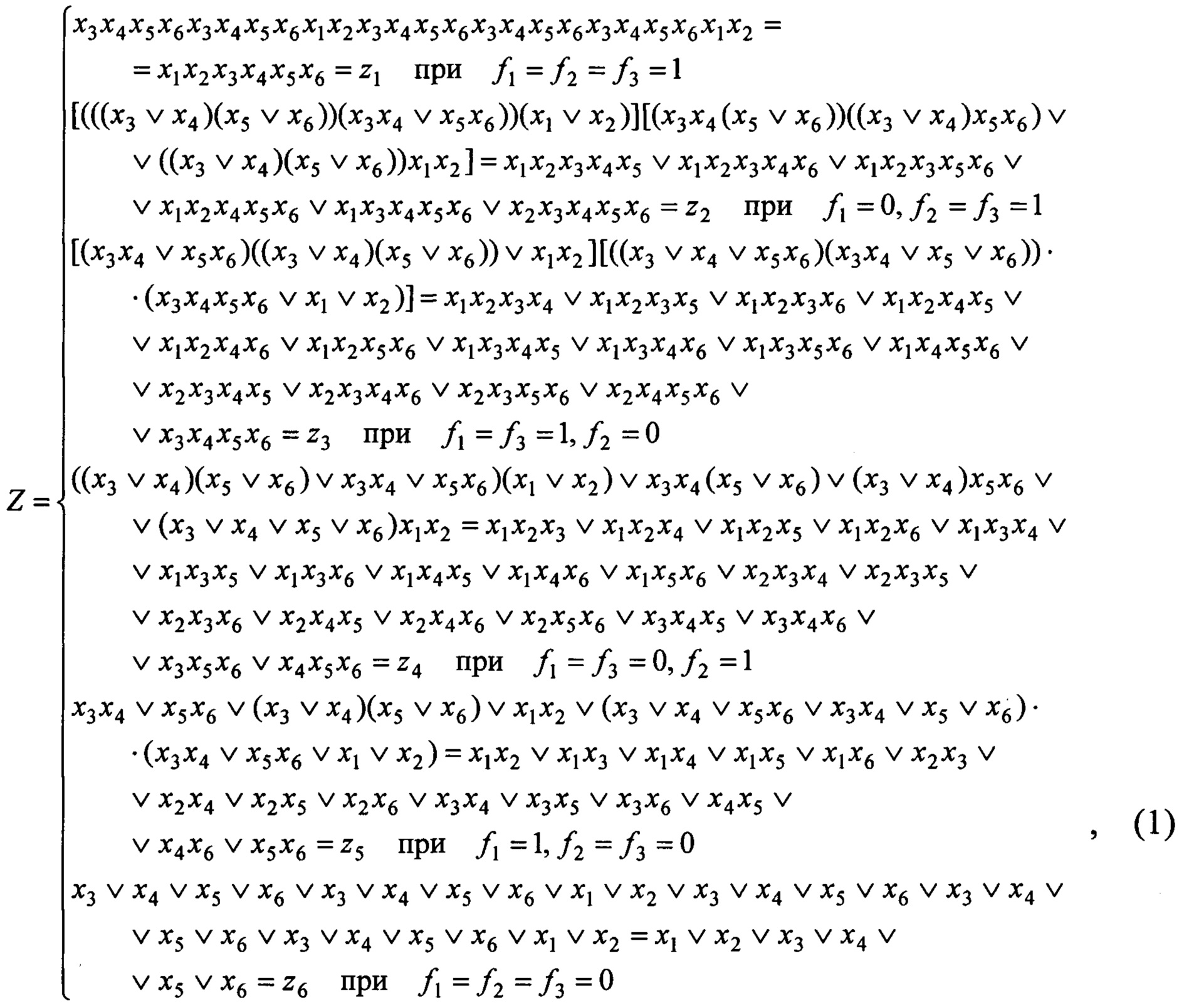

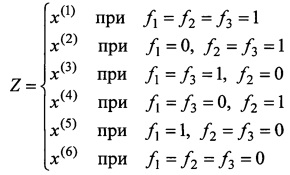

Работа предлагаемого аналогового процессора осуществляется следующим образом. На его первом, втором, третьем управляющих входах фиксируются соответственно необходимые управляющие сигналы ƒ1, ƒ2, ƒ3∈{0,1}. На первые и вторые входы реляторов 18, l17; первые и вторые входы реляторов 11 114; первые и вторые входы реляторов 16, 115 подаются соответственно подлежащие обработке аналоговые сигналы (напряжения) х1 и х2; х3 и х4; x5 и х6. Если на входе управления релятора присутствует логический "0" (логическая "1") и сигнал на его первом входе больше либо меньше сигнала на его втором входе, то ключ 41 соответственно замкнут (разомкнут) либо разомкнут (замкнут), а ключ 42 соответственно разомкнут (замкнут) либо замкнут (разомкнут). Следовательно, если на входе управления релятора присутствует логический "0" (логическая "1"), то этот релятор будет выделять на своем выходе наибольший (наименьший) из сигналов, действующих на его первом и втором входах. Таким образом, сигнал на выходе предлагаемого процессора определяется выражением

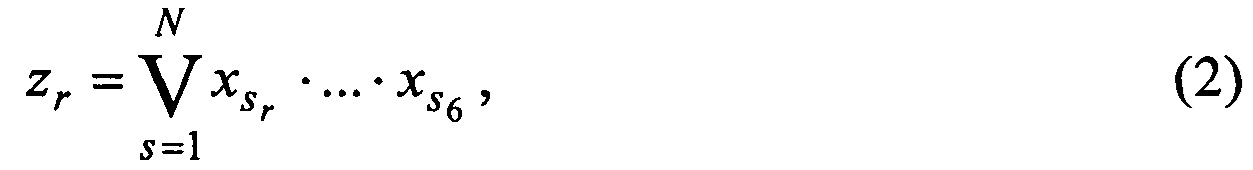

где символами ∨ и ⋅ обозначены соответственно операции max и min. Согласно (1) можно записать

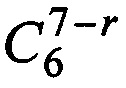

где r∈{1,…,6};  ∈{x1,…,x6} (1≤sr<...<s6≤6); N=

∈{x1,…,x6} (1≤sr<...<s6≤6); N= есть количество неповторяющихся фрагментов

есть количество неповторяющихся фрагментов  , определяемое как число сочетаний из 6 по 7-r. Выражение (2) совпадает с видом n-арной поисковой функции (функция (6.7) на стр. 117 в книге Левин В.И. Бесконечнозначная логика в задачах кибернетики. М.: Радио и связь, 1982 г.), которая при n=6 реализует алгоритм выделения из множества {х1,…,х6} элемента х(r) заданного ранга r∈{1,…,6} (х(1)=min(x1,…,x6),…,x(6)=max(х1,…,х6)). С учетом указанного, на выходе процессора (фиг. 1) окончательно имеем

, определяемое как число сочетаний из 6 по 7-r. Выражение (2) совпадает с видом n-арной поисковой функции (функция (6.7) на стр. 117 в книге Левин В.И. Бесконечнозначная логика в задачах кибернетики. М.: Радио и связь, 1982 г.), которая при n=6 реализует алгоритм выделения из множества {х1,…,х6} элемента х(r) заданного ранга r∈{1,…,6} (х(1)=min(x1,…,x6),…,x(6)=max(х1,…,х6)). С учетом указанного, на выходе процессора (фиг. 1) окончательно имеем

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый аналоговый процессор построен в элементном базисе прототипа и обладает более широкими по сравнению с прототипом функциональными возможностями, так как реализует выбор из шести входных аналоговых сигналов x1,…,х6 сигнала х(r) любого заданного ранга r∈{1,…,6} (х(1)=min(x1,…,x6),…,x(6)=max(x1,…,x6)).

Аналоговый процессор, предназначенный для ранговой обработки аналоговых сигналов, содержащий двенадцать реляторов, каждый из которых содержит компаратор, подключенный выходом к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого является входом управления релятора, а выход соединен с управляющим входом замыкающего и размыкающего ключей, выходы которых объединены и образуют выход релятора, первым и вторым входами которого являются соответственно неинвертирующий и инвертирующий входы компаратора, присоединенные соответственно к входам замыкающего и размыкающего ключей, причем первые входы третьего, пятого и вторые входы четвертого, пятого реляторов соединены соответственно с выходами второго, четвертого и восьмого, девятого реляторов, входы управления первого, шестого реляторов подключены к первому управляющему входу аналогового процессора, второй и третий управляющие входы которого соединены соответственно с входами управления двенадцатого и десятого реляторов, отличающийся тем, что в него дополнительно введены пять аналогичных вышеупомянутым реляторов, первый, второй входы второго и первый, второй входы седьмого реляторов соединены соответственно с выходами первого, шестого и четырнадцатого, пятнадцатого реляторов, первый, второй входы j-го и первый, второй входы двенадцатого реляторов подключены соответственно к выходам (j+1)-го, (j+3)-го и шестнадцатого, семнадцатого реляторов, первый, второй входы одиннадцатого и первый, второй входы тринадцатого реляторов соединены соответственно с выходами четырнадцатого, шестого и первого, пятнадцатого реляторов, первый, второй входы шестнадцатого, второй вход и выход третьего реляторов подключены соответственно к выходам первого, шестого, седьмого и первому входу четвертого реляторов, а входы управления седьмого, восьмого, девятого и выход пятого реляторов соединены соответственно с первым управляющим входом и выходом аналогового процессора, второй и третий управляющие входы которого подключены соответственно к объединенным входам управления второго, четвертого, одиннадцатого, тринадцатого, четырнадцатого, пятнадцатого, семнадцатого реляторов и объединенным входам управления третьего, пятого, шестнадцатого реляторов.