Результат интеллектуальной деятельности: УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОВЕДЕНИЯ ПОЛЬЗОВАТЕЛЯ

Вид РИД

Изобретение

Изобретение относится к автоматике и вычислительной технике и предназначено для контроля управляющих действий пользователя в вычислительных системах.

Известно устройство для распознавания образов (патент РФ на изобретение №2306605, опубл. 20.09.2007, БИ №26), используемое для идентификации состояний объектов по значениям их параметров, которое по своей технической сущности является наиболее близким к предлагаемому устройству. Это устройство содержит многоканальный коммутатор, информационные входы которого подключены к информационным входам устройства, аналого-цифровой преобразователь, информационный вход которого подключен к выходу многоканального коммутатора, счетчик адресов, блок памяти, у которого адресные входы младших разрядов подключены к выходу аналого-цифрового преобразователя, а адресные входы старших разрядов блока памяти подключены к выходам счетчика адресов и к адресным входам многоканального коммутатора, блок логических элементов И, в котором первые и вторые входы логических элементов И подключены к соответствующим первым и вторым входам блока логических элементов И, выходы логических элементов И являются выходами блока логических элементов И, блок сдвиговых регистров, в котором информационные входы первых разрядов сдвиговых регистров подключены к соответствующим информационным входам блока сдвиговых регистров, сдвиговые входы сдвиговых регистров подключены к соответствующим сдвиговым входам блока сдвиговых регистров, а выходы последних разрядов сдвиговых регистров подключены к выходам блока сдвиговых регистров, блок управления, первый, второй, третий и четвертый выходы которого подключены соответственно к управляющим входам счетчика адресов, блока памяти, ко второму входу блока логических элементов И и к управляющему входу аналого-цифрового преобразователя, а вход блока управления является управляющим входом устройства, выходы блока памяти подключены непосредственно к соответствующим информационным входам блока сдвиговых регистров и к соответствующим первым входам блока логических элементов И, выходы которого подключены к соответствующим сдвиговым входам блока сдвиговых регистров, выходы которого являются выходами устройства.

Недостатком устройства-прототипа является недостаточная универсальность, связанная с отсутствием возможности распознавания, контроля и анализа поведения объекта, как взаимосвязанной последовательности образов, а также обучения объекта по выполнению требуемой последовательности операций.

В качестве объекта может быть любой программируемый автомат, либо человек (пользователь), выполняющий некоторый комплекс (систему) операций (транзакций) в компьютерной системе.

Техническим результатом настоящего изобретения является повышение уровня универсальности устройства.

Для достижения результата в устройство для контроля поведения пользователя, содержащее блок памяти; блок сдвиговых регистров; блок логических элементов И, информационные входы которого подключены к выходам блока памяти; многоканальный коммутатор; счетчик адресов, выходы которого подключены к адресным входам блока памяти; блок управления, первый и третий выходы которого подключены, соответственно, к управляющему входу счетчика адресов и блока памяти, а первый вход к первому управляющему входу устройства, дополнительно включены: регистр кода транзакций и схема сравнения и сдвиговый регистр результатов сравнения, причем информационные входы регистра кода транзакции и блока сдвиговых регистров подключены, соответственно, к первой и второй группам информационных входов устройства, выход регистра кода транзакции подключен к первой группе адресных входов блока памяти, выходы счетчика адресов подключены к первой группе выходов устройства и к третьей адресной группе блока памяти, выходы многоканального коммутатора подключены к четвертому выходу устройства, ко входам четвертой адресной группы блока памяти и ко второй группе информационных входов схемы сравнения, первая группа информационных входов которой подключена к выходам блока памяти и к первой группе информационных входов блока логических элементов И, выходы которого подключены ко второй группе выходов устройства, выход схемы сравнения подключен к третьему выходу устройства, к информационному входу сдвигового регистра результатов сравнения и к пятому входу блока управления, второй выход которого подключен ко второму адресному входу блока памяти, шестой выход блока управления подключен к шестому выходу устройства, а седьмой, восьмой и девятый выходы блока управления подключены к управляющим входам, соответственно, блока сдвиговых регистров, многоканального коммутатора и регистра кода транзакций, а второй, третий и четвертый входы блока управления подключены, соответственно, ко второму, третьему и четвертому управляющим входам устройства.

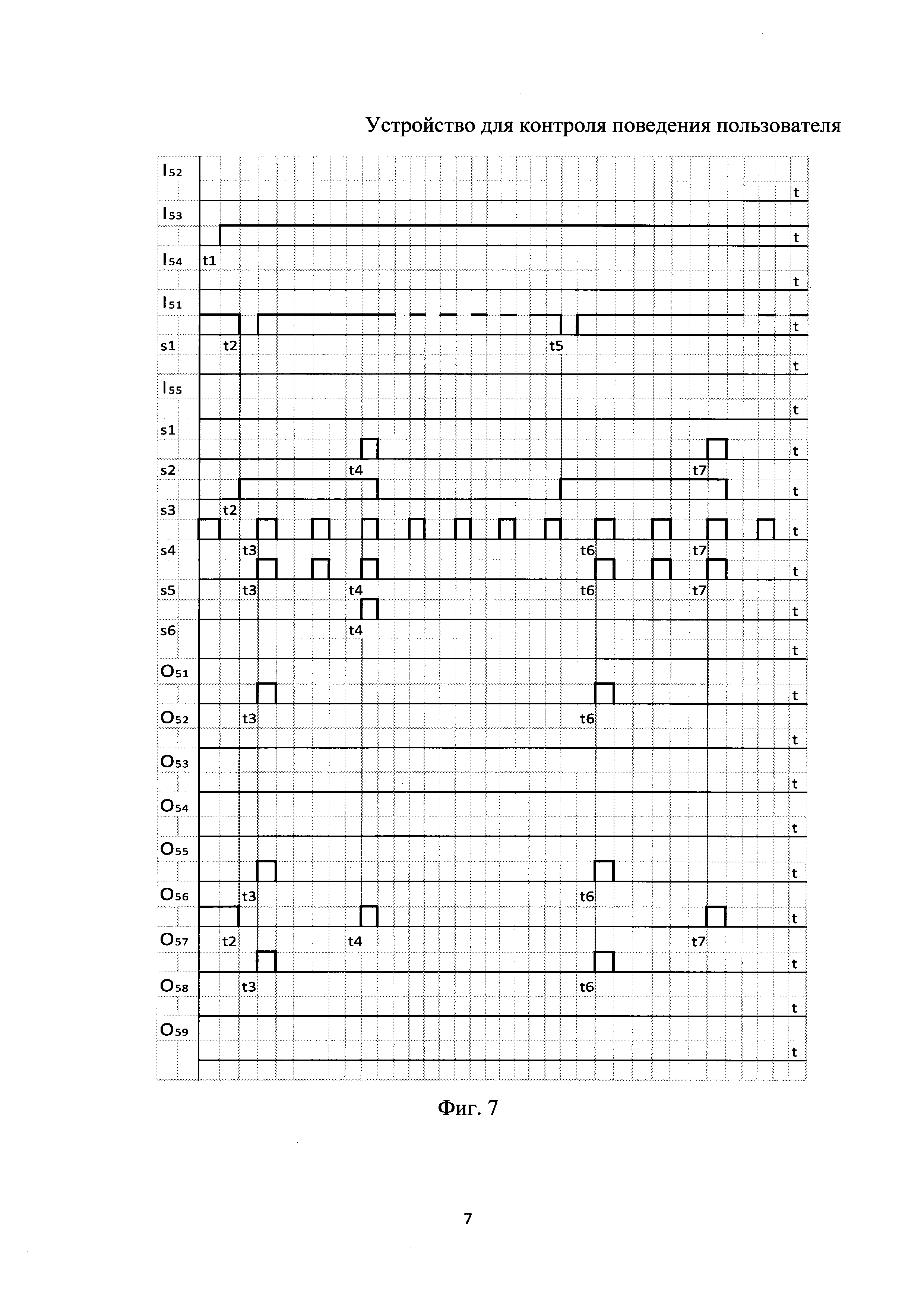

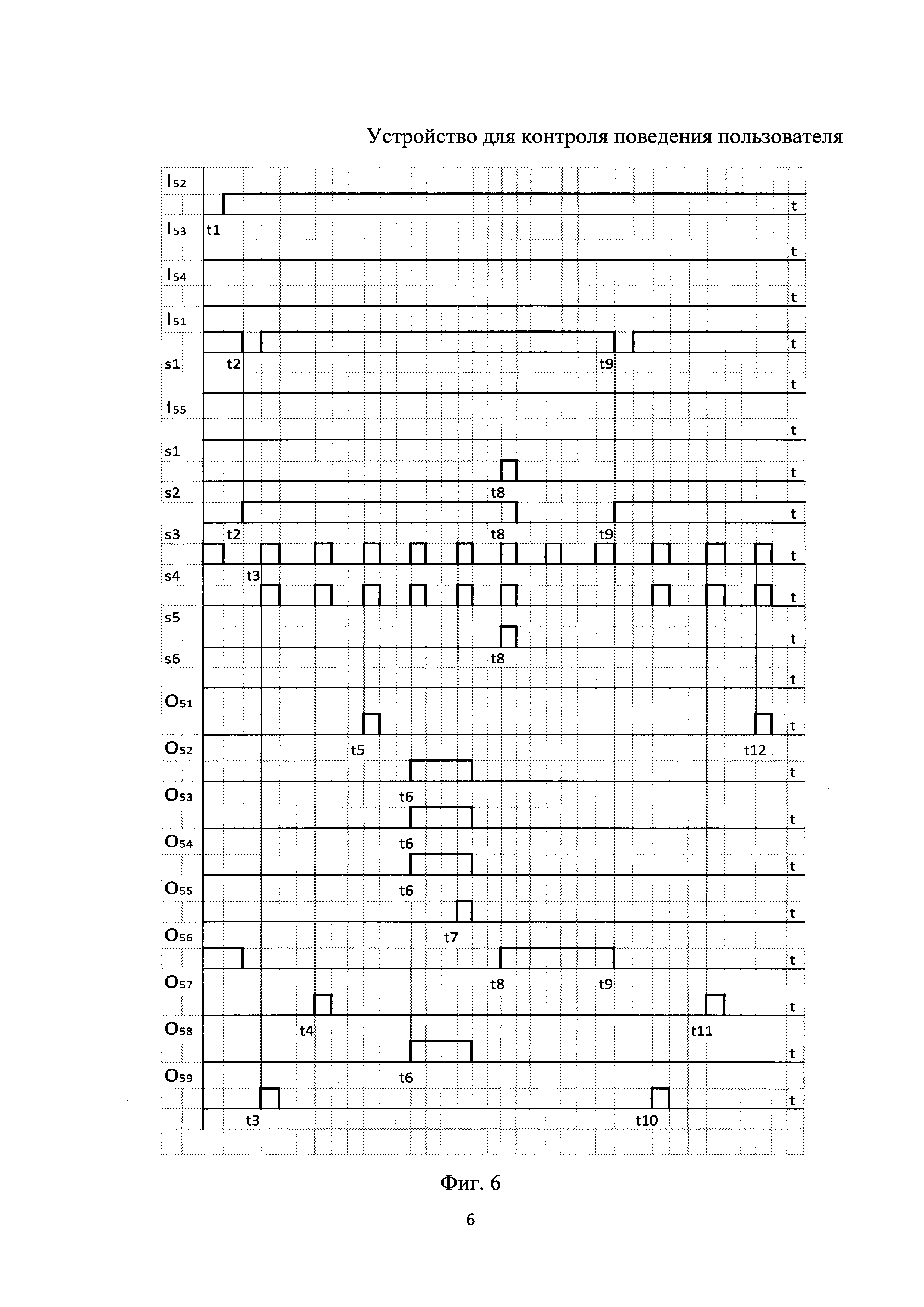

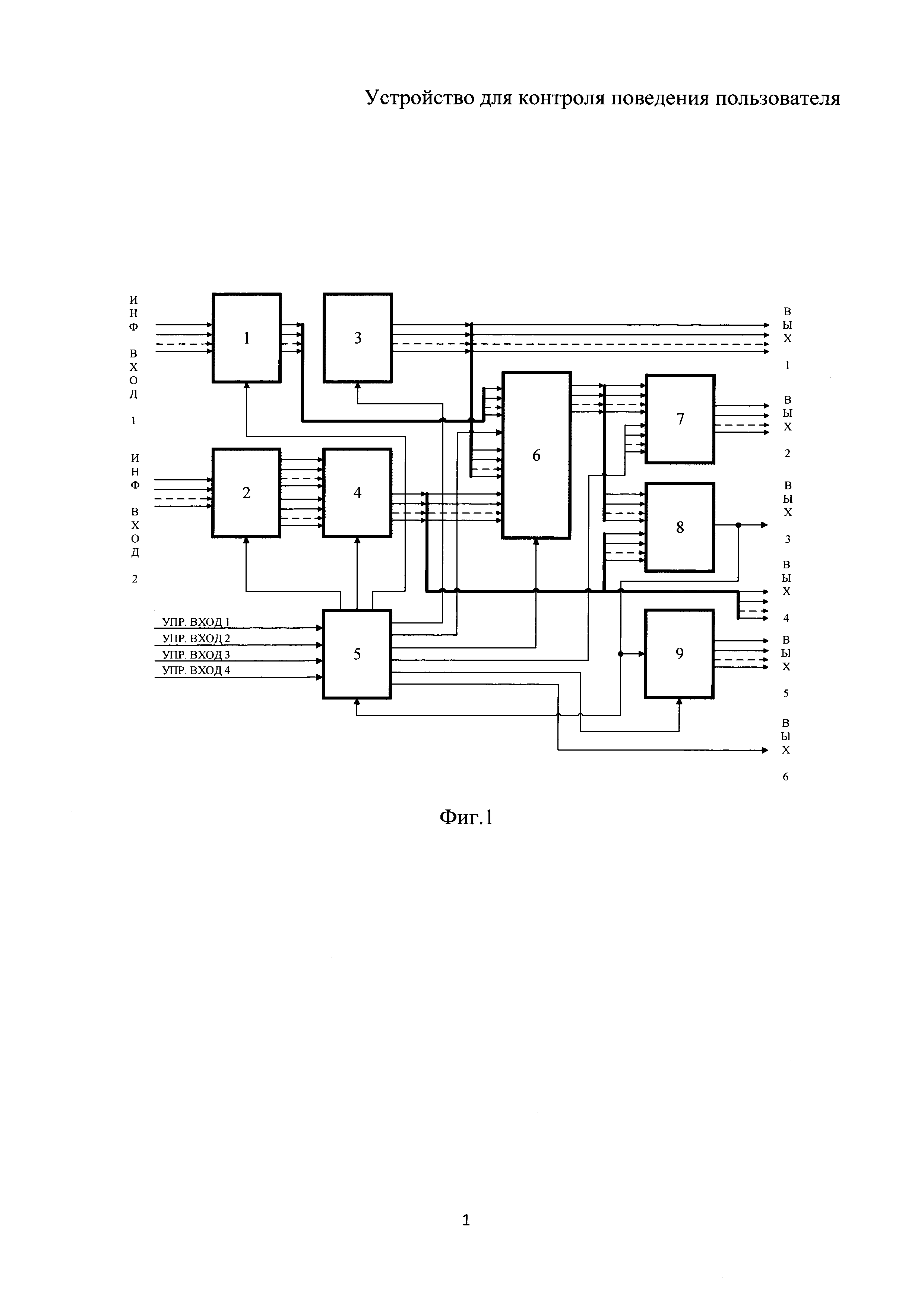

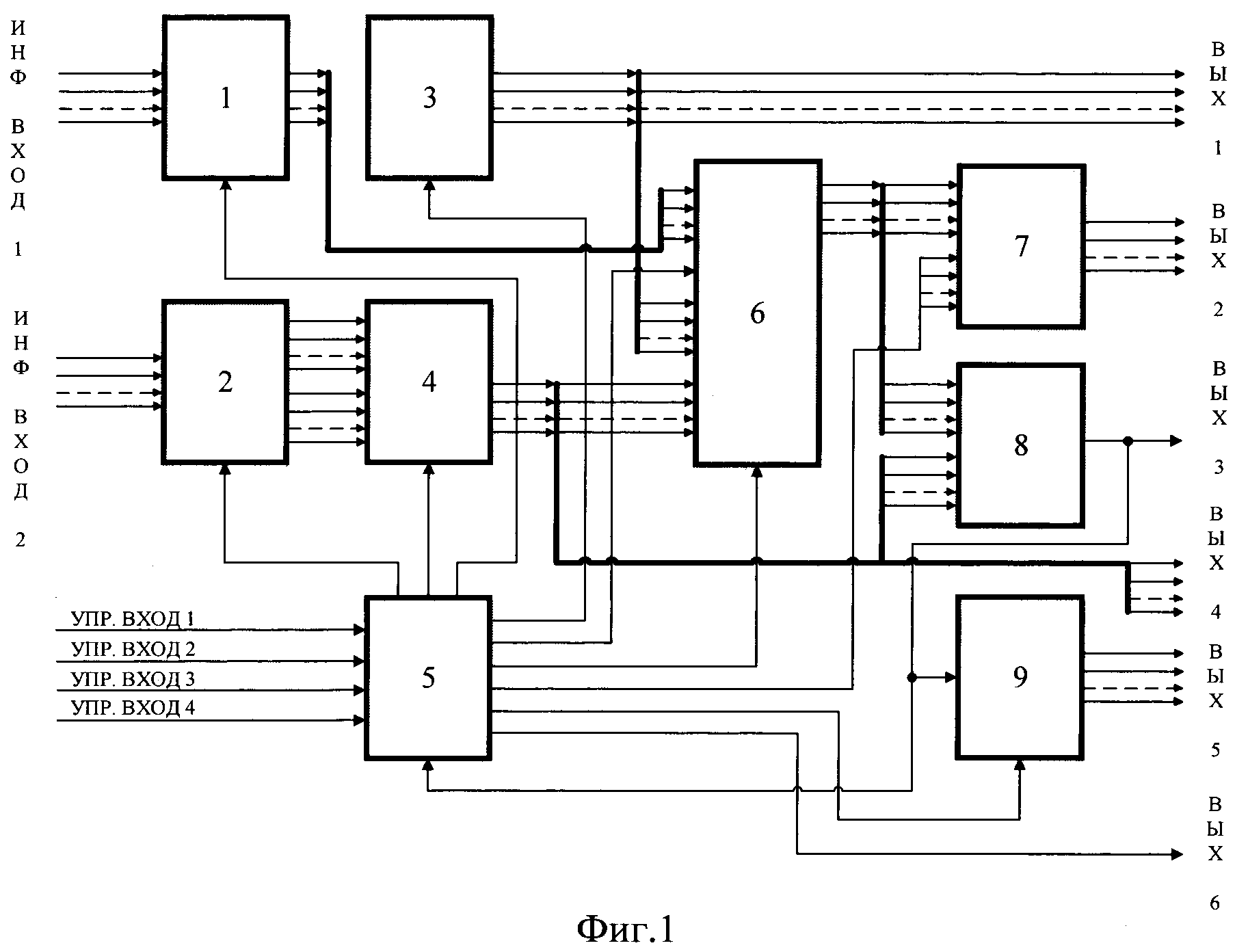

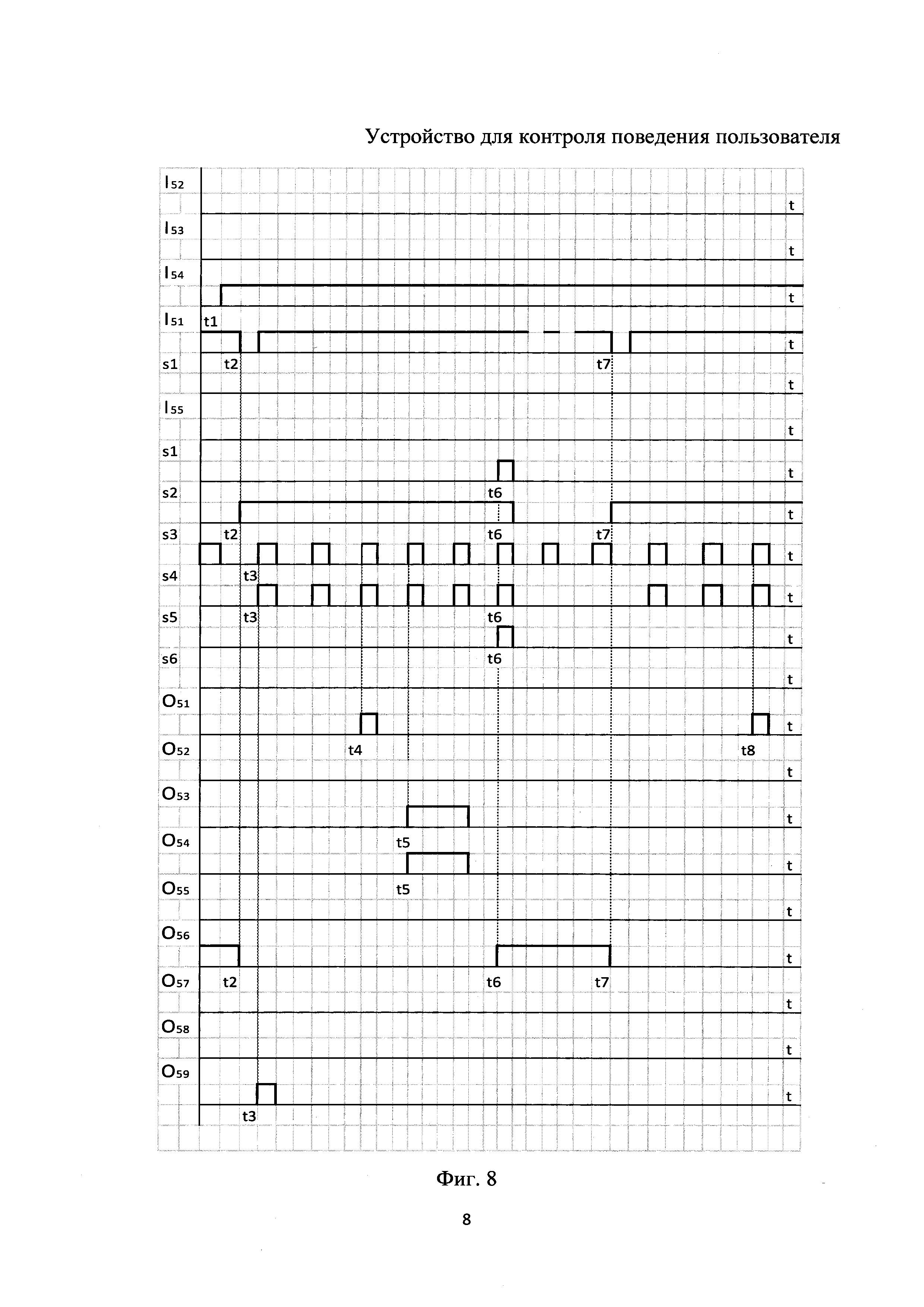

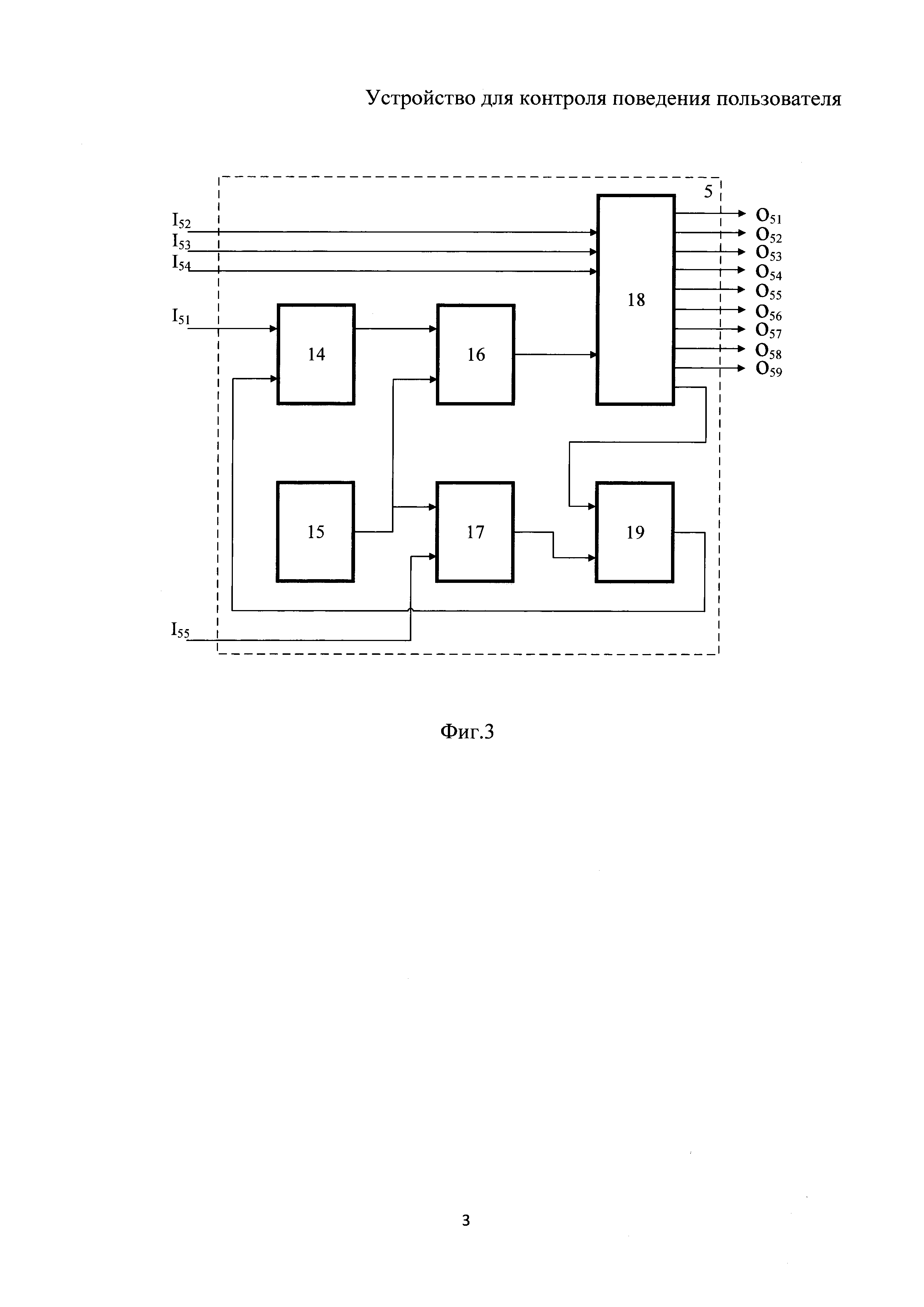

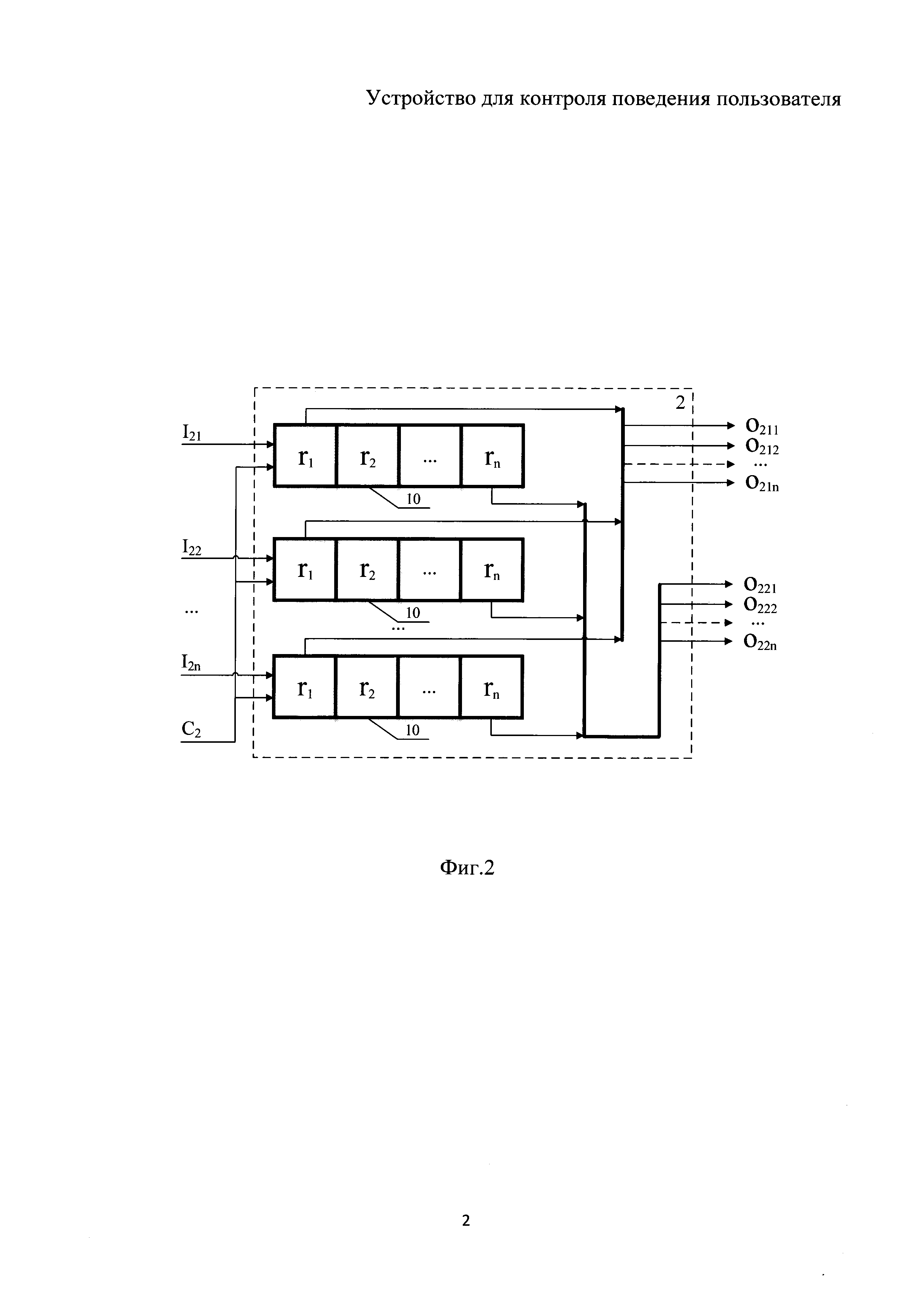

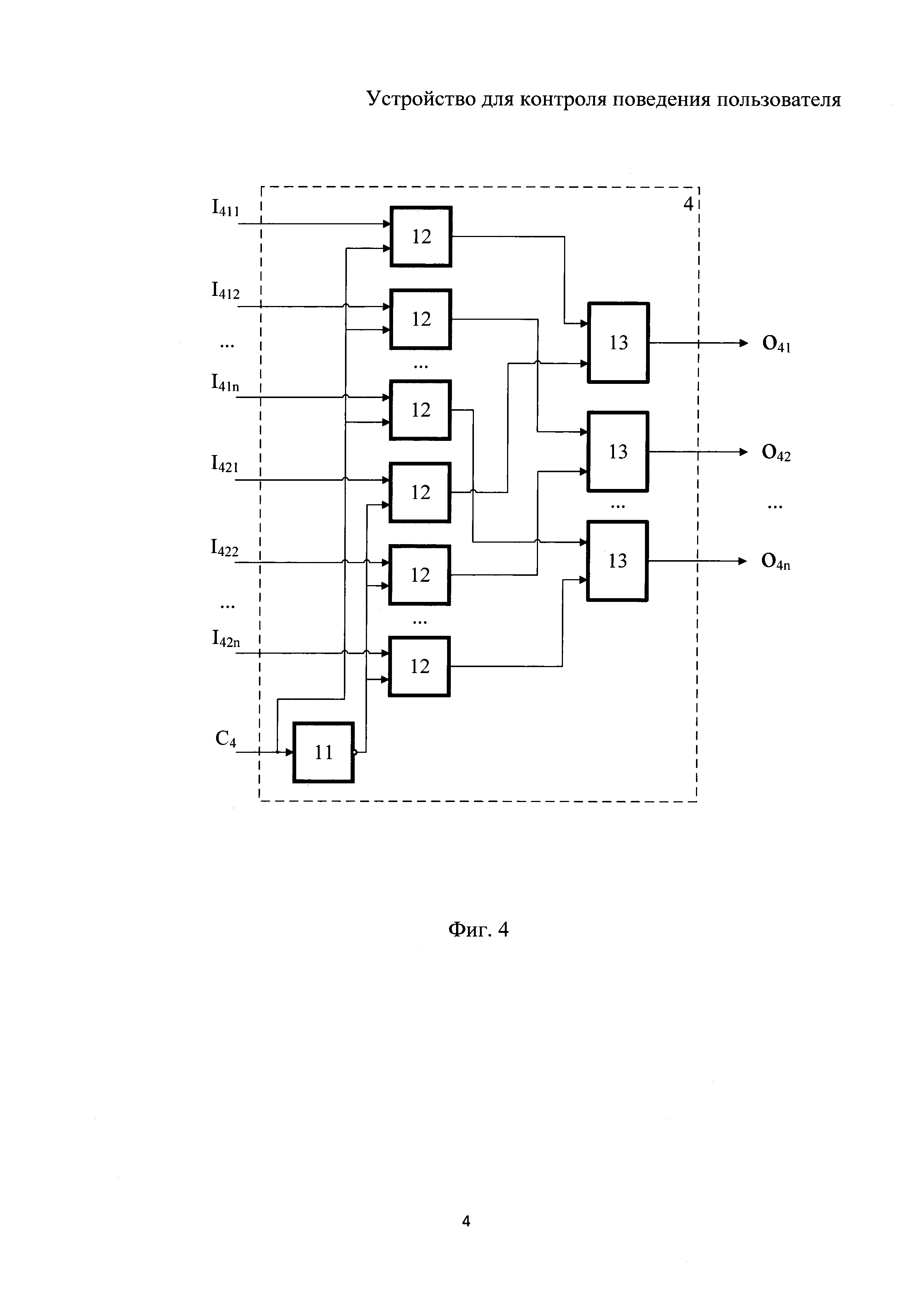

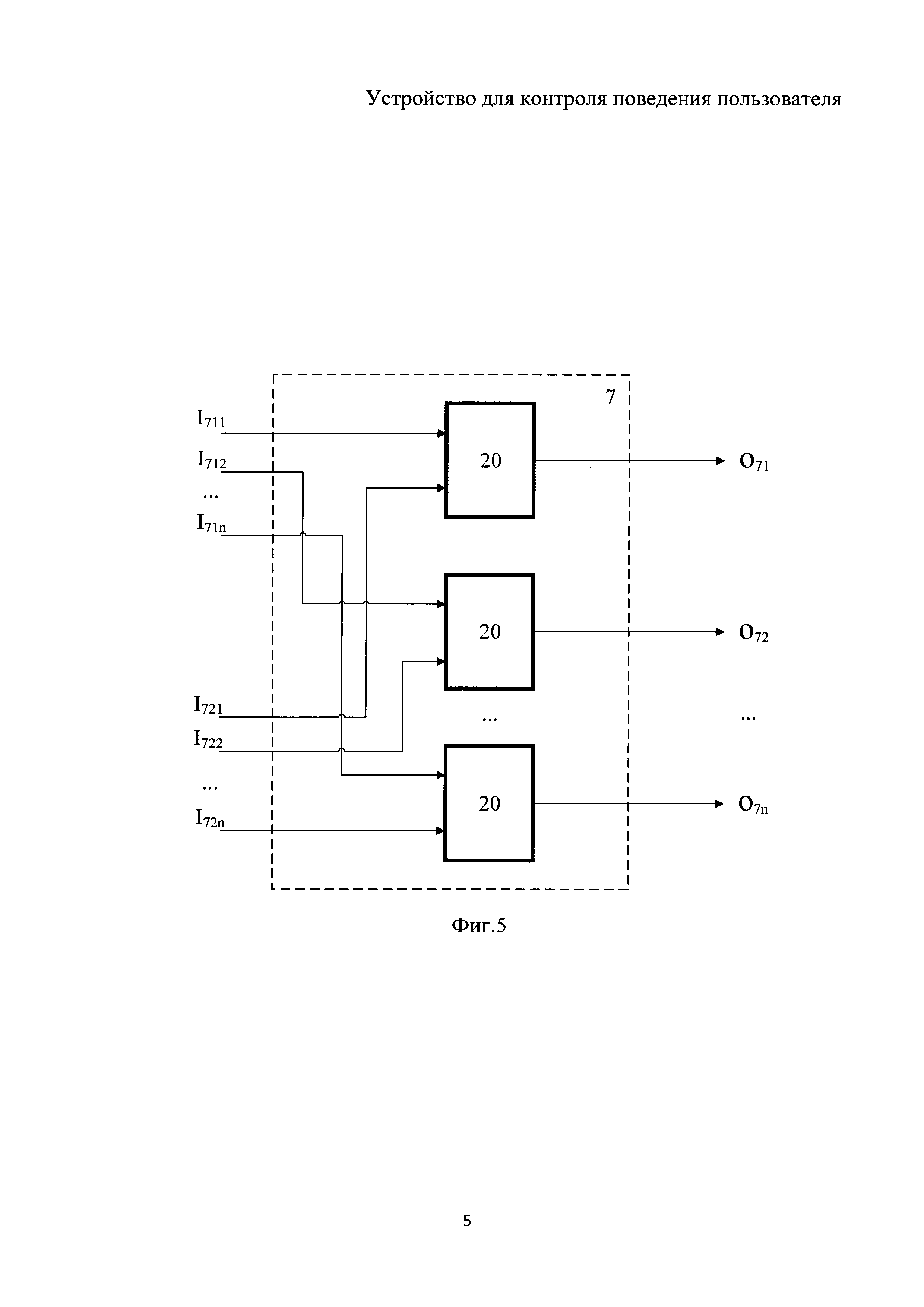

На фиг. 1 представлена структурная схема предлагаемого устройства, на фиг. 2 - структурная схема блока сдвиговых регистров, на фиг. 3 - структурная схема блока управления, на фиг. 4 - структурная схема многоканального коммутатора, на фиг. 5 - структурная схема блока логических элементов И. На фиг. 6 представлены временные диаграммы работы устройства в режиме контроля поведения пользователя, на фиг. 7 - временные диаграммы работы устройства в режиме анализа поведения пользователя, на фиг. 8 - временные диаграммы работы устройства в режиме обучения пользователя.

Устройство содержит регистр кода транзакций 1, блок сдвиговых регистров 2, многоканальный коммутатор 3, блок управления 4,счетчик адресов 5, блок памяти 6, блок логических элементов И 7, схему сравнения 8 и сдвиговый регистр результатов сравнения 9, причем информационные входы регистра кода транзакций 1 и блока сдвиговых регистров 2 подключены, соответственно, к первой и второй группам информационных входов устройства, выход регистра кода транзакций 1 подключен к первой группе адресных входов блока памяти 6, выходы счетчика адресов 5 подключены к первой группе выходов устройства и к третьей адресной группе блока памяти 6, выходы многоканального коммутатора 4 подключены к четвертому выходу устройства, ко входам четвертой адресной группы блока памяти 6 и ко второй группе информационных входов схемы сравнения 8, первая группа информационных входов которой подключена к выходам блока памяти 6 и к первой группе информационных входов блока логических элементов И 7, выходы которого подключены ко второй группе выходов устройства, выход схемы сравнения 8 подключен к третьему выходу устройства, к информационному входу сдвигового регистра результатов 9 и к пятому входу блока управления 5, второй выход которого подключен ко второму адресному входу блока памяти 6, шестой выход блока управления 5 подключен к шестому выходу устройства, а седьмой, восьмой и девятый выходы блока управления 5 подключены к управляющим входам, соответственно, блока сдвиговых регистров 2, многоканального коммутатора 4 и регистра кода транзакций 1, а второй, третий и четвертый входы блока управления 5 подключены, соответственно, ко второму, третьему и четвертому управляющим входам устройства. Адресный код блока памяти состоит из 4 групп двоичных разрядов: А, В, С и D. Первая адресная группа А содержит код транзакции. Она определяет содержание блока памяти для конкретной транзакции. Код В - одноразрядный, он представляет вторую адресную группу и определяет содержание блока памяти для конкретного режима работы устройства, причем значение разряда равно единице, если устройство работает в режиме контроля и анализа. Значение разряда равно нулю, если устройство работает в режиме обучения. Группа С содержит Nc разрядов, причем Nc=]log2K[, где K - максимальное число команд в транзакции. Например, для числа команд пользователя в транзакции, равного 16, Nc=4. Аналогично Nd=]log2R[, где R - число разрядов в коде команды. Обратные квадратные скобки означают округление результата логарифмирования до ближайшего большего целого. Под транзакцией при описании устройства понимается последовательность логически связанных действий, переводящих автоматизированную информационную систему из одного состояния в другое.

Блок сдвиговых регистров 2, как показано на фиг. 2, содержит m n-разрядных сдвиговых регистров 10, где m - число команд в транзакции, причем информационные входы (I21-I2n) сдвиговых регистров 10 через информационные входы блока сдвиговых регистров 2 подключены к информационным входам 2 устройства, первые разряды сдвиговых регистров 10 подключены к первой группе выходов (Q211-Q21n) блока сдвиговых регистров 2, а последние разряды, соответственно, ко второй группе выходов (Q221-Q22n), управляющие входы занесения-сдвига сдвиговых регистров 10 объединены и подключены к управляющему входу блока сдвиговых регистров 2. Принцип работы блока сдвиговых регистров 2 понятен из описания его структурной схемы.

Многоканальный коммутатор 4, как показано на фиг. 3, содержит логический элемент НЕ 11, первую и вторую группу логических элементов И, соответственно, 12 и 13, с числом логических элементов И в каждой группе, равным числу разрядов команды транзакции n, причем первые входы первой группы логических элементов И 12 подключены к соответствующим информационным входам первой группы входов многоканального коммутатора 4 (I411-I41n), первые входы второй группы логических элементов И 13 подключены к соответствующим информационным входам второй группы входов многоканального коммутатора 4 (I421-I42n), вторые входы первой группы логических элементов И 12 объединены и подключены к управляющему входу С4 многоканального коммутатора 4 и ко входу логического элемента НЕ 11, выход которого подключен к объединенным вторым входам логических элементов И 13 второй группы логических элементов И, выходы которых подключены к соответствующим вторым входам логических элементам ИЛИ 14, первые входы которых подключены к соответствующим выходам логических элементов И 12 первой группы логических элементов И, а выходы логических элементов ИЛИ 14 являются выходами многоканального коммутатора 4 (O41-O4n). Принцип работы многоканального коммутатора 4 понятен из описания его структурной схемы

Блок управления 5, как показано на фиг. 4, содержит триггер запуска-останова 15, генератор тактовых импульсов 16, первый и второй логические элементы И, соответственно 17 и 18, блок формирования и распределения управляющих сигналов 19 и логический элемент ИЛИ 20, причем установочный вход триггера пуска-останова 15 подключен через вход I51 к первому управляющему входу устройства, сбросовый вход триггера пуска-останова 15 - к выходу логического элемента ИЛИ 20, входы которого подключены к десятому выходу блока формирования и распределения управляющих сигналов 19 и к выходу второго элемента И 18, второй вход которого подключен к пятому входу I55 блока управления 5, выход триггера пуска останова 15 подключен к первому входу первого логического элемента И 17, второй вход которого подключен к выходу генератора тактовых импульсов 16 и первому входу второго логического элемента И 18, выход первого логического элемента И 17 подключен к четвертому входу блока формирования и распределения управляющих сигналов 19, у которого первый, второй и третий входы подключены через входы I52-I54, соответственно, к управляющим входам 2-4 устройства, первый - девятый выходы блока формирования и распределения управляющих сигналов 19 подключены, соответственно, к первому -девятому выходам блока управления 5. Принцип работы блока управления понятен из описания его структурной схемы

Блок логических элементов И 7, как показано на фиг. 5, содержит логические элементы И 20, число которых равно числу разрядов команды транзакции n причем входы первой группы логических элементов И 20 через первые входы блока логических элементов И 7 (I711-I71n) подключены к соответствующим выходам блока памяти 6 на фиг. 1, а вторые входы логических элементов И 20 через вторые входы блока логических элементов И 7 (I721-I72n) подключены к четвертому выходу блока управления 5 на фиг. 2. Выходы блока логических элементов И 7 являются выходами 3 устройства. Принцип работы блока логических элементов И 7 понятен из описания его структурной схемы.

На фиг. 6 временные диаграммы: "I51-I54", "s1-s6", "Q51-Q59" представляют процессы поступления и формирования сигналов в режиме контроля работы устройства, соответственно, на входах блока управления 5, на входах и выходах элементов блока управления 5, и на выходе самого блока управления 5, представленного на фиг. 4.

На фиг. 7 и фиг. 8 представлены аналогичные временные диаграммы сигналов работы устройства, соответственно, в режиме анализа и в режиме обучения.

Предлагаемое устройство работает следующим образом. Устройство работает в трех режимах: режим контроля поведения пользователя; - режим анализа поведения; режим обучения.

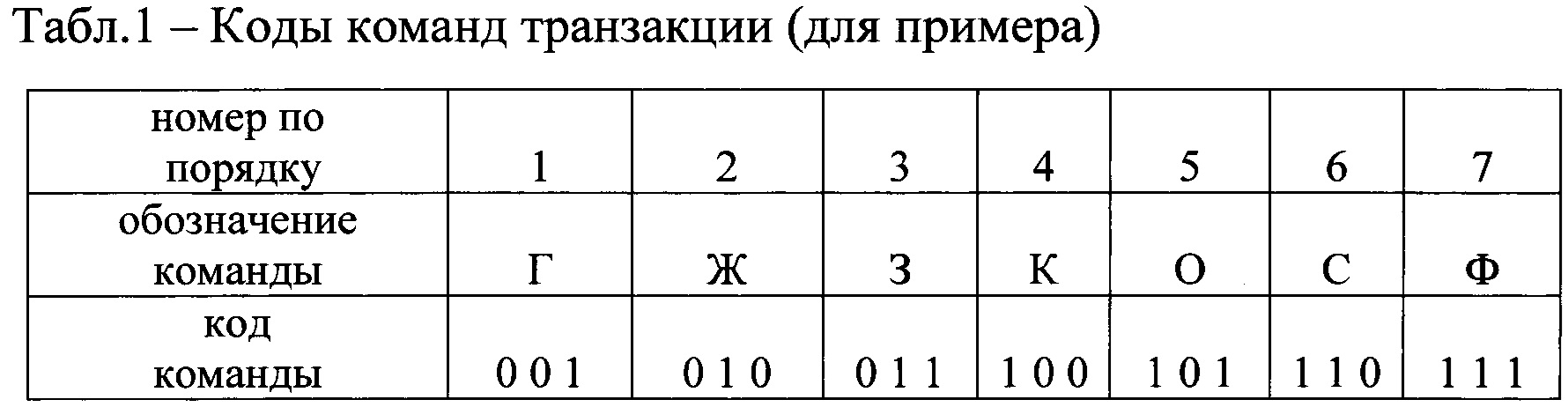

Режим контроля поведения пользователя. В исходном состоянии счетчик адресов 3, все сдвиговые регистры блока сдвиговых регистров 2 - обнулены. В блоке памяти 6 записана информация, соответствующая санкционированной последовательности команд пользователя, составляющих контролируемую транзакцию, таким образом, что код каждой команды пользователя, поданный на адресный вход блока памяти 6, инициирует чтение соответствующего контрольного кода санкционированной команды. Для иллюстрации работы устройства в таблицах 1, 2 и 3 представлены коды примерной контролируемой транзакции и содержимое блока памяти 6 в режиме контроля пользователя.

Для удобства проверки обозначение кодов команд и их последовательность в транзакции соответствуют начальным буквам слов, обозначающих цвета радуги: К, О, Ж, 3, Г, С. Ф.

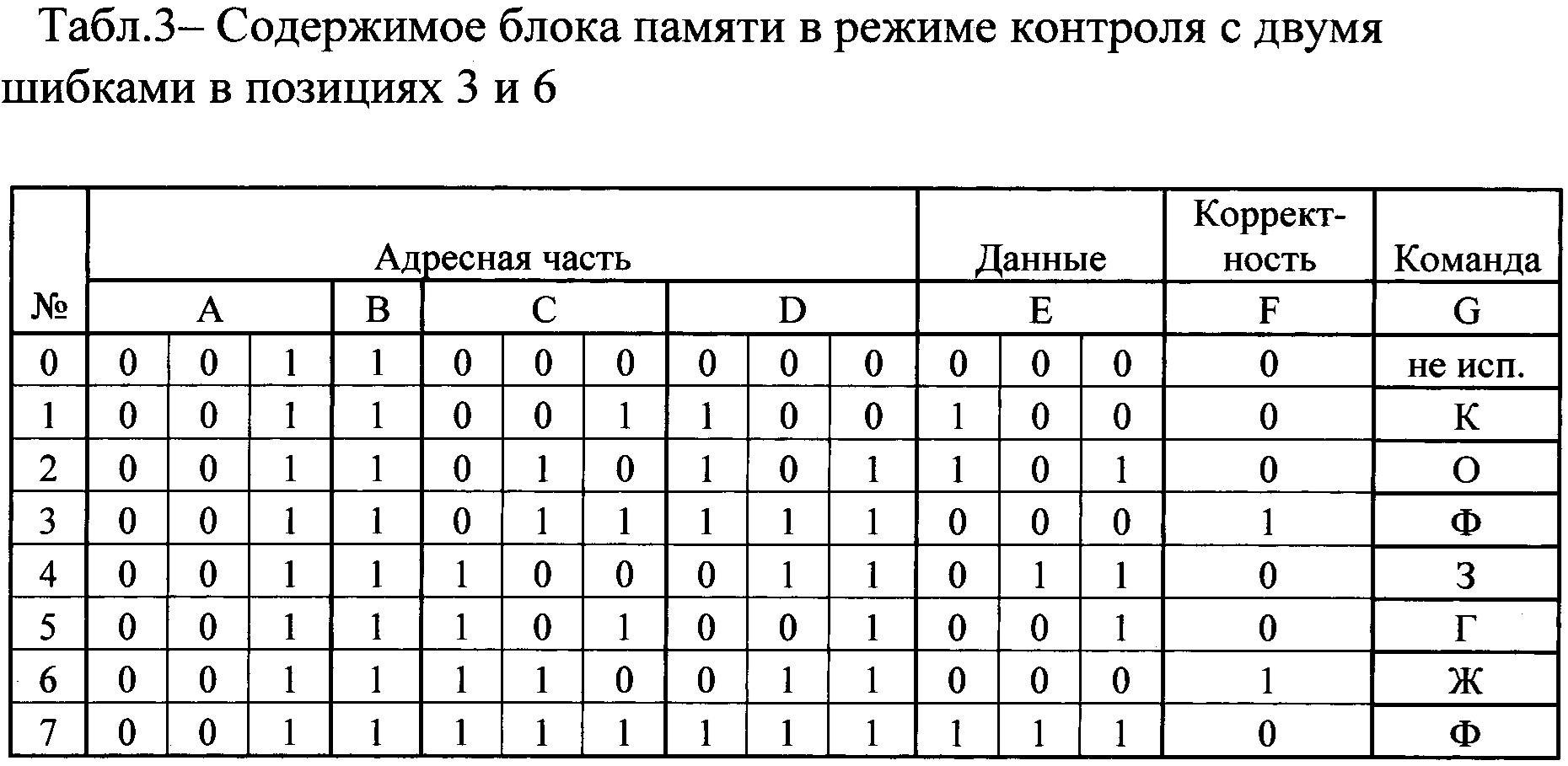

В таблице 2 в колонках А, В, С, D и Е представлено содержимое блока памяти 6 в режиме контроля без ошибок. В колонке F нулевой код свидетельствует о соответствии содержимого колонок С и Е, т.е. об отсутствии ошибки. В колонке G представлены наименования команд транзакции в порядке ее выполнения. Коды нулевой строки таблицы не использованы.

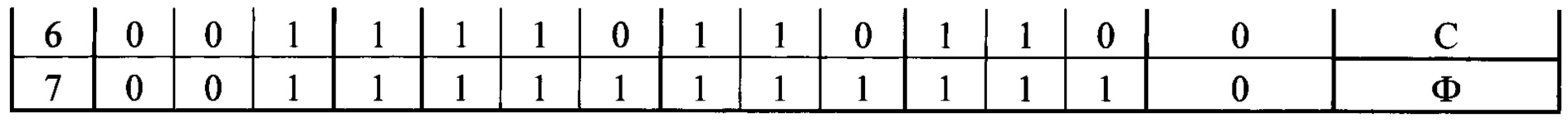

В таблице 3 в колонках А, В, С, D и Е представлено содержимое блока памяти 6 в режиме контроля с двумя ошибками в позициях 3 и 6. В колонке F единичный код свидетельствует о несоответствии содержимого колонок С и Е, т.е. о наличии ошибки. В колонке G представлены наименования команд транзакции, задаваемых пользователем. Для инициализации режима контроля на второй вход устройства (I52 на фиг. 3) подается отрицательный сигнал. По отрицательному импульсному сигналу «пуск» (на входе I51 на фиг. 3), поступающему на первый вход блока управления 5 на седьмом выходе блока управления 5 (см. фиг. 3 и фиг. 6) формируется сигнал, по которому в первые разряды сдвиговых регистров 10 блока сдвиговых регистров 2 со второго информационного входа устройства заносится цифровой код первой команды транзакции. При этом на управляющий вход многоканального коммутатора 4 с восьмого выхода блока управления 5 поступает сигнал положительной полярности, подающий коды первой команды с первой группы выходов блока сдвиговых регистров 2 на адресные входы четвертой группы блока памяти 6. Далее на счетный вход счетчика адресов 3 подается счетный импульс с первого выхода блока управления 5, определяющий адрес первой команды транзакции, а на второй адресный вход блока памяти 6 со второго выхода блока управления 5 подается положительный импульс (код 1 в колонке В в таблице 2), определяющий адресную часть блока памяти 6, используемую в режиме контроля. По совокупному адресу, сформированному на четырех группах адресных входов блока памяти 6, и по сигналу чтения на управляющем входе блока памяти 6, поступающему с третьего выхода блока управления 5, а также по положительному сигналу с выхода блока управления 5, поступающему на вторые информационные входы блока логических элементов И 7, на выходе блока памяти 6, а также на втором выходе устройства, появляется контрольный код первой команды пользователя. При этом на информационные входы схемы сравнения 8 поступают коды первой команды пользователя с выходов многоканального коммутатора 4 и контрольные коды этой команды из блока памяти 6. При неравенстве кодов на входах схемы сравнения 8 с выхода схемы сравнения 8 на третий выход устройства, на информационный вход сдвигового регистра результатов сравнения 9 и пятый вход блока управления 5 подается сигнал положительной полярности, и процедура контроля завершается. При этом на третий выход устройства поступает сигнал положительной полярности, свидетельствующий об обнаружении ошибки, который по управляющему сигналу, поступающему с пятого выхода блока управления 5, регистрируется в сдвиговом регистре результатов сравнения 9. При равенстве кодов на третий выход устройства поступает сигнал отрицательной полярности, разрешающий ввод следующей команды транзакции. При подаче второй и последующих команд транзакции подается сигнал «пуск» на первый управляющий вход устройства. В блоке управления 5 ведется подсчет количества команд транзакции, и по достижении их конечного числа режим контроля завершается.

Режим анализа поведения предназначен для выявления характера ошибок в поведении пользователя при выполнении транзакции. Исходное состояние режима анализа аналогично исходному состоянию режима контроля устройства. Выбор режима анализа производится подачей положительного сигнала на третий управляющий вход (I53 на фиг. 7) устройства. При этом на шестом выходе устройства появляется сигнал готовности к приему команд транзакций. В режиме анализа устройство работает аналогично режиму контроля. Отличие режима заключается в то, что в случае ошибки устройство фиксирует ошибку в сдвиговом регистре результатов сравнения 9 и продолжает ввод остальных команд до конца транзакции. При этом в блоке сдвиговых регистров 2 производится регистрация всех команд пользователя, а в сдвиговом регистре результатов сравнения 9 формируется код корректности этих команд. В разрядах сдвигового регистра результатов 9, соответствующих правильному коду содержится ноль, в разрядах сдвигового регистра результатов, соответствующих неверному коду, соответственно единица (коды в колонках F в таблицах 2 и 3)

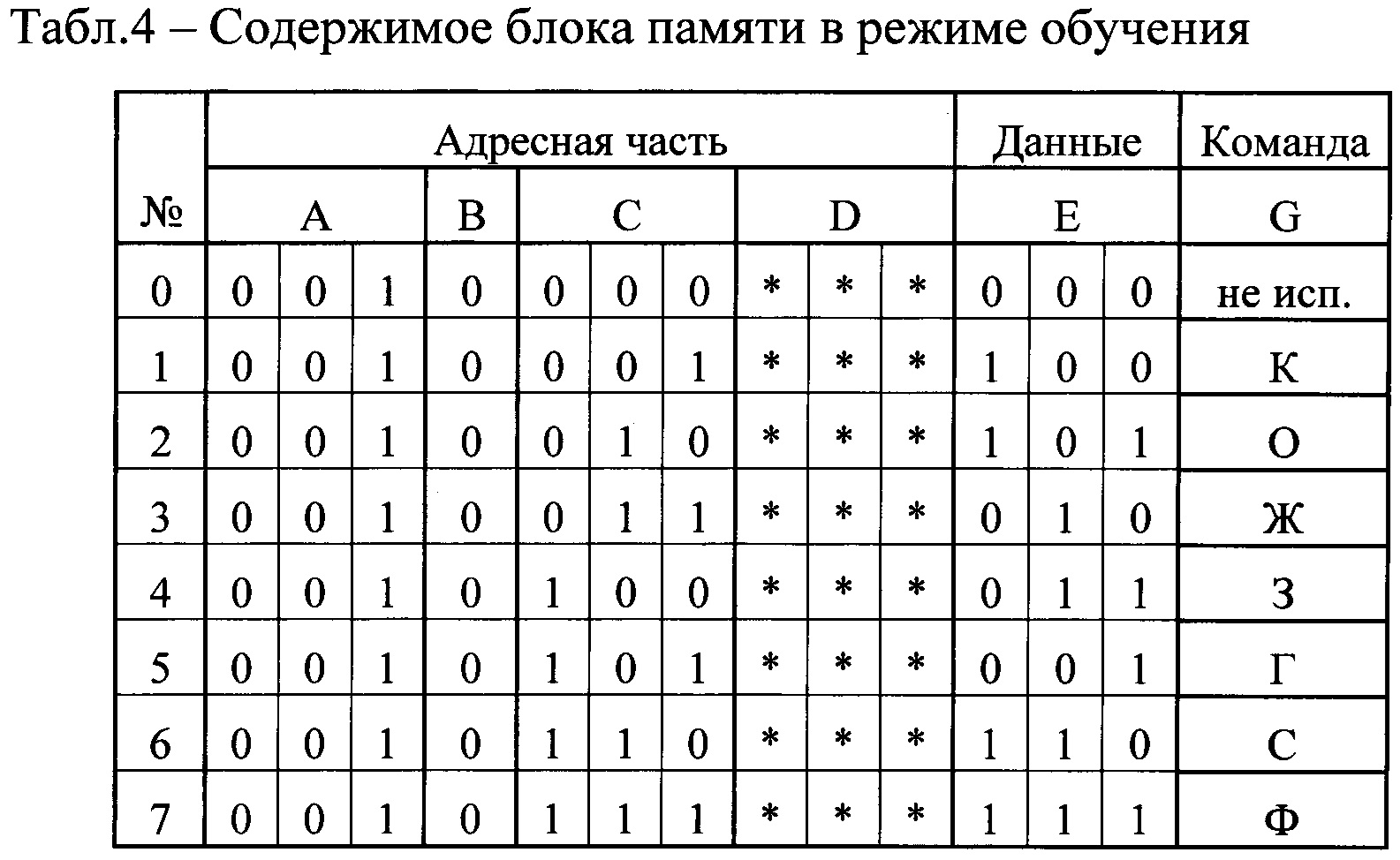

Режим обучения предназначен для ознакомления пользователя с составом команд транзакции и порядком их задания. Исходное состояние устройства соответствует конечному состоянию его в режиме анализа. Для перехода в режим обучения на управляющий вход 4 устройства подается сигнал положительной полярности. Просмотр каждой команды производится подачей отрицательного импульса «пуск» на первый управляющий вход устройства. При этом, в отличие от первых двух режимов, с выхода 8 блока управления 5 на управляющий вход многоканального коммутатора и с выхода 2 блока управления 5 на второй адресный вход блока памяти 6 не подаются положительные сигналы, что позволяет производить вывод содержимого блока сдвиговых регистров 2 на выход 4 устройства со вторых входов блока многоканального коммутатора 4, а также считывать контрольные команды из блока памяти 6 независимо от кодов на четвертых адресных входах блока памяти 6. Содержимое блока памяти 6 для реализации режима обучения представлено в таблице 4. В колонке D этой таблицы адресные коды представлены звездочками, которые обозначают любые возможные команды пользователя (корректные и некорректные), вызывающие в режиме обучения корректные команды из колонки данных.

При последующей последовательной подаче отрицательного сигнала на первый управляющий вход устройства из блока памяти 6 на выход 2 устройства подаются последовательно все корректные команды выбранной транзакции, а на выход 4 - все команды пользователя, зарегистрированные в режиме анализа в блоке сдвиговых регистров 2. При этом на выходе 3 устройства формируется код совпадения команд.

Таким образом, предлагаемое устройство, в отличие от известного, имеет большую универсальность, оно позволяет, кроме операции распознавания отдельных образов (команд), выполнять операцию распознавания их последовательностей, а также операции контроля и анализа корректности ввода команд и операцию обучения пользователя.

Достоинством предлагаемого устройства также является возможность контроля содержимого блока памяти 6, самого устройства со стороны администратора системы контроля, когда он по специальной проверочной процедуре по гарантированно корректным командам транзакции инспектирует работу самого устройства. Изобретение может быть также использовано в системах защиты информации, в частности, для защиты информации от несанкционированного доступа на основе контроля действий пользователя.

Устройство может быть реализовано на доступной элементной базе электронных микросхем. В частности, блок памяти 6 может быть реализован на базе микросхем серии К565РУ1, а остальные блоки устройства на базе типовых микросхем серии К155.

Устройство для контроля поведения пользователя, содержащее блок памяти; блок сдвиговых регистров, в котором информационные входы первых разрядов сдвиговых регистров подключены к соответствующим информационным входам блока сдвиговых регистров, сдвиговые входы сдвиговых регистров подключены к соответствующим сдвиговым входам блока сдвиговых регистров, а выходы последних разрядов сдвиговых регистров подключены к выходам блока сдвиговых регистров; блок логических элементов И, в котором первые входы логических элементов И через первые входы блока логических элементов подключены к соответствующим выходам блока памяти, а вторые входы логических элементов И через вторые входы блока логических элементов И подключены к четвертому выходу блока управления; многоканальный коммутатор; счетчик адресов, выходы которого подключены к адресным входам блока памяти; блок управления, первый и третий выходы которого подключены, соответственно, к управляющему входу счетчика адресов и блока памяти, а первый вход к первому управляющему входу устройства; отличающееся тем, что в него дополнительно включены: регистр кода транзакций, схема сравнения и сдвиговый регистр результатов сравнения, причем информационные входы регистра кода транзакций и блока сдвиговых регистров подключены, соответственно, к первой и второй группам информационных входов устройства, в блоке сдвиговых регистров сдвиговые входы блока сдвиговых регистров объединены и подключены к седьмому выходу блока управления, а все выходы блока сдвиговых регистров разделены на две группы, причем первую группу составляют выходы первых разрядов сдвиговых, а вторую - выходы последних разрядов сдвиговых регистров, в блоке памяти все адресные входы разделены на 4 группы, причем первая адресная группа содержит старшие адресные разряды, а вторая, третья и четвертая группы, соответственно, разряды в порядке уменьшения их величины, выход регистра кода транзакций подключен к первой адресной группе входов блока памяти, выходы счетчика адресов подключены к третьей адресной группе блока памяти и к первой группе выходов устройства, информационные входы многоканального коммутатора подключены к выходам блока сдвиговых регистров, а выходы многоканального коммутатора подключены к четвертому выходу устройства, а также ко входам четвертой адресной группы блока памяти и ко второй группе информационных входов схемы сравнения, первая группа информационных входов которой подключена к выходам блока памяти и к первой группе входов блока логических элементов И, выходы которого подключены ко второй группе выходов устройства, выход схемы сравнения подключен к третьему выходу устройства, к информационному входу сдвигового регистра результатов сравнения и к пятому входу блока управления, второй выход которого подключен ко второму адресному входу блока памяти, пятый выход блока управления подключен к управляющему входу сдвигового регистра результатов сравнения, шестой выход блока управления подключен к шестому выходу устройства, восьмой и девятый выходы блока управления подключены к управляющим входам, соответственно, многоканального коммутатора и регистра кода транзакций, а второй, третий и четвертый входы блока управления подключены, соответственно, ко второму, третьему и четвертому управляющим входам устройства.